半导体封装

1.相关申请的交叉引用

2.本技术要求2020年9月9日向韩国知识产权局递交的韩国专利申请no.10-2020-0115321的优先权,其内容通过引用整体并入本文。

技术领域

3.本发明构思的实施例涉及一种半导体封装,并且更具体地,涉及一种包括重分布基板的半导体封装及其制造方法。

背景技术:

4.半导体封装实现了在电子产品中使用的集成电路芯片。通常,半导体封装被配置为使得半导体芯片安装在印刷电路板(pcb)上,并且接合线或凸块用于将半导体芯片电连接到印刷电路板。

技术实现要素:

5.本发明构思的一些实施例提供了一种具有提高的可靠性的半导体封装及其制造方法。

6.根据本发明构思的一些实施例,半导体封装包括:重分布基板;以及半导体芯片,设置在重分布基板上。重分布基板包括:接地凸块下图案(ground under-bump pattern);多个信号凸块下图案(signal under-bump pattern),与接地凸块下图案横向地间隔开;多个第一信号线图案,设置在多个信号凸块下图案上,并与多个信号凸块下图案中的对应图案耦接;以及第一接地图案,耦接到接地凸块下图案,并与第一信号线图案横向地间隔开。信号凸块下图案和接地凸块下图案中的每一个包括:第一部分;以及第二部分,形成在第一部分上并比第一部分宽。接地凸块下图案的第二部分比信号凸块下图案的第二部分宽。接地凸块下图案与多个第一信号线图案在竖直方向上重叠。第一接地图案不与多个信号凸块下图案在竖直方向上重叠。

7.根据本发明构思的一些实施例,一种半导体封装包括:重分布基板,包括彼此面对的第一表面和第二表面;半导体芯片,设置在重分布基板的第一表面上;以及多个接地焊接图案,设置在重分布基板的第二表面上。重分布基板包括:凸块下图案,包括多个接地凸块下图案和多个信号凸块下图案,多个信号凸块下图案与接地凸块下图案横向地间隔开;第一导电图案,设置在凸块下图案的顶表面上并电连接到凸块下图案;以及第二导电图案,设置在第一导电图案上并耦接到第一导电图案。接地凸块下图案包括:多个第一部分,连接到多个接地焊接图案中的相应图案;以及第二部分,在平行于半导体芯片的顶表面的第一方向上延伸并连接到多个第一部分。第一导电图案包括多个第一信号线图案,该多个第一信号线图案耦接到多个信号凸块下图案中的相应图案。第二导电图案包括在第一方向上延伸的第二接地线图案。多个第一信号线图案设置在接地凸块下图案的顶表面和第二接地线图案的底表面之间。

8.根据本发明构思的一些实施例,半导体封装包括:重分布基板,包括彼此面对的第一表面和第二表面;半导体芯片,设置在重分布基板的第一表面上;以及多个焊接图案,设置在重分布基板的第二表面上。重分布基板包括:接地凸块下图案(ground under-bump pattem);下接地线图案,设置在接地凸块下图案上,该下接地线图案在平行于半导体芯片的顶表面的第一方向上延伸;上接地线图案,与下接地线图案在竖直方向上间隔开,该上接地线图案在第一方向上延伸;接地接合焊盘,介于上接地线图案和半导体芯片的芯片焊盘之间;信号凸块下图案,与接地凸块下图案横向地间隔开;多个下信号线图案,设置在接地凸块下图案的顶表面和下接地线图案的底表面之间;以及多个上信号线图案,设置在下接地线图案的顶表面和上接地线图案的底表面之间。接地凸块下图案和信号凸块下图案中的每一个包括:第一部分,耦接到多个焊接图案之一;以及第二部分,连接到第一部分并且比第一部分宽。接地凸块下图案的第二部分的截面面积大于信号凸块下图案的第二部分的截面面积。

附图说明

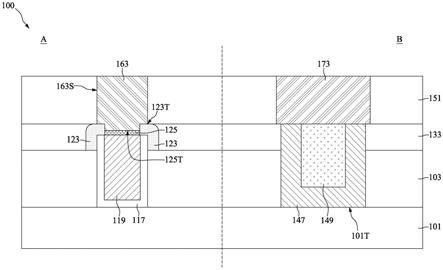

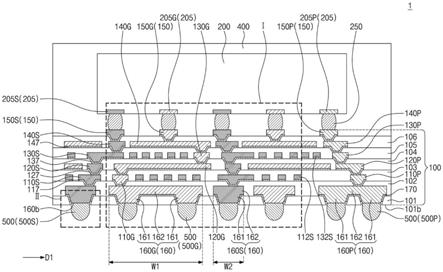

9.图1a是根据一些实施例的半导体封装的截面图。

10.图1b是示出了图1a的部分i的放大图。

11.图1c是图1a的部分ii的放大图。

12.图1d是根据一些实施例的凸块下图案的平面图。

13.图1e是根据一些实施例的第一导电图案的平面图。

14.图1f是根据一些实施例的第二导电图案的平面图。

15.图1g是根据一些实施例的凸块下种子图案和凸块下图案的截面图。

16.图2a至图2n示出了根据一些实施例的制造半导体封装的方法的截面图。

17.图3是根据一些实施例的半导体封装的截面图。

18.图4是根据一些实施例的半导体封装的截面图。

19.图5是根据一些实施例的半导体封装的截面图。

20.图6是根据一些实施例的半导体封装的截面图。

具体实施方式

21.在本说明书中,相同的附图标记可以表示相同的组件。

22.本文所使用的“约”或“近似”包括所述值和本领域普通技术人员所确定的对于特定值而言在可接受的偏差范围内的平均值,其考虑了所讨论的测量以及与特定量的测量相关联的误差,即,测量系统的局限性。

23.图1a是根据一些实施例的半导体封装的截面图。图1b是图1a的部分i的放大图。图1c是图1a的部分ii的放大图。图1d是根据一些实施例的凸块下图案的平面图。图1e是根据一些实施例的第一导电图案的平面图。图1f是根据一些实施例的第二导电图案的平面图。图1b对应于沿图1d、图1e或图1f的线a-b截取的截面。

24.参照图1a、图1b、图1c、图1d和图1e,根据一些实施例,半导体封装1包括重分布基板100、半导体芯片200和焊接图案500。重分布基板100具有彼此面对的第一表面和第二表面。第一表面可以是重分布基板100的顶表面,并且第二表面可以是重分布基板100的底表

面。

25.根据一些实施例,焊接图案500设置在重分布基板100的第二表面上。焊接图案500用作半导体封装1的端子。焊接图案500可以包括焊球、凸块、柱或其任何组合。焊接图案500包括焊接材料。在本说明书中,焊接材料包括锡、铋、铅、银或其任何合金。焊接图案500包括接地焊接图案500g、信号焊接图案500s和电源焊接图案500p。接地焊接图案500g、信号焊接图案500s和电源焊接图案500p彼此横向地间隔开并且电隔离。施加到电源焊接图案500p的电压与施加到接地焊接图案500g的电压不同。信号焊接图案500s用作将数据信号输入到半导体芯片200或从半导体芯片200输出的路径。

26.根据一些实施例,重分布基板100包括凸块下图案160、凸块下种子图案170、第一导电图案110s、110g和110p、第二导电图案120s、120g和120p、第三导电图案130s、130g和130p、第四导电图案140s、140g和140p、接合焊盘150和介电层。介电层可以包括第一介电层101、第二介电层102、第三介电层103、第四介电层104、第五介电层105和第六介电层106。

27.根据一些实施例,凸块下图案160设置在第一介电层101中。凸块下图案160包括金属,例如,铜。然而,凸块下图案160不包括例如钛。凸块下图案160中的每一个包括第一部分161和第二部分162。凸块下图案160中的每一个的第一部分161是焊接盘。凸块下图案160中的每一个的第二部分162设置在第一部分161上,并且第一部分161和第二部分162彼此一体地连接,而在它们之间没有边界。第二部分162平行于第一方向d1延伸。第一方向d1平行于半导体芯片200的顶表面。因此,凸块下图案160的第二部分162用作布线或线部分。例如,凸块下图案160的第二部分162可以是水平地传输从与其连接的焊接图案500接收到的电信号的路径。在本说明书中,术语“水平地”可以表示“平行于半导体芯片200的顶表面”。凸块下图案160的第二部分162的宽度大于凸块下图案160的第一部分161的宽度。凸块下图案160的第二部分162的宽度对应于凸块下图案160的顶表面的宽度,并且凸块下图案160的第一部分161的宽度对应于凸块下图案160的底表面160b的宽度。凸块下图案160的底表面160b面对凸块下图案160的顶表面。凸块下图案160的底表面160b是第一部分161的底表面。凸块下图案160的顶表面是第二部分162的顶表面。由于凸块下图案160的第二部分162是布线或线部分,所以可以减少堆叠的导电图案110s、110g、110p、120s、120g、120p、130s、130g、130p、140s、140g和140p的数量。因此,半导体封装1变得更紧凑。

28.根据一些实施例,凸块下图案160包括信号凸块下图案160s、接地凸块下图案160g和电源凸块下图案160p。信号凸块下图案160s、接地凸块下图案160g和电源凸块下图案160p分别耦接到信号焊接图案500s、接地焊接图案500g和电源焊接图案500p。信号凸块下图案160s、接地凸块下图案160g和电源凸块下图案160p中的每一个包括第一部分161和第二部分162。第二部分162设置在第一部分161上,并且第一部分161和第二部分162彼此一体地连接,而在它们之间没有边界。接地凸块下图案160g的第二部分162和电源凸块下图案160p的第二部分162均用作布线或线部分。

29.根据一些实施例,接地凸块下图案160g的第一部分161与对应的接地焊接图案500g接触。提供了多个接地凸块下图案160g,并且多个接地凸块下图案160g中的至少一个包括多个第一部分161,并且多个接地凸块下图案160g中的另一个包括单个第一部分161。至少一个接地凸块下图案160g的第二部分162设置在多个第一部分161上并电连接到多个第一部分161。因此,可以省略合并接地凸块下图案160g的单独导电图案。半导体封装1可以

具有简化的制造工艺和减小的厚度。

30.根据一些实施例,电源凸块下图案160p横向地与接地凸块下图案160g间隔开并与接地凸块下图案160g电隔离。提供了多个电源凸块下图案160p,并且多个电源凸块下图案160p中的至少一个包括多个第一部分161。电源凸块下图案160p的第一部分161与对应的电源焊接图案500p接触。至少一个电源凸块下图案160p的第二部分162设置在多个第一部分161上并电连接到多个第一部分161。因此,可以省略合并电源凸块下图案160p的单独导电图案。半导体封装1可以具有简化的制造工艺。另外,多个电源凸块下图案160p中的另一个包括单个第一部分161。

31.根据一些实施例,信号凸块下图案160s横向地与接地凸块下图案160g和电源凸块下图案160p间隔开并且与接地凸块下图案160g和电源凸块下图案160p电隔离。每个信号凸块下图案160s包括单个第一部分161。例如,信号凸块下图案160s的第二部分162电连接到单个第一部分161和单个信号焊接图案500s。

32.根据一些实施例,信号凸块下图案160s的第二部分162的宽度w2小于接地凸块下图案160g的第二部分162处的宽度w1。信号凸块下图案160s的第二部分162的横截面面积小于接地凸块下图案160g的第二部分162的横截面面积。接地凸块下图案160g的第二部分162用作布线或接线,但是信号凸块下图案160s的第二部分162不用作线部分。下面将讨论凸块下图案160的平面布置和形状。

33.如图1d所示,根据一些实施例,信号凸块下图案160s在平面图中具有圆形形状,但是本发明构思的实施例不限于此。接地凸块下图案160g的第二部分162具有不同于信号凸块下图案160s的第二部分162的平面形状和平面面积。例如,接地凸块下图案160g具有多边形形状,例如,四边形形状。对于另一示例,接地凸块下图案160g具有包括矩形段和连接到该矩形段的圆形段的平面形状。接地凸块下图案160g的顶表面处的平面面积大于信号凸块下图案160s的顶表面处的平面面积。接地凸块下图案160g的第二部分162具有相对较大的平面面积,因此可以电屏蔽第一导电图案110s、110g和110p,这将在下面讨论。除非在本说明书中另外公开,否则特定组件的平面形状和平面面积指示特定组件的顶表面处的平面形状和平面面积。

34.根据一些实施例,接地凸块下图案160g具有相对较大的平面面积。接地凸块下图案160g的第二部分162还可以具有第一孔169。第一孔169从接地凸块下图案160g的第二部分162的顶表面穿透到底表面。第二介电层102通过第一孔169直接接触第一介电层101。即使接地凸块下图案160g在平面图中具有相对较大的平面面积,第一孔169的存在也可以防止凸块下图案160集中在特定区域中。因此,重分布基板100具有提高的可靠性。第一孔169的形成可以通过接地凸块下图案160g的平面面积的大小来确定。

35.返回参考图1b和图1c,根据一些实施例,第一介电层101设置在凸块下图案160的侧壁上。第一介电层101是最下方的介电层。凸块下图案160的第一部分161的底表面160b未被第一介电层101覆盖。如图1c所示,凸块下图案160的第一部分161的底表面160b位于比第一介电层101的底表面101b更高的水平处。在本说明书中,术语“水平”指代竖直水平,并且在垂直于第一介电层101的底表面101b或半导体芯片200的顶表面的方向上测量水平差。第一介电层101的底表面101b平行于半导体芯片200的顶表面。第一介电层101包括有机材料,例如,光敏聚合物。在本说明书中,光敏聚合物可以是例如光敏聚酰亚胺、聚苯并恶唑、酚醛

聚合物或苯并环丁烯聚合物中的一种或多种。

36.根据一些实施例,凸块下种子图案170没置在凸块下图案160的第一部分161的侧壁上和凸块下图案160的第二部分162的底表面上。凸块下种子图案170介于第一介电层101和凸块下图案160之间。凸块下种子图案170增加了第一介电层101和凸块下图案160之间的粘合力。因此,半导体封装1具有提高的可靠性和耐久性。

37.根据一些实施例,凸块下种子图案170没有设置在凸块下图案160的第一部分161的底表面160b上。焊接图案500物理地接触凸块下图案160的第一部分161的底表面160b。在焊接图案500和凸块下图案160之间形成相对较大的粘合力。因此,可以将焊接图案500稳定地附接到凸块下图案160。

38.如图1c所示,根据一些实施例,设置在凸块下图案160的第二部分162的底表面上的凸块下种子图案170的一部分具有第一厚度t11。第一厚度t11是在第一介电层101的顶表面和凸块下图案160的第二部分162的底表面之间的凸块下种子图案170的厚度。凸块下种子图案170具有设置在凸块下图案160的第一部分161的侧壁和第一介电层101的侧壁之间的最下表面170b。凸块下种子图案170的最下表面170b位于比凸块下图案160的底表面160b更高的水平处。凸块下种子图案170的最下表面170b和凸块下图案160的底表面160b之间具有大于第一厚度t11且小于第一厚度t11的10倍的水平差。凸块下图案160的底表面160b位于比第一介电层101的底表面101b更高的水平处。凸块下图案160的底表面160b和第一介电层101的底表面101b之间具有与第一厚度t11基本相同的水平差。

39.如图1a和图1b所示,根据一些实施例,第二介电层102设置在第一介电层101上,并且覆盖第一介电层101的顶表面以及凸块下图案160的第二部分162的顶表面和侧壁。第二介电层102包括例如光敏聚合物。第一介电层101和第二介电层102之间具有模糊的边界。

40.如图1b所示,根据一些实施例,第一导电图案110s、110g和110p分别设置在凸块下图案160s、160g和160p上并耦接到凸块下图案160s、160g和160p。第一导电图案110s、110g和110p包括第一信号图案110s、第一接地图案110g和第一电源图案110p。第一信号图案110s、第一接地图案i10g和第一电源图案110p被电隔离并且彼此横向地间隔开。第一导电图案110s、110g和110p中的每一个包括金属,例如,铜。

41.根据一些实施例,第一信号图案110s包括第一信号通孔部分111s和第一信号线图案112s。在本说明书中,导电组件的通孔部分是用于竖直连接的部分。导电组件的线图案是用于水平连接的部分。第一信号通孔部分111s穿透第二介电层102的上部并耦接到信号凸块下图案160s。第一信号线图案112s设置在第二介电层102的顶表面上,并且第一信号线图案112s和第一信号通孔部分111s彼此一体地连接,而在它们之间没有边界。第一信号线图案112s包括与第一信号通孔部分111s相同的材料。第一信号线图案112s的底表面位于比第一信号通孔部分111s的底表面更高的水平处。第一信号线图案112s水平地延伸。例如,第一信号线图案112s平行于第一方向d1延伸。对于另一示例,在如图1e所示的平面图中,第一信号线图案112s的至少一部分具有与第二方向d2平行的部分。第二方向d2平行于第一介电层101的底表面101b并与第一方向d1相交。对于另一示例,第一信号线图案112s还包括在第三方向d3上延伸的部分。第三方向d3平行于第一介电层101的底表面101b,与第一方向d1和第二方向d2相交,并在由第一方向d1和第二方向d2限定的平面中倾斜地延伸。第一信号线图案112s的平面布置和形状不限于图1e所示,并且在其他实施例中可以变化。第一信号线图

案112s是下信号线图案。

42.根据一些实施例,提供了多个第一信号图案110s。多个第一信号图案110s包括彼此横向地间隔开的第一信号线图案112s。第一信号线图案112s具有窄间距和小宽度。因此,半导体封装1可以高度集成。例如,第一信号线图案112s中的每一个的宽度小于对应的接地凸块下图案160g的宽度w1。对应的接地凸块下图案160g在竖直方向上与第一信号线图案112s重叠。

43.根据一些实施例,当在第一信号线图案112s的底表面上不存在接地组件时,在第一信号线图案112s和外部器件之间会发生电干扰。根据一些实施例,多个第一信号线图案112s设置在接地凸块下图案160g的顶表面上。例如,接地凸块下图案160g的第二部分162在竖直方向上与第一信号线图案112s重叠。因此,当半导体封装1操作时,可以防止接地凸块下图案160g和外部电子器件之间的电干扰。半导体封装1具有提高的操作可靠性。

44.根据一些实施例,第一接地图案110g包括通孔部分,但是不包括线部分。第一接地图案110g耦接到接地凸块下图案160g。第一接地图案110g包括设置在第二介电层102中的下部。第一接地图案110g包括与第一信号线图案112s横向地间隔开的上部。如图1e所示,第一接地图案110g在平面图中具有圆形形状。

45.根据一些实施例,第一电源图案110p包括通孔部分,但是不包括线部分。第一电源图案110p耦接到电源凸块下图案160p。第一电源图案110p包括设置在第二介电层102中的下部。

46.根据一些实施例,第一种子图案117介于第一导电图案110s、110g和110p中的每一个与相应的凸块下图案160之间以及介于第一导电图案110s、110g和110p中的每一个与第二介电层102之间。第一种子图案117可以包括例如铜、钛或其合金。

47.根据一些实施例,第三介电层103设置在第二介电层102上,并且覆盖第一导电图案110g、110s和110p。例如,第三介电层103覆盖第一接地图案110g的上侧壁和顶表面、第一电源图案110p的上侧壁和顶表面、第一信号通孔部分111s的上侧壁和顶表面、以及第一信号线图案112s的侧壁和顶表面。第三介电层103包括例如光敏聚合物。第三介电层103包括与第二介电层102相同的材料。第二介电层102和第三介电层103之间具有模糊的边界。第一种子图案117不介于第三介电层103与第一导电图案110s、110g和110p之间。

48.根据一些实施例,第二导电图案120s、120g和120p分别设置在第一导电图案110s、110g和110p上并耦接到第一导电图案110s、110g和110p。第二导电图案120s、120g和120p设置在第三介电层103中并在第三介电层103的顶表面上。第二导电图案120s、120g和120p包括第二信号图案120s、第二接地图案120g和第二电源图案120p。第二信号图案120s、第二接地图案120g和第二电源图案120p被电隔离并彼此横向地间隔开。第二导电图案120s、120g和120p中的每一个包括金属,例如,铜。

49.根据一些实施例,第二接地图案120g包括第二接地通孔部分121g和第二接地线图案122g。第二接地通孔部分121g包括设置在第三介电层103中并耦接到第一接地图案110g的下部。第二接地线图案122g设置在第三介电层103的顶表面上,并且第二接地线图案122g与第二接地通孔部分121g的上侧壁彼此一体地连接,而在它们之间没有边界。第二接地线图案122g的底表面位于比第二接地通孔部分121g的底表面更高的水平处。第二接地线图案122g在第一方向d1上延伸。

50.如图1f所示,根据一些实施例,第二接地线图案122g还在第二方向d2上延伸。例如,第二接地线图案122g具有板状。第二接地线图案122g在平面图中具有四边形形状。当第二接地线图案122g具有相对较大的平面面积时,第二接地线图案122g具有多个第二孔129。第二孔129中的每一个从第二接地线图案122g的顶表面穿透到底表面。另外,第四介电层104通过第二孔129直接接触第三介电层103。在平面图中,第二孔129防止第二导电图案120s、120g和120p集中在特定区域上。因此,重分布基板100具有提高的可靠性。第二接地线图案122g的平面布置和形状不限于图1f所示,并且在其他实施例中可以变化。

51.如图1b所示,根据一些实施例,第二接地线图案122g位于多个第一信号线图案112s上并在竖直方向上与其重叠。例如,多个第一信号线图案112s介于接地凸块下图案160g的顶表面和第二接地线图案122g的底表面之间。第二接地线图案122g的宽度大于对应的第一信号线图案112s的宽度。对应的第一信号线图案112s在竖直方向上与第二接地线图案122g重叠。第二接地线图案122g是下接地线图案。

52.根据一些实施例,第二信号图案120s包括通孔部分。第二信号图案120s包括设置在第三介电层103中并耦接到第一信号图案110s的下部。第二信号图案120s不包括线部分。因此,第二信号图案120s的顶表面处的宽度小于第二接地图案120g的顶表面处的宽度。如图1f所示,第二信号图案120s的平面面积小于第二接地图案120g的平面面积。第二信号图案120s的平面形状与第二接地图案120g的平面形状不同。例如,第二信号图案120s在平面图中具有圆形形状,但是本发明构思的实施例不限于此。

53.如图1a所示,根据一些实施例,第二电源图案120p包括第二电源通孔部分。第二电源图案120p的第二电源通孔部分具有设置在第三介电层103中并耦接到第一电源图案110p的下部。第二电源图案120p还包括第二电源线部分。

54.根据一些实施例,第二种子图案127介于第二导电图案120s、120g和120p中的每一个与第一导电图案110s、110g和110p的对应图案之间以及介于第二导电图案120s、120g和120p中的每一个与第三介电层103之间。第二种子图案127包括例如铜、钛或其合金。

55.根据一些实施例,第四介电层104设置在第三介电层103上,并且覆盖第二导电图案120s、120g和120p的侧壁和顶表面。第四介电层104包括例如光敏聚合物。第四介电层104包括与第三介电层103相同的材料。第三介电层103和第四介电层104之间具有模糊的边界。第二种子图案127不介于第四介电层104与第二导电图案120g、120g和120p之间。

56.根据一些实施例,第三导电图案130s、130g和130p分别设置在第二导电图案120s、120g和120p上并耦接到第二导电图案120s、120g和120p。第三导电图案130s、130g和130p设置在第四介电层104中或在第四介电层104上。第三导电图案130s、130g和130p包括第三信号图案130s、第三接地图案130g和第三电源图案130p。第三信号图案130s、第三接地图案130g和第三电源图案130p被电隔离并且彼此横向地间隔开。第三导电图案130s、130g和130p包括金属,例如,铜。

57.根据一些实施例,第三信号图案130s包括第三信号通孔部分131s和第三信号线图案132s。第三信号通孔部分131s具有设置在第四介电层104中并耦接到第二信号图案120s的下部。第三信号线图案132s设置在第四介电层104的顶表面上,并且第三信号线图案132s和第三信号通孔部分131s的上侧壁彼此一体地连接,而在它们之间没有边界。第三信号线图案132s是上信号线图案。第三信号线图案132s的底表面位于比第三信号通孔部分131s的

底表面更高的水平处。提供了多个第三信号图案130s。多个第三信号图案130s包括彼此横向地间隔开的第三信号线图案132s。第三信号线图案132s具有窄间距和小宽度,因此半导体封装1可以高度集成。例如,第三信号线图案132s中的每一个的宽度小于对应的第二接地线图案122g的宽度。对应的第二接地线图案122g在竖直方向上与第三信号线图案132s的底表面重叠。第三信号线图案132s具有与参照图1e描述的第一信号线图案112s类似的平面形状。

58.根据一些实施例,第二接地线图案122g介于第一信号线图案112s和第三信号线图案132s之间。第二接地线图案122g将第三信号线图案132s与第一信号线图案112s电屏蔽。可以防止第一信号线图案112s和第三信号线图案132s之间的电干扰。半导体封装1具有提高的操作可靠性。

59.根据一些实施例,第三接地图案130g包括通孔部分,但是不包括线部分。第三接地图案130g具有设置在第四介电层104中并耦接到第二接地图案120g的下部。第三接地图案130g具有与参照图1e描述的第一接地图案110g类似的平面形状。

60.根据一些实施例,第三电源图案130p包括通孔部分,但是不包括线部分。第三电源图案130p具有设置在第四介电层104中并耦接到第二电源图案120p的下部。

61.根据一些实施例,第三种子图案137介于第三导电图案130s、130g和130p中的每一个与第二导电图案120s、120g和120p中的对应图案之间以及介于第三导电图案130s、130g和130p中的每一个与第三介电层103之间。第三种子图案137包括例如铜、钛或其合金。

62.根据一些实施例,第五介电层105设置在第四介电层104上,并且覆盖第三导电图案130s、130g和130p的侧壁和顶表面。第五介电层105包括例如光敏聚合物。第五介电层105包括与第四介电层104相同的材料。第四介电层104和第五介电层105之间具有模糊的边界。第三种子图案137不介于第五介电层105与第三导电图案130g、130g和130p之间。

63.根据一些实施例,第四导电图案140s、140g和140p分别设置在第三导电图案130s、130g和130p上并耦接到第三导电图案130s、130g和130p。第四导电图案140s、140g和140p设置在第五介电层105中和在第五介电层105的顶表面上。第四导电图案140s、140g和140p包括第四信号图案140s、第四接地图案140g和第四电源图案140p。第四信号图案140s、第四接地图案140g和第四电源图案140p被电隔离并且彼此横向地间隔开。第四导电图案140s、140g和140p中的每一个包括金属,例如,铜。

64.根据一些实施例,第四接地图案140g包括第四接地通孔部分141g和第四接地线图案142g。第四接地通孔部分141g具有设置在第四介电层104中并耦接到第三接地图案130g的下部。第四接地线图案142g设置在第五介电层105的顶表面上,并且第四接地线图案142g和第四接地通孔部分141g的上侧壁彼此一体地连接,而在它们之间没有边界。第四接地线图案142g的底表面位于比第四接地通孔部分141g的底表面更高的水平处。第四接地线图案142g在第一方向d1上延伸。第四接地线图案142g具有与参照图1f描述的第二接地线图案122g类似的平面形状。

65.根据一些实施例,第四接地线图案142g在竖直方向上与多个第三信号线图案132s重叠。例如,多个第三信号线图案132s介于第四接地线图案142g的底表面和第二接地线图案122g的顶表面之间。第四接地线图案142g的顶表面处的宽度大于对应的第三信号线图案132s中的每一个的顶表面处的宽度。对应的第三信号线图案132s在竖直方向上与第四接地

线图案142g重叠。第四接地线图案142g是上接地线图案。

66.根据一些实施例,第四信号图案140s包括通孔部分。第四信号图案140s具有设置在第五介电层105中并耦接到第三信号图案130s的下部。第四信号图案140s不包括线部分。因此,第四信号图案140s的顶表面处的宽度小于第四接地图案140g的顶表面处的宽度。第四信号图案140s的顶表面的平面面积小于第四接地图案140g的顶表面的平面面积。第四信号图案140s的平面布置和形状与参考图1f描述的第二信号图案120s的平面布置和形状类似。例如,第四信号图案140s在平面图中具有圆形形状。

67.根据一些实施例,第四电源图案140p包括第四电源通孔部分。第四电源图案140p的第四电源通孔部分设置在第五介电层105中,并且耦接到第三电源图案130p,但是本发明构思的实施例不限于此。第四电源图案140p还包括第四电源线图案。第四电源线图案具有与参照图1f描述的第二接地线图案122g类似的平面形状。

68.根据一些实施例,第四种子图案147介于第四导电图案140s、140g和140p中的每一个与第三导电图案130s、130g和130p的对应图案之间以及介于第四导电图案140s、140g和140p中的每一个与第五介电层105之间。第四种子图案147包括例如铜、钛或其合金。

69.根据一些实施例,第六介电层106设置在第五介电层105上,并且覆盖第四导电图案140s、140g和140p的侧壁和顶表面。第六介电层106包括例如光敏聚合物。第六介电层106包括与第五介电层105相同的材料。第五介电层105和第六介电层106之间具有模糊的边界。第四种子图案147不介于第六介电层106与第四导电图案140s、140g和140p之间。

70.根据一些实施例,接合焊盘150设置在第六介电层106中和在第六介电层106的顶表面上。接合焊盘150包括信号接合焊盘150s、接地接合焊盘150g和电源接合焊盘150p。信号接合焊盘150s、接地接合焊盘150g和电源接合焊盘150p彼此电隔离并且彼此横向地间隔开。信号接合焊盘150s、接地接合焊盘150g和电源接合焊盘150p分别设置在第四信号图案140s、第四接地图案140g和第四电源图案140p上并与其耦接。接合焊盘150具有设置在第六介电层106中的下部。接合焊盘150具有设置在第六介电层106的顶表面上的上部。每个接合焊盘150的上部的宽度大于每个接合焊盘150的下部的宽度。接合焊盘150包括导电材料,例如,铜。接合焊盘150中的每一个还包括与第一导电图案110s、110g和110p、第二导电图案120s、120g和120p、第三导电图案130s、130g和130p以及第四导电图案140s、140g和140p的材料不同的材料。例如,接合焊盘150中的每一个包括多个堆叠层,并且接合焊盘150中的每一个的最上层包括金或镍。

71.根据一些实施例,焊盘种子图案157介于第六介电层106和接合焊盘150中的每一个之间。焊盘种子图案157中的每一个介于接合焊盘150的对应焊盘与第四导电图案140s、140g和140p的对应图案之间。焊盘种子图案157彼此间隔开并且彼此电隔离。焊盘种子图案157包括例如铜、钛或其合金。

72.根据一些实施例,第四导电图案140s、140g和140p对应于最上面的线图案。例如,第四导电图案140s、140g和140p直接接触对应的焊盘种子图案157。第四导电图案140s、140g和140p设置在对应的接合焊盘150的底表面上,并耦接到对应的接合焊盘150。

73.当将上线图案用作信号线时,信号线和外部器件之间可能会发生电干扰。根据一些实施例,第四导电图案140s、140g和140p均包括第四接地图案142g,并且第四信号图案140s不包括线部分。第四接地线图案142g对应于重分布基板100的最上面的接地线图案,并

且第三信号线图案132s对应于最上面的信号线。第四接地线图案142g设置在第三信号线图案132s的顶表面上,并且在竖直方向上与第三信号线图案132s重叠。因此,可以防止第三信号线图案132s与外部电子器件之间的电干扰。半导体封装1具有提高的操作可靠性。

74.根据一些实施例,如图1b所示,凸块下图案160中的每一个具有相对较大的厚度t0。例如,凸块下图案160的厚度t0大于第一信号线图案112s的厚度t1、第二接地线图案122g的厚度t2、第三信号线图案132s的厚度t3以及第四接地线图案142g的厚度t4。凸块下图案160满足上述条件,因此重分布基板100具有提高的可靠性。当凸块下图案160的厚度t0小于约5μm时,半导体封装1的可靠性降低。当凸块下图案160的厚度t0大于约20μm时,半导体封装1变得太大。根据一些实施例,凸块下图案160的厚度t0在约5μm至约20μm的范围内。半导体封装1具有提高的可靠性和减小的厚度。

75.当凸块下图案160在其上部和下部具有相同的宽度时,凸块下图案160的厚度t0可以在第一介电层101的顶表面中引起起伏。在这种情况下,多个第一导电图案110s、110g和110p的顶表面可以处于不同的水平。同样,第二介电层102和第三介电层103中的每一个可以在其顶表面中具有起伏。在这种情况下,多个第二导电图案120s、120g和120p可以使其顶表面处于明显不同的水平。多个第三导电图案130s、130g和130p可以使其顶表面处于明显不同的水平。多个第四导电图案140s、140g和140p可以使其顶表面处于明显不同的水平。第一导电图案110s、110g和110p、第二导电图案120s、120g和120p、第三导电图案130s、130g和130p以及第四导电图案140s、140g和140p之间的不良电连接可能是由第一导电图案110s、110g和110p的顶部表面之间、第二导电图案120s、120g和120p的顶表面之间、第三导电图案130s、130g和130p的顶表面之间或第四导电图案140s、140g和140p的顶表面之间的水平差引起的。第一导电图案110s、110g和110p、第二导电图案120s、120g和120p、第三导电图案130s、130g和130p以及第四导电图案140s、140g和140p的任意两个竖直相邻的图案之间可能发生不良的电连接。

76.根据一些实施例,因为凸块下图案160的第二部分162的宽度大于凸块下图案160的第一部分161处的宽度,所以可以减少或防止第一导电图案110s、110g和110p的顶表面之间、第二导电图案120s、120g和120p的顶表面之间、第三导电图案130s、130g和130p的顶表面之间或第四导电图案140s、140g和140p的顶表面之间的起伏。因此,可以在第一导电图案110s、110g和110p、第二导电图案120s、120g和120p、第三导电图案130s、130g和130p以及第四导电图案140s、140g和140p之间提供良好的电连接。

77.对堆叠的介电层101、102、103、104、105和106的数量以及导电图案110s、110g、110p、120s、120g、120p、130s、130g、130p、140s、140g和140p的数量没有限制,并且该数量在其他实施例中可以变化。另外,重分布基板100还可以包括覆盖第六介电层106和接合焊盘150的上钝化层。重分布基板100还可以包括覆盖第一介电层101的底表面101b的下钝化层。

78.根据一些实施例,半导体芯片200被安装在重分布基板100的第一表面上。半导体芯片200包括芯片焊盘205和集成电路。芯片焊盘205暴露在半导体芯片200的底表面上。集成电路设置在半导体芯片200中。集成电路可以包括存储器电路、逻辑电路或其组合。集成电路通过内部连接线电连接到芯片焊盘205。短语“特定组件被连接到芯片焊盘205”是指该特定组件耦接到半导体芯片200。短语“特定组件耦接到半导体芯片200”是指该特定组件耦接到半导体芯片200的集成电路。芯片焊盘205包括信号芯片焊盘205s、接地芯片焊盘205g

和电源芯片焊盘205p。信号芯片焊盘205s、接地芯片焊盘205g和电源芯片焊盘205p彼此横向地间隔开并且彼此电隔离。

79.根据一些实施例,接合凸块250被相应地设置在半导体芯片200的芯片焊盘205和重分布基板100的接合焊盘150之间并且电连接到半导体芯片200的芯片焊盘205和重分布基板100的接合焊盘150。接合凸块250包括凸块、焊料或柱中的一个或多个。接合凸块250包括导电材料,例如,焊接材料。半导体芯片200通过接合凸块250电连接到重分布基板100。在本说明书中,短语“电连接到重分布基板100”是指“电连接到第一导电图案110s、110g和110p、第二导电图案120s、120g和120p、第三导电图案130s、130g和130p以及第四导电图案140s、140g和140p中的一个或多个”。接合凸块250之间的间距小于焊接图案500的间距。

80.根据一些实施例,半导体封装1还包括模制层400。模制层400设置在重分布基板100上,并且覆盖半导体芯片200。模制层400覆盖介电层101、102、103、104、105和106的最上层。最上面的介电层是第六介电层106。模制层400还向半导体芯片200和重分布基板100之间的间隙延伸,并且封装接合凸块250。模制层400包括介电聚合物,例如,环氧模制化合物。在一些实施例中,底部填充层还介于重分布基板100和半导体芯片200之间。

81.图1g是图1a中的部分ii的放大图,其示出了根据一些实施例的凸块下种子图案和凸块下图案。

82.参照图1g,根据一些实施例,凸块下种子图案170的最下表面170b位于与凸块下图案160的底表面160b基本相同的水平处。凸块下种子图案170的最下表面170b位于比第一介电层101的底表面101b更高的水平处。凸块下种子图案170的最下表面170b和第一介电层101的底表面101b之间具有与第一厚度t11基本相同的水平差。

83.现在将在下面描述根据一些实施例的制造半导体封装的方法。

84.图2a至图2n示出了根据一些实施例的制造半导体封装的方法的截面图。下面将省略对上述元件的重复描述。

85.参照图2a,根据一些实施例,制备载体基板900和释放层990。释放层990附接到载体基板900。在载体基板900上形成第一介电层101、凸块下种子层170z和第一抗蚀剂图案981。释放层990还介于载体基板900和第一介电层101之间以及介于载体基板900和凸块下种子层170z之间。第一介电层101和凸块下种子层170z通过释放层990附接到载体基板900。

86.根据一些实施例,第一介电层101的形成包括涂覆光敏聚合物以形成初步介电层,以及在初步介电层上执行曝光工艺和显影工艺。作为曝光工艺和显影工艺的结果,在第一介电层101中形成第一开口101a。第一开口101a暴露释放层990的顶表面和第一介电层101的内壁。

87.根据一些实施例,凸块下种子层170z形成在载体基板900上,并覆盖第一介电层101和释放层990的被暴露的顶表面。例如,凸块下种子层170z共形地覆盖第一介电层101的顶表面和内壁。可以通过沉积工艺来形成凸块下种子层170z。

88.根据一些实施例,第一抗蚀剂图案981形成在第一介电层101的顶表面上并覆盖凸块下种子层170z。第一引导开口981g形成在第一抗蚀剂图案981中,并暴露凸块下种子层170z。第一引导开口981g在竖直方向上与对应的第一开口101a重叠。第一引导开口981g比对应的第一开口101a宽。

89.参照图2b,根据一些实施例,凸块下图案160对应地形成在第一开口101a和第一引

导开口981g中,并覆盖凸块下种子层170z。可以通过执行将凸块下种子层170z用作电极的电镀工艺来形成凸块下图案160。电镀工艺在凸块下图案160延伸到第一抗蚀剂图案981的顶表面上之前终止。因此,不需要单独的平坦化工艺来形成凸块下图案160。

90.根据一些实施例,凸块下图案160中的每一个包括第一部分161和第二部分162。凸块下图案160的第一部分161形成在对应的第一开口101a中,并且凸块下图案160的第二部分162形成在对应的第一引导开口981g中。因为第一引导开口981g比第一开口101a宽,所以凸块下图案160的第二部分162比凸块下图案160的第一部分161宽。

91.根据一些实施例,当凸块下图案160形成为单层时,形成厚的凸块下图案160可能具有挑战性。根据一些实施例,凸块下种子层170z延伸到第一介电层101的顶表面上,并且凸块下图案160形成在第一开口101a和第一引导开口981g中的凸块下种子层170z上。因此,可以容易地形成厚的凸块下图案160。例如,凸块下图案160的厚度t0在约5μm至约20μm的范围内。

92.根据一些实施例,凸块下图案160包括信号凸块下图案160s、接地凸块下图案160g和电源凸块下图案160p。第一抗蚀剂图案981用于形成凸块下图案160s、160g和160p,并且因此不需要单独的蚀刻工艺来将信号凸块下图案160s、接地凸块下图案160g和电源凸块下图案160p彼此横向地分离。因此,简化了半导体封装的制造工艺。

93.参照图2c,根据一些实施例,去除第一抗蚀剂图案981以暴露凸块下种子层170z的第一部分的顶表面和凸块下图案160的第二部分162的侧壁。可以执行剥离工艺以去除第一抗蚀剂图案981。

94.依次参照图2c和图2d,根据一些实施例,对凸块下种子层170z进行图案化以形成多个凸块下种子图案170。凸块下种子层170z的图案化包括执行蚀刻工艺以蚀刻凸块下种子层170z的被暴露的第一部分。因此,去除凸块下种子层170z的第一部分以暴露第一介电层101的顶表面。在蚀刻工艺中,凸块下图案160相对于凸块下种子层170z具有蚀刻选择性。凸块下种子层170z具有被凸块下图案160相应地覆盖的第二部分。因此,凸块下种子层170z的第二部分未通过蚀刻工艺去除。在蚀刻工艺之后,凸块下种子层170z的其余第二部分是对应的凸块下种子图案170。凸块下种子图案170彼此间隔开并且彼此电隔离。

95.参照图2e,根据一些实施例,第二介电层102形成在第一介电层101和凸块下图案160上,并覆盖凸块下图案160的第二部分162的顶表面和侧壁。可以通过涂覆工艺(例如,旋涂或狭缝涂覆)来形成第二介电层102。

96.根据一些实施例,对第二介电层102进行图案化以在第二介电层102中形成第二开口102a。第二介电层102的图案化可以通过曝光工艺和显影工艺来执行。第二开口102a暴露凸块下图案160的对应的顶表面。

97.参照图2f,根据一些实施例,在第一介电层101上形成第一种子层117z、第二抗蚀剂图案982以及第一导电图案110s、110g和110p。第一种子层117z形成在第二介电层102上和在第二开口102a中。第一种子层117z共形地覆盖第二介电层102的顶表面、第二介电层102的内壁以及凸块下图案160的被暴露的顶表面。

98.根据一些实施例,第二抗蚀剂图案982形成在第一种子层117z上。第二抗蚀剂图案982的形成包括在第一种子层117z上涂覆光致抗蚀剂材料。对第二抗蚀剂图案982进行图案化以形成第二引导开口982g。第二抗蚀剂图案982的图案化包括曝光工艺和显影工艺。第二

引导开口982g在空间上连接到对应的第二开口102a。第二引导开口982g比对应的第二开口102a宽。第二引导开口982g中的每一个暴露第一种子层117z。

99.根据一些实施例,第一导电图案110s、110g和110p形成在对应的第二开口102a中,并且覆盖第一种子层117z。例如,第一导电图案110s、110g和110p填充对应的第二开口102a。第一导电图案110s、110g和110p填充对应的第二引导开口982g的下部,但是不延伸到第二抗蚀剂图案982的顶表面上。第一导电图案110s、110g和110p通过电镀工艺形成,其中,第一种子层117z用作电极。不需要单独的平坦化工艺来形成第一导电图案110s、110g和110p。

100.根据一些实施例,第一导电图案110s、110g和110p包括第一信号图案110s、第一接地图案110g和第一电源图案110p。第一信号图案110s、第一接地图案110g和第一电源图案110p彼此分离。例如,第一信号图案110s、第一接地图案110g和第一电源图案110p彼此横向地间隔开。第二抗蚀剂图案982用于形成第一导电图案110s、110g和110p,因此不需要附加的蚀刻工艺以将第一信号图案110s、第一接地图案110g和第一电源图案110p彼此横向地分离。因此,简化了第一导电图案110s、110g和110p的形成。

101.根据一些实施例,由于凸块下图案160的第二部分162相对较宽,因此可以形成第二介电层102和第一导电图案110s、110g和110p,而在其顶表面处没有起伏或在其顶表面处具有减少的起伏。

102.参照图2g,根据一些实施例,去除第二抗蚀剂图案982以暴露第一种子层117z的第一部分的顶表面。剥离工艺可以去除第二抗蚀剂图案982。

103.参照图2h,根据一些实施例,去除第一种子层117z的被暴露的第一部分以形成第一种子图案117。蚀刻工艺去除第一种子层117z的第一部分。蚀刻工艺可以是湿法蚀刻工艺。在蚀刻工艺中,第一导电图案110s、110g和110p相对于第一种子层117z具有蚀刻选择性。第一种子层117z具有被第一导电图案110s、110g和110p覆盖并且不暴露于蚀刻工艺的第二部分。在蚀刻工艺终止之后,第一种子层117z的其余第二部分是多个第一种子图案117。多个第一种子图案117彼此分离。

104.参照图2i,根据一些实施例,在第二介电层102上形成第三介电层103、第二种子图案127以及第二导电图案120s、120g和120p。通过与参照图2e至图2h描述的用于形成第二介电层102、第一种子图案117以及第一导电图案110s、110g和110p相同的方法形成第三介电层103、第二种子图案127以及第二导电图案120s,120g和120p。

105.例如,根据一些实施例,第三介电层103形成在第二介电层102上,并且覆盖第二介电层102和第一导电图案110s、110g和110p。由于凸块下图案160中的每一个包括第二部分162,所以第三介电层103在其顶表面处没有起伏或具有减少的起伏。可以通过涂覆工艺形成第三介电层103。

106.根据一些实施例,对第三介电层103进行图案化以在第三介电层103中形成第三开口。第三开口暴露第一导电图案110s、110g和110p的顶表面。

107.根据一些实施例,第二种子图案127以及第二导电图案120s、120g和120p的形成包括:在第三开口中和在第三介电层103的顶表面上形成第二种子层;在第二种子层上形成具有第三引导开口的第三抗蚀剂图案;执行将第二种子层用作电极的电镀工艺;去除第三抗蚀剂图案以暴露第二种子层的一部分;然后蚀刻第二种子层的暴露部分。

108.根据一些实施例,电镀工艺在第三开口和第三引导开口中形成第二导电图案120s、120g和120p。第二导电图案120s、120g和120p包括第二信号图案120s、第二接地图案120g和第二电源图案120p。第二信号图案120s、第二接地图案120g和第二电源图案120p彼此分离。

109.根据一些实施例,蚀刻第二种子层以形成多个第二种子图案127。第二种子图案127彼此分离。

110.参照图2j,根据一些实施例,在第三介电层103上形成第四介电层104、第三种子图案137以及第三导电图案130s、130g和130p。通过与参照图2e至图2h描述的用于形成第二介电层102、第一种子图案117以及第一导电图案110s、110g和110p相同的方法形成第四介电层104、第三种子图案137以及第三导电图案130s、130g和130p。

111.根据一些实施例,第五介电层105形成在第四介电层104上,并且覆盖第四介电层104以及第三导电图案130s、130g和130p。对第五介电层105进行图案化以在第五介电层105中形成第四开口。第四开口暴露第三导电图案130s、130g和130p的顶表面。

112.根据一些实施例,由于凸块下图案160中的每一个包括第二部分162,所以第四介电层104和第五介电层105中的每一个在其顶表面处没有起伏或具有减少的起伏。

113.参照图2k,根据一些实施例,在第五介电层105上形成第四种子图案147、第四导电图案140s、140g和140p以及第六介电层106。通过与参照图2f至图2h描述的用于形成第一种子图案117和第导电图案110s、110g和110p相同的方法形成第四种子图案147和第四导电图案140s、140g和140p。通过与参照图2e描述的用于形成第二介电层102基本相同的方法来形成第六介电层106。第六介电层106具有暴露第四导电图案140s、140g和140p的对应的顶表面的孔。由于凸块下图案160中的每一个包括第二部分162,所以第六介电层106在其顶表面处没有起伏或具有减少的起伏。

114.根据一些实施例,焊盘种子图案157和接合焊盘150形成在第六介电层106中和在第六介电层106上。通过与参照图2f至图2h描述的用于形成第一种子图案117和第一导电图案110s、110g和110p基本相同的方法形成焊盘种子图案157和接合焊盘150。

115.例如,根据一些实施例,焊盘种子图案157和接合焊盘150的形成包括:在第六介电层106上形成焊盘种子层;在焊盘种子层上形成具有引导开口的抗蚀剂图案;执行将焊盘种子层用作电极的电镀工艺;去除抗蚀剂图案以暴露焊盘种子层的一部分;然后蚀刻焊盘种子层的暴露部分。蚀刻焊盘种子层以形成多个焊盘种子图案157。多个焊盘种子图案157彼此分离。

116.根据一些实施例,电镀工艺在孔和引导开口中形成接合焊盘150。接合焊盘150包括信号接合焊盘150s、接地接合焊盘150g和电源接合焊盘150p。信号接合焊盘150s、接地接合焊盘150g和电源接合焊盘150p彼此分离。之后,去除抗蚀剂图案以暴露第六介电层106的顶表面。通过上述过程,可以制造重分布基板100。

117.参照图2l,根据一些实施例,制备包括多个芯片焊盘205的半导体芯片200。半导体芯片200设置在第六介电层106上,以允许芯片焊盘205与对应的接合焊盘150对准。在半导体芯片200和重分布基板100之间形成多个接合凸块250。接合凸块250耦接到对应的芯片焊盘205和接合焊盘150。

118.根据一些实施例,模制层400形成在第六介电层106上,并包封半导体芯片200。模

制层400还延伸到第六介电层106和半导体芯片200之间的间隙中,从而包封接合凸块250。

119.根据其他实施例,在第六介电层106和半导体芯片200之间还形成底部填充层。

120.参照图2m,根据一些实施例,从第一介电层101去除释放层990和载体基板900以暴露第一介电层101的底表面101b和凸块下种子图案170的底表面。物理方法可以用于去除释放层990和载体基板900。

121.参照图2n,根据一些实施例,凸块下种子图案170中的每一个被部分地去除以暴露凸块下图案160的底表面160b。蚀刻工艺部分地去除凸块下种子图案170。蚀刻工艺可以是湿法蚀刻工艺。在蚀刻工艺中,凸块下图案160和第一介电层101均相对于凸块下种子图案170具有蚀刻选择性。因此,在蚀刻工艺终止之后,保留了凸块下图案160和第一介电层101。

122.根据一些实施例,部分去除凸块下种子图案170使得凸块下图案160的底表面160b位于比第一介电层101的底表面101b更低的水平处。凸块下图案160的底表面160b和第一介电层101的底表面101b之间的水平差与凸块下种子图案170中的每一个的第一厚度t11(见图1c)基本相同。

123.在蚀刻工艺之后,根据一些实施例,每个凸块下种子图案170具有咬边(undercut)。凸块下种子图案170的咬边形成在第一介电层101和对应的凸块下图案160的第一部分161之间。因此,如图1c所示,凸块下种子图案170的最下表面170b位于比凸块下图案160的底表面160b低的水平处。

124.在一些实施例中,可以调整蚀刻工艺的条件,使得如参考图1g所述,凸块下种子图案170的最下表面170b位于与凸块下图案160的底表面160b基本相同的水平处。

125.返回参照图1a和图1b,根据一些实施例,焊接图案500形成在凸块下图案160的对应的被暴露的底表面160b上。焊接图案500的形成包括焊料球附接过程。

126.根据一些实施例,焊接图案500和凸块下种子图案170之间的粘合力相对较小。例如,焊接图案500和凸块下种子图案170之间的粘合力小于焊接图案500和凸块下图案160之间的粘合力。根据一些实施例,因为在部分去除凸块下种子图案170之后在凸块下图案160上形成焊接图案500,所以焊接图案500可以直接接触凸块下图案160。焊接图案500牢固地接合到凸块下图案160。通过上述过程,制造半导体封装1。

127.为了简化描述,已经示出并描述了单个半导体封装1,但是制造半导体封装1的方法不限于芯片级制造。例如,可以在芯片、面板或晶片级上制造半导体封装1。

128.图3是根据一些实施例的半导体封装的截面图。下面将省略对上述元件的重复描述。

129.参照图3,根据一些实施例,半导体封装2包括重分布基板100’、焊接图案500、半导体芯片200和模制层400。焊接图案500、半导体芯片200和模制层400与参照图1a至图1g描述的那些基本相同。相反,半导体封装2不包括接合凸块250。

130.根据一些实施例,重分布基板100’包括:第一介电层101、第二介电层102、第三介电层103、第四介电层104、第五介电层105和第六介电层106;第一导电图案110s、110g和110p、第二导电图案120s、120g和120p、第三导电图案130s、130g和130p以及第四导电图案140s、140g和140p;第一种子图案117、第二种子图案127、第三种子图案137和第四种子图案147;凸块下种子图案170和凸块下图案160。第一介电层101、第二介电层102、第三介电层103、第四介电层104、第五介电层105和第六介电层106,以及第一导电图案110s、110g和

110p、第二导电图案120s、120g和120p、第三导电图案130s、130g和130p以及第四导电图案140s、140g和140p与参照图1a至图1g描述的那些类似。相反,重分布基板100’不包括图1b所示的接合焊盘150,并且半导体芯片200直接物理地接触重分布基板100’的第一表面100a。例如,第六介电层106直接物理地接触半导体芯片200的底表面。第四导电图案140s、140g和140p在没有接合焊盘的情况下电连接到半导体芯片200的芯片焊盘205。例如,第四种子图案147介于对应的芯片焊盘205和对应的第四导电图案140g、140g和140p之间并与对应的芯片焊盘205和对应的第四导电图案140g、140g和140p直接接触。第四信号图案140s、第四接地图案140g和第四电源图案140p通过第四种子图案147耦接到信号芯片焊盘205s、接地芯片焊盘205g和电源芯片焊盘205p。

131.与参照图1a和图1b描述的实施例相反,第一导电图案110s、110g和110p、第二导电图案120s、120g和120p、第三导电图案130s、130g和130p以及第四导电图案140s、140g和140p中的每一个在其顶表面处的宽度小于在其底表面处的宽度。在平面图中,第一信号图案110s和第一接地图案110g的底表面形状和其布置与参照图1e描述的第一信号图案110s和第一接地图案110g的顶表面形状和布置类似。在平面图中,第二信号图案120s和第二接地图案120g的底表面形状和布置与参照图1f描述的第二信号图案120s和第二接地图案120g的顶表面形状和布置类似。

132.根据一些实施例,第一种子图案117设置在第一导电图案110s、110g和110p的对应的顶表面上。例如,第一种子图案117介于第一导电图案110s、110g和110p与第三介电层103之间以及介于第一导电图案110s、110g和110p与第二导电图案120s、120g和120p之间。第二种子图案127设置在第二导电图案120s、120g和120p的对应的顶表面上。第三种子图案137设置在第三导电图案130s、130g和130p的对应的顶表面上。第四种子图案147设置在第四导电图案140s、140g和140p的对应的顶表面上。

133.根据一些实施例,凸块下图案160与参照图1a、图1b和图1d描述的那些基本相同。例如,凸块下图案160中的每一个在其第一部分161处的宽度小于在其第二部分162处的宽度。相反,凸块下图案160的第一部分161对应于凸块下图案160的上部。例如,凸块下图案160的第一部分161设置在凸块下图案160的第二部分162上。凸块下图案160的第一部分161介于凸块下图案160的第二部分162与第一导电图案110s、110g和110p的对应图案之间。焊接图案500中的每一个附接到凸块下图案160的第二部分162的底表面。凸块下图案160的第二部分162用作焊接盘。凸块下图案160包括信号凸块下图案160s、接地凸块下图案160g和电源凸块下图案160p。如上所述,接地凸块下图案160g和电源凸块下图案160p均用作布线或线部分。例如,多个第一信号图案110s包括位于单个接地凸块下图案160g的第二部分162上并在竖直方向上与所述第二部分162重叠的多个第一信号线图案。凸块下种子图案170介于凸块下图案160和第二介电层102之间。凸块下种子图案170覆盖凸块下图案160的第一部分161的顶表面和侧壁,并且还覆盖凸块下图案160的第二部分162的顶表面。凸块下种子图案170未设置在凸块下图案160的底表面上。

134.图4是根据一些实施例的半导体封装的截面图。

135.参照图4,根据一些实施例,半导体封装3包括封装基板800、重分布基板100、焊接图案500、第一半导体芯片210、芯片叠层2000、接合凸块250和模制层400。

136.根据一些实施例,封装基板800包括印刷电路板。封装基板800包括金属线820和金

属焊盘810。金属线820设置在封装基板800中。在本说明书中,短语“耦接到封装基板800”是指“耦接到金属线820”。金属焊盘810设置在封装基板800的顶表面上,并且电连接到金属线820。外部耦接端子850设置在封装基板800的底表面上,并且耦接到对应的金属线820。外部电信号可以通过外部耦接端子850传输到金属线820。焊球可以用作外部耦接端子850。外部耦接端子850包括金属,例如,焊接材料。

137.根据一些实施例,重分布基板100设置在封装基板800上。重分布基板100用作内插基板。焊接图案500与封装基板800的对应的金属焊盘810对准。重分布基板100通过焊接图案500电连接到封装基板800。重分布基板100、焊接图案500和模制层400与参照图1a至图1g描述的那些基本相同。接合凸块250包括第一接合凸块251和第二接合凸块252。

138.根据一些实施例,第一半导体芯片210安装在重分布基板100的顶表面上。第一接合凸块251介于第一半导体芯片210的芯片焊盘215和接合焊盘150之间。第一半导体芯片210与参照图1a和图1b描述的半导体芯片200基本相同,并且第一接合凸块251的布置、功能和材料与参照图1a和图1b描述的接合凸块250的布置、功能和材料基本相同。第一接合凸块251的间距小于焊接图案500的间距。第一接合凸块251的间距小于外部耦接端子850的间距。

139.根据一些实施例,芯片堆叠2000安装在重分布基板100的顶表面上。芯片堆叠2000与第一半导体芯片210横向地间隔开。芯片堆叠2000包括多个第二半导体芯片220。第二半导体芯片220中的每一个与参照图1a和图1b描述的半导体芯片200相同或相似。相反,第二半导体芯片220具有与第一半导体芯片210不同的类型。例如,第一半导体芯片210可以是逻辑芯片、缓冲芯片或片上系统(soc)之一,并且第二半导体芯片220中的每一个可以是逻辑芯片、缓冲芯片或片上系统(soc)中的另一个。存储器芯片可以包括高带宽存储器(hbm)芯片。例如,最下面的第二半导体芯片220可以是逻辑芯片,而其余的第二半导体芯片220可以是高带宽存储器(hbm)芯片。第一半导体芯片210是与最下面的第二半导体芯片220不同类型的逻辑芯片。例如,最下面的第二半导体芯片220是控制器芯片,并且第一半导体芯片210是专用集成电路(asic)芯片或应用处理器(ap)芯片。asic芯片包括专用集成电路(asic)。

140.根据一些实施例,第二半导体芯片220中的每一个包括下焊盘225、贯通电极227和上焊盘226。下焊盘225和上焊盘226分别设置在第二半导体芯片220的底表面和顶表面上。下焊盘225和上焊盘226中的一个或多个电连接到第二半导体芯片220的集成电路。贯通电极227设置在第二半导体芯片220中,并且耦接到下焊盘225和上焊盘226。最上面的第二半导体芯片220包括下焊盘225,但是不包括贯通电极227或上焊盘226。然而,在其他实施例中,最上面的第二半导体芯片220还包括贯通电极227和上焊盘226。内插凸块229介于两个相邻的第二半导体芯片220之间,并且耦接到下焊盘225和上焊盘226。因此,多个第二半导体芯片220可以彼此电连接。内插凸块229可以包括焊料、柱或凸块。内插凸块229包括焊接材料,但是本发明构思的实施例不限于此。

141.根据其他实施例,省略了内插凸块229。在这种情况下,相邻的第二半导体芯片220通过彼此面对并直接彼此接合的下焊盘225和上焊盘226连接。

142.根据一些实施例,第二接合凸块252介于最下面的第二半导体芯片220和重分布基板100之间,并且耦接到下焊盘225和对应的接合焊盘150。因此,第二半导体芯片220可以通过重分布基板100电连接到第一半导体芯片210和焊接图案500。多个第二接合凸块252的布

置、功能和材料与参照图1a和图1b描述的接合凸块250的布置、功能和材料基本相同。第二接合凸块252的间距小于焊接图案500的间距以及外部耦接端子850的间距。

143.根据一些实施例,提供了多个芯片堆叠2000。多个芯片堆叠2000彼此横向地间隔开。第一半导体芯片210设置在芯片堆叠2000之间。因此,可以在第一半导体芯片210和芯片堆叠2000之间提供减少的电学路径。

144.根据一些实施例,第一底部填充层410设置在重分布基板100和第一半导体芯片210之间的第一间隙中,从而包封第一接合凸块251。第一底部填充层410包括介电聚合物,例如,基于环氧的聚合物。第二底部填充层420设置在重分布基板100和芯片堆叠2000之间的对应的第二间隙中,从而包封对应的第二接合凸块252。第二底部填充层420包括介电聚合物,例如,基于环氧的聚合物。然而,在其他实施例中,省略了第二底部填充层420,并且第一底部填充层410还延伸到第二间隙中,从而包封第一接合凸块251和第二接合凸块252。

145.根据一些实施例,第三底部填充层430介于第二半导体芯片220之间,从而包封内插凸块229。第三底部填充层430包括介电聚合物,例如,基于环氧的聚合物。

146.根据一些实施例,模制层400设置在重分布基板100上,并且覆盖第一半导体芯片210的侧壁和第二半导体芯片220的侧壁。模制层400暴露第一半导体芯片210的顶表面和最上面的第二半导体芯片220的顶表面。然而,在其他实施例中,模制层400覆盖第一半导体芯片210的顶表面和最上面的第二半导体芯片220的顶表面。在其他实施例中,省略了第一底部填充层410和第二底部填充层420,并且模制层400延伸到第一间隙和第二间隙中。

147.根据一些实施例,导电板770还设置在第一半导体芯片210的顶表面、芯片堆叠2000的顶表面和模制层400的顶表面上。导电板770还可以延伸到模制层400的侧壁上。导电板770保护第一半导体芯片210和芯片堆叠2000免受外部环境的影响。例如,导电板770可以吸收外部物理冲击。导电板770包括导热材料,并且用作散热器或散热块。例如,当半导体封装3操作时,导电板770向外部散发从重分布基板100、第一半导体芯片210或第二半导体芯片210产生的热。导电板770是导电的,并且用作电磁场屏蔽层。例如,导电板770屏蔽第一半导体芯片210和第二半导体芯片220之间的电磁干扰(emi)。导电板770通过重分布基板100电接地,并且防止第一半导体芯片210或第二半导体芯片220被静电放电(esd)电损坏。

148.另外,第三半导体芯片还可以安装在重分布基板100上。第三半导体芯片可以是与第一半导体芯片210和第二半导体芯片220不同的类型。此外,可以省略模制层400。

149.根据一些实施例,可以通过使用参照图3描述的重分布基板100

′

来制造半导体封装3。在这种情况下,可以从半导体封装3中省略接合凸块250、第一底部填充层410和第二底部填充层420。另外,重分布基板100’与第一半导体芯片210和第二半导体芯片220之间的布置关系与参照图3描述的重分布基板100’与半导体芯片200之间的布置关系基本相同。

150.图5是根据一些实施例的半导体封装的截面图。

151.参照图5,根据一些实施例,半导体封装4包括下半导体封装20和上半导体封装22。下半导体封装20包括重分布基板100、焊接图案500、接合凸块250、第一半导体芯片210a、第二下半导体芯片220a、模制层400和导电结构310。重分布基板100、焊接图案500和模制层400与参照图1a至图1g描述的那些基本相同。

152.根据一些实施例,第二下半导体芯片220a与第一下半导体芯片210a横向地间隔开。第二下半导体芯片220a具有与第一半导体芯片210a不同的类型。例如,第一下半导体芯

片210a可以是逻辑芯片、存储器芯片或电源管理芯片之一,并且第二下半导体芯片220a可以是逻辑芯片、存储器芯片或电源管理芯片中的另一个。逻辑芯片可以是专用集成电路(asic)芯片或应用处理器(ap)芯片。电力管理芯片可以是电力管理集成电路(pmic)。例如,第一下半导体芯片210a是asic芯片,并且第二下半导体芯片220a是电源管理芯片。第一下半导体芯片210a和第二下半导体芯片220a中的每一个与参照图1a和图1b描述的半导体芯片200类似。然而,在其他实施例中,省略了第一下半导体芯片210a和第二下半导体芯片220a中的一个或多个。在其他实施例中,第三半导体芯片还安装在重分布基板100的顶表面上。

153.根据一些实施例,接合凸块250包括第一接合凸块251a和第二接合凸块252a。第一接合凸块251a与参照图3描述的第一接合凸块251类似,并且第二接合凸块252a与参照图3描述的第二接合凸块252类似。第一下半导体芯片210a包括通过第一接合凸块251a电连接到重分布基板100的芯片焊盘215a。第二下半导体芯片220a包括通过第二接合凸块252a电连接到重分布基板100的芯片焊盘225a。因此,第二下半导体芯片220a可以通过重分布基板100电连接到第一下半导体芯片210a。

154.根据一些实施例,导电结构310设置在重分布基板100的顶表面上,并且耦接到对应的接合焊盘150。导电结构310与第一下半导体芯片210a和第二下半导体芯片220a横向地间隔开。在平面图中,导电结构310位于重分布基板100的边缘区域上。将金属柱设置在重分布基板100上,从而形成导电结构310。例如,导电结构310是金属柱。导电结构310与重分布基板100电连接。例如,导电结构310通过重分布基板100电连接到第一下半导体芯片210a、第二下半导体芯片220a或焊接图案500。导电结构310包括金属,例如,铜。

155.根据一些实施例,模制层400设置在重分布基板100的顶表面上,并且覆盖第一下半导体芯片210a和第二下半导体芯片220a。模制层400覆盖导电结构310的侧壁。模制层400具有与重分布基板100的侧壁对准的侧壁。模制层400暴露导电结构310的顶表面310a。

156.根据一些实施例,下半导体封装20还包括上重分布层600。上重分布层600设置在模制层400的顶表面上。上重分布层600包括上介电层610、上重分布图案620和上接合焊盘640。上介电层610堆叠在模制层400上。上介电层610包括光敏聚合物。上重分布图案620中的每一个包括上介电层610中的通孔部分和上介电层610之间的线部分。上重分布图案620包括金属,例如,铜。上重分布图案620中的至少一个接触导电结构310的顶表面310a。上接合焊盘640设置在上介电层610的最上层上,并且耦接到上重分布图案620。上接合焊盘640通过上重分布图案620和导电结构310电连接到焊接图案500、第一下半导体芯片210a或第二下半导体芯片220a。上重分布图案620的存在防止上接合焊盘640与导电结构310在竖直方向上对准。

157.备选地,在其他实施例中,通过使用参照图3描述的重分布基板100

′0′

来制造下半导体封装20。在这种情况下,省略了接合凸块250。另外,重分布基板100’与第一半导体芯片210a和第二半导体芯片220a之间的布置关系与参照图3描述的重分布基板100’与半导体芯片200之间的布置关系基本相同。

158.根据一些实施例,上半导体封装22设置在下半导体封装20上。例如,上半导体封装22被放置在上重分布层600上。上半导体封装22包括上基板710、上半导体芯片720和上模制层730。上基板710是印刷电路板。然而,在其他实施例中,上基板710是重分布层。可以与参

照图2a至图2k描述的重分布基板100相同或相似地制造上基板710。第一连接焊盘701和第二连接焊盘702分别设置在上基板710的底表面和顶表面上。布线703设置在上基板710中,该布线703与第一连接焊盘701和第二连接焊盘702耦接。布线703被示意性地示出,并且可以具有与所示的不同形状和布置。第一连接焊盘701、第二连接焊盘702和布线703包括导电材料,例如,金属。

159.根据一些实施例,上半导体芯片720设置在上基板710上。上半导体芯片720包括集成电路,该集成电路可以包括存储器电路、逻辑电路或其组合。上半导体芯片720具有与第一下半导体芯片210a和第二下半导体芯片220a不同的类型。例如,上半导体芯片720是存储芯片。凸块端子715介于上基板710和上半导体芯片720之间,并且耦接到第二连接焊盘702和上半导体芯片720的芯片焊盘725。上半导体芯片720通过凸块端子715和布线703电连接到第一连接焊盘701。然而,在其他实施例中,省略了凸块端子715,并且芯片焊盘725直接耦接到第二连接焊盘702。

160.根据一些实施例,上模制层730设置在上基板710上,并覆盖上半导体芯片720。上模制层730包括介电聚合物,例如,基于环氧的聚合物。

161.根据一些实施例,上半导体封装22还包括热辐射结构780。热辐射结构780包括散热器、散热块或热界面材料(tim)层中的一个或多个。热辐射结构780包括例如金属。热辐射结构780设置在上模制层730的顶表面上。热辐射结构780还可以延伸到上模制层730的侧壁或模制层400的侧壁上。

162.根据一些实施例,半导体封装4还包括连接端子650。连接端子650介于上接合焊盘640和第一连接焊盘701之间并耦接到上接合焊盘640和第一连接焊盘701。因此,上半导体封装22可以通过连接端子650电连接到第一半导体芯片210a、第二下半导体芯片220a和焊接图案500。上半导体封装22的电连接包括与上半导体芯片720中的集成电路的电连接。连接端子650可以是焊料、凸块或其组合。连接端子650包括焊料。

163.在其他实施例中,省略了上基板710,并且连接端子650直接耦接到上半导体芯片720的芯片焊盘725。在这种情况下,上模制层730与上重分布层600的顶表面直接接触。在其他实施例中,省略了上基板710和连接端子650,并且上半导体芯片720的芯片焊盘725直接耦接到上接合焊盘640。

164.图6是根据一些实施例的半导体封装的截面图。

165.参照图6,根据一些实施例,半导体封装5包括下半导体封装21和上半导体封装22。下半导体封装21包括重分布基板100、焊接图案500、接合凸块250、第一下半导体芯片210a、第二下半导体芯片220a、模制层400和连接基板300。重分布基板100、焊接图案500、接合凸块250和模制层400与参照图1a至图1g描述的那些相同或相似。第一下半导体芯片210a和第二下半导体芯片220a分别与参照图5描述的第一下半导体芯片210a和第二下半导体芯片220a基本相同。接合凸块250包括第一接合凸块251a和第二接合凸块252a。第一接合凸块251a和第二接合凸块252a分别与参照图5描述的第一接合凸块251a和第二接合凸块252a基本相同。

166.根据一些实施例,半导体封装5还包括第一底部填充图案411和第二底部填充图案421。第一底部填充图案411设置在重分布基板100和第一下半导体芯片210a之间的第一间隙中。第一底部填充图案411包封第一接合凸块251a。第二底部填充图案421设置在重分布

基板100和第二下半导体芯片220a之间的第二间隙中,从而包封第二接合凸块252a。

167.根据一些实施例,连接基板300设置在重分布基板100上。连接基板300包括贯穿其中的基板孔390。例如,可以通过制备印刷电路板并形成贯穿印刷电路板的顶表面和底表面的基板孔390来执行连接基板300的形成。在平面图中,基板孔390形成在重分布基板100的中央部分上。第一下半导体芯片210a和第二下半导体芯片220a设置在连接基板300的基板孔390中。第一下半导体芯片210a和第二下半导体芯片220a与连接基板300的内壁间隔开。

168.根据一些实施例,连接基板300包括基层320和导电结构310。另外,基层320包括多个堆叠的层。基层320包括介电材料。例如,基层320可以包括碳基材料、陶瓷或聚合物中的至少一种。基板孔390贯穿基层320。导电结构310设置在基层320中。连接基板300还包括第一焊盘311和第二焊盘312。第一焊盘311设置在导电结构310的底表面上。第二焊盘312设置在导电结构310的顶表面上。第二焊盘312通过导电结构310电连接到第一焊盘311。导电结构310、第一焊盘311和第二焊盘312包括例如铜、铝、钨、钛、钽、铁或其任何合金中的至少一种。

169.根据一些实施例,连接凸块255设置在重分布基板100和连接基板300之间。连接凸块255介于第一焊盘311和对应的接合焊盘150之间并耦接到第一焊盘311和对应的接合焊盘150。导电结构310通过连接凸块255电连接到重分布基板100。连接凸块255包括焊球、凸块或柱中的一个或多个。连接凸块255包括金属。第三底部填充图案431设置在重分布基板100和连接基板300之间的间隙中,从而包封连接凸块255。第三底部填充图案431包括介电聚合物。

170.根据一些实施例,模制层400设置在第一下半导体芯片210a、第二下半导体芯片220a和连接基板300上。模制层400介于第一下半导体芯片210a和第二下半导体芯片220a之间、介于第一下半导体芯片210a和连接基板300之间、以及介于第二下半导体芯片220a和连接基板300之间。在一些实施例中,模制层基本上填充基板孔390。根据一些实施例,将粘性介电膜附接到连接基板300的顶表面、第一下半导体芯片210a和第二下半导体芯片220a的顶表面、以及第一下半导体芯片210a和第二下半导体芯片220a的侧壁,其结果是形成了模制层400。例如,味之素堆积膜(ajinomoto build-up film,abf)可以用作粘合介电膜。对于另一示例,模制层400包括介电聚合物,例如,基于环氧的聚合物。对于另一示例,省略了第一底部填充图案411和第二底部填充图案421,并且模制层400还延伸到第一下半导体芯片210a的底表面和第二下半导体芯片220a的底表面上。当省略第三底部填充图案431时,模制层400还延伸到重分布基板100和连接基板300之间的间隙中。

171.根据一些实施例,下半导体封装21还包括上重分布层600。上重分布层600设置在模制层400和连接基板300上。上重分布层600包括上介电层610、上重分布图案620和上接合焊盘640。上介电层610、上重分布图案620和上接合焊盘640与参照图5描述的那些基本相同。然而,在其他实施例中,上重分布图案620中的至少一个延伸到模制层400中,并因此耦接到第二焊盘312。

172.在其他实施例中,可以通过使用参照图3描述的重分布基板100

′

来制造下半导体封装21。在这种情况下,从半导体封装5中省略了接合凸块250、连接凸块255以及第一底部填充图案411、第二底部填充图案421和第三底部填充图案431。另外,重分布基板100’与第一半导体芯片210a和第二半导体芯片220a之间的布置关系与参照图3描述的重分布基板

100’与半导体芯片200之间的布置关系基本相同。

173.根据一些实施例,上半导体封装22设置在下半导体封装21上。例如,上半导体封装22被放置在上重分布层600上,并通过连接端子650连接到上重分布层600。上半导体封装22包括上基板710、上半导体芯片720和上模制层730。上半导体封装22和连接端子650与参照图5描述的那些基本相同。例如,连接端子650介于下半导体封装21和上半导体封装22之间。上半导体封装22还包括热辐射结构780。

174.根据本发明构思的实施例,凸块下图案包括第一部分和比第一部分宽的第二部分。由于凸块下图案的第二部分用作布线,所以导电图案具有增加的电学特性。凸块下图案的第二部分减少了导电图案的顶表面处的起伏。因此,导电图案之间具有增加的电连接。凸块下种子图案延伸到凸块下图案的侧壁上,因此凸块下图案稳定地附接到介电层。重分布基板和包括该重分布基板的半导体封装具有提高的可靠性。

175.本发明构思的该详细描述不应被解释为限于本文阐述的实施例,并且本发明构思的实施例旨在覆盖本发明的各种组合、修改和变化,而不脱离本发明构思的精神和范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。