半导体装置及其制造方法

1.[相关申请案]

[0002]

本技术案享有以日本专利申请案2020-151455号(申请日:2020年9月9日)为基础申请案的优先权。本技术案通过参照该基础申请案而包含基础申请案的所有内容。

技术领域

[0003]

本发明的实施方式涉及一种半导体装置及其制造方法。

背景技术:

[0004]

在具有三维结构的存储单元阵列的半导体装置中,设置着包含多个电极层的积层体及贯通该积层体的通道膜。关于这样的半导体装置的结构,已知有使通道膜的侧壁与设置在积层体之下的源极线直接接触的dsc(direct strap contact,直接带状接触)结构。另外,通道膜会通过栅极感应漏极泄漏(gidl:gate-induced drain leakage)来产生空穴(hole)。当空穴充分蓄积时,数据会被抹除。

[0005]

在具有所述dsc结构的半导体装置中,磷(p)等杂质掺杂在源极线中。当产生所述gidl时,该杂质扩散到通道膜。

技术实现要素:

[0006]

在具有所述dsc结构的半导体装置中,磷(p)等杂质掺杂在源极线中。当产生所述gidl时,该杂质扩散到通道膜。此时,可能会产生杂质向通道膜的扩散距离达不到、或杂质的扩散距离变动之类的事态。这样,如果杂质的扩散范围变得不稳定,那么有数据抹除的性能降低的可能性。

[0007]

本发明要解决的问题在于提供一种能够使杂质的扩散范围稳定的半导体装置及其制造方法。

[0008]

一实施方式的半导体装置具备:衬底;配线层,设置在衬底上,且包含第1膜;积层体,在配线层上将多个第1层与多个第2层交替地积层而成;单元膜,设置在积层体内;半导体膜,在积层体内与单元膜对向;及扩散膜,在配线层内与第1膜相接并且在积层体内与半导体膜相接。扩散膜包含杂质,扩散膜的上端部位于多个第1层中的比最下层的第1层高的位置。

附图说明

[0009]

图1是表示第1实施方式的半导体装置的主要部分的结构的立体图。

[0010]

图2是表示沿着图1所示的切断线a-a的截面的一部分的图。

[0011]

图3是将图2的一部分放大的剖视图。

[0012]

图4a是表示在衬底上积层电路层及配线层的工序的剖视图。

[0013]

图4b是表示在配线层上形成积层体的工序的剖视图。

[0014]

图4c是表示形成空穴的工序的剖视图。

[0015]

图4d是表示使单元膜在空穴内成膜的工序的剖视图。

[0016]

图4e是表示使扩散膜成膜的工序的剖视图。

[0017]

图4f是表示扩散膜的一部分进行蚀刻的工序的剖视图。

[0018]

图4g是表示使半导体膜成膜的工序的剖视图。

[0019]

图4h是表示形成狭缝的工序的剖视图。

[0020]

图4i是表示选择性地蚀刻绝缘层的工序的剖视图。

[0021]

图4j是表示形成导电层及源极线的工序的剖视图。

[0022]

图4k是表示在空穴及狭缝嵌埋绝缘膜的工序的剖视图。

[0023]

图5是第2实施方式的半导体装置的主要部分的剖视图。

[0024]

图6a是表示使半导体膜在单元膜的内侧成膜的工序的剖视图。

[0025]

图6b是表示使第1芯绝缘膜在半导体膜的内侧成膜的工序的剖视图。

[0026]

图6c是表示蚀刻第1芯绝缘膜的一部分的工序的剖视图。

[0027]

图6d是表示对第1芯绝缘膜进行退火的工序的剖视图。

[0028]

图6e是表示在空穴嵌埋第2芯绝缘膜的工序的剖视图。

具体实施方式

[0029]

以下,参照附图对本发明的实施方式进行说明。本实施方式并不限定本发明。在以下的实施方式中,对具有三维结构的存储单元阵列的半导体装置进行说明。该半导体装置是能够电气地自由地进行数据的抹除及写入,且即便切断电源也能够保存存储内容的nand(not and,与非)型非易失性半导体存储装置。

[0030]

(第1实施方式)

[0031]

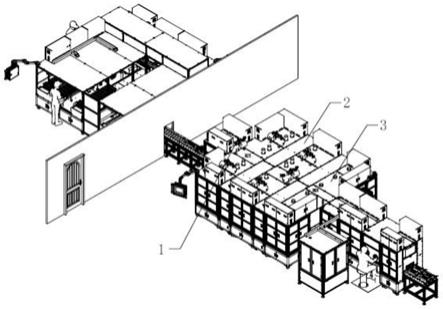

图1是表示第1实施方式的半导体装置的主要部分的结构的立体图。图1所示的半导体装置1具备衬底10、电路层20、配线层30、积层体40、及多个柱状部50。在以下的说明中,将与衬底10平行的方向且相互正交的2个方向设为x方向及y方向。另外,将与衬底10垂直的方向且相对于x方向及y方向正交的方向设为z方向。z方向也是积层体40的积层方向。

[0032]

衬底10例如是硅衬底。在衬底10上设置着电路层20。电路层20具有设置在柱状部50的存储单元的周边电路。在该周边电路,配置着用于驱动存储单元的晶体管等。在电路层20上设置着配线层30。配线层30具有与柱状部50电连接的源极线。在配线层30上设置着积层体40。

[0033]

积层体40具有sgd41、单元42、及sgs43。sgd41位于积层体40的上层部,且具有多个漏极侧选择栅极电极。sgs43位于积层体40的下层部,且具有多个源极侧选择栅极电极。单元42位于sgd41与sgs43之间,具有多个字线。

[0034]

多个柱状部50在x方向及y方向锯齿配置。另外,各柱状部50在配线层30内及积层体40内沿着z方向延伸。

[0035]

图2是表示沿着图1所示的切断线a-a的截面的一部分的图。此处,参照图2对配线层30、积层体40及柱状部50的结构进行说明。

[0036]

首先,对配线层30的结构进行说明。在配线层30中,源极线301形成在绝缘层302与绝缘层303之间。源极线301例如是钨(w)等金属、多晶硅、或掺杂着磷等杂质的非晶硅。绝缘层302及绝缘层303例如包含氧化硅(sio2)。

etching,反应性离子蚀刻)来形成空穴60。空穴60在z方向贯通积层体40a、配线层30的绝缘层303及绝缘膜301a,且在绝缘层302处终止。

[0049]

接下来,如图4d所示,使单元膜51在空穴60内成膜。具体来说,将图3所示的阻挡绝缘膜511、电荷蓄积膜512、及隧道绝缘膜513按照该次序连续地成膜。

[0050]

接下来,如图4e所示,例如通过cvd,使扩散膜54在单元膜51的内侧成膜。扩散膜54使用掺杂着磷的非晶硅来成膜。此时,由于空穴60的底部变细,所以该底部由扩散膜54嵌埋。

[0051]

接下来,如图4f所示,对扩散膜54的一部分共形地进行蚀刻。结果,在扩散膜54中,嵌埋在空穴60的底部的部分残留,而其它部分被去除。扩散膜54的蚀刻既可以为cde(chemical dry etching,化学干式蚀刻)等干式蚀刻,也可以为湿式蚀刻。

[0052]

在干式蚀刻的情况下,例如,能够通过在107pa(800mtorr)的压力条件下导入包含三氟化氮(nf3)与氧(o2)的混合气体,来蚀刻扩散膜54。另一方面,在湿式蚀刻的情况下,例如,能够通过将(2-羟乙基)三甲基氢氧化铵(tmy)用作化学溶液,来蚀刻扩散膜54。

[0053]

另外,扩散膜54的蚀刻既可以为各向同性蚀刻,也可以为各向异性蚀刻。尤其在各向异性蚀刻的情况下,能够控制扩散膜54的蚀刻量,换句话说能够控制残留在空穴60的底部的扩散膜54的高度。在本实施方式中,扩散膜54的上端部被控制为比积层体40a的最下层的绝缘层401a高的位置。

[0054]

接下来,如图4g所示,使半导体膜52在单元膜51的内侧及扩散膜54上成膜。半导体膜52例如是通过cvd形成的非掺杂非晶硅膜。

[0055]

接下来,经过数个工序,如图4h所示,例如通过rie来形成狭缝61。狭缝61也与空穴60同样地,在z方向贯通积层体40a、配线层30的绝缘层303及绝缘膜301a,且在绝缘层302处终止。

[0056]

接下来,如图4i所示,使用狭缝61选择性地蚀刻绝缘层401a及绝缘膜301a。该蚀刻例如将磷酸溶液用作化学溶液。另外,在该蚀刻中,将单元膜51中与绝缘膜301a相接的部分去除。结果,扩散膜54露出。

[0057]

接下来,如图4j所示,在绝缘层401a的去除部位形成导电层401,并且在绝缘膜301a的去除部位形成源极线301。由此,由于源极线301与扩散膜54相接,所以源极线301经由扩散膜54而与半导体膜52电连接。

[0058]

接下来,如图4k所示,在空穴60内嵌埋芯绝缘膜53。另外,在狭缝61内嵌埋绝缘膜62。绝缘膜62例如包含氧化硅。最后,将残留在积层体40的上表面的不需要的膜去除。由此,完成图2所示的半导体装置1。

[0059]

根据以上所说明的本实施方式,将含磷的扩散膜54嵌埋在空穴60的底部。另外,该扩散膜54具有突出到积层体40的sgs43为止的结构。因此,在产生gidl时,可确保磷的扩散距离其减少扩散距离的变动。由此,由于磷的扩散范围稳定,所以能够提高数据抹除的性能。

[0060]

另外,在本实施方式中,通过形成扩散膜54,而无须向源极线301中掺杂磷等杂质。因此,能够由金属形成源极线301。在该情况下,由于能够避免源极线301内残留硅缝的事态,所以装置的可靠性提高。

[0061]

(第2实施方式)

[0062]

图5是第2实施方式的半导体装置的主要部分的剖视图。对与所述第1实施方式相同的构成要素标注相同的符号,并省略详细的说明。

[0063]

图5所示的半导体装置2在具备第1芯绝缘膜53a及第2芯绝缘膜53b的方面与第1实施方式不同。第1芯绝缘膜53a与扩散膜54对向。在第1芯绝缘膜53a中包含与扩散膜54相同的浓度的磷作为杂质。

[0064]

另一方面,第2芯绝缘膜53b与半导体膜52对向。第2芯绝缘膜53b的磷浓度低于第1芯绝缘膜53a的磷浓度。

[0065]

以下,参照图6a~图6e,对本实施方式的半导体装置的制造工序进行说明。此外,由于直到在空穴60内形成单元膜51为止的工序与第1实施方式相同,所以省略说明。

[0066]

在单元膜51的成膜后,如图6a所示,例如通过cvd,使半导体膜52在单元膜51的内侧成膜。半导体膜52例如是非晶硅膜。

[0067]

接下来,如图6b所示,例如通过ald,使第1芯绝缘膜53a在半导体膜52的内侧成膜。第1芯绝缘膜53a使用掺杂着磷的氧化硅来成膜。此时,由于空穴60的底部变细,所以由第1芯绝缘膜53a嵌埋。

[0068]

接下来,如图6c所示,对第1芯绝缘膜53a共形地进行蚀刻。结果,第1芯绝缘膜53a中嵌埋在空穴60的底部的部分残留,而其它部分被去除。

[0069]

第1芯绝缘膜53a的蚀刻既可以为cde等干式蚀刻,也可以为湿式蚀刻。另外,第1芯绝缘膜53a的蚀刻既可以为各向同性蚀刻,也可以为各向异性蚀刻。在各向异性蚀刻的情况下,能够控制第1芯绝缘膜53a的蚀刻量,换句话说能够控制残留在空穴60的底部的第1芯绝缘膜53a的高度。在本实施方式中,第1芯绝缘膜53a的上端部被控制为比积层体40a的最下层的绝缘层401a高的位置。

[0070]

接下来,例如于高于1000℃的温度条件下对第1芯绝缘膜53a进行退火。由此,第1芯绝缘膜53a中所包含的磷的一部分向半导体膜52扩散。结果,如图6d所示,半导体膜52中与第1芯绝缘膜53a对向的部分变化为含磷的扩散膜54。

[0071]

接下来,如图6e所示,在空穴60嵌埋第2芯绝缘膜53b。第2芯绝缘膜53b包含磷浓度低于第1芯绝缘膜53a的非掺杂的氧化硅。

[0072]

然后,与第1实施方式同样地,形成狭缝61(参照图4j),使用狭缝61将绝缘层401a向导电层401置换,并且将绝缘膜301a置换为源极线301。另外,对与绝缘膜301a对向的单元膜51进行蚀刻而将源极线301与扩散膜54直接连接。由此,完成图5所示的半导体装置2。

[0073]

根据以上所说明的本实施方式,将含磷的第1芯绝缘膜53a预先嵌埋在空穴60的底部。通过对该第1芯绝缘膜53a进行退火,而磷扩散到半导体膜52,形成扩散膜54。与第1实施方式同样地,该扩散膜54也具有突出到积层体40的sgs43为止的结构。因此,在产生gidl时,可确保磷的扩散距离且减少扩散距离的变动。由此,由于磷的扩散范围稳定,所以能够提高数据抹除的性能。

[0074]

另外,在本实施方式中,也因形成了与源极线301及半导体膜52分别相接的扩散膜54,所以无须向源极线301中掺杂磷等杂质。因此,如果由金属形成源极线301,那么能够避免硅缝残留之类的事态,所以提高装置的可靠性。

[0075]

对本发明的几个实施方式进行了说明,但这些实施方式是作为示例而提出的,并不旨在限定发明的范围。这些实施方式能够以其它各种方式实施,在不脱离发明的主旨的

范围内,能够进行各种省略、置换、变更。这些实施方式或其变化包含在发明的范围或主旨中,同样地包含在权利要求书中所记载的发明及与其均等的范围中。

[0076]

[符号的说明]

[0077]

1,2:半导体装置

[0078]

10:衬底

[0079]

30:配线层

[0080]

40:积层体

[0081]

51:单元膜

[0082]

52:半导体膜

[0083]

53a:第1芯绝缘膜

[0084]

53b:第2芯绝缘膜

[0085]

54:扩散膜

[0086]

301:源极线

[0087]

401:导电层

[0088]

402:绝缘层。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。