semiconductor:金属氧化物半导体)晶体管。此外,实施方式并不限定于以下的例子。半导体元件10也可以是二极管、igbt(insulated gate bipolar transistor:绝缘栅双极型晶体管)等。

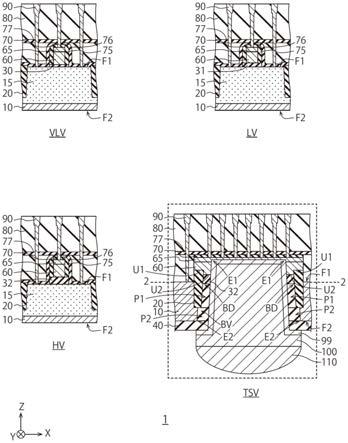

14.如图1所示,半导体元件10包括半导体部11、第一电极13和第二电极15。第一电极13设置于半导体部11的背面上。第二电极15设置于半导体部11的表面上。半导体部11例如是硅。第一电极13及第二电极15例如是包含铝等的金属层。

15.半导体部11具有将其背面和表面连接的侧面。半导体部11具有设置于侧面的槽sg。槽sg例如沿x-y平面延伸。槽sg例如以包围半导体部11的方式设置。

16.半导体元件10例如被安装在引线21之上。引线21例如是包含铜的金属板。半导体元件10将第一电极13朝向引线21安装。半导体元件10例如经由焊料25与引线21电连接。

17.半导体元件10例如经由金属线17与引线23电连接。引线23例如是包含铜的金属板。金属线17被接合于第二电极15以及引线23。金属线17例如是金线。

18.半导体元件10使用树脂20进行气密密封。树脂20例如是环氧树脂。树脂20以覆盖半导体元件10、金属线17、引线21及23的方式成形。引线21具有设置于树脂20之中的安装部和从树脂20延伸出的端子。引线23具有设置于树脂20之中并与金属线17连接的接合部和从树脂20延伸出的其他端子。

19.树脂20包括被填充到在半导体部11的侧面设置的槽sg的内部的部分。由此,能够提高半导体元件10与树脂20之间的紧贴强度。另外,通过设置槽sg,由此能够经由树脂20与引线21的界面以及树脂20与半导体部11的界面,使从树脂20的外侧到第二电极15的沿面距离延长。由此,能够抑制外部气体向半导体元件10的活性区域的侵入。

20.接着,参照图2a~图4c,对实施方式的半导体元件10的制造方法进行说明。图2a~图4c是表示将半导体元件10芯片化的过程的示意剖视图。

21.如图2a所示,使用在半导体晶片50的表面上形成的蚀刻掩模61形成槽g1。半导体晶片50例如为硅晶片。在半导体晶片50的背面上形成第一电极13。在半导体晶片50的表面上形成第二电极15。在半导体晶片50与第二电极15之间,例如设置未图示的mos构造。

22.蚀刻掩模61形成为覆盖第二电极15。蚀刻掩模61例如是抗蚀剂膜。蚀刻掩模61具有开口61f。开口61f例如沿着半导体晶片50的切割线形成。

23.槽g1例如通过使用六氟化硫(sf6)作为蚀刻气体的各向异性的干式蚀刻来形成。槽g1通过使用蚀刻掩模61将半导体晶片50选择性地去除至规定的深度而形成。

24.如图2b所示,形成将槽g1的内表面覆盖的保护膜63。保护膜63例如是碳膜。保护膜63例如通过以c4f8等特氟隆(注册商标)系气体为原料的等离子体cvd(chemical vapor deposition:化学气相沉积)而沉积。保护膜63也以覆盖蚀刻掩模61的方式形成。

25.如图2c所示,选择性地去除将保护膜63的槽g1的底面覆盖的部分。保护膜63例如通过各向异性的干式蚀刻,留下沉积在槽g1的内壁上的部分而被去除。即,保护膜63的沉积在蚀刻掩模61的上表面的部分也被去除。

26.如图2d所示,在半导体晶片50之中形成槽sg。槽sg通过经由蚀刻掩模61的开口61f和槽g1将半导体晶片50选择性地去除而形成。槽sg例如使用各向同性的干式蚀刻而形成。由于槽g1的内壁被保护膜63覆盖,因此蚀刻从槽g1的底面起进行,通过侧面蚀刻形成在横向上扩展的空洞。在将各向同性干式蚀刻的速度设为恒定的情况下,槽sg的蚀刻时间比槽

g1的蚀刻时间长。

27.用于形成槽sg的蚀刻例如优选在通过各向同性干式蚀刻而使保护膜63消失之前停止。为了扩大槽sg的横宽,例如,较厚地形成保护膜63而延长蚀刻时间。

28.如图3a所示,以覆盖槽sg的内表面的方式再次形成保护膜63。保护膜63以将槽g1的内壁及蚀刻掩模61都覆盖的方式形成。

29.如图3b所示,例如通过各向异性的干式蚀刻选择性地去除在保护膜63的槽sg的底面所沉积的部分。保护膜63经由蚀刻掩模61的开口61f、槽g1而被选择性地去除。保护膜63保留在槽g1的内壁以及槽sg的内壁上沉积的部分而被选择性地去除。在槽sg的底面,保护膜63被去除的区域的宽度we例如与槽g1的x方向的宽度wt相同,或比wt宽。

30.如图3c所示,在槽sg的下方形成槽g2。槽g2通过在槽sg的底面经由将保护膜63选择性地去除的部分将半导体晶片50选择性地去除而形成。槽g2例如通过各向异性的干式蚀刻而形成。另外,在将各向同性干式蚀刻的速度设为恒定的情况下,槽g2的蚀刻时间比槽sg的蚀刻时间短。另外,槽g2的蚀刻时间被设定为与槽g1的蚀刻时间相同或比其长。

31.如图4a所示,以覆盖槽g2的内表面的方式再次形成保护膜63。保护膜63以将槽g1的内壁、槽sg的内壁以及蚀刻掩模61都覆盖的方式形成。

32.如图4b所示,例如通过各向异性的干式蚀刻选择性地去除在保护膜63的槽g2的底面上沉积的部分。保护膜63经由蚀刻掩模61的开口61f、槽g1以及槽g2而被选择性地去除。

33.接着,反复进行半导体晶片50的选择性去除、保护膜63的形成以及保护膜63的选择性去除,由此形成从半导体晶片50的表面连通至背面的分离槽dg。由此,半导体晶片50被分割成多个半导体部11,如图4c所示,半导体元件10被芯片化。最后,蚀刻掩模61和保护膜63例如通过氧灰化而被去除。

34.如图4c所示,分离槽dg的比槽sg靠下的区域的宽度wb形成为比槽sg靠上的区域的宽度wt宽。即,半导体部11形成为位于槽sg的上方的部分比位于槽sg下方的部分更向外侧突出的形状。由此,能够进一步提高半导体元件10与树脂20之间的紧贴强度。

35.图5a及图5b是表示实施方式的半导体元件10的示意图。图5a是半导体元件10的剖视图。图5b是表示半导体元件10的表面的俯视图。

36.图5a表示通过上述的芯片化方法形成的半导体元件10的剖面。如图5a所示,半导体部11具有槽sg和分别与槽g1及g2对应的凹部。槽sg的x方向的深度rd比各个凹部的x方向的深度深。槽sg的深度rd为凹部的深度的2倍以上。另外,槽sg的z方向的宽度rw比凹部的z方向的宽度宽。

37.另外,在图2a~图2c所示的例子中,示出了形成1个槽g1的过程,但并不限定于此。例如,也可以通过反复进行半导体晶片50的选择蚀刻、保护膜63的形成以及保护膜63的选择性去除,从而在z方向上形成较深的槽g1。

38.如图5b所示,半导体元件10除了第二电极15以外,还具有控制电极16。在该例子中,第一电极13(参照图5a)是漏极电极,第二电极15是源极电极。另外,控制电极16例如是与mos结构的栅极连接的栅极电极。槽sg例如以包围半导体部11的方式沿着半导体部11的外缘设置。槽sg的沿着半导体部11的表面的深度比第二电极15与半导体部11的表面的外缘之间的距离浅。另外,槽sg的沿着半导体部11的表面的深度比控制电极16与半导体部11的表面的外缘之间的距离浅。

39.图6是表示实施方式的变形例的半导体元件10的示意剖视图。在该例子中,半导体部11具有沿z方向延伸的槽vg。槽vg设置于半导体部11的侧面,从半导体部11的表面向背面延伸。在半导体部11的背面上设置有第一电极13,在半导体部11的表面上设置有第二电极15(参照图5a)。

40.槽vg例如通过在蚀刻掩模61(参照图2a)的开口61f设置局部向内侧凹陷的凹槽部而形成。槽vg在半导体部11的侧面形成有多个。

41.如图6所示,槽vg既可以设置于半导体部11的1个侧面,也可以分别设置于半导体部11的4个侧面(参照图5b)。另外,槽vg也可以在1个侧面设置2个以上。通过在槽vg的内部填充树脂20,对于在x方向或y方向上产生的应力,能够提高半导体元件10与树脂20之间的紧贴性。

42.另外,半导体元件10设置有凹部,该凹部设置于半导体部11的侧面、在沿着半导体部11的表面的方向上延伸、且包围半导体部11。凹部设置有多个,在从半导体部11的背面朝向表面的方向上排列。

43.对本发明的几个实施方式进行了说明,但这些实施方式是作为例子进行提示的,并不意图限定发明的范围。这些新的实施方式能够以其他各种方式实施,在不脱离发明的主旨的范围内,能够进行各种省略、置换、变更。这些实施方式及其变形包含在发明的范围及主旨中,并且包含在权利要求书所记载的发明及其等同的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。