1.本发明涉及一种图案形成方法。

背景技术:

2.在半导体装置的制造中,已知有sti(shallow trench isolation:浅槽隔离)这样的技术,其中,在硅基片上形成微小的槽,在槽内埋入绝缘体以进行元件分离(例如,专利文献1)。在形成sti时,通常准备在表面具有形成有多个微小的凸状线材的线图案的基片,切割线材以形成所希望的微小图案,转印该图案以在基片形成sti槽。

3.现有技术文献

4.专利文献

5.专利文献1:日本特开平11-214651号公报

技术实现要素:

6.发明要解决的技术问题

7.本发明提供一种图案形成方法,其能够高精度且不使工序复杂化地进行线材的线切割以形成所希望的图案。

8.用于解决技术问题的技术方案

9.本发明的一方面的图案形成方法是在基片形成图案的图案形成方法,其包括:准备的基片的步骤,其中,上述基片在基体上形成有呈凸状且线状地设置的多个芯材、和分别在上述芯材的一侧及另一侧呈凸状且线状地设置的第一线材及第二线材;通过包含各向异性成膜的处理,在上述第一线材和上述第二线材中的任一者选择性地形成掩模材的步骤;通过包含使用线掩模的蚀刻的处理,以蚀刻的方式除去要进行线切割的区域中的上述第一线材和上述第二线材中没有形成上述掩模材的一侧的步骤,其中,上述线掩模在与该区域对应的部分具有线状的孔;以及除去上述芯材的步骤。

10.发明效果

11.依照本发明,提供一种图案形成方法,其能够高精度且不使工序复杂化地进行线材的线切割以形成所希望的图案。

附图说明

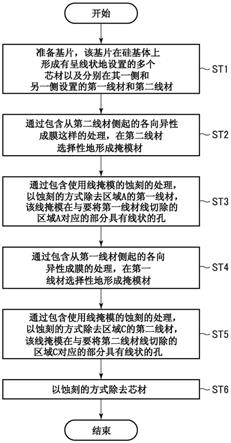

12.图1是表示一实施方式的图案形成方法的流程图。

13.图2是表示一实施方式的图案形成方法中使用的基片的构造的截面图。

14.图3是表示一实施方式的图案形成方法中使用的基片的构造的俯视图。

15.图4是表示对一实施方式的图案形成方法中使用的基片,进行第一阶段的图案化时的进行线切割的区域和不进行线切割的区域的俯视图。

16.图5是表示对一实施方式的图案形成方法中使用的基片进行第一阶段的图案化时,通过倾斜成膜,在第二线材和芯材上选择性地形成了掩模材的状态的截面图。

17.图6是表示进行倾斜成膜的成膜装置的例子的概要截面图。

18.图7是表示对图5的基片,在整个面填充了填充材的状态的截面图。

19.图8是表示从图7的状态起进行整个面的回刻或cmp,除去至芯材上的掩模材为止的状态的截面图。

20.图9是表示从图8的状态起再次填充填充材,进一步形成了sog层和抗蚀剂层的状态的截面图。

21.图10是用于说明用于进行图9所示的基片的线切割的线掩模的俯视图。

22.图11是表示将抗蚀剂层作为掩模,以蚀刻的方式除去了图9的基片的sog层和填充材的状态的截面图。

23.图12是表示将抗蚀剂层作为掩模,以蚀刻的方式除去了图9的基片的sog层和填充材的状态的俯视图。

24.图13是表示对图11和图12所示的基片,进一步蚀刻了sog层和填充材的状态的截面图。

25.图14是表示对图11和图12所示的基片,进一步蚀刻了sog层和填充材的状态的俯视图。

26.图15是表示在图13和图14所示的基片中,进行了区域a的第一线材的线切割时的状态的截面图。

27.图16是表示在图13和图14所示的基片中,进行了区域a的第一线材的线切割时的状态的俯视图。

28.图17是表示在图13和图14所示的基片中,进行了区域a的第一线材的线切割时的状态的俯视图。

29.图18是表示在对一实施方式的图案形成方法中使用的基片进行第二阶段的图案化时,通过倾斜成膜,在第一线材和芯材上选择性地形成了掩模材的状态的截面图。

30.图19是用于说明用于对图18所示的基片进行线切割的线掩模的俯视图。

31.图20是表示对图18所示的基片,使用图19的线掩模进行了区域c的线切割的状态的截面图。

32.图21是表示对图18所示的基片,使用图19的线掩模进行了区域c的线切割的状态的俯视图。

33.图22是表示除去图21所示的基片的芯材而形成了sti槽形成用图案的状态的俯视图。

34.图23是表示在线状图案形成sti槽形成用的图案时使用的现有的孔掩模和进行线切割而形成的sti槽用的图案的俯视图。

35.图24是表示在使用孔掩模进行了线切割时,切割部从线材偏移了的状态的俯视图。

36.附图标记说明

37.10:硅基体

38.11:sin膜

39.12:sio2膜

40.13:芯材

41.14a:第一线材

42.14b:第二线材

43.15:掩模材

44.16:填充材

45.17:sog层

46.18:抗蚀剂层

47.19:线掩模

48.19a:孔

49.20:sti槽形成用图案

50.100:成膜装置

51.110:腔室

52.112:靶材保持件

53.114:电源

54.118:溅射颗粒遮挡板

55.118a:通过孔

56.120:排气装置

57.122:气体导入部

58.124:靶材

59.w:基片。

具体实施方式

60.以下,参照附图,对实施方式进行说明。

61.此处,作为一实施方式的图案形成方法,以形成sti槽形成用的图案的方法为例进行说明。

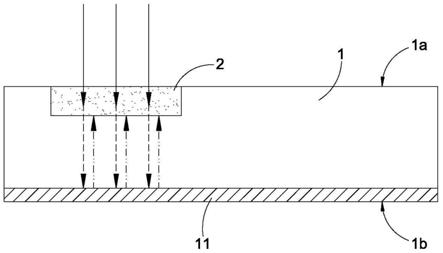

62.图1是表示一实施方式的图案形成方法的流程图。在本实施方式的图案形成方法中,首先,准备例如如图2的截面图和图3的俯视图所示的基片w(步骤st1)。

63.作为基片w,例如如图2、图3所示,使用半导体晶片。基片w构成为,例如在硅基体10上,隔着作为转印层的sin膜11和sio2膜12,形成有呈线状且凸状地平行设置的多个芯材13、以及分别在其一侧和另一侧呈线状且凸状地设置的第一线材14a和第二线材14b。第一线材14a和第二线材14b构成凸状的线图案。该线图案例如在光刻工序中,通过使用双重图案化或进行两次双重图案化的四重图案化来形成。由此,能够形成为用通常的光刻技术可形成的节距的1/2的节距或1/4的节距的微小图案。此时,芯材13的高度被加工得高于第一线材14a和第二线材14b。芯材13例如由si形成。此外,第一线材14a和第二线材14b例如由sin形成。

64.接着,通过包含从第二线材14b侧起的各向异性成膜的处理,在第二线材14b选择性地形成掩模材(步骤st2)。

65.接着,通过包含使用线掩模的蚀刻的处理,以蚀刻的方式除去区域a的第一线材14a,其中该线掩模在与要将第一线材14a线切割的区域a对应的部分具有线状的孔(步骤st3)。

66.通过步骤st2和步骤st3进行第一阶段的图案化。即,在第一阶段的图案化中,通过步骤st2和步骤st3,进行图3的线图案中的、图4所示的区域a的第一线材14a的线切割,在其以外的区域b中,第一线材14a未被切割而保留。

67.在步骤st2中,首先,作为各向异性成膜,例如进行从第二线材14b侧对基片w在倾斜方向上供给成膜颗粒的倾斜成膜,如图5所示,在第二线材14b和芯材13上形成掩模材15。在倾斜成膜中,成膜材不到达第一线材14a,而在第二线材14b和芯材13上选择性地形成掩模材15。作为掩模材15,例如使用tin膜、sio2膜。

68.倾斜成膜例如能够用如图6所示的成膜装置进行。图6的成膜装置100是通过溅射来成膜的装置,具有腔室110、靶材124、电源114、基片移动部116、溅射颗粒遮挡板118、排气装置120和气体导入部122。

69.腔室110具有上部开口的圆筒状的腔室主体110a和以封闭腔室主体110a的上部开口的方式设置的尖头圆锥状的盖体110b,腔室110的内部被板状的溅射颗粒遮挡板118划分成上部和下部。上部空间是生成溅射颗粒的空间,下部空间是在基片w进行溅射成膜的处理空间。在溅射颗粒遮挡板118形成有使溅射颗粒通过的呈隙缝状的通过孔118a。

70.气体导入部122设置于腔室110的盖体110b的顶部,从气体导入部122将ar气体等非活性气体作为溅射气体导入腔室110内。

71.在腔室110的底部形成有排气口121,排气装置120连接到排气口121。排气装置120包括压力控制阀和真空泵,用排气装置120,能够将腔室110内真空排气至规定的真空度。

72.在腔室110的侧壁形成有用于送入送出基片w的送入送出口123。送入送出口123由闸门(gate valve)130开闭。

73.靶材保持件112倾斜地设置于腔室110的盖体110b的倾斜地形成的壁部。因此,靶材124倾斜地配置在靶材保持件112上。靶材124由构成要成膜的掩模材15的材料构成。在靶材保持件112连接有电源114,通过从电源114对靶材保持件112施加电压,在靶材124的周围,从气体导入部122导入的气体解离。然后,解离的气体中的离子撞击到靶材124,从靶材124倾斜地释放作为其构成材料的颗粒即溅射颗粒p。

74.在腔室110的溅射颗粒遮挡板118的下方空间,配置有基片移动部116。基片移动部116支承基片w并使其在作为箭头方向的一个方向移动。在本例中,基片移动部116具有支承销126,在支承销126上支承基片w。作为基片移动部116,可以使用基片输送臂、盘输送装置等现有设备。

75.在这样的成膜装置100中,将从相邻的输送室由输送装置(均未图示)输送来的基片w交接到基片移动部116上。然后,用排气装置120对腔室110内进行排气,并且从气体导入部122向腔室110内导入例如非活性气体,以调节至规定压力。一边使基片移动部116在箭头所示的方向上移动,一边从电源114对靶材保持件112施加电压,从靶材124使溅射颗粒p释放,以规定的角度倾斜地通过隙缝状的通过孔118a,在基片w上形成规定的膜。

76.通过像这样成膜,能够在基片w的整个面,进行将溅射颗粒的入射角维持成基本一定的状态的倾斜成膜。

77.在步骤st2中,像这样进行了掩模材15的成膜后,如图7所示,在整个面形成由soc(旋涂碳)构成的填充材16。然后,通过进行整个面的回刻(etch back)或cmp,如图8所示,除去至芯材13上的掩模材15为止,成为掩模材15仅保留在第二线材14b的状态。

78.在步骤st3中,如图9所示,再次填充由soc构成的填充材16,进一步形成作为第一掩模层的sog(旋涂玻璃)层17和作为第二掩模层的抗蚀剂层18。接着,如图10所示,以孔19a位于与上述区域a(参照图3)对应的位置的方式配置线掩模19,以蚀刻的方式除去区域a的抗蚀剂层18。然后,将抗蚀剂层18作为掩模,以蚀刻的方式除去sog层17和由soc构成的填充材16。由此,成为如图11的截面图和图12的俯视图所示的状态。此时的蚀刻,例如能够通过使用cf4、c4f8、o2、ar的等离子体蚀刻来进行。

79.在步骤st3中,进一步在作为第一线材14a的构成材料的sin最容易蚀刻的条件下,进行例如基于chf3、ar、h2的等离子体蚀刻,来以蚀刻的方式除去sog层17和区域a的第一线材14a。由此,成为图13的截面图和图14的俯视图所示的状态。此时的蚀刻,例如能够通过使用cf4、c4f8、o2、ar的等离子体蚀刻来进行。

80.在步骤st3中,接着,以蚀刻的方式除去掩模材15和由soc构成的填充材16,如图15的截面图和图16的俯视图所示,形成区域a的第一线材14a被线切割了的图案。此时的蚀刻在掩模材15为tin的情况下,能够通过使用例如cl2、n2的等离子体蚀刻来进行。

81.接着,通过包含从第一线材14a侧起采用倾斜成膜的各向异性成膜的处理,在第一线材14a选择性地形成掩模材(步骤st4)。

82.接着,通过包含使用线掩模的蚀刻的处理,以蚀刻的方式除去的区域c的第二线材14b,其中该线掩模在要将第二线材14b切割的区域c具有线状的孔(步骤st5)。

83.通过步骤st4和st5,对进行了第一阶段的图案化后的图17的基片w(图案)进行第二阶段的图案化。即,在第二阶段的图案化中,通过步骤st4和步骤st5,进行图17所示的区域c的第二线材14b的线切割,在此外的区域d中,不对第二线材14b进行线切割。

84.在步骤st4中,首先,从与第一阶段的图案化相反的一侧的第一线材14a侧起,通过与第一阶段相同的倾斜成膜,如图18所示,在第一线材14a和芯材13上形成掩模材15。之后,按照与第一阶段的图案化相同的步骤,进行芯材13上的掩模材15的除去,成为掩模材15保留在第二线材14b的状态。

85.在步骤st5中,按照与第一阶段的图案化相同的步骤,形成填充材16、sog层17和抗蚀剂层18。之后,如图19所示,以使孔19a的位置与区域c对应的方式将线掩模19错开地配置,以蚀刻的方式除去区域c的抗蚀剂层18。然后,与第一阶段的图案化同样地,将抗蚀剂层18作为掩模,以蚀刻的方式除去区域c的sog层17和由soc构成的填充材16。然后,与第一阶段的图案化同样地,以蚀刻的方式除去掩模材15和由soc构成的填充材16,如图20的截面图和图21的俯视图所示,形成区域c的第二线材14b被线切割了的图案。

86.最后,以蚀刻的方式除去芯材13(步骤st6)。由此,形成如图22所示的sti槽形成用图案20。此时的蚀刻,例如通过基于使用hbr、ar的等离子体蚀刻的si的选择性蚀刻来进行。此外,根据材料的组合的不同,也可以用sin构成芯材13,在此情况下,芯材13的蚀刻除去例如能够通过使用chf3、ar、h2的等离子体蚀刻来进行。

87.之后,将图22的图案依次转印到sio2膜12和sin膜11,最终对硅基体10进行蚀刻而形成sti槽,在sti槽埋入适宜的材料以形成sti。

88.在形成sti槽形成用的图案时,以往,使用如图23的(a)所示的方法,该方法中使用具有与要切割线材240的位置对应的孔250的孔掩模,来进行线材240的线切割。即,使用通过该方法,如图23的(b)所示,在线材240形成切割部241,形成sti槽用的图案的方法。然而,

随着半导体元件向微小化发展,光刻工序的尺寸微小化,允许误差变小,因此对于孔掩模而言,容易发生孔250的偏移。因此,如图24所示,切割部241从线材240偏移,难以高精度地形成图案。

89.因此,在本实施方式中,通过包含各向异性成膜的处理在仅一线材形成掩模材后,进行包含使用具有线状的孔的线掩模的蚀刻的处理。由此,能够通过比较简单的工序自对准地进行线材的线切割,不会产生如使用孔掩模时那样的精度问题,并且不会带来工序的复杂化,就能够进行线切割而形成所希望的图案。

90.以上,虽然对实施方式进行了说明,但是应当认为,本次公开的实施方式在所有方面均是例示而并非限制性的。在不脱离所附的权利要求的范围及其主旨的情况下,能够以各种形式省略、替换、改变上述实施方式。

91.例如,在上述实施方式中,虽然给出了形成用于形成sti槽的图案的情况,但是不限于此,只要是切割线材以形成图案的用途就能够应用。此外,虽然给出了切割第一线材和第二线材这两者的情况,但是在只切割任意一者的情况下也能够应用。

92.另外,在上述实施方式中,给出了以使用si作为芯材,使用sin作为线材,使用tin或sio2作为掩模材的例子,但是不限于此。例如,作为芯材、第一线材和第二线材、以及掩模材,可以使用从包括si、ti、zr、al、w、wc、wsi、hf、sic、c、ta、它们的氧化物、氮化物的组中适当选择的材料。特别是,作为芯材、线材、掩模材,使用从包括sio2、sin、si、tin、w、wsi、wc的组中选择的材料是更有效的。芯材、第一线材和第二线材、以及掩模材优选分别是不同的材料。

93.另外,在上述实施方式中,作为用于形成掩模材的各向异性成膜,给出了通过溅射进行倾斜成膜的例子,但是不限于此,此外,装置也不限于图6所示的装置。

94.另外,虽然示出了使用半导体晶片作为基片的情况,但是不限于此,可以是fpd(平板显示器)基片、陶瓷基片等其他基片。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。