1.本公开涉及倍频器,尤其涉及具有省电的工作周期控制的倍频电路与方法。

背景技术:

2.许多现代电子电路需要精确的时钟才能正确操作。时钟是一种在低准位和高准位之间周期性地来回切换的电压信号。电压信号维持在高准位的时间百分比称为工作周期。许多电路需要特定的时钟工作周期以提供最佳性能。例如,在时钟的上升缘和下降缘都被使用的多相时钟系统中,通常希望工作周期是50%。

3.现有的倍频电路(这里亦简称为倍频器)接收输入时钟并输出输出时钟,输出时钟的频率是输入时钟的频率的两倍,然而,输出时钟的工作周期可能不是所需要的。schwartz在美国专利6,348,821中公开了一种具有50%工作周期输出的倍频器,该倍频器具有模拟电路特性,该特性要求使用电流产生器定期给电容器充电,所以该倍频器并不省电。此外,该倍频器是用来产生50%的工作周期输出,这对于许多应用是有益的,但可能并非对所有应用都是好的。

4.因此,需要一种可控制工作周期的倍频器,其除了具有数位电路特性以及更好的用电效率之外,还不限于产生50%的工作周期输出。

技术实现要素:

5.本公开一实施例提供一种倍频电路。倍频电路包含:一多工器、一数位控制延迟电路、一一比二分频电路、一工作周期检测器以及一控制器。多工器接收一第一时钟并根据一第三时钟输出一第二时钟,其中,该第一时钟具有百分之五十的工作周期,并且是包含一第一相位及一第二相位的一两相时钟。数位控制延迟电路接收该第二时钟并根据一数位字输出一第四时钟。一比二分频电路接收该第四时钟并输出该第三时钟。工作周期检测器接收该第二时钟,并根据该第二时钟的一工作周期与一目标工作周期值的比较来输出一逻辑信号。控制器根据该逻辑信号输出该数位字。

6.本公开一实施例提供一种倍频方法,包含以下步骤:接收一第一时钟,该第一时钟具有百分之五十的一工作周期,而且是包含一第一相位及一第二相位的一两相时钟;根据一第三时钟使用一多工器选择该第一时钟的该第一相位及该第二相位的其中之一以输出一第二时钟;使用一数位控制延迟电路根据一数位字将该第二时钟延迟为一第四时钟;使用一比二分频电路来根据该第四时钟输出该第三时钟;使用一工作周期检测器根据该第二时钟的一工作周期与一目标工作周期值的比较来产生一逻辑信号;以及根据该逻辑信号更新该数位字。

附图说明

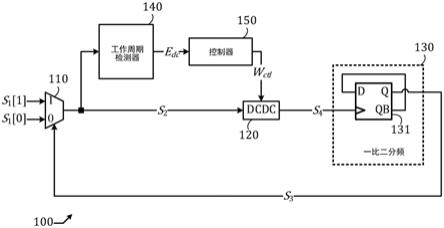

7.图1a显示根据本公开一实施例的倍频器的电路图;

8.图1b显示图1a的倍频器的时序图;

channel metal oxide semiconductor,nmos)”、“p通道金属氧化物半导体(p-channel metal oxide semiconductor,pmos)”、“电阻器”、“电容器”、“比较器”、“反相器”、“逻辑信号”、“多工器”、“开关”、“数据触发器(data flip flop)”、“低通滤波器”及“工作周期”。这类的术语在微电子学的领域中使用,并且相关的概念对于本技术领域技术人员而言是显而易见的,因此这里将不进行详细说明。

41.本技术领域技术人员认得电阻器的符号以及金属氧化物半导体(metal-oxide semiconductor,mos)晶体管的符号(包含pmos晶体管和nmos晶体管),并且可以识别其“源极”、“栅极”和“漏极”等端点。本技术领域技术人员可以阅读包含电阻器、nmos晶体管及pmos晶体管的电路的示意图,并且不需要关于在示意图中一个晶体管或电阻器如何连接另一晶体管或电阻器的详细描述。

42.本公开是以工程概念做描述。例如,关于两个变量x和y,当说“x等于y”时,意味着“x大约等于y”,即“x和y之间的差小于指定的工程公差”。当说“x为零”时,表示“x约为零”,即“x小于指定的工程公差”。当说“x显著小于y”时,意味着“相对于y而言x可以忽略不计”,即“x与y的比小于工程公差,因此与y相比x可以忽略不计”。

43.在整个本公开中,“v

dd”表示电源节点。请注意,电源节点是电压准位基本上固定的节点。在本公开中,取决于对于本技术领域技术人员来说是显而易见的上下文,有时v

dd

是指电源节点v

dd

处的电压准位。例如,很明显的,当我们说“v

dd

为1.05v”时,是指电源节点v

dd

上的电压准位为1.05v。接地节点是电压准位基本上为零的节点。

44.在本公开中,信号是可以随着时间变化的可变准位的电压,或者是一个数,该数具有可以随时间变化的值。当信号是电压时,称之为电压信号,而且信号在某一时刻的准位表示信号在该时刻的状态。当信号为一个数时,称为数值信号(numerical signal),并且信号在某一时刻的值表示信号在该时刻的状态。

45.逻辑信号是有两种状态的电压信号:低准位状态和高准位状态。低准位状态也称为“0”状态,而高准位也称为“1”状态。关于逻辑信号q,当说“q为高准位”或“q为低准位”时,意思是“q处于高准位状态”或“q处于低准位状态”。同样,当说“q为1”或“q为0”时,意思是“q处于1的状态”或“q处于0的状态”。

46.当逻辑信号从低准位切换到高准位时,它会经历从低准位到高准位的转变,并呈现上升缘。当逻辑信号从高准位切换到低准位时,它会经历从高准位到低准位的转变,并呈现下降缘。

47.当使用mos晶体管来实现开关时,它由控制信号控制,该控制信号是施加在mos晶体管的栅极上的逻辑信号。当控制信号为高准位时,由nmos晶体管实现的开关处于“导通”状态,而当控制信号为低准位时,其处于“不导通”状态。

48.如果第一逻辑信号和第二逻辑信号总是处于相反的状态,则我们说第一逻辑信号是第二逻辑信号的反相或反相逻辑。也就是说,当第一逻辑信号为低准位时,第二逻辑信号为高准位;当第一逻辑信号为高准位时,第二逻辑信号为低准位。当我们说第一逻辑信号是第二逻辑信号的反相逻辑时,意思是第一逻辑信号和第二逻辑信号是彼此互补的。

49.两相时钟(two-phase clock)是具有两个相位(包含第一相位和第二相位)的时钟,其中第二相位是第一相位的反相逻辑(即,第二相位与第一相位互补);当第一相位和第二相位都具有百分之五十的工作周期时,此两相时钟被认为是具有百分之五十的工作周

期。

50.数位字(digital word)是整数值的数值信号,数值信号可以是一个集合,该集合包含根据某个编码方案的多个逻辑信号。

51.一个电路是晶体管、电阻器及/或其他电子装置的集合,晶体管、电阻器及/或其他电子装置以某种方式互连以实现某种功能。

52.图1a显示本公开一实施例的倍频器100的示意图。倍频器100包含多工器110、数位控制延迟电路(digitally controlled delay circuit,dcdc)120、一比二分频电路(divide-by-two circuit,二次分频电路)130、工作周期检测器140以及控制器150。多工器110用来接收第一时钟s1。第一时钟s1具有50%的工作周期,并且是包含第一相位s1[0]和第二相位s1[1]的两相时钟。多工器110还根据第三时钟s3输出第二时钟s2。数位控制延迟电路120用来接收第二时钟s2并根据数位字w

ctl

输出第四时钟s4。一比二分频电路130用来接收第四时钟s4并输出第三时钟s3。工作周期检测器140用来接收第二时钟s2并输出逻辑信号e

dc

。控制器150用来接收逻辑信号e

dc

并输出数位字w

ctl

。为了简洁起见,以下将第一时钟s1简称为s1、将第一时钟s1的第一相位s1[0]简称为s1[0]、将第一时钟s1的第二相位s1[1]简称为s1[1]、将第二时钟s2简称为s2、将第三时钟s3简称为s3、将第四时钟s4简称为s4、将逻辑信号e

dc

简称为e

dc

,以及将数位字w

ctl

简称为w

ctl

。

[0053]

多工器110根据s3选择s1[0]或s1[1]作为输出(即,s2),其功能可以描述如下:

[0054][0055]

可以根据方程式(1)来实现图1a的多工器110的多工器在现有技术中是众所周知的,因此这里不再详细描述。

[0056]

dcdc 120实现了可编程延迟的功能,使得s4是s2的延迟,其中,s2的上升缘往后传递并最终变成s4的上升缘,其传递延迟由w

ctl

控制。一比二分频电路130实现了一比二分频(divide-by-two)的功能,使得s4的上升缘触发s3切换状态,从而导致s3的上升缘或下降缘。如果为s4的每个上升缘分配一个序号,则s4的偶数上升缘触发s3从低准位切换到高准位(即s3的上升缘),而s4的奇数上升缘触发s3从高准位切换到低准位(即s3的下降缘)。s4的每两个上升缘仅触发s3的一个上升缘,因此s3被称为s4的一比二分频时钟。

[0057]

s1是具有50%工作周期的两相时钟。令s1的周期为t。倍频器100的目的是使s2成为倍频的时钟并且具有目标工作周期值。也就是说,s2的周期等于t/2,因为倍频意味着周期减半。s4是s2的延迟,因此也具有相同的周期t/2。s3是s4的一比二分频时钟,因此s3的周期是s4的周期的两倍,亦即s3的周期等于t。

[0058]

dcdc 120接收s2并输出s4,使得s2的上升缘可以传递并且变成具有传递延迟的s4的上升缘。令dcdc 120的传递延迟为td。图1b显示倍频器100的时序图,其中,s1[0]、s1[1]、s2、s4及s3均为时钟,而时钟是逻辑信号

──

不是高准位(v

dd

)就是低准位(0v)。如图所示,s1[0]和s1[1]是互补的。s1[0]的周期是t,如上升缘190a(在时间点ta)和下一上升缘190e(在时间点te)之间的时间差t所示。s1[0]的工作周期为50%,如上升缘190a和下一个下降缘190c(在时间点tc)之间的时间差t/2所示,表示s1[0]在一个时钟周期的50%的时间保持在高准位。对于本技术领域具有通常知识而言显而易见且无需对其进行解释是,s1[1]的周期

为t,且s1[1]的工作周期为50%。最初,s3为低准位(即0),所以多工器110选择s1[0]作为s2。在时间点ta,s1[0]的上升缘190a导致s2的上升缘192a,上升缘192a在dcdc 120中传递后导致s4在时间点tb的上升缘194b,其中时间点tb与时间点ta之间的时间差为td,即dcdc 120的传递延迟。s4的上升缘194b触发s3切换到高准位(即1),并导致s3在时间点tb的上升缘193b,上升缘193b促使多工器110选择s1[1]作为s2并导致s2在时间点tb的下降缘192b。之后,在时间点tc(时间点tc和时间点tb之间的时间差为t/2-td),由于多工器110选择s1[1]作为s2,s1[1]的上升缘191c导致s2的上升缘192c。s2的上升缘192c在dcdc 120中传递,并导致s4在时间点td的上升缘194d,上升缘194d触发s3切换为低准位(即0),并导致s3在时间点td的下降缘193d,下降缘193d促使多工器110选择s1[0]作为s2,并且导致s2在时间点td的下降缘192d,其中时间点td和时间点tc之间的时间差是td,即dcdc 120的传递延迟。之后,在时间点te(时间点te和时间点td之间的时间差是t/2-td),因为多工器110选择s1[0]作为s2,s1[0]的上升缘190e导致s2的上升缘192e。s2的工作周期等于td除以t/2,如下式所示:

[0059][0060]

其中,do代表s2的工作周期。

[0061]

工作周期检测器140和控制器150的目的是为w

ctl

建立适当的值,以使do等于目标工作周期值d

t

。

[0062]

工作周期检测器140根据下式输出e

dc

:

[0063][0064]

当e

dc

为1时,表示s2的工作周期大于目标工作周期值d

t

,因此需要减小s2的工作周期。当e

dc

为0时,表示s2的工作周期小于目标工作周期值d

t

,因此需要增加s2的工作周期。

[0065]

在一个实施例中,w

ctl

是整数,并且w

ctl

的值越大dcdc 120的传递延迟td就越大。在一个实施例中,控制器150根据下式定期更新w

ctl

的值:

[0066][0067]

其中,代表w

ctl

更新之前的旧值,而代表w

ctl

更新之后的新值。当s2的工作周期太大(即,do》d

t

)时,e

dc

为1,则控制器150减小w

ctl

的值,使得dcdc 120的传递延迟变小,从而减小了s2的工作周期。当s2的工作周期太小(即,do<d

t

)时,e

dc

为0,则控制器150增加w

ctl

的值,使得dcdc 120的传递延迟变大,从而增加了s2的工作周期。

[0068]

图2a显示可用于实现工作周期检测器140的工作周期检测电路200a的示意图。工作周期检测电路200a包含:低通滤波器210,其包含电阻器211和电容器212;电阻分压器220,其包含电阻器221和电阻器222;以及比较器230。低通滤波器210接收s2并输出平均电压va,平均电压va大约是d

ovdd

。举例来说,如果s2的工作周期为40%,则va约为0.4v

dd

,因为s2在40%的时间内都保持在高准位v

dd

。电阻分压器220输出代表d

t

的目标电压v

t

,d

t

是s2的目标工作周期值。令电阻器221和电阻器222的电阻分别为r

221

和r

222

,则r

221

可以根据下式决定:

[0069][0070]

目标电压v

t

是根据v

dd

的在电阻器221和222上的分压决定的,即:

[0071][0072]

其中应用了方程式(5)。比较器230将va与v

t

进行比较并输出e

dc

,e

dc

指示va是否高于v

t

。当va高于(低于)v

t

时,e

dc

为1(0),这表示d

ovdd

大于(小于)d

tvdd

,因此do大于(小于)d

t

。当do大于(小于)d

t

时,e

dc

为1(0),控制器150减少(增加)w

ctl

的值,从而导致传递延迟td和s2的工作周期减少(增加)。因此,s2的工作周期以闭回路方式被调节,而逐渐等于d

t

。

[0073]

在目标工作周期值d

t

为50%的特殊情况下,图2b中所示的另一种工作周期检测器200b可用来实现图1a的工作周期检测器140。工作周期检测器200b包含:第一低通滤波器240,其包含电阻器241和电容器242;反相器270;第二低通滤波器250,其包含电阻器251和电容器252;以及比较器260。反相器270接收s2并输出互补信号s

′2,s

′2是s2的反相逻辑。由于s2的工作周期为do,所以s

′2的工作周期为1-do(因为s

′2与s2互补)。第一低通滤波器240接收s2并输出第一平均电压v

p

(约等于d

ovdd

)。举例来说,如果s2的工作周期为40%,则v

p

约为0.4v

dd

,因为s2在40%的时间内都保持在高准位v

dd

。第二低通滤波器250接收s

′2,并输出第二平均电压vn(约等于(1-do)v

dd

)。举例来说,如果s2的工作周期为40%,由于s

′2在60%的时间内都保持在高准位v

dd

(因为s

′2与s2互补),因此vn约为0.6v

dd

。比较器260将v

p

与vn进行比较并输出e

dc

,e

dc

指示v

p

是否高于vn。当v

p

高于/低于vn时,e

dc

为1(0),表示d

ovdd

大于/小于(1-do)v

dd

,因此do大于/小于(1-do),而那表示do大于/小于50%。因此,如果目标工作周期值d

t

为50%,则工作周期检测器200b可以对s2进行工作周期检测。

[0074]

比较器(例如图2a的比较器230或图2b的比较器260)是一种接收两个电压并输出一个逻辑信号的电路,逻辑信号指示两个电压中的哪个是较高的,并且该电路可以由电路设计者酌情使用现有技术中已知的任何电路来实现。反相器(例如反相器270)执行逻辑反相,而且反相器在现有技术中是众所周知的,因此这里不再详细描述。

[0075]

图3描绘可用于实现图1a的dcdc 120的数位控制延迟电路300的示意图。数位控制延迟电路300包含:编码器310,编码器310被配置为将w

ctl

编码为多个逻辑控制信号c1、c2、c3、

…

等;以及多个可编程延迟电路(programmable delay circuit,pdc)311、312、313、

…

等,所述可编程延迟电路311、312、313、

…

等分别由所述多个逻辑信号c1、c2、c3、

…

等控制,并且级联(cascaded)形成一个延迟链,该延迟链被配置为接收s2并且输出s4,其中s2的上升缘将沿着延迟链传递,并且在延迟链的末端成为s4的上升缘。如图3所示(作为示例而非限制本发明),其显示七个逻辑控制信号c1、c2、c3、c4、c3、c6及c7,以及七个可编程延迟电路311、312、313、314、315、316及317,该七个可编程延迟电路311、312、313、314、315、316及317级联,并且分别受c1、c2、c3、c4、c3、c6及c7控制。在一个实施例中,可编程延迟电路311、312、313、

…

等都是相同的电路,但是分别由c1、c2、c3、

…

等独立地控制。每个可编程延迟电路引入由其各自的逻辑控制信号所决定的延迟;可编程延迟电路311(312、313、314、315、316、317)引入了由c1(c2、c3、c4、c5、c6、c7)控制的延迟;当c1(c2、c3、c4、c5、c6、c7)为0时,可编程延迟电路311(312、313、314、315、316、317)具有小延迟δ0;当c1(c2、c3、c4、c5、c6、c7)为1时,可编程延迟电路311(312、313、314、315、316、317)具有大延迟δ1,其中δ1大于δ0。在此,“大

延迟”和“小延迟”是相对而言。因此,当dcdc 120由数位控制延迟电路300实现时,dcdc 120的传递延迟是:

[0076]

td=∑

i=1,2,3

,

…

(ciδ1 (1-ci)δ0)

ꢀꢀꢀ

(7)

[0077]

在一个实施例中,编码器310根据“温度计码(thermometer code)”编码方式将w

ctl

编码为c1、c2、c3、

…

等,该编码方式可以由下式描述:

[0078][0079]

其中,i为索引,其值为1、2、3、

…

。对于该包含七个可编程延迟电路的例子来说,编码表如下所示:

[0080]wctl

01234567c101111111c200111111c300011111c400001111c500000111c600000011c700000001

[0081]

随着w

ctl

值的增加,逻辑控制信号c1、c2、c3、

…

等的当中有更多被设为1,使得pdc 311、312、313、

…

等的当中有更多被控制为具有较大的延迟,结果,数位控制延迟电路300的传递延迟增加。

[0082]

pdc 314的一种实施例的示意图显示在细节框cob314之内。pdc 314接收来自pdc 313的输入,并根据逻辑控制信号c4将输出输出到pdc 315。pdc 314包含级联的第一反相器inv1(包含第一nmos晶体管mn1和第一pmos晶体管mp1)和第二反相器inv2(包含第二nmos晶体管mn2和第二pmos晶体管mp2),以及可调电容器pc314(包含电容器cl和一个开关,该开关系以由逻辑控制信号c4所控制的第三nmos晶体管mn3实现)。可调电容器pc314在第一反相器inv1与第二反相器inv2之间的内部节点n314处实现可调电容负载;内部节点n314上的较高电容负载导致信号从pdc 313传递到pdc 315的延迟更大。当c4为1时,第三nmos晶体管mn3导通,可调pc314的电容大约等于电容器cl的电容;当c4为0时,第三nmos晶体管mn3不导通,可调pc314的电容大约为零。如此一来,当c4为0时,pdc 314具有小的延迟,而当c4为1时,pdc 314具有大的延迟。

[0083]

细节框cob314内部的相同电路用于所有其他可编程延迟单元,只是输入,输出和逻辑控制信号不同。

[0084]

一比二分频电路130包含数据触发器(data flip flop,dff)131,其具有数据引脚“d”、输出引脚“q”、互补输出引脚“qb”及以楔形表示的边缘触发引脚。dff 131由s4的上升缘触发,并通过其输出引脚“q”输出s3,同时通过将互补输出引脚“qb”连接到数据引脚“d”形成负反馈。在现有技术中,数据触发器131本身是众所周知的,以及当数据触发器131以如图1a所示的负反馈拓扑配置时可用来实现一比二分频功能也是众所周知的,因此这里不再详细描述。

[0085]

如图4的流程图所示,根据本公开的实施例的倍频方法包含:(步骤410)接收第一时钟,第一时钟具有百分之五十的工作周期并且是一个包含第一相位和第二相位的两相时钟;(步骤420)根据第三时钟通过多工器选择第一时钟的第一相位和第二相位的其中之一以输出第二时钟;(步骤430)使用数位控制延迟电路根据数位字将第二时钟延迟为第四时钟;(步骤440)使用一比二分频电路根据第四时钟输出第三时钟;(步骤450)使用工作周期检测器根据第二时钟的工作周期与目标工作周期值的比较来产生逻辑信号;(步骤460)根据逻辑信号更新数位字。

[0086]

本领域技术人员将容易地观察到,在保持本公开的教导的同时,可以对装置和方法进行多种修改和变更。因此,以上的公开内容不应被解释为仅由权利要求的界限来限定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。