技术特征:

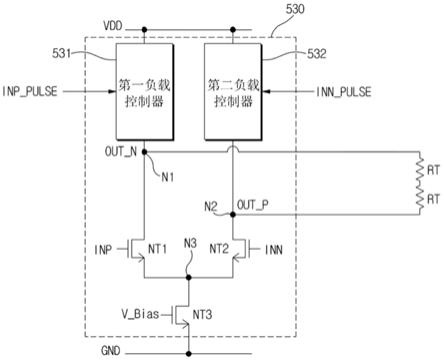

1.一种传输驱动器,包括:脉冲生成器,其被配置成通过在第一输入信号的下降沿时间点处进行同步来生成并输出第一脉冲信号,并且通过在第二输入信号的下降沿时间点处进行同步来生成并输出第二脉冲信号;以及电流模式逻辑驱动器,其被配置成:通过分别基于所述第一脉冲信号和所述第二脉冲信号来改变第一负载电阻值和第二负载电阻值,来输出已经应用了预加重技术的预加重信号。2.根据权利要求1所述的传输驱动器,还包括反相器,所述反相器被配置成接收输入信号并且将所述第一输入信号和所述第二输入信号分别输出至所述脉冲生成器和所述电流模式逻辑驱动器。3.根据权利要求2所述的传输驱动器,其中,所述反相器包括:第一运算放大器,其被配置成通过缓冲所述输入信号来生成所述第一输入信号;以及反相放大器,其包括两个电阻器和第二运算放大器,所述第二运算放大器被配置成通过使所述第一输入信号的相位反相来生成所述第二输入信号。4.根据权利要求1所述的传输驱动器,其中,所述电流模式逻辑驱动器包括:第一nmos晶体管,所述第一nmos晶体管被配置成通过栅极端子接收所述第一输入信号,所述第一nmos晶体管连接在第一输出节点与第三公共节点之间;第二nmos晶体管,所述第二nmos晶体管被配置成通过所述栅极端子接收所述第二输入信号,所述第二nmos晶体管连接在第二输出节点与所述第三公共节点之间;以及第三nmos晶体管,所述第三nmos晶体管串联连接至所述第一nmos晶体管和所述第二nmos晶体管。5.根据权利要求4所述的传输驱动器,其中,根据偏置控制信号使所述第三nmos晶体管导通以使偏置电流流动,从而激活所述电流模式逻辑驱动器。6.根据权利要求5所述的传输驱动器,其中,所述电流模式逻辑驱动器包括:第一负载控制器,所述第一负载控制器连接在所述第一输出节点与电源电压之间,所述第一负载控制器通过接收所述第一脉冲信号来控制所述第一负载电阻值;以及第二负载控制器,所述第二负载控制器连接在所述第二输出节点与所述电源电压之间,所述第二负载控制器通过接收所述第二脉冲信号来控制所述第二负载电阻值。7.根据权利要求6所述的传输驱动器,其中,所述第一负载控制器包括:第一电阻器,其一端连接至所述电源电压并且另一端连接至所述第一输出节点;第一可变电阻器,其一端连接至所述电源电压;以及第一pmos晶体管,其将所述第一脉冲信号连接至栅极端子,将源极端子连接至所述第一可变电阻器的另一端,并且将漏极端子连接至所述第一输出节点。8.根据权利要求7所述的传输驱动器,其中,所述第二负载控制器包括:第二电阻器,其一端连接至所述电源电压并且另一端连接至所述第二输出节点;第二可变电阻器,其一端连接至所述电源电压;以及第二pmos晶体管,其将所述第二脉冲信号连接至栅极端子,将源极端子连接至所述第二可变电阻器的另一端,并且将漏极端子连接至所述第二输出节点。9.根据权利要求8所述的传输驱动器,其中,所述电流模式逻辑驱动器还包括:连接在

所述第一输出节点与所述第二输出节点之间的第三电阻器。10.根据权利要求9所述的传输驱动器,其中,与所述第一输入信号的下降沿时间点同步生成的所述第一脉冲信号具有低电平第一部分,并且其中,与所述第二输入信号的下降沿时间点同步生成的所述第二脉冲信号具有低电平第二部分。11.根据权利要求10所述的传输驱动器,其中,在所述低电平第一部分中,所述第一nmos晶体管和所述第二pmos晶体管被关断,并且所述第二nmos晶体管和所述第一pmos晶体管被导通。12.根据权利要求11所述的传输驱动器,其中,在所述低电平第二部分中,所述第一nmos晶体管和所述第二pmos晶体管被导通,并且所述第二nmos晶体管和所述第一pmos晶体管被关断。13.根据权利要求12所述的传输驱动器,其中,在所述低电平第一部分和所述低电平第二部分中,通过控制所述电流模式逻辑驱动器的所述第一负载电阻值和所述第二负载电阻值来输出所述预加重信号。14.一种电流模式逻辑驱动器,包括:第一负载控制器,所述第一负载控制器由第一脉冲信号控制,所述第一负载控制器连接至电源电压;第二负载控制器,所述第二负载控制器由第二脉冲信号控制,所述第二负载控制器连接至所述电源电压;第一nmos晶体管,其串联连接至所述第一负载控制器;第二nmos晶体管,其串联连接至所述第二负载控制器;以及第三nmos晶体管,其串联连接至所述第一nmos晶体管和所述第二nmos晶体管。15.根据权利要求14所述的电流模式逻辑驱动器,其中,所述第一nmos晶体管和所述第二nmos晶体管被配置成接收具有不同电平的第一输入信号和第二输入信号。16.根据权利要求15所述的电流模式逻辑驱动器,其中,根据偏置控制信号使所述第三nmos晶体管导通以使偏置电流流动。17.根据权利要求16所述的电流模式逻辑驱动器,其中,所述第一负载控制器包括:第一电阻器,其一端连接至所述电源电压并且另一端连接至第一输出节点;第一可变电阻器,其一端连接至所述电源电压;以及第一pmos晶体管,其将所述第一脉冲信号连接至栅极端子,将源极端子连接至所述第一可变电阻器的另一端,并且将漏极端子连接至所述第一输出节点。18.根据权利要求17所述的电流模式逻辑驱动器,其中,所述第二负载控制器包括:第二电阻器,其一端连接至所述电源电压并且另一端连接至第二输出节点;第二可变电阻器,其一端连接至所述电源电压;以及第二pmos晶体管,其将所述第二脉冲信号连接至栅极端子,将源极端子连接至所述第二可变电阻器的另一端,并且将漏极端子连接至所述第二输出节点。19.根据权利要求18所述的电流模式逻辑驱动器,其中,与所述第一输入信号的下降沿时间点同步生成的所述第一脉冲信号具有低电平第一部分,并且其中,与所述第二输入信号的下降沿时间点同步生成的所述第二脉冲信号具有低电平第二部分。20.根据权利要求19所述的电流模式逻辑驱动器,其中,在所述低电平第一部分和所述

低电平第二部分中通过所述第一负载控制器和所述第二负载控制器的可变电阻器控制来输出已经应用了预加重技术的预加重信号。21.一种传输驱动器,包括:脉冲生成器,其被配置成在第一输入信号的下降沿时间点处进行同步以生成第一脉冲信号,并且在第二输入信号的下降沿时间点处进行同步以生成第二脉冲信号;以及电流模式逻辑驱动器,包括:第一负载控制器,所述第一负载控制器由所述第一脉冲信号控制,所述第一负载控制器连接至电源电压;以及第二负载控制器,所述第二负载控制器由所述第二脉冲信号控制,所述第二负载控制器连接至所述电源电压。22.根据权利要求21所述的传输驱动器,其中,所述电流模式逻辑驱动器还包括:串联连接至所述第一负载控制器的第一nmos晶体管;串联连接至所述第二负载控制器的第二nmos晶体管;以及串联连接至所述第一nmos晶体管和所述第二nmos晶体管的第三nmos晶体管。23.根据权利要求21所述的传输驱动器,其中,所述电流模式逻辑驱动器被配置成:通过分别基于所述第一脉冲信号和所述第二脉冲信号来改变第一负载电阻值和第二负载电阻值,来输出已经应用了预加重技术的预加重信号。24.根据权利要求21所述的传输驱动器,还包括反相器,所述反相器被配置成接收输入信号并且将所述第一输入信号和所述第二输入信号分别输出至所述脉冲生成器和所述电流模式逻辑驱动器。25.根据权利要求24所述的传输驱动器,其中,所述反相器包括:第一运算放大器,其被配置成通过缓冲所述输入信号来生成所述第一输入信号;以及反相放大器,其包括两个电阻器和第二运算放大器,所述第二运算放大器被配置成通过使所述第一输入信号的相位反相来生成所述第二输入信号。

技术总结

本申请公开了电流模式逻辑驱动器和包括其的传输驱动器。传输驱动器包括脉冲生成器和电流模式逻辑驱动器。脉冲生成器被配置成通过在第一输入信号的下降沿时间点处进行同步来生成并输出第一脉冲信号,并且通过在第二输入信号的下降沿时间点处进行同步来生成并输出第二脉冲信号。电流模式逻辑驱动器被配置成:通过分别基于第一脉冲信号和第二脉冲信号来改变第一负载电阻值和第二负载电阻值,来输出已经应用了预加重技术的预加重信号。已经应用了预加重技术的预加重信号。已经应用了预加重技术的预加重信号。

技术研发人员:卢吉成 金相更

受保护的技术使用者:美格纳半导体有限公司

技术研发日:2021.05.31

技术公布日:2022/2/23

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。