1.本发明涉及滤波器技术领域,特别是涉及一种滤波器阵列的平滑快速更新方法、系统、介质及装置。

背景技术:

2.数字滤波是数字信号分析中最重要的组成部分之一,数字滤波与模拟滤波相比,具有精度和稳定性高、系统函数容易改变、灵活性高、不存在阻抗匹配问题、便于大规模集成、可实现多维滤波等优点。

3.数字滤波器的作用是利用离散时间系统的特性对输入信号波形(或频谱)进行加工处理,或者说利用数字方法按预定的要求对信号进行变换。把输入序列x(n)变换成一定的输出序列y(n)从而达到改变信号频谱的目的。

4.数字滤波器由数字乘法器bai、加法器和du延时单元组成的一种算法或装置。数字滤波器的功能是对输入离散信号的数字代码进行运算处理,以达到改变信号频谱的目的。

5.数字滤波器有低通、高通、带通、带阻和全通等类型。它可以是时不变的或时变的、因果的或非因果的、线性的或非线性的。应用最广的是线性、时不变数字滤波器,以及f.i.r滤波器。

6.在实现本发明的过程中,发明人发现现有技术至少存在以下问题。

7.对于数字滤波器阵列,为追求更好的效果往往倾向于设计成阶数高、数量大、采样频率高。更新其状态的所需计算量相当大,会推高硬件成本,增加发热和减少电池续航。

8.因此,希望能够解决如何减少计算量、降低硬件成本的问题。

技术实现要素:

9.鉴于以上所述现有技术的缺点,本发明的目的在于提供一种滤波器阵列的平滑快速更新方法、系统、介质及装置,用于解决现有技术中如何减少计算量、降低硬件成本的问题。

10.为实现上述目的及其他相关目的,本发明提供一种滤波器阵列的平滑快速更新方法,包括以下步骤:将滤波器阵列中的滤波器按照滤波器的通带上界从高到底排列,将排列后的滤波器按照通带上界划分为n个分组,记为[g1,g2,...,gn];将滤波器组gi的频率设计参数扩大m

i-1

倍,m为整数,m≥2;i为整数,i∈[1,n];构造n-1个降采样抗混叠滤波器记为[d2,d3,...,dn],降采样抗混叠滤波器dr的降采样倍数为m

r-1

倍,其中r为整数,r∈[2,n];将原始输入的时域离散信号s的每个采样输入所有的dr;将s中的每个采样输入滤波器组g1;当将s中的第m

r-2

*(1 k*m)个采样输入给dr后,将dr的输出输入给gi,其中k是整数,k∈[0,∞)。

[0011]

于本发明的一实施例中,所述滤波器为低通或带通滤波器。

[0012]

于本发明的一实施例中,所述滤波器组gi的包含的滤波器通带上界区间为其中i为整数,i∈[1,n-1],m为整数,m≥2,fs为原始输入的时域离散信

号的采样率。gn包含所有其余的滤波器。

[0013]

为实现上述目的,本发明还提供一种滤波器阵列的平滑快速更新系统,包括:原始输入模块、划分模块、参数扩大模块、构造模块和输入模块;所述划分模块用于将滤波器阵列中的滤波器按照滤波器的通带上界从高到底排列,将排列后的滤波器按照通带上界划分为n个分组,记为[g1,g2,...,gn];所述参数扩大模块用于将滤波器组gi的频率设计参数扩大m

i-1

倍,m为整数,m≥2;i为整数,i∈[1,n];所述构造模块用于构造n-1个降采样抗混叠滤波器记为[d2,d3,...,dn],降采样抗混叠滤波器dr的降采样倍数为m

r-1

倍,其中r为整数,r∈[2,n];所述输入模块用于将原始输入的时域离散信号s的每个采样输入所有的dr;将s的每个采样输入滤波器组g1;当将s中的第m

r-2

*(1 k*m)个采样输入给dr后,将dr的输出输入给gi,其中k是整数,k∈[0,∞)。

[0014]

于本发明的一实施例中,所述滤波器为低通或带通滤波器。

[0015]

于本发明的一实施例中,所述滤波器组gi的包含的滤波器通带上界区间为其中i为整数,i∈[1,n-1],m为整数,m≥2,fs为原始输入的时域离散信号的采样率。gn包含所有其余的滤波器。

[0016]

为实现上述目的,本发明还提供一种计算机可读存储介质,其上存储有计算机程序,所述计算机程序被处理器执行时实现任一上述滤波器阵列的平滑快速更新方法。

[0017]

为实现上述目的,本发明还提供一种滤波器阵列的平滑快速更新装置,包括:处理器和存储器;所述存储器用于存储计算机程序;所述处理器与所述存储器相连,用于执行所述存储器存储的计算机程序,以使所述滤波器阵列的平滑快速更新装置执行任一上述的滤波器阵列的平滑快速更新方法。

[0018]

如上所述,本发明的一种滤波器阵列的平滑快速更新方法、系统、介质及装置,具有以下有益效果:减少滤波器阵列的计算需求,减少硬件成本。

附图说明

[0019]

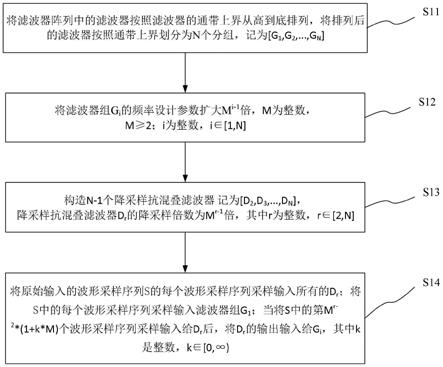

图1显示为本发明的滤波器阵列的平滑快速更新方法于一实施例中的流程图;

[0020]

图2显示为本发明的滤波器阵列的平滑快速更新系统于一实施例中的结构示意图;

[0021]

图3显示为本发明的滤波器阵列的平滑快速更新装置于一实施例中的结构示意图。

[0022]

元件标号说明

[0023]

21

ꢀꢀꢀꢀꢀꢀꢀ

原始输入模块

[0024]

22

ꢀꢀꢀꢀꢀꢀꢀ

划分模块

[0025]

23

ꢀꢀꢀꢀꢀꢀꢀ

参数扩大模块

[0026]

24

ꢀꢀꢀꢀꢀꢀꢀ

构造模块

[0027]

25

ꢀꢀꢀꢀꢀꢀꢀ

输入模块

[0028]

31

ꢀꢀꢀꢀꢀꢀꢀ

处理器

[0029]

32

ꢀꢀꢀꢀꢀꢀꢀ

存储器

具体实施方式

[0030]

以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书

所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。需说明的是,在不冲突的情况下,以下实施例及实施例中的特征可以相互组合。

[0031]

需要说明的是,以下实施例中所提供的图示仅以示意方式说明本发明的基本构想,故图式中仅显示与本发明中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的型态、数量及比例可为一种随意的改变,且其组件布局型态也可能更为复杂。

[0032]

本发明的滤波器阵列的平滑快速更新方法、系统、介质及装置,用于减少滤波器阵列的计算需求,减少硬件成本。

[0033]

如图1所示,于一实施例中,本发明的滤波器阵列的平滑快速更新方法,包括以下步骤:

[0034]

具体地,原始输入的时域离散信号记为s,其采样率记为fs。

[0035]

具体地,所述时域离散信号(discrete-timesignal),即只在一系列分离的时间点n(n是整数,n=0,

±

1,

±

2,

……

)上才有取值的一种信号。也称离散时间信号序列。时域离散信号可以用一个离散时间的数字序列来表示。因为现实世界里存在的是模拟信号,因此数字信号处理的第一个问题是将信号离散化(取样),然后进行量化编码,最后进行数字处理。将连续信号变成离散信号的常用方法是等间隔或不等间隔周期t取样。其中t称为取样周期,t的倒数称为取样频率或取样率fs。

[0036]

步骤s11、将滤波器阵列中的滤波器按照滤波器的通带上界从高到底排列,将排列后的滤波器按照通带上界划分为n个分组,记为[g1,g2,...,gn];

[0037]

具体地,所述滤波器为低通椭圆滤波器。椭圆低通滤波器是一种零、极点型滤波器,它在有限频率范围内存在传输零点和极点。椭圆低通滤波器的通带和阻带都具有等波纹特性,因此通带,阻带逼近特性良好。对于同样的性能要求,它比其他滤波器所需用的阶数都低,而且它的过渡带比较窄。

[0038]

具体地,所述滤波器按照通带上界划分为n个分组为在预设音高范围内划分成n组。例如,在[c2,c10)音高范围内,划分为8组。在[c2,c10)音高范围内,每25音分设置滤波器,共384个滤波器。所有滤波器的通带占比都是50音分,apass(通带波纹)都是3db,astop(阻带衰减)都是80db。将384个滤波器按照2倍频,划分成8组:

[0039]

g1音高范围[c9,c10),含48个滤波器。

[0040]

g2音高范围[c8,c9),含48个滤波器。

[0041]

……

[0042]

g8音高范围[c2,c3),含48个滤波器。

[0043]

具体地,所述滤波器组gi的通带上界区间为m为整数,m≥2,fs为原始输入的时域离散信号的采样率。当滤波器的通带上界(说通带指的是个频率区间,区间的端点还是频率,所以这个上界是个频率数值)及可接受的过渡带(还是个频率范围)低于采样频率的一半,则可以用降采样后的信号(采样率降低了)取代原始信号(降采样操作是同步的,并不是生成了一个完全无关的另一信号)输入给滤波器,以求降低计算量(因为采

样率更低了,而数字滤波器的计算量是正比于采样个数的)。

[0044]

步骤s12、将滤波器组gi的频率设计参数扩大m

i-1

倍,m为整数,m≥2;i为整数,i∈[1,n]。因为降低了输入给滤波器的采样率,滤波器的各种频率设计参数也需要相应的提高。采样率降低到了原始采样率的1/m,则滤波器参数就要提高到原来的m倍。gi指代[g1,g2,...,gn]中的具体一个。

[0045]

步骤s13、构造n-1个降采样抗混叠滤波器记为[d2,d3,...,dn],降采样抗混叠滤波器dr的降采样倍数为m

r-1

倍,其中r为整数,r∈[2,n]。

[0046]

具体地,由于非整数倍的降采样会带来显著的额外计算开销,没有实用价值,所以本专利表述中仅使用整数倍的降采样。降采样会产生一个被称为术语

‘

混叠’的现象,降采样抗混叠滤波器可被视为一个处理混叠问题的黑盒。内部是个低通滤波器。dr指代[d2,d3,...,dn]中任意一个。

[0047]

步骤s14、将原始输入的时域离散信号s的每个采样输入所有的dr;将s中的每个采样输入滤波器组g1;当将s中的第m

r-2

*(1 k*m)个采样输入给dr后,将dr的输出输入给gi,其中k是整数,k∈[0,∞)。

[0048]

具体地,将s的每个采样输入所有的di,其中i为整数,i∈[2,n]。即将s的每个采样输入所有的d2,d3,...,dn。

[0049]

将s的每个采样输入滤波器组g1。

[0050]

具体地,将s的每个采样依次输入滤波器组g1。

[0051]

当将s中的第m

r-2

*(1 k*m)个采样输入给dr后,将dr的输出输入给gi,其中k是整数,k∈[0,∞)。

[0052]

具体地,将dr的输出输入给gi,中的r和i为同一个数字。即将d3的输出输入给g3。而滤波器阵列的平滑快速更新方法能够在不影响功能的情况下,大幅提高计算速度,并且能够流式计算。降低硬件成本,减少发热和增加电池续航。

[0053]

具体地,所述滤波器为低通或带通滤波器。

[0054]

具体地,不同滤波器更新其输出的频率不同(这里频率是相对于原始输入的,或者说输入的离散时域信号的采样率的,例如:每个输入样本更新1次,每2个输入样本更新一次,每4个输入样本更新一次等等),这样就有了峰谷调配的空间。

[0055]

具体地,于一实施例中,音乐音频的处理如下,在[c2,c10)音高范围内,每25音分设置滤波器,共384个滤波器。所有滤波器的通带占比都是50音分,apass都是3db,astop都是80db。

[0056]

将384个滤波器按照2倍频,划分成8组:

[0057]

g1音高范围[c9,c10),含48个滤波器。

[0058]

g2音高范围[c8,c9),含48个滤波器。

[0059]

……

[0060]

g8音高范围[c2,c3),含48个滤波器。

[0061]

由于频率的等比关系,[g2~g8]数字滤波器组的系数都与g1相同,因此系数都使用g1的系数。

[0062]

设置7个降采样器记为[d2~d8],每个内涵一个6阶低通椭圆滤波器。低通滤波器每采样更新。降采样倍数分别为[2,4,8,16,32,64,128]。降采样器输出的信号记为[s2~

s8]。原始未经降采样的序号记为s1。

[0063]

g1组每采样更新。每采样按如下周期为128的序列依次读一个序号,在[g2~g8]中选取对应序号的那组更新。

[0064]

[2,3,2,4,2,3,2,5,2,3,2,4,2,3,2,6,2,3,2,4,2,3,2,5,2,3,2,4,2,3,2,7,2,3,2,4,2,3,2,5,2,3,2,4,2,3,2,6,2,3,2,4,2,3,2,5,2,3,2,4,2,3,2,8,2,3,2,4,2,3,2,5,2,3,2,4,2,3,2,6,2,3,2,4,2,3,2,5,2,3,2,4,2,3,2,7,2,3,2,4,2,3,2,5,2,3,2,4,2,3,2,6,2,3,2,4,2,3,2,5,2,3,2,4,2,3,2,轮空]。

[0065]

具体地,本发明的时间复杂度从o(n)直接优化到了o(1)。处理每一个采样所需的计算量有一个很小的上界,不会有峰谷问题。将滤波器阵列,按m倍频关系划分成n个分组,例如每组滤波器的更新开销设为单位1,则未采用本发明的原始计算开销cost

orig

=n。本发明计算开销有界。不论传感器阵列有多长,其计算开销小于一个定值。对于2倍频分组,计算开销小于2组;对于3倍频分组,计算开销小于1.5组。加速比大于n*(m-1)/m,阵列越长,加速比越大。若滤波器组的频率参数是等比关系,其他参数相同,则可共用最高频组的滤波器参数。

[0066]

如图2所示,于一实施例中,本发明的滤波器阵列的平滑快速更新系统,划分模块21、参数扩大模块22、构造模块23和输入模块24。

[0067]

所述划分模块21用于将滤波器阵列中的滤波器按照滤波器的通带上界从高到底排列,将排列后的滤波器按照通带上界划分为n个分组,记为[g1,g2,...,gn]。

[0068]

所述参数扩大模块22用于将滤波器组gi的频率设计参数扩大m

i-1

倍,m为整数,m≥2;i为整数,i∈[1,n]。

[0069]

所述构造模块23用于构造n-1个降采样抗混叠滤波器记为[d2,d3,...,dn],降采样抗混叠滤波器dr的降采样倍数为m

r-1

倍,其中r为整数,r∈[2,n]。

[0070]

所述输入模块24用于将原始输入的时域离散信号s的每个采样输入所有的dr;将s中的每个采样输入滤波器组g1;当将s中的第m

r-2

*(1 k*m)个采样输入给dr后,将dr的输出输入给gi,其中k是整数,k∈[0,∞)。

[0071]

具体地,所述滤波器为低通或带通滤波器。

[0072]

具体地,所述滤波器按照通带上界划分为n个分组为在预设音高范围内划分成n组。

[0073]

具体地,所述滤波器组gi的包含的滤波器通带上界区间为其中i为整数,i∈[1,n-1],m为整数,m≥2,fs为原始输入的时域离散信号的采样率。gn包含所有其余的滤波器。

[0074]

需要说明的是,划分模块21、参数扩大模块22、构造模块23和输入模块24的结构和原理与上述滤波器阵列的平滑快速更新方法中的步骤一一对应,故在此不再赘述。

[0075]

需要说明的是,应理解以上系统的各个模块的划分仅仅是一种逻辑功能的划分,实际实现时可以全部或部分集成到一个物理实体上,也可以物理上分开。且这些模块可以全部以软件通过处理元件调用的形式实现;也可以全部以硬件的形式实现;还可以部分模块通过处理元件调用软件的形式实现,部分模块通过硬件的形式实现。例如,x模块可以为

单独设立的处理元件,也可以集成在上述装置的某一个芯片中实现,此外,也可以以程序代码的形式存储于上述装置的存储器中,由上述装置的某一个处理元件调用并执行以上x模块的功能。其它模块的实现与之类似。此外这些模块全部或部分可以集成在一起,也可以独立实现。这里所述的处理元件可以是一种集成电路,具有信号的处理能力。在实现过程中,上述方法的各步骤或以上各个模块可以通过处理器元件中的硬件的集成逻辑电路或者软件形式的指令完成。

[0076]

例如,以上这些模块可以是被配置成实施以上方法的一个或多个集成电路,例如:一个或多个特定集成电路(application specific integrated circuit,简称asic),或,一个或多个微处理器(micro processor uint,简称mpu),或,一个或者多个现场可编程门阵列(field programmable gate array,简称fpga)等。再如,当以上某个模块通过处理元件调度程序代码的形式实现时,该处理元件可以是通用处理器,例如中央处理器(central processing unit,简称cpu)或其它可以调用程序代码的处理器。再如,这些模块可以集成在一起,以片上系统(system-on-a-chip,简称soc)的形式实现。

[0077]

于本发明一实施例中,本发明还包括一种计算机可读存储介质,其上存储有计算机程序,该程序被处理器执行时实现上述任一所述滤波器阵列的平滑快速更新方法。

[0078]

本领域普通技术人员可以理解:实现上述各方法实施例的全部或部分步骤可以通过计算机程序相关的硬件来完成。前述的计算机程序可以存储于一计算机可读存储介质中。该程序在执行时,执行包括上述各方法实施例的步骤;而前述的存储介质包括:rom、ram、磁碟或者光盘等各种可以存储程序代码的介质。

[0079]

如图3所示,于一实施例中,本发明的滤波器阵列的平滑快速更新装置包括:处理器31和存储器32;所述存储器32用于存储计算机程序;所述处理器31与所述存储器32相连,用于执行所述存储器32存储的计算机程序,以使所述滤波器阵列的平滑快速更新装置执行任一所述的滤波器阵列的平滑快速更新方法。

[0080]

具体地,所述存储器32包括:rom、ram、磁碟、u盘、存储卡或者光盘等各种可以存储程序代码的介质。

[0081]

优选地,所述处理器31可以是通用处理器,包括中央处理器(central processing unit,简称cpu)、网络处理器(network processor,简称np)等;还可以是数字信号处理器(digital signal processor,简称dsp)、专用集成电路(application specific integrated circuit,简称asic)、现场可编程门阵列(field programmable gate array,简称fpga)或者其他可编程逻辑器件、分立门或者晶体管逻辑器件、分立硬件组件。

[0082]

综上所述,本发明滤波器阵列的平滑快速更新方法、系统、介质及装置,减少滤波器阵列的计算需求,减少硬件成本。所以,本发明有效克服了现有技术中的种种缺点而具高度产业利用价值。

[0083]

上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,举凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。