1.本发明涉及显示装置,更详细地涉及包括多个晶体管的显示装置。

背景技术:

2.随着显示装置的小型化,为了增加显示区域的大小,要最小化显示区域的外围部即边框(bezel)区域的努力在继续。一般来说,由于在相当于非显示区域的边框区域中配置用于驱动显示装置的布线以及驱动电路,在最小化边框区域的方面存在局限。因此,通过减小显示装置的薄膜晶体管的大小,谋求显示装置的小型化的研究正在进行。

3.但是,随着显示装置的驱动频率增加或者分辨率增加,薄膜晶体管的驱动电压确保变难,可能产生对薄膜晶体管进行充电的时间变短的问题。

技术实现要素:

4.本发明的技术问题着眼于这些方面,本发明的目的在于提供显示质量得到改善的显示装置。

5.但是,本发明所要解决的问题不限于上述提及的问题,可以在不脱离本发明的构思以及领域的范围内进行各种扩展。

6.可以是,用于实现上述本发明的目的的根据一实施例的显示装置包括像素,所述像素包括像素驱动晶体管以及像素开关晶体管,所述像素驱动晶体管包括:第一有源层,用第三族元素掺杂,并包括具有第一长度的第一沟道区域;第一栅极绝缘层,配置在所述第一有源层上;第一栅极电极,配置在所述第一栅极绝缘层上;第一源极电极,配置在所述第一栅极电极上,并与所述第一有源层的源极区域连接;以及第一漏极电极,配置在所述第一栅极电极上,并与所述第一有源层的漏极区域连接。另外,可以是,所述像素开关晶体管包括:第二有源层,用第五族元素掺杂,并包括具有比所述第一长度短的第二长度的第二沟道区域;第二栅极绝缘层,配置在所述第二有源层上;第二栅极电极,配置在所述第二栅极绝缘层上;第二源极电极,配置在所述第二栅极电极上,并与所述第二有源层的源极区域连接;以及第二漏极电极,配置在所述第二栅极电极上,并与所述第二有源层的漏极区域连接。在此,可以是,所述像素驱动晶体管以及所述像素开关晶体管是pmos晶体管。

7.在实施例中,可以是,所述第一栅极绝缘层和所述第二栅极绝缘层配置于相同的层,所述第一栅极绝缘层是包括氧化硅系物质的单层,所述第二栅极绝缘层是包括第2

‑

1栅极绝缘层以及第2

‑

2栅极绝缘层的多层,所述第2

‑

1栅极绝缘层包括所述氧化硅系物质,所述第2

‑

2栅极绝缘层配置在所述第2

‑

1栅极绝缘层上,并包括氮化硅系物质。

8.在实施例中,可以是,所述第一长度是10um至30um,所述第二长度是1um至5um。

9.在实施例中,可以是,所述像素还包括:电容电极,配置在所述第一栅极电极上,并配置于所述第一源极电极以及所述第一漏极电极之下。

10.在实施例中,可以是,所述像素还包括:有机发光二极管,与所述像素驱动晶体管连接,所述有机发光二极管包括:下部电极,与所述第一漏极电极连接;中间层,配置在所述

下部电极上;以及上部电极,配置在所述中间层上。

11.在实施例中,可以是,所述显示装置还包括:扫描驱动部,将扫描信号提供于所述像素,并包括扫描缓冲晶体管以及扫描电路晶体管,所述扫描电路晶体管包括:第三有源层,用所述第三族元素掺杂,并包括具有所述第一长度的第三沟道区域;第三栅极绝缘层,配置在所述第三有源层上;第三栅极电极,配置在所述第三栅极绝缘层上;第三源极电极,配置在所述第三栅极电极上,并与所述第三有源层的源极区域连接;以及第三漏极电极,配置在所述第三栅极电极上,并与所述第三有源层的漏极区域连接。另外,所述扫描缓冲晶体管包括:第四有源层,用所述第五族元素掺杂,并包括具有所述第二长度的第四沟道区域;第四栅极绝缘层,配置在所述第四有源层上;第四栅极电极,配置在所述第四栅极绝缘层上;第四源极电极,配置在所述第四栅极电极上,并与所述第四有源层的源极区域连接;以及第四漏极电极,配置在所述第四栅极电极上,并与所述第四有源层的漏极区域连接。

12.在实施例中,可以是,所述第三栅极绝缘层是包括氧化硅系物质的单层,所述第四栅极绝缘层是包括第4

‑

1栅极绝缘层以及第4

‑

2栅极绝缘层的多层,所述第4

‑

1栅极绝缘层包括所述氧化硅系物质,所述第4

‑

2栅极绝缘层配置在所述第4

‑

1栅极绝缘层上,并包括氮化硅系物质。

13.在实施例中,可以是,所述扫描缓冲晶体管连接于所述扫描驱动部的扫描信号输出部。

14.在实施例中,可以是,所述扫描电路晶体管配置在所述扫描缓冲晶体管上。

15.在实施例中,可以是,所述显示装置还包括:发光驱动部,将发光控制信号提供于所述像素,并包括发光缓冲晶体管以及发光电路晶体管,所述发光电路晶体管包括:第五有源层,用所述第三族元素掺杂,并包括具有所述第一长度的第五沟道区域;第五栅极绝缘层,配置在所述第五有源层上;第五栅极电极,配置在所述第五栅极绝缘层上;第五源极电极,配置在所述第五栅极电极上,并与所述第五有源层的源极区域连接;以及第五漏极电极,配置在所述第五栅极电极上,并与所述第五有源层的漏极区域连接。另外,所述发光缓冲晶体管包括:第六有源层,用所述第五族元素掺杂,并包括具有所述第二长度的第六沟道区域;第六栅极绝缘层,配置在所述第六有源层上;第六栅极电极,配置在所述第六栅极绝缘层上;第六源极电极,配置在所述第六栅极电极上,并与所述第六有源层的源极区域连接;以及第六漏极电极,配置在所述第六栅极电极上,并与所述第六有源层的漏极区域连接。

16.在实施例中,可以是,所述第五栅极绝缘层是包括氧化硅系物质的单层,所述第六栅极绝缘层是包括第6

‑

1栅极绝缘层以及第6

‑

2栅极绝缘层的多层,所述第6

‑

1栅极绝缘层包括所述氧化硅系物质,所述第6

‑

2栅极绝缘层配置在所述第6

‑

1栅极绝缘层上,并包括氮化硅系物质。

17.在实施例中,可以是,所述发光缓冲晶体管连接于所述发光驱动部的发光控制信号输出部。

18.在实施例中,可以是,所述发光电路晶体管配置在所述发光缓冲晶体管上。

19.在实施例中,可以是,所述像素开关晶体管配置在所述像素驱动晶体管上。

20.在实施例中,可以是,所述第一栅极绝缘层是包括氧化硅系物质的单层,所述第二栅极绝缘层是包括第2

‑

1栅极绝缘层以及第2

‑

2栅极绝缘层的多层,所述第2

‑

1栅极绝缘层

包括所述氧化硅系物质,所述第2

‑

2栅极绝缘层配置在所述第2

‑

1栅极绝缘层上,并包括氮化硅系物质。

21.在实施例中,可以是,所述像素还包括:有机发光二极管,与所述像素驱动晶体管连接,所述有机发光二极管包括:下部电极,与所述第一漏极电极连接;中间层,配置在所述下部电极上;以及上部电极,配置在所述中间层上。

22.在实施例中,可以是,所述像素驱动晶体管还包括:连接电极,配置于所述第一栅极电极和所述第一漏极电极之间,所述连接电极连接所述第一漏极电极和所述第一有源层的所述漏极区域。

23.在实施例中,可以是,所述连接电极与所述第一栅极电极重叠。

24.在实施例中,可以是,所述像素驱动晶体管与所述像素开关晶体管至少一部分重叠。

25.可以是,用于实现上述的本发明的目的的根据一实施例的显示装置包括像素,所述像素包括像素驱动晶体管以及像素开关晶体管,所述像素驱动晶体管包括:第一有源层,用第五族元素掺杂,并包括具有第一长度的第一沟道区域;第一栅极绝缘层,配置在所述第一有源层上;第一栅极电极,配置上所述第一栅极绝缘层上;第一源极电极,配置在所述第一栅极电极上,并与所述第一有源层的源极区域连接;以及第一漏极电极,配置在所述第一栅极电极上,并与所述第一有源层的漏极区域连接。另外,可以是,所述像素开关晶体管包括:第二有源层,用第三族元素掺杂,并包括具有比所述第一长度短的第二长度的第二沟道区域;第二栅极绝缘层,配置在所述第二有源层上;第二栅极电极,配置在所述第二栅极绝缘层上;第二源极电极,配置在所述第二栅极电极上,并与所述第二有源层的源极区域连接;以及第二漏极电极,配置在所述第二栅极电极上,并与所述第二有源层的漏极区域连接。在此,可以是,所述像素驱动晶体管以及所述像素开关晶体管是nmos晶体管。

26.(发明的效果)

27.根据本发明的实施例的显示装置可以包括:像素驱动晶体管,用第三族元素掺杂,并包括具备具有第一长度的第一沟道区域的第一有源层以及配置在第一有源层上且以单层构成的第一栅极绝缘层;以及像素开关晶体管,用第五族元素掺杂,并包括具备具有比第一长度短的第二长度的第二沟道区域的第二有源层以及配置在第二有源层上且以多层构成的第二栅极绝缘层。

28.由此,能够将驱动像素的像素驱动晶体管的驱动电压范围确保得宽,能够确保像素开关晶体管的充电时间,并延迟导通/截止时所需的反应时间。

29.但是,本发明的效果不限于上述效果,可以在不脱离本发明的构思以及领域的范围内进行各种扩展。

附图说明

30.图1是示出根据本发明的实施例的显示装置的框图。

31.图2是示出包括在图1的像素中的像素电路以及有机发光二极管的电路图。

32.图3是示出配置于图1的显示装置的晶体管的一实施例的截面图。

33.图4是示出配置于图1的显示装置的晶体管的一实施例的截面图。

34.图5是示出配置于图1的扫描驱动部的扫描电路的一实施例的电路图。

35.图6是示出配置于图1的发光驱动部的发光电路的一实施例的电路图。

36.图7是示出配置于图1的扫描驱动部以及发光驱动部的晶体管的一实施例的截面图。

37.(附图标记)

38.100:显示装置

ꢀꢀꢀꢀꢀꢀ

110:显示部

39.120:时序控制部

ꢀꢀꢀꢀ

130:数据驱动部

40.140:扫描驱动部

ꢀꢀꢀꢀ

150:发光驱动部

41.230a,430,850:第一有源层

42.230b,490,915:第二有源层

43.240a,440,840:第一栅极绝缘层

44.240d,510,900:第二栅极绝缘层

45.sw_tft1,sw_tft2:第一以及第二像素开关晶体管

46.dr_tft1,dr_tft2:第一以及第二像素驱动晶体管

47.buf_tft:缓冲晶体管

48.circuit_tft:电路晶体管

具体实施方式

49.以下,参照所附的附图,更详细地说明本发明的实施例。针对附图中的相同的构成要件,使用相同的附图标记,省略针对相同的构成要件的重复说明。

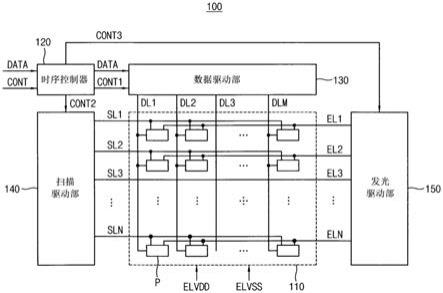

50.图1是示出根据本发明的实施例的显示装置的框图。

51.参照图1,所述显示装置100可以包括显示部110、时序控制器120、数据驱动部130、扫描驱动部140以及发光驱动部150。

52.所述显示部110可以包括多个像素p。所述多个像素p可以与多个扫描线sl1、

…

、sln、多个数据线dl1、

…

、dlm以及多个发光控制线el1、

…

、eln连接(n以及m是自然数)。

53.所述数据线dl1、

…

、dlm可以连接于所述数据驱动部130而将数据电压传送于所述像素p。所述扫描线sl1、

…

、sln可以与所述扫描驱动部140连接而将扫描信号传送于所述像素p。所述发光控制线el1、

…

、eln可以连接于所述发光驱动部150而将发光控制信号传送于所述像素p。

54.所述像素p可以接收第一电源电压elvdd以及第二电源电压elvss。所述像素p可以响应所述扫描信号而接收所述数据电压。所述像素p可以利用所述第一电源电压elvdd以及所述第二电源电压elvss产生与所述数据电压对应的灰度的光。

55.所述时序控制器120可以从外部装置接收数据信号data以及控制信号cont。在实施例中,所述数据信号data可以包括红色、绿色以及蓝色图像数据。所述控制信号cont可以包括水平同步信号、垂直同步信号、主时钟信号等。

56.所述时序控制器120可以将所述数据信号data以所述显示部110的像素结构以及分辨率等之类的规格作为基准进行变换并输出到所述数据驱动部130。

57.所述时序控制器120可以基于所述控制信号cont生成用于驱动所述数据驱动部130的第一控制信号cont1、用于驱动所述扫描驱动部140的第二控制信号cont2以及用于驱动所述发光驱动部150的第三控制信号cont3。

58.所述数据驱动部130可以响应所述第一控制信号cont1将所述数据信号data转换为所述数据电压,将所述数据电压输出到所述数据线dl1、

…

、dlm。

59.所述扫描驱动部140可以响应所述第二控制信号cont2生成多个扫描信号。所述发光驱动部150可以响应所述第三控制信号cont3生成多个发光控制信号。

60.图2是示出包括在图1的像素p中的像素电路以及有机发光二极管的电路图。

61.参照图1以及图2,各个所述像素p可以包括像素电路以及有机发光二极管oled。所述像素电路可以包括第一晶体管至第七晶体管tr1、tr2、tr3、tr4、tr5、tr6、tr7以及存储电容器cst、第一电源电压elvdd布线、第二电源电压elvss布线、初始化电压vint布线、数据信号data布线、扫描信号gw布线、数据初始化信号gi布线、发光控制信号em布线、二极管初始化信号gb布线。所述像素电路可以连接于有机发光二极管oled。

62.所述有机发光二极管oled可以基于驱动电流id发出光。所述有机发光二极管oled可以包括第一端子以及第二端子。在实施例中,所述有机发光二极管oled的第二端子可以接收第二电源电压elvss的供应。例如,可以是,所述有机发光二极管oled的第一端子为正极端子,所述有机发光二极管oled的第二端子为负极端子。选择性地,也可以是,所述有机发光二极管oled的第一端子为负极端子,所述有机发光二极管oled的第二端子为正极端子。

63.所述第一晶体管tr1可以包括栅极端子、第一端子以及第二端子。在实施例中,可以是,所述第一晶体管tr1的第一端子为源极端子,所述第一晶体管tr1的第二端子为漏极端子。选择性地,可以是,所述第一晶体管tr1的第一端子为漏极端子,所述第一晶体管tr1的第二端子为源极端子。在以下叙述的第二晶体管至第七晶体管tr2、tr3、tr4、tr5、tr6、tr7中也可以相同地适用。因此,以下省略与此相关的说明。

64.所述第一晶体管tr1可以生成驱动电流id。在实施例中,所述第一晶体管tr1可以被定义为用于驱动像素的像素驱动晶体管。所述第一晶体管tr1可以基于所述栅极端子和所述源极端子之间的电压差生成所述驱动电流id。另外,可以基于供应于所述有机发光二极管oled的所述驱动电流id的大小,在所述像素p中呈现灰度。

65.所述第二晶体管tr2可以包括栅极端子、第一端子以及第二端子。所述第二晶体管tr2的栅极端子可以接收扫描信号gw的供应。所述第二晶体管tr2的第一端子可以接收数据电压v_data的供应。所述第二晶体管tr2的第二端子可以连接于第一晶体管tr1的第一端子。

66.所述第二晶体管tr2可以在所述扫描信号gw的激活区间期间将所述数据电压v_data供应给所述第一晶体管tr1的第一端子。

67.所述第三晶体管tr3可以包括栅极端子、第一端子以及第二端子。所述第三晶体管tr3的栅极端子可以接收所述扫描信号gw的供应。所述第三晶体管tr3的第一端子可以连接于所述第一晶体管tr1的栅极端子。所述第三晶体管tr3的第二端子可以连接于所述第一晶体管tr1的第二端子。

68.所述第三晶体管tr3可以在所述扫描信号gw的激活区间期间连接所述第一晶体管tr1的栅极端子和所述第一晶体管tr1的第二端子。所述第三晶体管tr3可以在所述扫描信号gw的激活区间期间使所述第一晶体管tr1二极管连接。由于所述第一晶体管tr1二极管连接,可以在所述第一晶体管tr1的第一端子和所述第一晶体管tr1的栅极端子之间产生所述

第一晶体管tr1的阈值电压大小的电压差。其结果,在所述扫描信号gw的激活区间期间,在供应于所述第一晶体管tr1的第一端子的所述数据电压v_data相加所述电压差(即,阈值电压)的电压可以供应于所述第一晶体管tr1的栅极端子。即,所述数据电压v_data可以补偿所述第一晶体管tr1的阈值电压,被补偿的所述数据电压v_data可以供应于所述第一晶体管tr1的栅极端子。

69.所述第四晶体管tr4可以包括栅极端子、第一端子以及第二端子。在此,所述第四晶体管tr4的栅极端子可以接收数据初始化信号gi的供应。所述第四晶体管tr4的第一端子可以接收所述初始化电压vint的供应。所述第四晶体管tr4的第二端子可以连接于所述第一晶体管tr1的栅极端子。

70.所述第四晶体管tr4可以在所述数据初始化信号gi的激活区间期间将所述初始化电压vint供应于所述第一晶体管tr1的栅极端子。即,所述第四晶体管tr4可以在所述数据初始化信号gi的激活区间期间使得所述第一晶体管tr1的栅极端子初始化为所述初始化电压vint。

71.所述第五晶体管tr5可以在所述发光控制信号em的激活区间期间将所述第一电源电压elvdd供应于所述第一晶体管tr1的第一端子。与此相反,所述第五晶体管tr5可以在所述发光控制信号em的非激活区间期间切断所述第一电源电压elvdd的供应。所述第五晶体管tr5在所述发光控制信号em的激活区间期间将所述第一电源电压elvdd供应于所述第一晶体管tr1的第一端子,从而所述第一晶体管tr1可以生成所述驱动电流id。另外,所述第五晶体管tr5在所述发光控制信号em的非激活区间期间切断所述第一电源电压elvdd的供应,从而供应到所述第一晶体管tr1的第一端子的所述数据电压v_data可以向所述第一晶体管tr1的栅极端子供应。

72.所述第六晶体管tr6可以包括栅极端子、第一端子以及第二端子。所述第六晶体管tr6的栅极端子可以接收所述发光控制信号em的供应。所述第六晶体管tr6的第一端子可以连接于所述第一晶体管tr1的第二端子。所述第六晶体管tr6的第二端子可以连接于所述有机发光二极管oled的第一端子。

73.所述第六晶体管tr6可以在所述发光控制信号em的激活区间期间将所述驱动电流id供应于所述有机发光二极管oled。所述第六晶体管tr6在所述发光控制信号em的激活区间期间将所述驱动电流id供应于所述有机发光二极管oled,从而所述有机发光二极管oled可以输出光。另外,所述第六晶体管tr6可以在所述发光控制信号em的非激活区间期间使得所述第一晶体管tr1和所述有机发光二极管oled彼此电分离。由此,供应到所述第一晶体管tr1的第二端子的所述数据电压v_data可以向所述第一晶体管tr1的栅极端子供应。

74.所述第七晶体管tr7可以包括栅极端子、第一端子以及第二端子。所述第七晶体管tr7的栅极端子可以接收二极管初始化信号gb的供应。所述第七晶体管tr7的第一端子可以接收所述初始化电压vint的供应。所述第七晶体管tr7的第二端子可以连接于所述有机发光二极管oled的第一端子。

75.所述第七晶体管tr7可以在所述二极管初始化信号gb的激活区间期间将所述初始化电压vint供应于所述有机发光二极管oled的第一端子。所述第七晶体管tr7可以在所述二极管初始化信号gb的激活区间期间使得所述有机发光二极管oled的第一端子初始化为所述初始化电压vint。

76.所述存储电容器cst可以包括第一端子以及第二端子。所述存储电容器cst可以连接于所述第一电源电压elvdd布线和所述第一晶体管tr1的栅极端子之间。例如,所述存储电容器cst的第一端子可以连接于所述第一晶体管tr1的栅极端子,所述存储电容器cst的第二端子可以连接于所述第一电源电压elvdd布线。所述存储电容器cst可以在所述扫描信号gw的非激活区间期间保持所述第一晶体管tr1的栅极端子的电压电平。所述扫描信号gw的非激活区间可以包括所述发光控制信号em的激活区间。所述发光控制信号em的激活区间期间所述驱动电流id可以供应于所述有机发光二极管oled。因此,可以基于由所述存储电容器cst保持的电压电平,所述驱动电流id供应于所述有机发光二极管oled。

77.在实施例中,所述第二晶体管至第七晶体管tr2、tr3、tr4、tr5、tr6、tr7可以定义为像素开关晶体管。

78.图3是示出配置于图1的显示部的晶体管的一实施例的截面图。

79.参照图1以及图3,所述显示装置100可以包括基板210、缓冲层220、电容电极cst1、第一层间绝缘层260、第二层间绝缘层270、通孔绝缘层290、第一像素驱动晶体管dr_tft1、第一像素开关晶体管sw_tft1、像素界定膜pdl以及有机发光二极管oled。

80.所述第一像素驱动晶体管dr_tft1可以包括第一有源层230a、第一栅极绝缘层240a、第一栅极电极250a、第一源极电极280a以及第一漏极电极280b。在实施例中,所述第一像素驱动晶体管dr_tft1可以对应于图2的第一晶体管tr1。

81.所述第一像素开关晶体管sw_tft1可以包括第二有源层230b、第二栅极绝缘层240b、第二栅极电极250b、第二源极电极280c以及第二漏极电极280d。在此,所述第二栅极绝缘层240b可以是包括第2

‑

1栅极绝缘层240c以及第2

‑

2栅极绝缘层240d的多层。在实施例中,所述第一像素开关晶体管sw_tft1可以对应于图2的第二晶体管至第七晶体管tr2、tr3、tr4、tr5、tr6、tr7。

82.所述基板210可以包括透明或者不透明的材料。例如,所述基板210可以包括石英基板、合成石英基板、氟化钙基板、掺氟石英基板、钠钙玻璃基板、无碱玻璃基板等。选择性地,所述基板210也可以由具有柔性的透明树脂基板构成。

83.可以在所述基板210上配置所述缓冲层220。所述缓冲层220可以防止金属原子或杂质从所述基板210向所述晶体管dr_tft1、sw_tft1扩散的现象。

84.所述第一有源层230a以及所述第二有源层230b可以配置在所述缓冲层220上。所述第一有源层230a以及所述第二有源层230b可以包括无机物半导体(例如,多晶硅等)。所述第一有源层230a可以包括具有第一长度a的第一沟道区域235a。在实施例中,所述第一长度a可以是约10um至约30um。所述第二有源层230b可以包括具有比所述第一长度a短的第二长度b的第二沟道区域235b。在实施例中,所述第二长度b可以是约1um至约5um。为了驱动电压确保以及余像残留改善,所述第一沟道区域235a可以具有比所述第二长度b相对长的所述第一长度a。为了减少充电时间,所述第二沟道区域235b可以具有比所述第一长度a相对短的所述第二长度b。

85.在实施例中,所述第一沟道区域235a可以用第三族元素掺杂。例如,所述第三族元素可以包括硼(b)、铝(al)、镓(ga)、铟(in)等。在所述第一像素驱动晶体管dr_tft1是pmos晶体管的情况下,所述第一沟道区域235a可以用所述第三族元素掺杂。在实施例中,在所述第一像素驱动晶体管dr_tft1是nmos晶体管的情况下,所述第一沟道区域235a可以用第五

族元素掺杂。在实施例中,所述第二沟道区域235b可以用第五族元素掺杂。例如,所述第五族元素可以包括氮(n)、磷(p)、砷(as)等。在所述第一像素开关晶体管sw_tft1是pmos晶体管的情况下,所述第二沟道区域235b可以用所述第五族元素掺杂。在实施例中,在所述第一像素开关晶体管sw_tft1是nmos晶体管的情况下,所述第二沟道区域235b可以用所述第三族元素掺杂。

86.所述第一像素驱动晶体管dr_tft1和所述第一像素开关晶体管sw_tft1可以具有彼此不同的驱动范围。例如,所述第一像素驱动晶体管dr_tft1的驱动范围可以是约3v至约3.5v。所述第一像素开关晶体管sw_tft1的驱动范围可以比所述第一像素驱动晶体管dr_tft1的驱动范围窄。随着所述第二沟道区域235b用所述第五族元素掺杂,第一像素开关晶体管sw_tft1导通/截止时所需的反应时间可以延迟。

87.所述第一栅极绝缘层240a可以覆盖所述第一有源层230a并配置在所述缓冲层220上。所述第一栅极绝缘层240a可以是包括氧化硅(sio

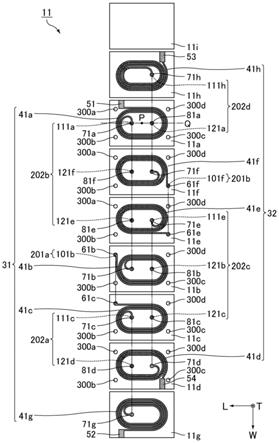

x

)的单层。

88.所述第二栅极绝缘层240b可以覆盖所述第二有源层230b并配置在所述缓冲层220上。在所述第二有源层230b上可以配置所述第2

‑

1栅极绝缘层240c。所述第2

‑

1栅极绝缘层240c可以是包括氧化硅(sio

x

)的单层。在所述第2

‑

1栅极绝缘层240c上可以配置所述第2

‑

2栅极绝缘层240d。所述第2

‑

2栅极绝缘层240d可以是包括氮化硅(sin

x

)的单层。

89.在实施例中,所述第一栅极绝缘层240a以及所述第二栅极绝缘层240b可以配置于相同的层。另外,所述第一栅极绝缘层240a以及所述第二栅极绝缘层240b的厚度可以相同。随着所述第一像素开关晶体管sw_tft1具有相对短的所述第二长度b,可能受到在所述第二源极电极280c以及所述第二漏极电极280d流动的信号引起的影响多。但是,随着所述第二栅极绝缘层240b具有包括所述氧化硅(sio

x

)以及所述氮化硅(sin

x

)的多层结构,所述第二栅极绝缘层240b相比包括所述氧化硅(sio

x

)的单层时可以减少介电常数。由此,可以比所述第二源极电极280c以及所述第二漏极电极280d的影响,受到所述第二栅极电极250b的影响的更多。

90.可以在所述第一栅极绝缘层240a上配置所述第一栅极电极250a。所述第一栅极电极250a可以与所述第一有源层230a重叠。在所述第二栅极绝缘层240b上可以配置所述第二栅极电极250b。所述第二栅极电极250b可以与所述第二有源层230b重叠。所述第一栅极电极250a以及第二栅极电极250b可以包括金属、合金、金属氮化物、导电性金属氧化物、透明导电性物质等。

91.可以配置在所述第一栅极绝缘层240a上覆盖所述第一栅极电极250a并在所述第二栅极绝缘层240b上覆盖所述第二栅极电极250b的所述第一层间绝缘层260。所述第一层间绝缘层260可以包括硅化合物、金属氧化物等。

92.在所述第一层间绝缘层260上可以配置所述电容电极cst1。所述电容电极cst1可以与所述第一栅极电极250a重叠。所述电容电极cst1可以包括金属、合金、金属氮化物、导电性金属氧化物、透明导电性物质等。

93.在所述第一层间绝缘层260上可以配置覆盖所述电容电极cst1的所述第二层间绝缘层270。所述第二层间绝缘层270可以包括硅化合物、金属氧化物等。

94.在所述第二层间绝缘层270上可以配置所述第一源极电极280a、所述第一漏极电极280b、所述第二源极电极280c以及所述第二漏极电极280d。所述第一源极电极280a以及

所述第一漏极电极280b可以分别通过接触孔连接于所述第一有源层230a的源极区域以及所述第一有源层230a的漏极区域。所述第二源极电极280c以及所述第二漏极电极280d可以分别通过接触孔连接于所述第二有源层230b的源极区域以及所述第二有源层230b的漏极区域。所述第一源极电极280a、所述第一漏极电极280b、所述第二源极电极280c以及所述第二漏极电极280d可以包括金属、合金、金属氮化物、导电性金属氧化物、透明导电性物质等。

95.在所述第二层间绝缘层270上可以将所述通孔绝缘层290配置成覆盖所述第一源极电极280a、所述第一漏极电极280b、所述第二源极电极280c以及所述第二漏极电极280d。所述通孔绝缘层290可以包括有机物质或者无机物质。

96.在所述通孔绝缘层290上可以配置所述下部电极310。所述下部电极310可以通过接触孔连接于所述第一漏极电极280b。在实施例中,所述下部电极310可以是正极。选择性地,所述下部电极310也可以是负极。所述下部电极310可以包括金属、合金、金属氮化物、导电性金属氧化物、透明导电性物质等。

97.所述像素界定膜pdl可以配置在所述通孔绝缘层290上。所述像素界定膜pdl可以具有使得所述下部电极310的上面暴露的开口。所述像素界定膜pdl可以由有机物质或者无机物质构成。

98.所述中间层320可以配置在通过所述像素界定膜pdl暴露的所述下部电极310上。所述中间层320可以包括从空穴注入层、空穴输送层、发光层、电子输送层以及电子注入层中选择的至少一个。

99.所述上部电极330可以配置在所述中间层320以及所述像素界定膜pdl上。所述上部电极330可以在所述基板210上整面地配置成覆盖所述中间层320以及所述像素界定膜pdl。在实施例中,所述上部电极330可以是负极。选择性地,所述上部电极330可以是正极。所述上部电极330可以包括金属、合金、金属氮化物、导电性金属氧化物、透明导电性物质等。

100.图4是示出配置于图1的显示部的晶体管的另一实施例的截面图。

101.参照图1以及图4,所述显示装置100可以包括基板410、缓冲层420、第一层间绝缘层460、第二层间绝缘层480、第三层间绝缘层530、通孔绝缘层550、第二像素驱动晶体管dr_tft2、第二像素开关晶体管sw_tft2、像素界定膜pdl以及有机发光二极管oled。

102.所述第二像素驱动晶体管dr_tft2可以包括第一有源层430、第一栅极绝缘层440、第一栅极电极450、连接电极470、第一源极电极540a以及第一漏极电极540b。所述第二像素驱动晶体管dr_tft2可以对应于图2的第一晶体管tr1。

103.所述第二像素开关晶体管sw_tft2可以包括第二有源层490、第二栅极绝缘层510、第二栅极电极520、第二源极电极540c以及第二漏极电极540d。在此,所述第二栅极绝缘层510可以包括第2

‑

1栅极绝缘层500以及第2

‑

2栅极绝缘层505。所述第二像素开关晶体管sw_tft2可以对应于图2的第二晶体管至第七晶体管tr2、tr3、tr4、tr5、tr6、tr7。

104.所述基板410可以包括透明或者不透明的材料。例如,所述基板410可以包括石英基板、合成石英基板、氟化钙基板、掺氟石英基板、钠钙玻璃基板、无碱玻璃基板等。选择性地,所述基板410也可以由具有柔性的透明树脂基板构成。

105.可以在所述基板410上配置所述缓冲层420。所述缓冲层420可以防止金属原子或杂质从所述基板410向所述晶体管dr_tft2、sw_tft2扩散的现象。

106.可以在所述缓冲层420上配置所述第一有源层430。所述第一有源层430可以包括无机物半导体(例如,多晶硅等)。所述第一有源层430可以包括具有所述第一长度a的第一沟道区域435。在实施例中,所述第一沟道区域435可以用第三族元素掺杂。在所述第二像素驱动晶体管dr_tft2是pmos晶体管的情况下,所述第一沟道区域435可以用所述第三族元素掺杂。在实施例中,在所述第二像素驱动晶体管dr_tft2是nmos晶体管的情况下,所述第一沟道区域435可以用所述第五族元素掺杂。

107.所述第一栅极绝缘层440可以在所述缓冲层420上配置成覆盖所述第一有源层430。所述第一栅极绝缘层440可以是包括氧化硅(sio

x

)的单层。

108.可以在所述第一栅极绝缘层440上配置所述第一栅极电极450。所述第一栅极电极450可以与所述第一有源层430重叠。所述第一栅极电极450可以包括金属、合金、金属氮化物、导电性金属氧化物、透明导电性物质等。

109.可以在所述第一栅极绝缘层440上配置覆盖所述第一栅极电极450的所述第一层间绝缘层460。所述第一层间绝缘层460可以包括硅化合物、金属氧化物等。

110.在所述第一层间绝缘层460上可以配置所述连接电极470。所述连接电极470可以与所述第一栅极电极450重叠。所述连接电极470可以与所述第一有源层430的漏极区域连接。所述连接电极470可以包括金属、合金、金属氮化物、导电性金属氧化物、透明导电性物质等。

111.在所述第一层间绝缘层460上可以配置覆盖所述连接电极470的所述第二层间绝缘层480。所述第二层间绝缘层480可以包括硅化合物、金属氧化物等。

112.可以在所述第二层间绝缘层480上配置所述第二有源层490。所述第二有源层490可以包括无机物半导体(例如,多晶硅等)。所述第二有源层490可以包括具有比所述第一长度a短的所述第二长度b的第二沟道区域495。在实施例中,所述第二沟道区域495可以用第五族元素掺杂。在所述第二像素开关晶体管sw_tft2是pmos晶体管的情况下,所述第二沟道区域495可以用所述第五族元素掺杂。在实施例中,在所述第二像素开关晶体管sw_tft2是nmos晶体管的情况下,所述第二沟道区域495可以用所述第三族元素掺杂。

113.为了驱动电压确保以及余像残留改善,所述第一沟道区域435可以具有比所述第二长度b长的所述第一长度a。为了减少充电时间,所述第二沟道区域495可以具有比所述第一长度a短的所述第二长度b。

114.可以在所述第二层间绝缘层480上将所述第2

‑

1栅极绝缘层500配置成覆盖所述第二有源层490。所述第2

‑

1栅极绝缘层500可以是包括氧化硅(sio

x

)的单层。在所述第2

‑

1栅极绝缘层500上可以配置所述第2

‑

2栅极绝缘层505。所述第2

‑

2栅极绝缘层505可以是包括氮化硅(sin

x

)的单层。在实施例中,所述第二栅极绝缘层510可以是包括所述第2

‑

1栅极绝缘层500以及所述第2

‑

2栅极绝缘层505的多层。

115.可以在所述第二栅极绝缘层510上配置所述第二栅极电极520。所述第二栅极电极520可以与所述第二有源层490重叠。所述第二栅极电极520可以包括金属、合金、金属氮化物、导电性金属氧化物、透明导电性物质等。

116.在所述第二栅极绝缘层510上可以配置覆盖所述第二栅极电极520的所述第三层间绝缘层530。所述第三层间绝缘层530可以包括硅化合物、金属氧化物等。

117.在所述第三层间绝缘层530上可以配置所述第一源极电极540a、所述第一漏极电

极540b、所述第二源极电极540c以及所述第二漏极电极540d。所述第一源极电极540a可以连接于所述第一有源层430的源极区域。所述第一漏极电极540b可以通过所述连接电极470连接于所述第一有源层430的漏极区域。所述第一漏极电极540b可以与所述下部电极610连接。在图4中示出了所述第一源极电极540a以及所述第一漏极电极540b配置在所述第三层间绝缘层530上,但不限于此。例如,所述第一源极电极540a以及所述第一漏极电极540b可以配置于与所述第二栅极电极520相同的层。在此情况下,所述第一漏极电极540b可以通过另外的导电图案与所述下部电极610连接。

118.所述第二源极电极540c可以连接于所述第二有源层490的源极区域。所述第二漏极电极540d可以连接于所述第二有源层490的漏极区域。所述第一源极电极540a、所述第一漏极电极540b、所述第二源极电极540c以及所述第二漏极电极540d可以包括金属、合金、金属氮化物、导电性金属氧化物、透明导电性物质等。

119.在所述第三层间绝缘层530上可以将所述通孔绝缘层550配置成覆盖所述第一源极电极540a、所述第一漏极电极540b、所述第二源极电极540c以及所述第二漏极电极540d。所述通孔绝缘层550可以包括有机物质或者无机物质。

120.可以在所述通孔绝缘层550上配置所述下部电极610。所述下部电极610可以连接于所述第一漏极电极540b。在实施例中,所述下部电极610可以是正极。选择性地,所述下部电极610也可以是负极。所述下部电极610可以包括金属、合金、金属氮化物、导电性金属氧化物、透明导电性物质等。

121.所述像素界定膜pdl可以配置在所述通孔绝缘层550上。所述像素界定膜pdl可以具有使得所述下部电极610的上面暴露的开口。所述像素界定膜pdl可以由有机物质或者无机物质构成。

122.所述中间层620可以配置在通过所述像素界定膜pdl暴露的所述下部电极610上。所述中间层620可以包括能够产生红色光、绿色光、蓝色光等不同颜色光的发光物质。

123.所述上部电极630可以配置在所述中间层620以及所述像素界定膜pdl上。所述上部电极630可以在所述基板410上整体地配置成覆盖所述中间层620以及所述像素界定膜pdl。在实施例中,所述上部电极630可以是负极。选择性地,所述上部电极630可以是正极。所述上部电极630可以包括金属、合金、金属氮化物、导电性金属氧化物、透明导电性物质等。

124.如此,所述第二像素开关晶体管sw_tft2配置在所述第二像素驱动晶体管dr_tft2上,从而所述第二像素开关晶体管sw_tft2可以与所述第二像素驱动晶体管dr_tft2至少一部分重叠。由此,能够减少所述显示装置100的无用空间(dead space)。

125.图5是示出配置于图1的扫描驱动部的扫描电路的一实施例的电路图。

126.参照图1以及图5,根据本发明的实施例的所述扫描驱动部140可以包括多个级,各个级可以包括扫描电路。所述扫描电路可以包括第一输入部710、第二输入部720、第一输出部730以及第二输出部740。在一实施例中,所述扫描电路可以还包括保持部750、同步驱动控制部760以及稳定化部770。

127.所述第一输入部710可以响应第二时钟信号clk2将输入信号传送于设定节点nq。例如,可以是,所述扫描驱动部140的第一个级的第一输入部710作为所述输入信号接收开始信号flm,剩余级作为所述输入信号接收前一扫描信号pscan。在实施例中,所述第一输入

部710可以包括第一输入晶体管t1,该第一输入晶体管t1包括接收所述第二时钟信号clk2的栅极端子、接收所述输入信号的第一端子以及连接于所述设定节点nq的第二端子。

128.所述第二输入部720可以响应所述输入信号以及所述第二时钟信号clk2将第一时钟信号clk1传送于复位节点nqb。例如,当所述输入信号以及所述第二时钟信号clk2具有激活电平时,所述第二输入部720可以将具有非激活电平的所述第一时钟信号clk1传送于所述复位节点nqb。在一实施例中,所述第二输入部720可以包括第二输入晶体管t2_1以及第三输入晶体管t2_2,所述第二输入晶体管t2_1包括接收所述输入信号的栅极端子、接收所述第一时钟信号clk1的第一端子以及第二端子,所述第三输入晶体管t2_2包括接收所述第二时钟信号clk2的栅极端子、连接于所述第二输入晶体管t2_1的所述第二端子的第一端子以及连接于所述复位节点nqb的第二端子。

129.所述保持部750可以响应所述第一时钟信号clk1保持所述复位节点nqb的电压。例如,当所述第一时钟信号clk1具有低电平时,所述保持部750可以将所述复位节点nqb的电压保持为所述低电平。在实施例中,所述保持部750可以包括保持晶体管t5,所述保持晶体管t5包括接收所述第一时钟信号clk1的栅极端子、接收所述第一时钟信号clk1的第一端子以及连接于所述复位节点nqb的第二端子。

130.所述同步驱动控制部760可以响应同步驱动信号gck使第一输出部730非激活。在一实施例中,所述同步驱动信号gck可以在所述同步补偿区间具有低电平,在剩余区间具有高电平。在所述同步补偿区间,所述同步驱动控制部760可以响应所述低电平的所述同步驱动信号gck将高电平的栅极截止电压vgh传送于所述设定节点nq。通过所述设定节点nq的栅极截止电压vgh,所述第一输出部730可以非激活。在实施例中,所述同步驱动控制部760可以包括同步驱动控制晶体管t6,所述同步驱动控制晶体管t6包括接收所述同步驱动信号gck的栅极端子、接收栅极截止电压vgh的第一端子以及连接于所述设定节点nq的第二端子。

131.所述稳定化部770可以响应所述复位节点nqb的电压以及第三时钟信号clk3使扫描信号scan稳定。例如,当所述复位节点nqb的电压以及所述第三时钟信号clk3具有低电平时,所述稳定化部770可以将扫描信号scan稳定为高电平。在一实施例中,所述稳定化部770可以包括第二稳定化晶体管t7_2以及第一稳定化晶体管t7_1,所述第二稳定化晶体管t7_2包括接收所述第三时钟信号clk3的栅极端子、连接于所述设定节点nq的第一端子以及第二端子,所述第一稳定化晶体管t7_1包括连接于所述复位节点nqb的栅极端子、连接于所述第二稳定化晶体管t7_2的所述第二端子的第一端子以及连接于输出节点no的第二端子。

132.所述第一输出部730可以响应所述设定节点nq的电压作为所述扫描信号scan输出所述第三时钟信号clk3。例如,在所述数据编程区间,响应所述第二时钟信号clk2的脉冲,低电平的输入信号可以传送于所述设定节点nq。接着,在所述第三时钟信号clk3的下一脉冲下,所述设定节点nq的电压可以通过所述第一输出部730的第一输出电容器c730从所述低电平改变为更低的电平。所述第一输出部730的第一输出晶体管t3可以响应所述设定节点nq的所述改变的电压作为所述扫描信号scan输出低电平的所述第三时钟信号clk3。在一实施例中,所述第一输出部730包括第一输出晶体管t3以及第一输出电容器c730,所述第一输出晶体管t3包括连接于所述设定节点nq的栅极端子、接收所述第三时钟信号clk3的第一端子以及连接于所述输出节点no的第二端子;所述第一输出电容器c730包括连接于所述设

定节点nq的第一电极以及连接于所述输出节点no的第二电极。

133.所述第二输出部740可以响应复位节点nqb的电压作为扫描信号scan输出同步驱动信号gck。例如,在所述同步补偿区间,当同步驱动信号gck从高电平变更为低电平时,复位节点nqb的电压可以通过第二输出部740的第二输出电容器c740从所述低电平改变为更低的电平。第二输出部740的第二输出晶体管t4可以响应复位节点nqb的所述改变的电压作为扫描信号scan输出低电平的同步驱动信号gck。在一实施例中,第二输出部740可以包括第二输出晶体管t4以及第二输出电容器c740,所述第二输出晶体管t4包括连接于复位节点nqb的栅极端子、接收同步驱动信号gck的第一端子以及连接于输出节点no的第二端子,所述第二输出电容器c740包括连接于复位节点nbq的第一电极以及接收同步驱动信号gck的第二电极。

134.所述第一输出部730以及所述第二输出部740可以连接于所述扫描电路的扫描信号输出部。连接于所述扫描信号输出部的所述第一输出晶体管t3以及所述第二输出晶体管t4可以被定义为扫描缓冲晶体管。所述扫描电路的除第一输出晶体管t3以及第二输出晶体管t4以外的晶体管t1、t2_1、t2_2、t5、t6、t7_1、t7_2可以被定义为扫描电路晶体管。

135.图6是示出配置于图1的发光驱动部的发光电路的一实施例的电路图。

136.参照图1以及图6,根据本发明的实施例的所述发光驱动部150可以包括发光电路。所述发光电路可以包括多个晶体管m1、m2、m3、m4、m5、m6、m7、m8、m9、m10、m11、m12、m13以及多个电容器c1、c2、c3。所述发光电路可以被施加多个信号in、clk1、clk2、vgl、vgh、esr,并可以响应所述信号输出发光控制信号em。

137.在实施例中,连接于输出所述发光控制信号em的发光控制信号输出部的晶体管m9、m10可以被定义为发光缓冲晶体管,除所述发光缓冲晶体管以外的剩余晶体管m1、m2、m3、m4、m5、m6、m7、m8、m11、m12、m13可以被定义为发光电路晶体管。

138.所述发光电路可以将所述发光控制信号em输出于所述显示部110。所述发光电路可以接收第一时钟信号clk1、第二时钟信号clk2、保护信号esr、第一栅极电源电压vgh、第二栅极电源电压vgl的输入,输出发光控制信号em。

139.所述发光电路可以包括第九晶体管m9以及第十晶体管m10,所述第九晶体管m9连接于被施加所述第一栅极电源电压vgh的第一栅极电源电压端子和输出所述发光控制信号em的发光控制信号输出端子之间,所述第十晶体管m10连接于被施加所述第二栅极电源电压vgl的第二栅极电源电压端子和所述发光控制信号输出端子之间。

140.所述发光电路可以还包括第十三晶体管m13,所述第十三晶体管m13响应所述保护信号esr将所述第一栅极电源电压vgh施加于所述第十晶体管m10的控制电极。

141.所述发光电路可以包括参与将所述发光控制信号em下拉到所述第二栅极电源电压vgl的动作的下拉部。所述下拉部可以包括第一晶体管m1、第二晶体管m2、第三晶体管m3、第十晶体管m10以及第十二晶体管m12。

142.所述第一晶体管m1可以响应所述第一时钟信号clk1将栅极信号输出于第四节点x4。所述第一晶体管m1的控制电极可以连接于被施加所述第一时钟信号clk1的所述第一时钟端子,所述第一晶体管m1的输入电极in可以连接于被施加所述栅极信号的输入端子,所述第一晶体管m1的输出电极可以连接于所述第四节点x4。

143.所述第二晶体管m2可以响应第一节点x1的电压将所述第一栅极电源电压vgh输出

于第二节点x2。所述第二晶体管m2的控制电极可以连接于所述第一节点x1,所述第二晶体管m2的输入电极可以连接于所述第一栅极电源电压端子,所述第二晶体管m2的输出电极可以连接于所述第二节点x2。

144.所述第三晶体管m3可以响应第三节点x3的电压将所述第二时钟信号clk2输出于所述第二节点x2。所述第三晶体管m3的控制电极可以连接于所述第三节点x3,所述第三晶体管m3的输入电极可以连接于被施加所述第二时钟信号clk2的所述第二时钟端子,所述第三晶体管m3的输出电极可以连接于所述第二节点x2。

145.所述第十晶体管m10可以响应第八节点x8的电压将所述第二栅极电源电压vgl输出于输出所述发光控制信号em的输出端子。所述第十晶体管m10的控制电极可以连接于所述第八节点x8,所述第十晶体管m10的输入电极连接于所述第二栅极电源电压端子,所述第十晶体管m10的输出电极连接于所述输出端子。

146.所述第十二晶体管m12可以响应所述第二栅极电源电压vgl将所述第四节点x4的电压向所述第八节点x8输出。所述第十二晶体管m12的控制电极可以连接于所述第二栅极电源电压端子,所述第十二晶体管m12的输入电极可以连接于所述第四节点x4,所述第十二晶体管m12的输出电极可以连接于所述第八节点x8。

147.所述发光电路可以包括参与将所述发光控制信号em上拉到所述第一栅极电源电压vgh的动作的上拉部。所述上拉部可以包括第四晶体管m4、第五晶体管m5、第六晶体管m6、第七晶体管m7、第八晶体管m8、第九晶体管m9以及第十一晶体管m11。

148.所述第四晶体管m4可以响应所述第四节点x4的电压将所述第一时钟信号clk1输出于所述第一节点x1。所述第四晶体管m4可以包括连接于所述第四节点x4的控制电极、连接于所述第一时钟端子的输入电极以及连接于所述第一节点x1的输出电极。

149.所述第五晶体管m5可以响应所述第一时钟信号clk1将所述第二栅极电源电压vgl输出于所述第一节点x1。所述第五晶体管m5包括连接于所述第一时钟端子的控制电极、连接于所述第二栅极电源电压端子的输入电极以及连接于所述第一节点x1的输出电极。

150.所述第六晶体管m6可以响应所述第二时钟信号clk2连接第五节点x5和第七节点x7。所述第六晶体管m6可以包括连接于所述第二时钟端子的控制电极、连接于所述第五节点x5的输入电极以及连接于所述第七节点x7的输出电极。

151.所述第七晶体管m7可以响应第六节点x6的电压将所述第二时钟信号clk2输出于所述第五节点x5。所述第七晶体管m7可以包括连接于所述第六节点x6的控制电极、连接于所述第二时钟端子的输入电极以及连接于所述第五节点x5的输出电极。

152.所述第八晶体管m8可以响应所述第四节点x4的电压将所述第一栅极电源电压vgh输出于所述第七节点x7。所述第八晶体管m8可以包括连接于所述第四节点x4的控制电极、连接于所述第一栅极电源电压端子的输入电极以及连接于所述第七节点x7的输出电极。

153.所述第九晶体管m9可以响应所述第七节点x7的电压将所述第一栅极电源电压vgh输出于所述输出端子。所述第九晶体管m9可以包括连接于所述第七节点x7的控制电极、连接于所述第一栅极电源电压端子的输入电极以及连接于所述输出端子的输出电极。

154.所述第十一晶体管m11可以响应所述第二栅极电源电压vgl将所述第一节点x1连接于所述第六节点x6。所述第十一晶体管m11可以包括连接于所述第二栅极电源电压端子的控制电极、连接于所述第一节点x1的输入电极以及连接于所述第六节点x6的输出电极。

155.所述发光电路可以还包括第一电容器c1、第二电容器c2、以及第三电容器c3,所述第一电容器c1包括连接于所述第一栅极电源电压端子的第一电极以及连接于所述第七节点x7的第二电极,所述第二电容器c2包括连接于所述第五节点x5的第一电极以及连接于所述第六节点x6的第二电极,所述第三电容器c3包括连接于所述第二节点x2的第一电极以及连接于所述第三节点x3的第二电极。

156.所述第一电容器c1可以是使所述第七节点x7的电压稳定的稳定化电容器。所述第二电容器c2可以是进行将所述第七节点x7的电压充分下拉到低电平的动作的变压电容器。所述第三电容器c3可以是进行将所述第八节点x8的电压充分下拉到低电平的动作的变压电容器。

157.在一实施例中,所述第十三晶体管m13可以连接于所述第四节点x4。

158.图7是示出缓冲晶体管以及电路晶体管的一实施例的图。

159.参照图5以及图7,所述显示装置100可以包括基板810、缓冲层820、第一层间绝缘层860、第二层间绝缘层880、第三层间绝缘层920、通孔绝缘层940、缓冲晶体管buf_tft以及电路晶体管circuit_tft。

160.在实施例中,所述缓冲晶体管buf_tft可以是所述扫描缓冲晶体管。在此情况下,所述缓冲晶体管buf_tft可以是所述第一输出晶体管t3以及第二输出晶体管t4。所述缓冲晶体管buf_tft的结构可以与图3的第一像素开关晶体管sw_tft1的结构实质上相同。所述电路晶体管circuit_tft可以是所述扫描电路晶体管。在此情况下,所述电路晶体管circuit_tft可以是所述晶体管t1、t2_1、t2_2、t5、t6、t7_1、t7_2。所述电路晶体管circuit_tft的结构可以与图3的第一像素驱动晶体管dr_tft1实质上相同。

161.参照图6以及图7,在实施例中所述缓冲晶体管buf_tft可以是所述发光缓冲晶体管。在此情况下,所述缓冲晶体管buf_tft可以是连接于所述发光控制信号输出部的晶体管m9、m10。所述电路晶体管circuit_tft可以是所述发光电路晶体管。在此情况下,所述电路晶体管circuit_tft可以是所述晶体管m1、m2、m3、m4、m5、m6、m7、m8、m11、m12、m13。

162.参照图7,所述缓冲晶体管buf_tft可以包括第一有源层850,第一栅极绝缘层840、第一栅极电极870、第一源极电极890a以及第一漏极电极890b。所述第一栅极绝缘层840可以是包括第1

‑

1栅极绝缘层830以及第1

‑

2栅极绝缘层835的多层。所述电路晶体管circuit_tft可以包括第二有源层910、第二栅极绝缘层900、第二栅极电极930、第二源极电极950a以及第二漏极电极950b。

163.在实施例中,所述第1

‑

1栅极绝缘层830可以包括氧化硅(sio

x

)。所述1

‑

2栅极绝缘层835可以包括氮化硅(sin

x

)。所述第二栅极绝缘层900可以是包括氧化硅(sio

x

)的单层。

164.所述第二有源层910的第二沟道区域915可以具有所述第一长度a,所述第一有源层850的第一沟道区域855可以具有比所述第一长度a短的所述第二长度b。所述缓冲晶体管buf_tft包括具有相对短的所述第二长度b的所述第一沟道区域855,从而能够减少所述显示装置的无用空间。另外,所述缓冲晶体管buf_tft包括具有相对短的所述第二长度b的所述第一沟道区域855,从而在所述第一有源层850流动的电流的量变多而能够向显示部110有效地传送信号。另外,所述第二有源层910包括具有相对长的长度的所述第二沟道区域915,从而能够稳定地驱动图1的扫描驱动部140以及发光驱动部150。

165.在上述中,参照本发明的例示性实施例进行了说明,但本技术领域中具有通常知

识的人会理解在不脱离下面的权利要求书中记载的本发明的构思以及领域的范围内可以对本发明进行各种修改以及变更。

166.(产业上可利用性)

167.本发明可以适用于显示装置。例如,本发明可以适用于高分辨率智能电话、便携式电话、智能平板、智能手表、平板电脑、车辆用导航系统、电视机、计算机显示器、笔记本电脑等。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。