1.本发明涉及半导体技术领域,尤其涉及一种半导体结构及其制备方法。

背景技术:

2.宽禁带半导体材料iii族氮化物作为第三代半导体材料的典型代表,具有禁带宽带大、耐高压、耐高温、电子饱和速度和漂移速度高、容易形成高质量异质结构的优异特性,非常适合制造高温、高频、大功率电子器件。

3.谐振腔发光二极管与垂直腔面发射激光器在内的氮化镓基谐振腔发光器件通常采用dbr(distributed bragg reflector,分布式布拉格反射)结构,而al(ga)n/gan的第一dbr结构因为晶格不匹配而产生的应力,会造成裂纹等问题。

技术实现要素:

4.本技术提供一种半导体结构的制备方法,包括:在衬底上制备缓冲层;在所述缓冲层上制备掩膜层;图形化所述掩膜层使部分暴露所述缓冲层;在所述缓冲层被所述掩膜层暴露的部分制备第一dbr结构;在所述第一dbr结构上制备发光结构;以及在所述发光结构上制备第二dbr结构。通过图形化的掩膜层,可以生长高质量的第一dbr结构。此外掩膜层的存在,也有利于后续发光结构选择性地制备于第一dbr结构上。

5.可选地,在图形化所述掩膜层使部分暴露所述缓冲层后,先部分刻蚀被所述掩膜层露出的所述缓冲层,以在所述缓冲层中形成凹槽,再在所述缓冲层被所述掩膜层暴露的部分上制备第一dbr结构。通过继续刻蚀缓冲层,从而可以制备更厚的第一dbr结构,从而增加其反射率。

6.可选地,在所述缓冲层中形成凹槽后,先在所述凹槽的侧壁制备掩膜层,然后在再在所述缓冲层被所述掩膜层暴露的部分上制备第一dbr结构。掩膜层可以对凹槽的侧壁形成很好的保护,防止后续制备第一dbr结构时,凹槽的侧壁出现寄生生长。

7.可选地,衬底包括硅、蓝宝石、氮化镓、碳化硅。

8.可选地,所述掩膜层包括氧化硅、氮化硅。

9.可选地,所述缓冲层、所述第一dbr结构、所述发光结构包括ⅲ族氮化物材料。

10.本技术提供一种半导体结构,包括:衬底;位于所述衬底上的缓冲层;位于所述缓冲层上的图形化的掩膜层;位于所述缓冲层上及位于所述掩膜层之间的第一dbr结构;位于所述第一dbr结构之上的发光结构;以及位于第二dbr结构之上的第二dbr结构。

11.可选地,所述第一dbr结构延伸至所述缓冲层中。

12.可选地,所述第一dbr结构延伸至所述缓冲层的部分与缓冲层之间设有掩膜层。

附图说明

13.图1a-图1f是本技术第一实施例的半导体结构的示意图。

14.图2a-图2c是本技术第二实施例的半导体结构的示意图。

15.图3a-图3b是本技术第二实施例的半导体结构的示意图。

具体实施方式

16.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整的描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

17.应注意到:相似的标号和字母在下面的附图中表示类似项,因此,一旦某一项在一个附图中被定义,则在随后的附图中不需要对其进行进一步定义和解释。同时,在本发明的描述中,术语“第一”、“第二”等仅用于区分描述,而不能理解为指示或暗示相对重要性。在本发明实施例的描述中,将理解的是:当层(或膜)、区域、图案或结构被称作在另一衬底、另一层(或膜)、另一区域、另一垫或另一图案“上”或“下”时,其可以“直接地”或“间接地”在另一衬底、层(或膜)、区域、垫或图案上,或者还可以存在一个或更多个中间层。已经参照附图描述了层的这种位置。出于方便或清楚的目的,附图中所示出的每个层的厚度和尺寸可能被放大、省略或示意性地绘制。此外,元件的尺寸不完全反映实际尺寸。

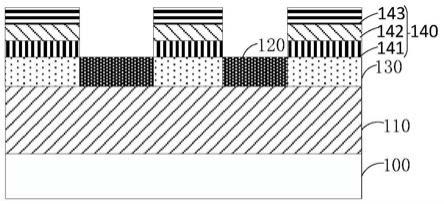

18.图1a-图1e示出了本技术第一实施例中所述半导体结构的制造方法的工艺流程。

19.步骤s1,参照图1a所示,在衬底100上制备缓冲层110。

20.衬底100包括硅、蓝宝石、氮化镓、碳化硅等,本技术对衬底100的材料种类不作特别限定。缓冲层110包括ⅲ族氮化物材料,例如gan、algan等。

21.步骤s2,参照图1b所示,在缓冲层110上制备掩膜层120。

22.掩膜层130包括氧化硅、氮化硅等。

23.步骤s3,参照图1c所示,图形化所述掩膜层120,部分暴露缓冲层110。

24.步骤s4,参照图1d所示,在暴露的缓冲层110上制备第一dbr结构130。优选地,第一dbr结构130的高度不超过掩膜层120的高度。

25.第一dbr结构包括ⅲ族氮化物材料,例如gan、algan交替形成的周期结构。

26.步骤s5,参照图1e所示,在第一dbr结构130上制备发光结构140。发光结构140包括第一掺杂层141,量子阱层142,及第二掺杂层143。发光结构140第一掺杂层141可例如为n型掺杂、第二掺杂层143可例如为p型掺杂。

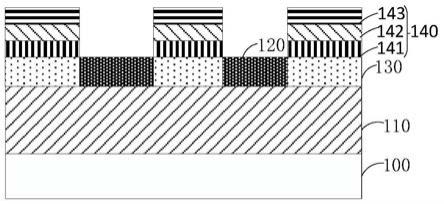

27.步骤s6,参照图1f所示,在发光结构140继续生长第二dbr结构150。

28.第二dbr结构150包括ⅲ族氮化物材料,例如gan、algan交替形成的周期结构,还可包括介质材料,如ta2o5/sio2交替形成的周期结构。

29.通过图形化的掩膜层120,选择性地生长第一dbr结构,可以很好的释放压力,生长高质量的第一dbr结构。此外掩膜层120的存在,也有利于后续发光结构140选择性地制备于第一dbr结构130上。

30.在本技术第二实施例中,如图2a所示,在步骤s3之后,部分刻蚀被掩膜层120暴露出的缓冲层110,在缓冲层110中形成凹槽111;然后如图2b及图2c所示,在暴露的缓冲层110上制备第一dbr结构130;在第一dbr结构130上制备发光结构140;在发光结构140上制备第二dbr结构150。通过继续刻蚀缓冲层,从而可以制备更厚的第一dbr结构,从而增加其反射率。

31.在本技术第三实施例中,如图3a-3b所示,在上述第二实施例中所述的“部分刻蚀被掩膜层120暴露出的缓冲层110,在缓冲层110中形成凹槽111之后,再制备掩膜层,使掩膜层120覆盖凹槽111的侧壁,同时暴露凹槽111底部的缓冲层110。掩膜层可以对凹槽111的侧壁形成很好的保护,防止后续制备第一dbr结构时,凹槽111的侧壁出现寄生生长。

32.本技术的一实施例中还揭示了一种半导体结构,如图1e所示,所述半导体结构包括衬底100,衬底100上的缓冲层110,缓冲层110上图形化的掩膜层130,位于缓冲层110上及位于掩膜层130之间的第一dbr结构130,位于第一dbr结构130上的发光结构140,以及位于发光结构140上的第二dbr结构150。发光结构140包括第一掺杂层141,量子阱层142,及第二掺杂层143。优选地,第一dbr结构130的高度不超过掩膜层120的高度。

33.通过图形化的掩膜层120,可以生长高质量的第一dbr结构。此外掩膜层120的存在,也有利于后续发光结构140选择性地制备于第一dbr结构130上。

34.衬底100包括硅、蓝宝石、氮化镓、碳化硅等,本技术对衬底100的材料种类不作特别限定。缓冲层110包括ⅲ族氮化物材料,例如gan、algan等。第一dbr结构包括ⅲ族氮化物材料,例如gan、algan交替形成的周期结构。第二dbr结构150包括ⅲ族氮化物材料,例如gan、algan交替形成的周期结构,还可包括介质材料,如ta2o5/sio2交替形成的周期结构。

35.在本技术的另一实施例中,如图2c所示,所述半导体结构中,第一dbr结构130延伸至缓冲层130中。通过继续刻蚀缓冲层,从而可以制备更厚的第一dbr结构,从而增加其反射率。

36.在本技术的又一实施例中,如图3b所示,所述半导体结构中,第一dbr结构130的延伸至缓冲层110的部分与缓冲层110之间设置有掩膜层120。掩膜层可以对凹槽111的侧壁形成很好的保护,防止后续制备第一dbr结构时,凹槽111的侧壁出现寄生生长。

37.虽然本发明披露如上,但本发明并非限定于此。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各种更动与修改,因此本发明的保护范围应当以权利要求所限定的范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。