1.本发明属于放大器技术领域,具体涉及一种动态调整偏压电流的通道运算放大器电路。

背景技术:

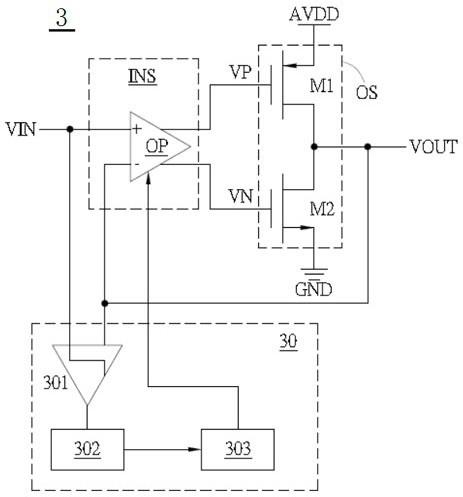

2.请参照图1,图1是传统通道运算放大器(chop)电路的示意图。如图1所示,传统通道运算放大器电路包括输入级(input stage)电路ins及输出级电路os。输入级电路ins包括差动运算放大器op。输出级电路os包括第一晶体管m1及第二晶体管m2。差动运算放大器op的正输入端接收输入电压vin且其负输入端接收输出电压vout。差动运算放大器op的第一输出端提供第一闸极控制电压vp至第一晶体管m1的闸极且其第二输出端提供第二闸极控制电压vn至第二晶体管m2的闸极。第一晶体管m1与第二晶体管m2串接于工作电压avdd与接地端gnd之间。第一晶体管m1与第二晶体管m2之间的接点具有输出电压vout。

3.亦请参照图2,图2是传统通道运算放大器电路的输入级电路之一实施例的示意图。如图2所示,传统通道运算放大器电路的输入级电路包括第一n型晶体管mn1

‑

第三n型晶体管mn3及第一p型晶体管mp1

‑

第三p型晶体管mp3。第一n型晶体管mn1的闸极耦接输入电压vin。第二n型晶体管mn2的闸极耦接输出电压vout。第三n型晶体管mn3的闸极耦接第一偏压vbn。第三n型晶体管mn3耦接第一电压v1与接地端gnd之间。第一n型晶体管mn1的一端与第二n型晶体管mn2的一端亦耦接至第一电压v1。第一p型晶体管mp1的闸极耦接输入电压vin。第二p型晶体管mp2的闸极耦接输出电压vout。第三p型晶体管mp3的闸极耦接第二偏压vbp。第三p型晶体管mp3耦接工作电压avdd与第二电压v2之间。第一p型晶体管mp1的一端与第二p型晶体管mp2的一端亦耦接至第二电压v2。

4.传统上,为了获得良好的稳定性,通常会将传统通道运算放大器电路的输入级电路设计为低偏压电流(low bias current),即降低第一偏压vbn及第二偏压vbp。然而,这也导致充/放电所需的安定时间(settling time)变长,因此,该问题亟待改善。

技术实现要素:

5.本发明旨在至少解决现有技术中存在的技术问题之一。

6.为此,本发明提出一种动态调整偏压电流的通道运算放大器电路,该动态调整偏压电流的通道运算放大器电路具有对载带进行微整形,解决载带自然翘曲的优点。

7.根据本发明实施例的动态调整偏压电流的通道运算放大器电路,包括:输出级电路,包括第一晶体管及第二晶体管,该第一晶体管与该第二晶体管串接于工作电压与接地端之间;输入级电路,分别耦接该第一晶体管的闸极及该第二晶体管的闸极,用以分别接收输入电压以及该第一晶体管与该第二晶体之间的输出电压,并分别输出第一闸极控制电压及第二闸极控制电压至该第一晶体管及该第二晶体管的闸极;以及辅助偏压电路,分别耦接该输入级电路及该输出级电路,用以侦测该输入电压及该输出电压并选择性地输出辅助偏压至该输入级电路。

8.根据本发明一个实施例,当该输出电压与目标输出电压的差值超过1v时,该辅助偏压电路输出该辅助偏压至该输入级电路,从而增大偏压电流,以缩短充电/放电所需的安定时间。

9.根据本发明一个实施例,该辅助偏压电路包括:比较器,用以接收该输入电压及该输出电压并产生该输入电压与该输出电压之比较结果;控制单元,耦接该比较器,用以根据该比较结果产生控制信号;以及偏压单元,耦接该控制单元及该输入级电路,用以根据该控制信号选择性地输出该辅助偏压至该输入级电路。

10.根据本发明一个实施例,该第一晶体管为p型晶体管且该第二晶体管为n型晶体管。

11.根据本发明一个实施例,该输入级电路包括运算放大器,该运算放大器之两输入端分别接收该输入电压及该输出电压且该运算放大器之两输出端分别输出该第一闸极控制电压及该第二闸极控制电压至该第一晶体管及该第二晶体管的闸极。

12.根据本发明一个实施例,该输入级电路包括第一n型晶体管、第二n型晶体管、第三n型晶体管、第一p型晶体管、第二p型晶体管、第三p型晶体管、第一辅助电路及第二辅助电路;该第一n型晶体管的闸极耦接该输入电压;该第二n型晶体管的闸极耦接该输出电压;该第三n型晶体管耦接于第一电压与该接地端之间;该第三n型晶体管的闸极耦接第一偏压;该第一辅助电路耦接于该第一电压与该接地端之间;该第一n型晶体管及该第二n型晶体管的一端耦接该第一电压;该第一p型晶体管的闸极耦接该输入电压;该第二p型晶体管的闸极耦接该输出电压;该第三p型晶体管耦接于该工作电压与第二电压之间;该第二辅助电路耦接于该工作电压与该第二电压之间;该第三p型晶体管的闸极耦接第二偏压;该第一p型晶体管及该第二p型晶体管的一端耦接该第二电压。

13.根据本发明一个实施例,该第一辅助电路包括第四n型晶体管且该第四n型晶体管的闸极耦接第一辅助偏压。

14.根据本发明一个实施例,该第二辅助电路包括第四p型晶体管且该第四p型晶体管的闸极耦接第二辅助偏压。

15.本发明的有益效果是,本发明的动态调整偏压电流的通道运算放大器电路能够动态调整偏压电流。当本发明的动态调整偏压电流的通道运算放大器电路侦测到其输出电压与目标输出电压的差值超过1v时,代表其输入级电路为了获得良好的稳定性而被设计为低偏压电流,因此,本发明的动态调整偏压电流的通道运算放大器电路立即透过辅助偏压电路输出额外的辅助偏压至输入级电路,从而有效增加偏压电流的大小,故能缩短充/放电所需的安定时间。

16.本发明的其他特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变得显而易见,或者通过实施本发明而了解。本发明的目的和其他优点在说明书、权利要求书以及附图中所特别指出的结构来实现和获得。

17.为使本发明的上述目的、特征和优点能更明显易懂,下文特举较佳实施例,并配合所附附图,作详细说明如下。

附图说明

18.本发明的上述和/或附加的方面和优点从下面附图对实施例的描述中将变得明显

和容易理解,其中:图1是传统通道运算放大器电路的示意图;图2是传统通道运算放大器电路的输入级电路之一实施例的示意图;图3是根据本发明的动态调整偏压电流的通道运算放大器电路的示意图;图4是根据本发明的动态调整偏压电流的通道运算放大器电路中输入级电路的示意图。

具体实施方式

19.下面详细描述本发明的实施例,所述实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施例是示例性的,仅用于解释本发明,而不能理解为对本发明的限制。

20.在本发明的描述中,需要理解的是,术语“中心”、“纵向”、“横向”、“长度”、“宽度”、“厚度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”、“顺时针”、“逆时针”、“轴向”、“径向”、“周向”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。此外,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本发明的描述中,除非另有说明,“多个”的含义是两个或两个以上。

21.在本发明的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本发明中的具体含义。

22.下面参考附图具体描述本发明实施例的动态调整偏压电流的通道运算放大器电路3。

23.如图3至图4所示,根据本发明实施例的动态调整偏压电流的通道运算放大器电路3,包括:输入级电路ins、输出级电路os及辅助偏压电路30。

24.输出级电路os包括第一晶体管m1及第二晶体管m2。第一晶体管m1与第二晶体管m2串接于工作电压avdd与接地端gnd之间且第一晶体管m1为p型晶体管且第二晶体管m2为n型晶体管,但不以此为限。

25.输入级电路ins分别耦接第一晶体管m1及第二晶体管m2的闸极。输入级电路ins分别接收输入电压vin以及第一晶体管m1与第二晶体管m2之间的输出电压vout,并分别输出第一闸极控制电压vp及第二闸极控制电压vn至第一晶体管m1及第二晶体管m2的闸极。输入级电路ins包括差动运算放大器op,其两输入端分别接收输入电压vin及输出电压vout且其两输出端分别输出第一闸极控制电压vp及第二闸极控制电压vn。

26.辅助偏压电路30分别耦接输入级电路ins及输出级电路os,用以侦测输入电压vin及输出电压vout并选择性地输出辅助偏压至输入级电路ins。举例而言,当侦测到的输出电压vout与目标输出电压的差值超过1v时,代表为了获得良好的稳定性而将输入级电路ins设计为低偏压电流,因此,辅助偏压电路30即会输出辅助偏压至输入级电路ins,从而增大

充/放电电流,以缩短充/放电所需的安定时间。

27.于一实施例中,辅助偏压电路30可包括比较器301、控制单元302及偏压单元303。比较器301耦接控制单元302,用以产生输入电压vin与输出电压vout之比较结果至控制单元302。控制单元302耦接至偏压单元303,用以根据比较结果产生控制信号至偏压单元303。偏压单元303耦接至输入级电路ins,用以根据控制信号选择性地输出辅助偏压至输入级电路ins。

28.如图4所示,输入级电路4包括第一n型晶体管mn1、第二n型晶体管mn2、第三n型晶体管mn3、第一p型晶体管mp1、第二p型晶体管mp2、第三p型晶体管mp3、第一辅助电路40及第二辅助电路42。

29.第一n型晶体管mn1的闸极耦接输入电压vin。第二n型晶体管mn2的闸极耦接输出电压vout。第三n型晶体管mn3耦接于第一电压v1与接地端gnd之间。第三n型晶体管mn3的闸极耦接第一偏压vbn。第一辅助电路40耦接于第一电压v1与接地端gnd之间。第一n型晶体管mn1的一端及第二n型晶体管mn2的一端耦接第一电压v1。

30.于此实施例中,第一辅助电路40包括第四n型电晶体mn3b且其闸极耦接第一辅助偏压vbnd,并且第一辅助偏压vbnd是由图3中的辅助偏压电路30在侦测到输出电压vout与目标输出电压的差值超过1v时所提供,以对低偏压电流的输入级电路4进行补偿,从而增大充/放电电流,以缩短充/放电所需的安定时间。至于辅助偏压电路30所提供的第一辅助偏压vbnd的电压值大小并无特定之限制,只要能让安定时间缩短至理想值即可。

31.第一p型晶体管mp1的闸极耦接输入电压vin。第二p型晶体管mp2的闸极耦接输出电压vout。第三p型晶体管mp3耦接于工作电压avdd与第二电压v2之间。第二辅助电路42耦接于工作电压avdd与第二电压v2之间。第三p型晶体管mp3的闸极耦接第二偏压vbp。第一p型晶体管mp1及第二p型晶体管mp2的一端耦接第二电压v2。

32.于此实施例中,第二辅助电路42包括第四p型晶体管mp3b且其闸极耦接第二辅助偏压vbpd,并且第二辅助偏压vbpd是由图3中的辅助偏压电路30在侦测到输出电压vout与目标输出电压的差值超过1v时所提供,以对低偏压电流的输入级电路4进行补偿,从而增大充/放电电流,以缩短充/放电所需的安定时间。至于辅助偏压电路30所提供的第二辅助偏压vbpd的电压值大小并无特定之限制,只要能让安定时间缩短至理想值即可。

33.相较于先前技术,本发明的动态调整偏压电流的通道运算放大器电路能够动态调整偏压电流。当本发明的动态调整偏压电流的通道运算放大器电路侦测到其输出电压与目标输出电压的差值超过1v时,代表其输入级电路为了获得良好的稳定性而被设计为低偏压电流,因此,本发明的动态调整偏压电流的通道运算放大器电路立即透过辅助偏压电路输出额外的辅助偏压至输入级电路,从而有效增加偏压电流的大小,故能缩短充/放电所需的安定时间(settling time)。

34.在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示意性实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。

35.尽管已经示出和描述了本发明的实施例,本领域的普通技术人员可以理解:在不

脱离本发明的原理和宗旨的情况下可以对这些实施例进行多种变化、修改、替换和变型,本发明的范围由权利要求及其等同物限定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。