1.本发明涉及对多赫蒂放大器进行控制的控制电路。

背景技术:

2.在下述的专利文献1中记载了有关多赫蒂(doherty)放大器的偏置电路的技术。在下述的专利文献2中记载了对放大电路的温度特性进行补偿的技术。

3.在先技术文献

4.专利文献

5.专利文献1:日本特开2012

‑

199746号公报

6.专利文献2:日本特开2014

‑

171170号公报

7.在专利文献1记载的技术中,将峰值放大器的fet(field effect transistor,场效应晶体管)的栅极电压设定为偏移了(offsetting)载波放大器的fet的栅极电压的电压。这利用的是,在构成载波放大器以及峰值放大器各自的fet为同晶片批次的情况、制造时期相同的情况下,能够期待针对峰值放大器以及载波放大器各自的fet的栅极电压的漏极电流特性大体一致。

8.然而,专利文献1记载的技术并没有考虑峰值放大器以及载波放大器的个体差异造成的动作阈值的偏差所引起的、峰值放大器以及载波放大器的输出功率

‑

增益特性以及输出功率

‑

相位特性的偏差。

技术实现要素:

9.发明要解决的课题

10.本发明正是鉴于上述情形而完成的,其目的在于,抑制特性的偏差。

11.用于解决课题的手段

12.本发明的一个方面的控制电路对包含载波放大器以及峰值放大器的多赫蒂放大器进行控制,该控制电路包含电阻值能够不可逆地调整并基于电阻值来决定峰值放大器的偏置的电阻。

13.发明效果

14.根据本发明,能够抑制特性的偏差。

附图说明

15.图1是示出比较例的多赫蒂放大器的结构的图。

16.图2是示出ab级放大器的输入输出特性的图。

17.图3是示出c级放大器的输入输出特性的图。

18.图4是示出成为本发明的构思的功率放大模块的电路结构的图。

19.图5是示出第1实施方式的功率放大模块的电路结构的图。

20.图6是示出多赫蒂放大器的特性的图。

21.图7是示出多赫蒂放大器的特性的图。

22.图8是示出电阻阵列的其他例的图。

23.图9是示出第1实施方式的功率放大模块的第1调整过程的图。

24.图10是示出第1实施方式的功率放大模块的第2调整过程的图。

25.图11是示出第1实施方式的功率放大模块的第3调整过程的图。

26.图12是示出第2实施方式的功率放大模块的电路结构的图。

27.图13是示出第3实施方式的功率放大模块的电路结构的图。

28.图14是示出第4实施方式的功率放大模块的电路结构的图。

29.图15是示出第5实施方式的功率放大模块的电路结构的图。

30.图16是示出第6实施方式的功率放大模块的电路结构的图。

31.符号说明

32.1、1a、1b、1c、1d、1e 功率放大模块;

33.2、2a、2b、2c、2e 第1集成电路;

34.3、3a、3b、3c、3d、3e 第2集成电路;

35.11 驱动放大器;

36.12 载波放大器;

37.13 峰值放大器;

38.14、15 移相器;

39.16 匹配电路;

40.17 第1偏置电路;

41.18 第2偏置电路;

42.31 可变恒流输出电路;

43.32、32a 电阻阵列;

44.41 减法运算电路;

45.amp1、amp2、amp3、amp4 缓冲放大器;

46.d11、d12、d21、d22、dr1、dr2、dd1、dd2 二极管;

47.q1、q2、q11、q21、qd1、qdd 晶体管;

48.iref、iref2 基准电流输出电路;

49.vref、vref2 基准电压输出电路;

50.rf

‑

1、rf

‑

2、

…

、rf

‑

n 电阻元件;

51.f

‑

1、f

‑

2、

…

、f

‑

n 电子熔丝(e fuse);

52.s

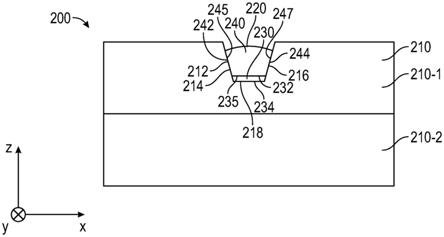

‑

1、s

‑

2、

…

、s

‑

n 开关;

53.vr1、vr2 可变电阻。

具体实施方式

54.以下,基于附图对本发明的控制电路的实施方式详细地说明。另外,并非由本实施方式限定本发明。各实施方式为例示,能够进行在不同的实施方式中示出的结构的部分置换或者组合,这是不言而喻的。在第2实施方式以后,省略关于与第1实施方式共同的事项的记述,仅对不同点进行说明。特别是,关于基于同样的结构的同样的作用效果,不在每个实

施方式中逐次提及。

55.<第1实施方式以及比较例>

56.以下,对第1实施方式进行说明,但为使容易理解第1实施方式,先对比较例进行说明。

57.(比较例)

58.图1是示出比较例的多赫蒂(doherty)放大器的结构的图。多赫蒂放大器100包含输入功率分配电路111、载波放大器112、峰值放大器113和输出功率合成电路114。

59.输入功率分配电路111将从rf(radio frequency,射频)输入端子121输入的高频输入信号rfin分配至两条路径并输出。作为输入功率分配电路111的一个输出信号的高频信号rf11经由dc截止电容器122而供给至构成载波放大器112的fet(field effect transistor,场效应晶体管)的栅极。作为输入功率分配电路111的另一个输出信号的高频信号rf12经由dc截止电容器123而供给至构成峰值放大器113的fet的栅极。

60.载波放大器112例如是使用了fet的功率放大器,将从输入功率分配电路111输入的高频信号rf11始终放大。在构成载波放大器112的fet的栅极,从直流电源124经由扼流圈125被施加偏置电压vg1。偏置电压vg1被设定为对载波放大器112进行ab级(或者,a级或者b级)偏置。此外,在构成载波放大器112的fet的漏极,从直流电源128经由扼流圈129被施加直流电压(例如, 28v)。

61.此外,从直流电源124输出的偏置电压vg1还供给至电压偏移电路126。电压偏移电路126使偏置电压vg1仅偏移给定的电压voffset,生成针对峰值放大器113的偏置电压vg2。

62.峰值放大器113例如是使用了fet的功率放大器,将从输入功率分配电路111输入的高频信号rf12的峰值放大。在构成峰值放大器113的fet的栅极,从电压偏移电路126经由扼流圈127被施加偏置电压vg2。偏置电压vg2被设定为对峰值放大器113进行c级偏置。此外,在构成峰值放大器113的fet的漏极,从直流电源128经由扼流圈130被施加直流电压(例如, 28v)。

63.在此,载波放大器112和峰值放大器113利用的是具有晶片批次、制造时期等的与器件有关的共同要素的放大器。

64.作为载波放大器112的输出信号的高频信号rf13经由dc截止电容器131而供给至输出功率合成电路114。此外,作为峰值放大器113的输出信号的高频信号rf14经由dc截止电容器132而供给至输出功率合成电路114。输出功率合成电路114从输出端子133输出对高频信号rf13和高频信号rf14进行了合成的高频输出信号rfout。

65.像这样,在多赫蒂放大器100中,针对载波放大器112的偏置电压vg1从直流电源124供给。另一方面,针对峰值放大器113的偏置电压vg2通过使偏置电压vg1仅偏移电压voffset从而由电压偏移电路126生成,并从电压偏移电路126供给至构成峰值放大器113的fet的栅极。

66.作为多赫蒂放大器100的特征,载波放大器112以ab级(或者,a级或者b级)动作,峰值放大器113以c级动作。为了与该动作对应,偏置电压vg2被设定为比载波放大器112的偏置电压vg1仅低电压voffset的电压。

67.多赫蒂放大器100在高频输入信号rfin较小时,仅以ab级偏置动作的载波放大器112进行动作。多赫蒂放大器100在高频输入信号rfin变大时,以c级偏置动作的峰值放大器

113开始动作。多赫蒂放大器100随着峰值放大器113的动作开始而载波放大器112的负载阻抗变低,从而过渡至发出较大输出功率的动作。

68.像这样,多赫蒂放大器100的放大动作根据高频输入信号rfin的电平而在中途切换。因此,多赫蒂放大器100的输出功率

‑

增益特性以及输出功率

‑

相位特性在峰值放大器113开始动作的定时变化。该变化给高频输出信号rfout带来失真,导致相邻信道泄漏功率(acp)的增加、即相邻信道泄漏功率比(aclr)的恶化、误差矢量幅度(evm)的增加(恶化)。在使用多赫蒂放大器100的情况下,为了抑制(消除)高频输出信号rfout的失真而采用如下的数字预失真(dpd)技术,即,使用了将多赫蒂放大器100的失真的反特性的失真预先以数值的方式与高频输入信号rfin相加的数据表。

69.然而,比较例的多赫蒂放大器100没有考虑载波放大器112以及峰值放大器113的晶体管的个体差异造成的动作阈值的偏差所引起的、载波放大器112以及峰值放大器113的晶体管的输出功率

‑

增益特性以及输出功率

‑

相位特性的偏差。

70.例如,若构成载波放大器112的晶体管以及构成峰值放大器113的晶体管的动作阈值相对地不同,则即使电压voffset一定,相对的偏置条件也不同。因此,峰值放大器113开始动作的高频输入信号rfin的电平偏移,产生峰值放大器113的输出功率

‑

增益特性以及输出功率

‑

相位特性的偏差。

71.图2是示出ab级放大器的输入输出特性的图。在图2中,横轴为输入功率pin,纵轴为输出功率pout。线141是示出ab级放大器的输入输出特性的一例的线。直至输入功率pin到达某个电平为止,输入功率和输出功率的关系为线性。若输入功率pin变大使得晶体管饱和,则输出功率pout达到顶点(饱和)。ab级放大器的增益根据晶体管的偏置电流(偏置电压)电平、晶体管的特性、输入输出匹配电路等的个体差异,例如,如线142至线143所示,产生偏差。该偏差能够通过调整偏置电压或偏置电流而抑制。

72.图3示出c级放大器的输入输出特性。在图3中,横轴为输入功率pin,纵轴为输出功率pout。线151是示出c级放大器的输入输出特性的一例的线。c级放大器直至输入功率pin到达某个电平为止不动作。若输入功率pin到达某个电平而c级放大器开始动作,则伴随着输入功率pin的增加而c级放大器的增益也增加。最终地,与ab级放大器同样地,若输入功率pin变大使得晶体管饱和,则输出功率pout达到顶点(饱和)。c级放大器的增益根据晶体管的偏置电流(偏置电压)电平、晶体管的特性、输入输出匹配电路等的个体差异,例如,如线152至线153所示,产生偏差。

73.c级放大器开始动作的高频输入信号rfin的电平依赖于晶体管的偏置电流(偏置电压)电平和晶体管的基极(栅极)中的高频信号振幅,根据偏置电流电平、输入匹配电路的个体差异产生偏差。载波放大器112以及峰值放大器113的特性的偏差主要原因不同,因此不一定相关较强,也存在分别变动的情况。

74.在将多赫蒂放大器100用于例如便携电话基站的情况下,为了改变数字预失真的设定而减少失真,存在适当设定表的训练专用的定时,因此上述偏差不会成为本质上的问题。

75.可是,在将多赫蒂放大器100用于例如便携电话装置等无线通信终端装置的情况下,不存在训练专用的定时,难以抑制个体差异导致的特性的偏差。虽然也可考虑在无线通信终端装置的工厂出货前按照每个终端创建数字预失真的表从而抑制个体差异导致的特

性的偏差,但存在无线通信终端装置出货时的测试成本上升的问题。因此,希望抑制个体差异所引起的输出功率

‑

增益特性以及输出功率

‑

相位特性的偏差。

76.图4是表示本发明的想法的构思的电路图。

77.相对于图1所示的比较例的多赫蒂(doherty)放大器,在图4的结构中,为使峰值放大器13的动作变得可靠,基于基准电压输出电路vref的电压,经由带熔丝调整功能的偏移电路30而使第2偏置电路18驱动。通过用带熔丝调整功能的偏移电路30调整电压值或电流值,从而使峰值放大器13可靠地动作。

78.(第1实施方式)

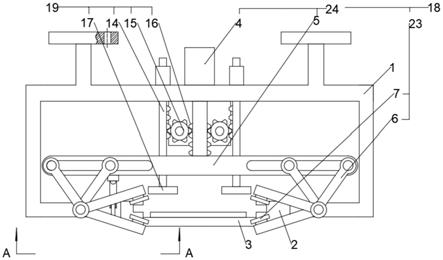

79.图5是示出第1实施方式的功率放大模块的电路结构的图。

80.功率放大模块1可以由在一个基板上安装了多个部件(半导体集成电路等)的混合ic(也可以称为模块)实现,但本公开不限定于此。功率放大模块1例如在便携电话装置等无线通信终端装置中为了向基站发送声音、数据等各种信号而使用。

81.功率放大模块1包含第1集成电路(第1ic芯片)2和第2集成电路(第2ic芯片)3。例示第1集成电路2形成在化合物半导体基板(例如,gaas基板)上,但本公开不限定于此。例示第2集成电路3形成在半导体基板(例如,si基板)上,但本公开不限定于此。

82.第2集成电路3相当于本公开的“控制电路”的一例。

83.第1集成电路2包含初级(驱动级)的驱动放大器11和最终级(功率级)的载波放大器12以及峰值放大器13。载波放大器12以及峰值放大器13构成多赫蒂放大器。

84.载波放大器12包含晶体管q1。峰值放大器13包含晶体管q2。晶体管q1通过第1偏置电路17被进行ab级(或者,a级或者b级)偏置。晶体管q2通过第2偏置电路18被进行c级偏置。

85.以后,存在将第1偏置电路17以及载波放大器12总称为“载波放大系统”的情况。此外,存在将第2偏置电路18以及峰值放大器13总称为“峰值放大系统”的情况。

86.在本公开中,各晶体管设为双极晶体管,但本公开不限定于此。双极晶体管例示异质结双极晶体管(heterojunction bipolar transistor:hbt),但本公开不限定于此。晶体管例如也可以为场效应晶体管(field effect transistor:fet)。晶体管也可以为将多个单位晶体管进行了电并联连接的多指晶体管。所谓单位晶体管,是指构成晶体管的最小限度的结构。

87.在驱动放大器11,经由端子1a被输入高频输入信号rfin。驱动放大器11输出将高频输入信号rfin放大了的高频信号rf1。

88.在驱动放大器11的输出端子,电连接有dc截止电容器c1的一端以及移相器14的一端。dc截止电容器c1的另一端与晶体管q1的基极电连接。高频信号rf1经由dc截止电容器c1而供给至晶体管q1的基极。

89.移相器14输出使高频信号rf1的相位超前或者滞后了大致90度(degree)的高频信号rf2。在本公开中,大致90度设为90度

±

20度。

90.移相器14的另一端经由dc截止电容器c2而与晶体管q2的基极电连接。高频信号rf2经由dc截止电容器c2而供给至晶体管q2的基极。

91.晶体管q1的发射极与基准电位电连接。基准电位例示接地电位,但本公开不限定于此。晶体管q1的集电极经由扼流电感器l而与电源电位vcc电连接。晶体管q1从集电极输出将高频信号rf1放大了的高频信号rf3。

92.移相器15的一端与晶体管q1的集电极电连接。移相器15的另一端与晶体管q2的集电极电连接。

93.移相器15输出使高频信号rf3的相位超前或者滞后了大致90度的高频信号rf4。

94.在移相器14使高频信号rf1的相位超前大致90度的情况下,移相器15使高频信号rf3的相位超前大致90度。在移相器14使高频信号rf1的相位滞后大致90度的情况下,移相器15使高频信号rf3的相位滞后90度。

95.晶体管q2的发射极与基准电位电连接。晶体管q2从集电极输出将高频信号rf2放大了的高频信号rf5。

96.移相器15的另一端以及晶体管q2的集电极经由匹配电路16而与端子1b电连接。高频信号rf4和高频信号rf5被重叠在一起,作为高频输出信号rfout经由匹配电路16从端子1b输出。

97.在高频输入信号rfin较小的情况下,载波放大器12(晶体管q1)动作,但峰值放大器13(晶体管q2)不动作。在该情况下,载波放大器12的负载阻抗成为匹配电路16的阻抗rl。这是因为,在移相器15中没有产生阻抗的变化。

98.若高频输入信号rfin变大,则载波放大器12(晶体管q1)接近饱和,同时峰值放大器13(晶体管q2)开始动作。在该情况下,从峰值放大器13向匹配电路16施加的高频信号rf5的相位变得与从载波放大器12经由移相器15向匹配电路16施加的高频信号rf4的相位相同。此时,晶体管q2的集电极中的信号振幅变大,因此从峰值放大器13看上去负载阻抗(匹配电路16的阻抗)等效地增加了。该阻抗的等效变化经由移相器15传递给载波放大器12。从载波放大器12看上去负载阻抗反之减少了,因此载波放大器12的饱和功率(最大功率)变大。

99.最终地,在峰值放大器13饱和的状态下,从峰值放大器13看上去负载阻抗(匹配电路16的阻抗)为2rl,从载波放大器12看上去负载阻抗为rl/2。

100.通过该动作,载波放大器12一旦接近饱和,负载阻抗看上去下降,从而能够送出更大的输出。载波放大器12在饱和附近动作,因此能够在较宽的功率范围内实现较高的效率。

101.图6以及图7是示出多赫蒂放大器的特性的图。详细地,图6是示出多赫蒂放大器的输出功率和效率的关系的图。图7是示出多赫蒂放大器的输出功率和增益的关系的图。

102.在图6中,横轴为输出功率pout,纵轴为效率。箭头161表示载波放大器12动作的输出功率pout的范围。箭头162表示峰值放大器13动作的输出功率pout的范围。如线163所示,从载波放大器12在饱和附近动作的输出功率pout的电平至负载阻抗变为一半而饱和的电平为止,可达到较高的效率。

103.在图7中,横轴为输出功率pout,纵轴为增益。如线171所示,在峰值放大器13开始动作的区域172中,多赫蒂放大器的非线性尤其显著。

104.像这样,多赫蒂放大器的放大动作在作为峰值放大器13开始动作的定时的区域172进行切换。因此,多赫蒂放大器的输出功率

‑

增益特性以及输出功率

‑

相位特性在区域172变化。该变化给高频输出信号rfout带来失真,导致相邻信道泄漏功率(acp)的增加、即相邻信道泄漏功率比(aclr)的恶化、误差矢量幅度(evm)的增加(恶化)。

105.如先前所述,在数字预失真(dpd)技术中,由发送电路的数字信号处理部生成区域172中的多赫蒂放大器的失真的反特性的失真并与高频输入信号rfin相加,抑制高频输出

信号rfout的失真造成的aclr、evm的恶化。多赫蒂放大器的失真容易根据第1集成电路2内包含的双极晶体管的个体差异等而变化。例如,若晶体管q1以及晶体管q2有个体差异,动作阈值相对地不同,则相对的偏置条件不同。于是,峰值放大器13(晶体管q2)开始动作的定时为一前一后。也就是说,区域172在图7中的左右方向上移动。抑制多赫蒂放大器的失真的变化、即抑制区域172向图7中的左右方向的移动,对于将多赫蒂放大器应用于无线通信终端装置是重要的。

106.再次参照图5对载波放大器12以及峰值放大器13的偏置进行说明。第2集成电路3将电流i1输出至第1偏置电路17,将电压v2输出至第2偏置电路18。

107.对电流i1的生成进行说明。第2集成电路3内的基准电压输出电路vref将基准电压v21输出至基准电流输出电路iref。

108.基准电流输出电路iref将与基准电压v21相应的基准电流i21输出至可变恒流输出电路31。可变恒流输出电路31将与基准电流i21成比例的电流i1输出至第1集成电路2的端子b1。

109.第1集成电路2包含电阻rp1和第1偏置电路17。第1偏置电路17包含二极管d11以及d12、晶体管q11和电阻rbias1。二极管d11以及d12各自例示的是hbt的基极和集电极被电连接、即被二极管连接的二极管。

110.电阻rp1的一端与端子b1电连接。电阻rp1的另一端与二极管d11的阳极电连接。二极管d11的阴极与二极管d12的阳极电连接。二极管d12的阴极与基准电位电连接。二极管d11以及d12的串联连接电路产生一定的电压。例如,若想要使二极管d11以及d12各自产生约1.3v(伏特)的电压,则二极管d11以及d12的串联连接电路要产生约2.6v的电压。

111.二极管d11以及d12的串联连接电路的电压被施加于晶体管q11的基极。晶体管q11的集电极经由端子cq11以及端子1c而与电源电位vcbias电连接。晶体管q11的发射极经由电阻rbias1而与晶体管q1的基极电连接。也就是说,晶体管q11以及电阻rbias1被进行了发射极跟随连接。晶体管q1的基极电流基于被施加于晶体管q11的基极的电压来决定。

112.对电压v2的生成进行说明。第2集成电路3内的缓冲放大器amp1将基于基准电压v21的电压v22输出至可变电阻vr1的一端。例示电压v22与基准电压v21相同,但本公开不限定于此。可变电阻vr1和电阻阵列32的串联电路对电压v22进行电阻分压,并输出电压v23。

113.电阻阵列32包含n个(n为自然数)电阻元件rf

‑

1、rf

‑

2、

…

、rf

‑

n和n个电子熔丝(e fuse)f

‑

1、f

‑

2、

…

、f

‑

n。电阻元件rf

‑

1、rf

‑

2、

…

、rf

‑

n的一端相互电连接,并与可变电阻vr1的另一端电连接。电阻元件rf

‑

1、rf

‑

2、

…

、rf

‑

n的另一端分别经由电子熔丝f

‑

1、f

‑

2、

…

、f

‑

n而相互电连接,并与基准电位电连接。也就是说,电阻元件rf

‑

1、rf

‑

2、

…

、rf

‑

n被并联连接。

114.电阻元件rf

‑

1、rf

‑

2、

…

、rf

‑

n的电阻值既可以相同,也可以不同。以后,存在将电阻元件rf

‑

1、rf

‑

2、

…

、rf

‑

n总称为电阻元件rf的情况。

115.电子熔丝f

‑

1、f

‑

2、

…

、f

‑

n与n个端子3a

‑

1、3a

‑

2、

…

、3a

‑

n分别电连接。通过对端子3a

‑

1、3a

‑

2、

…

、3a

‑

n选择性地施加电压或者电流,从而能够将电子熔丝f

‑

1、f

‑

2、

…

、f

‑

n选择性地熔断。电阻阵列32的电阻值能够通过将电子熔丝f

‑

1、f

‑

2、

…

、f

‑

n选择性地熔断从而可变。例如,若电子熔丝f

‑

1被熔断,则电阻元件rf

‑

1变得与电阻阵列32的电阻值没有关系,因此电阻阵列32的电阻值变大。

116.以后,存在将电子熔丝f

‑

1、f

‑

2、

…

、f

‑

n总称为电子熔丝f的情况。

117.电子熔丝f是若被熔断则不会复原的不可逆性的元件。电阻阵列32的电阻值在初始时(电子熔丝f一个也未被熔断时)最小,随着电子熔丝f被熔断而不可逆地变大。也就是说,电阻阵列32的电阻值是能够不可逆地调整的。

118.图8是示出电阻阵列的其他例的图。

119.电阻阵列32a包含n个电阻元件rf

‑

1、rf

‑

2、

…

、rf

‑

n和n个开关s

‑

1、s

‑

2、

…

、s

‑

n。电阻元件rf

‑

1、rf

‑

2、

…

、rf

‑

n的一端相互电连接。电阻元件rf

‑

1、rf

‑

2、

…

、rf

‑

n的另一端分别经由开关s

‑

1、s

‑

2、

…

、s

‑

n而相互电连接。

120.非易失性存储器51存储n比特的数据,将n比特宽度的信号输出至开关s

‑

1、s

‑

2、

…

、s

‑

n。开关s

‑

1、s

‑

2、

…

、s

‑

n各自根据被供给的信号而接通或者断开。电阻阵列32a的电阻值能够通过将开关s

‑

1、s

‑

2、

…

、s

‑

n选择性地接通或者断开从而可变。例如,若开关s

‑

1被断开,则电阻元件rf

‑

1变得与电阻阵列32a的电阻值没有关系,因此电阻阵列32a的电阻值变大。通过向非易失性存储器51写入数据,从而能够对开关s

‑

1、s

‑

2、

…

、s

‑

n的接通或者断开进行切换,能够使电阻阵列32a的电阻值可变。

121.非易失性存储器51例示一次性rom(read only memory,只读存储器)。一次性rom是若写入数据则不能改写的不可逆性的元件。也就是说,电阻阵列32a的电阻值是不可逆的。

122.电阻阵列32以及32a相当于本公开的“电阻”的一例。

123.另外,例示可变电阻vr1由与图8同样的电路结构实现。可变电阻vr1能够通过将eprom(erasable programmable read only memory,可擦可编程只读存储器)、闪存(注册商标)等作为非易失性存储器51使用从而使电阻值可逆地可变。

124.再次参照图5,电压v23能够通过调整电阻阵列32的电阻值(以及可变电阻vr1的电阻值)而调整。

125.在将可变电阻vr1的电阻值维持一定的情况下,电压v23随着电阻阵列32的电阻值上升而上升。也就是说,电压v23是电压v22根据电阻阵列32的电阻值被调整后的电压。

126.缓冲放大器amp2将基于电压v23的电压v2输出至第1集成电路2的端子b2。例示电压v2与电压v23相同,但本公开不限定于此。电压v23能够通过调整电阻阵列32的电阻值(以及可变电阻vr1的电阻值)而调整。因此,电压v2能够通过调整电阻阵列32(以及可变电阻vr1的电阻值)的电阻值而调整。

127.第1集成电路2包含电阻rp2和第2偏置电路18。第2偏置电路18包含二极管d21以及d22、晶体管q21和电阻rbias2。二极管d21以及d22各自例示被二极管连接的hbt。

128.电阻rp2的一端与端子b2电连接。电阻rp2的另一端与二极管d21的阳极电连接。二极管d21的阴极与二极管d22的阳极电连接。二极管d22的阴极与基准电位电连接。

129.二极管d21的阳极与晶体管q21的基极电连接。晶体管q21的集电极经由端子cq21以及端子1c而与电源电位vcbias电连接。晶体管q21的发射极经由电阻rbias2而与晶体管q2的基极电连接。也就是说,晶体管q21以及电阻rbias2被进行了发射极跟随连接。

130.电压v2的电压值设为小于被二极管连接的hbt即二极管d21以及d22各自的接通电压(例如,1.3v程度)的两倍(例如,2.6v程度)的电压,例示2.1v至2.2v的程度。即使电压v2被施加于端子b2,由于电压v2小于二极管d21以及d22的串联连接电路的接通电压,因此二

极管d21以及d22也不会流过电流。同样地,晶体管q21以及q2也不动作。

131.若被输入高频输入信号rfin,则随着输入rf信号的增加而流过晶体管的电流增加。此时,在直流下,会引起基极

‑

发射极间二极管的接通电压减少的自偏置效应。若由于该自偏置效应而晶体管q2以及晶体管q21的二极管(基极

‑

发射极间的pn结)的接通阈值电压开始下降,则晶体管q2以及q21开始动作。由此,在端子b2

→

电阻rp2

→

晶体管q21

→

晶体管q2的路径开始流动电流。电连接在晶体管q21的发射极与移相器14的另一端之间的电容器cb2有以下作用:对晶体管q21的发射极高效地施加高频信号rf2,促进晶体管q21的接通阈值电压下降。另外,优选设置电容器cb2,但不是必需的,也可以没有。

132.各晶体管的二极管的接通阈值电压根据制造工艺产生偏差。即使为相同晶片上的不同芯片上的晶体管,接通阈值电压也有差异,即使在相同晶片上的相同芯片上的晶体管q1和晶体管q2之间,也有偏差。功率放大模块1通过将先前所述的电子熔丝f选择性地熔断从而抑制该偏差。

133.图9是示出第1实施方式的功率放大模块的第1调整过程的图。图9所示的过程例示半导体检查装置(半导体测试仪)针对第1集成电路2被切割之前的化合物半导体晶片而实施。

134.从晶片上的多个第1集成电路2中选择第1集成电路2,并记录晶片上的坐标(步骤s100)。另外,晶片上的坐标是对所选择的第1集成电路2进行识别的识别信息的一例,只要能够对所选择的第1集成电路2进行识别,也可以为其他信息。

135.对端子b1以及b2施加给定电位(或者,给定电流)(步骤s102)。给定电位例示预先决定的2.6v程度以上的电位,但本公开不限定于此。此时,如果第1集成电路2内包含的各晶体管以及各二极管无偏差(个体差异),那么晶体管q11的集电极电流和晶体管q21的集电极电流变得相同,此外,晶体管q1的集电极电流和晶体管q2的集电极电流变得相同。但是,实际上,第1集成电路2内包含的各晶体管以及各二极管有偏差,因此晶体管q11的集电极电流和晶体管q21的集电极电流不会变得相同,此外,晶体管q1的集电极电流和晶体管q2的集电极电流不会变得相同。

136.测定晶体管q1以及q2(或者,晶体管q11以及q21)各自的集电极电流值(步骤s104)。最终地,直接影响高频输出信号rfout的是晶体管q1以及q2的集电极电流,因此优选测定晶体管q1以及q2各自的集电极电流值。但是,只要晶体管q1以及q2各自的集电极电流值比半导体测试仪能够测定的最大电流值大,也可以测定晶体管q11以及q21各自的集电极电流值。

137.在为了抑制芯片面积而晶体管q11以及q21的集电极与一个焊盘电连接的情况下,只要以时分的方式测定晶体管q11的集电极电流值和晶体管q21的集电极电流值即可。另外,例如,若晶体管q11以及q21的集电极与其他电路例如对驱动放大器11赋予偏置的偏置电路连接,则测定精度会下降。因此,如图5所示,优选晶体管q11以及q21的集电极不与其他电路连接。

138.将所测定的两个集电极电流值与第1集成电路2的坐标建立关联地记录(步骤s106)。

139.对于使晶体管q1以ab级(或者,a级或者b级)偏置动作且使晶体管q2以c级偏置动作的情况下的、晶体管q1的集电极电流值和晶体管q2的集电极电流值之间的差为最小的电

压v2,基于二极管特性来计算。将计算出的电压v2与第1集成电路2的坐标建立关联地记录(步骤s108)。

140.从步骤s100至步骤s108是针对化合物半导体晶片上的全部的第1集成电路2而实施的。

141.从化合物半导体晶片切割出多个第1集成电路2并分别安装于多个基板,组装多个功率放大模块1(步骤s110)。

142.将一个或者多个电子熔丝f熔断,使得针对多个功率放大模块1各自,输出缓冲放大器amp2通过步骤s108计算出的电压v2(步骤s112)。在用电子熔丝f未调整完的情况下,对可变电阻vr1进行调整。

143.第1调整过程能够抑制功率放大模块1的二极管(晶体管的pn结)的动作阈值的偏差。

144.图10是示出第1实施方式的功率放大模块的第2调整过程的图。图10所示的过程例示功率放大模块检查装置针对组装后的功率放大模块1而实施。

145.将第1集成电路2以及第2集成电路3安装在基板上,组装功率放大模块1(步骤s200)。

146.使开关sw2为断开。也可以使可变恒流输出电路31为断开,来代替将开关sw2断开。此外,将开关sw1连接至端子b1侧(步骤s202)。由此,晶体管q11以及q1动作。

147.测定晶体管q1(或者q11)的集电极电流值(步骤s204)。

148.使开关sw2为断开。此外,将开关sw1连接至端子b2侧(步骤s206)。由此,晶体管q21以及q2动作。

149.测定晶体管q2(或者q21)的集电极电流值(步骤s208)。

150.求出晶体管q1(或者q11)的集电极电流值与晶体管q2(或者q21)的集电极电流值之差δicc(步骤s210)。

151.判定差δicc的绝对值abs(δicc)是否小于预先决定的容许差ε(步骤s212)。一旦判定为绝对值abs(δicc)不小于容许差ε(步骤s212中否),则将处理前进至步骤s214。一旦判定为绝对值abs(δicc)小于容许差ε(步骤s212中是),则将处理前进至步骤s216。

152.一旦判定为绝对值abs(δicc)不小于容许差ε(步骤s212中否),则将一个或者多个电子熔丝f熔断(步骤s214),将处理前进至步骤s202。

153.一旦判定为绝对值abs(δicc)小于容许差ε(步骤s212中是),则使开关sw2为接通,将开关sw1连接至端子b2侧(步骤s216),结束处理。

154.第2调整过程与先前的第1调整过程同样地,能够抑制功率放大模块1的二极管(晶体管的pn结)的动作阈值的偏差。进而,第2调整过程与先前的第1调整过程相比,不需要管理第1集成电路2的坐标、晶片评价的历史记录等,能够在功率放大模块1的良品试验的时间点同时执行。

155.图11是示出第1实施方式的功率放大模块的第3调整过程的图。图11所示的过程例示功率放大模块检查装置针对组装后的功率放大模块1而实施。

156.将第1集成电路2以及第2集成电路3安装在基板上,组装功率放大模块1(步骤s300)。

157.使开关sw2为断开。也可以使可变恒流输出电路31为断开,来代替将开关sw2断开。

此外,将开关sw1连接至端子b2侧(步骤s302)。由此,晶体管q11以及q1停止,晶体管q21以及q2能够动作。

158.将预先决定的第1高频信号输入至端子1a(步骤s304)。第1高频信号的功率例如设定在峰值放大器13开始c级动作(参照图3)的近处。

159.测定晶体管q2(或者q21)的集电极电流值(步骤s306)。

160.将预先决定的第2高频信号输入至端子1a(步骤s308)。第2高频信号的功率例如设定在峰值放大器13开始c级动作(参照图3)的近处。

161.测定晶体管q2(或者q21)的集电极电流值(步骤s310)。

162.另外,步骤s308以及s310用于使判定精度提高,也可以省略。

163.判定通过步骤s306以及s310测定出的集电极电流值是否在预先决定的设定范围内(步骤s312)。一旦判定为集电极电流值不在设定范围内(步骤s312中否),则将处理前进至步骤s314。一旦判定为集电极电流值在设定范围内(步骤s312中是),则将处理前进至步骤s316。

164.一旦判定为集电极电流值不在设定范围内(步骤s312中否),则将一个或者多个电子熔丝f熔断(步骤s314),将处理前进至步骤s302。

165.一旦判定为集电极电流值在设定范围内(步骤s312中是),则使开关sw2为接通,将开关sw1连接至端子b2侧(步骤s316),结束处理。

166.先前的第1以及第2调整过程仅抑制了二极管(晶体管的pn结)的动作阈值的偏差,相对于此,第3调整过程能够抑制包含移相器14以及15、匹配电路16在内的元件的个体差异的影响。

167.图5所示的功率放大模块1的电路结构与上述的第1至第3调整过程均能够对应。

168.如以上说明的那样,功率放大模块1通过电子熔丝f能够抑制在多赫蒂放大器内容易受到个体差异的影响的进行c级动作的峰值放大系统的特性的偏差。功率放大模块1能够在抑制了峰值放大系统的特性的偏差的状态下向无线通信终端装置制造商出货。因此,功率放大模块1能够抑制无线通信终端装置制造商向无线通信终端装置应用数字预失真用的测试成本。

169.<第2实施方式>

170.图12是是示出第2实施方式的功率放大模块的电路结构的图。

171.对于第2实施方式的功率放大模块1a的构成要素之中与第1实施方式相同的构成要素,标注相同的参照符号并省略说明。

172.功率放大模块1a包含第1集成电路2a和第2集成电路3a。

173.第1集成电路2a与第1实施方式的第1集成电路2(参照图5)相比较,在晶体管q21的发射极与移相器14的另一端之间不包含电容器cb2。电容器cb2有对晶体管q21的发射极高效地施加高频信号rf2、促进晶体管q21的接通阈值电压下降的作用,因此优选设置,但不是必需的,也可以没有。

174.第2集成电路3a与第1实施方式的第2集成电路3(参照图5)相比较,还包含基准电压输出电路vref2。

175.基准电压输出电路vref2将基准电压v31输出至缓冲放大器amp1。缓冲放大器amp1将基于基准电压v31的电压v22输出至可变电阻vr1的一端。

176.第1实施方式的第2集成电路3基于从基准电压输出电路vref输出的基准电压v21而生成了电压v2。另一方面,第2实施方式的第2集成电路3a基于从基准电压输出电路vref2输出的基准电压v31来生成电压v2。其理由如下所述。

177.hbt的二极管(pn结)特性有温度依赖性。例如,在载波放大系统中,二极管d11以及d12的串联连接具有若温度上升则电压下降而若温度下降则电压上升这样的温度特性。二极管d11以及d12能够根据该温度特性来抑制晶体管q11以及q1的温度特性。

178.另一方面,在峰值放大系统中,直至某个电平的高频输入信号rfin被输入为止,不流过电流。特别是,二极管d21以及d22是为了在测试时将条件设为与载波放大系统相同而设置的,在实际的放大动作时,不流过电流。因此,二极管d21以及d22不能抑制晶体管q21以及q2的温度特性。

179.因此,基准电压输出电路vref2设为具有消除晶体管q21以及q2的温度特性的特性。具体地,基准电压输出电路vref2设为具有若温度上升则基准电压v31下降而若温度下降则基准电压v31上升这样的负的温度依赖性。由此,基准电压输出电路vref2能够抑制晶体管q21以及q2的温度特性。

180.如以上说明的那样,功率放大模块1a与功率放大模块1同样地,通过电子熔丝f能够抑制在多赫蒂放大器内也容易受到个体差异的影响的进行c级动作的峰值放大系统的特性的偏差。进而,功率放大模块1a还能够抑制基于峰值放大系统的温度的特性变动。

181.<第3实施方式>

182.图13是示出第3实施方式的功率放大模块的电路结构的图。

183.对于第3实施方式的功率放大模块1b的构成要素之中与第1或者第2实施方式相同的构成要素,标注相同的参照符号并省略说明。

184.功率放大模块1b包含第1集成电路2b和第2集成电路3b。

185.第1集成电路2b与第1实施方式的第1集成电路2(参照图5)相比较,还包含二极管dr1以及dr2。二极管dr1以及dr2各自例示的是将hbt进行了二极管连接的二极管。二极管dr1的阴极与二极管dr2的阳极电连接。

186.二极管dr1以及dr2相当于本公开的“多个二极管”的一例。

187.此外,第1集成电路2b与第1集成电路2相比较,不包含电容器cb2。电容器cb2有对晶体管q21的发射极高效地施加高频信号rf2、促进晶体管q21的接通阈值电压下降的作用,因此优选设置,但不是必须的,也可以没有。

188.此外,第1集成电路2b与第1集成电路2相比较,不包含二极管d21以及d22。在第1实施方式中,二极管d21以及d22是为了在测试时将条件设为与载波放大系统相同而设置的,在实际的放大动作时,不流过电流。因此,第1集成电路2b省略了二极管d21以及d22。

189.第2集成电路3b与第1实施方式的第2集成电路3(参照图5)相比较,还包含缓冲放大器amp3以及amp4、可变电阻vr2、电阻rcont、开关sw3、基准电流输出电路iref2和减法运算电路41。

190.基准电流输出电路iref2相当于本公开的“恒流输出电路”的一例。

191.缓冲放大器amp3将基于基准电压v21的电压v42输出至可变电阻vr2的一端。电压v42例示与基准电压v21相同,但本公开不限定于此。可变电阻vr2和电阻rcont的串联电路对电压v42进行电阻分压,并输出电压v43。缓冲放大器amp4输出基于电压v43的电压

voffset。电压voffset例示与电压v43相同,但本公开不限定于此。电压voffset相当于驱动载波放大器12的ab级(或者,a级或者b级)偏置和驱动峰值放大器13的c级偏置的偏置的差电压。电压voffset为与基准电压v21相应的电压。

192.基准电流输出电路iref2将与电压v41相应的电流i41输出至二极管dr1的阳极。二极管dr1以及dr2的串联连接电路产生一定的电压v44。例如,若想要使二极管dr1以及dr2各自产生约1.3v的电压,则二极管dr1以及dr2的串联连接电路产生约2.6v的电压。

193.减法运算电路41将电压v44与电压voffset之差的电压v2输出至第1集成电路2b的端子b2。减法运算电路41例示使用了运算放大器41a的差动放大器。

194.电压v44经由电阻41b而输入至运算放大器41a的同相输入端子。运算放大器41a的同相输入端子经由电阻41c而与基准电位电连接。电压voffset经由电阻41d而输入至运算放大器41a的反相输入端子。运算放大器41a的反相输入端子经由电阻41e而与运算放大器41a的输出端子电连接。

195.将电阻41d的电阻值设为r1,将电阻41e的电阻值设为r2,将电阻41b的电阻值设为r3,将电阻41c的电阻值设为r4。若设r1=r3且r2=r4,则电压v2用下述的式(1)表示。

196.v2=r2/r1(v44

‑

voffset)

…

(1)

197.也就是说,减法运算电路41的增益成为r2/r1。减法运算电路41能够通过调整电阻r1至r4从而调整电压v2。

198.第2实施方式的功率放大模块1a通过具备具有温度特性的基准电压输出电路vref2,从而抑制了晶体管q21以及q2的温度特性。另一方面,本实施方式的功率放大模块1b通过在第1集成电路2b内具备二极管dr1以及dr2,并向二极管dr1以及dr2供给电流i41从而使其产生二极管2级份的电压。二极管dr1以及dr2和二极管d11以及d12形成在第1集成电路2b内。因此,能够期待二极管dr1以及dr2的电压与二极管d11以及d12的电压相同。

199.与二极管d11以及d12具有若温度上升则电压下降而若温度下降则电压上升这样的温度特性同样地,二极管dr1以及dr2也具有若温度上升则电压下降而若温度下降则电压上升这样的温度特性。

200.电流i41的电流值是与用可变电阻vr1和电阻阵列32的电阻分压电路对基准电压v21进行了调整的电压相应的电流值。电压voffset的电压值是用缓冲放大器amp3、可变电阻vr2和电阻rcont的电阻分压电路、以及缓冲放大器amp4对基准电压v21进行了调整的电压值。

201.在将第1实施方式中说明的第2以及第3调整过程应用于功率放大模块1b的情况下,通过将开关sw3闭合(接通)从而将电压voffset终止,使减法运算电路41作为缓冲放大器发挥动作。在该情况下,电压v2变得与二极管dr1以及dr2的电压、即二极管d11以及d12的电压相同。由此,功率放大模块1b能够使峰值放大系统与载波放大系统同样地动作,因此能够应用第2以及第3调整过程。

202.如以上说明的那样,功率放大模块1b与功率放大模块1同样地,能够通过电子熔丝f抑制在多赫蒂放大器内也容易受到个体差异的影响的进行c级动作的峰值放大系统的特性的偏差。进而,功率放大模块1b能够比功率放大模块1a精度良好地抑制基于温度的特性变动。

203.<第4实施方式>

204.图14是示出第4实施方式的功率放大模块的电路结构的图。

205.对于第4实施方式的功率放大模块1c的构成要素之中与第1至第3实施方式相同的构成要素,标注相同的参照符号并省略说明。

206.功率放大模块1c包含第1集成电路2c和第2集成电路3c。

207.第1集成电路2c与第3实施方式的第1集成电路2b(参照图13)相比较,不包含二极管dr1以及dr2。

208.第2集成电路3c与第3实施方式的第2集成电路3b(参照图13)相比较,还包含二极管dr1以及dr2。

209.二极管dr1以及dr2相当于本公开的“多个二极管”的一例。

210.也就是说,在第3实施方式的功率放大模块1b中,二极管dr1以及dr2形成在第1集成电路2b(化合物半导体基板的ic芯片)内。与之相对,在第4实施方式的功率放大模块1c中,二极管dr1以及dr2形成在第2集成电路3c(si基板的ic芯片)内。

211.形成在si基板的ic芯片内的二极管dr1以及dr2具有与形成在化合物半导体基板的ic芯片的二极管d11以及d12相同的倾向的温度特性,但接通阈值电压的绝对值不同。因此,使得具有放大电压v44的功能的减法运算电路41产生电压v2。

212.如以上说明的那样,功率放大模块1c与功率放大模块1同样地,能够通过电子熔丝f抑制在多赫蒂放大器内也容易受到个体差异的影响的进行c级动作的峰值放大系统的特性的偏差。进而,功率放大模块1c不会使第1集成电路2c与第2集成电路3c之间的连接布线数增加,能够比功率放大模块1a精度良好地抑制基于温度的特性变动。

213.<第5实施方式>

214.图15是示出第5实施方式的功率放大模块的电路结构的图。

215.对于第5实施方式的功率放大模块1d的构成要素之中与第1至第4实施方式相同的构成要素,标注相同的参照符号并省略说明。

216.功率放大模块1d包含第1集成电路2c和第2集成电路3d。

217.第2集成电路3d包含基准电压输出电路vref、基准电流输出电路iref和可变恒流输出电路31。此外,第2集成电路3d包含缓冲放大器amp1、可变电阻vr1、电阻阵列32和缓冲放大器amp2。此外,第2集成电路3d包含缓冲放大器amp3、可变电阻vr2、电阻rcont、缓冲放大器amp4、开关sw3和减法运算电路41。

218.可变恒流输出电路31相当于本公开的“恒流输出电路”的一例。

219.在第3实施方式的功率放大模块1b(参照图13)中,第2集成电路3b基于设置在第1集成电路2b内的二极管dr1以及dr2的电压而输出了电压v2。另一方面,在本实施方式的功率放大模块1d中,第2集成电路3d基于第1偏置电路17内的二极管d11以及d12的电压来输出电压v2。

220.缓冲放大器amp1的输入端子与端子b1电连接。也就是说,被施加于缓冲放大器amp1的电压v51为二极管d11以及d12的电压。

221.缓冲放大器amp1将基于电压v51的电压v52输出至可变电阻vr1的一端。可变电阻vr1和电阻阵列32的串联电路对电压v52进行电阻分压,并输出电压v53。缓冲放大器amp2将基于电压v53的电压v54经由电阻41b而输出至运算放大器41a的同相输入端子。

222.如以上说明的那样,功率放大模块1d与功率放大模块1同样地,能够通过电子熔丝

f抑制在多赫蒂放大器内也容易受到个体差异的影响的进行c级动作的峰值放大系统的特性的偏差。进而,功率放大模块1d不会使第1集成电路2c与第2集成电路3d之间的连接布线数增加,能够比功率放大模块1c精度良好地抑制基于温度的特性变动。

223.<第6实施方式>

224.图16是示出第6实施方式的功率放大模块的电路结构的图。

225.对于第6实施方式的功率放大模块1e的构成要素之中与第1至第5实施方式相同的构成要素,标注相同的参照符号并省略说明。

226.功率放大模块1e包含第1集成电路2e和第2集成电路3e。第1集成电路2e包含匹配电路61、dc截止电容器cd1、驱动放大器11、第3偏置电路62和匹配电路63。

227.在匹配电路61,经由端子1a被输入高频输入信号rfin。高频信号rf1经由匹配电路61以及dc截止电容器cd1而供给至驱动放大器11内的晶体管qd1的基极。

228.晶体管qd1的发射极与基准电位电连接。晶体管qd1的集电极经由扼流电感器l2而与电源电位vcc电连接。晶体管qd1将对高频输入信号rfin进行了放大的高频信号rf6经由匹配电路63而输出至dc截止电容器c1以及移相器14。

229.第3偏置电路62包含二极管dd1以及dd2、晶体管qdd和电阻rbiasd1。二极管dd1以及dd2各自例示的是被二极管连接的hbt。

230.在二极管dd1的阳极,经由端子b3从第2集成电路3e被输入偏置电流(偏置电压)。二极管dd1的阴极与二极管dd2的阳极电连接。二极管dd2的阴极与基准电位电连接。二极管dd1以及dd2的串联连接电路产生一定的电压。

231.二极管dd1以及dd2的串联连接电路的电压被输入至晶体管qdd的基极。晶体管qdd的集电极经由端子cq31以及端子1d而与电源电位vcbias2电连接。晶体管qdd的发射极经由电阻rbiasd1而与晶体管qd1的基极电连接。也就是说,晶体管qdd以及电阻rbiasd1被进行了发射极跟随连接。晶体管qd1的基极电流基于被施加于晶体管qdd的基极的电压来决定。

232.像这样,用于向第3偏置电路62供给功率的端子1d与用于向第1偏置电路17以及第2偏置电路18供给功率的端子1c不同。因此,可抑制第3偏置电路62给第1偏置电路17内的晶体管q11的集电极电流以及第2偏置电路18内的晶体管q21的集电极电流的测定带来影响。由此,功率放大模块1e能够精度良好地进行载波放大器12以及峰值放大器13的偏置的设定。

233.另外,上述的实施方式用于使本发明容易理解,并非用于限定解释本发明。本发明能够在不脱离其主旨的情况下进行变更/改良,并且其等价物也包含于本发明。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。