一种基于dds的高精度信号发生器

技术领域

1.本技术涉及信号发生器技术领域,尤其是涉及一种基于dds的高精度信号发生器。

背景技术:

2.dds是直接数字式频率合成器(directdigital synthesizer),目前的信号发生器普遍采用dds技术来产生波形,与传统的频率合成器相比,dds具有低成本、低功耗、高分辨率和快速转换时间等优点,广泛使用在电子仪器领域,是实现设备全数字化的一项关键技术。

3.音频扫频信号发生器是音频相关产品生产测试中的一类十分重要的仪器。目前市场上的音频扫频信号发生器有很大的比例是调谐信号发生器,该种仪器结构复杂、频率范围窄,而且稳定性较差,但其价格低廉;在此基础上发展起来的锁相信号发生器频率精度和稳定度高,但要实现快速、程控比较困难,同时输出信号的频率分辨率较差;而合成信号发生器具有较高的频率稳定度,频率分辨率高和频率的设定重复性好,能方便实现频率的程序控制;最新的技术是数字处理技术与信号合成相结合,即直接数字合成技术(directdigital synthesis,简称dds),基于dds技术的信号发生器频率转换时间短、相对带宽宽、频率分辨率高、输出相位连续等优点,可以实现对信号的全数字调制。

技术实现要素:

4.为了改善现有技术中的音频扫频信号发生器结构复杂、频率范围窄,而且稳定性较差的问题,本技术提供一种基于dds的高精度信号发生器。采用如下的技术方案:

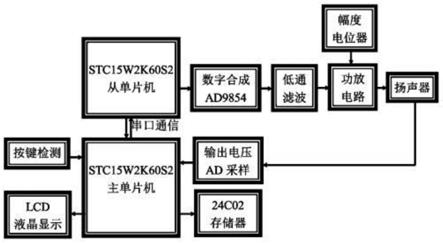

5.一种基于dds的高精度信号发生器,包括主芯片模块、从芯片模块、数字sdd合成器、滤波模块、数字功放模块、数控电位器、扬声器、ad模块电压采样电路、存储器、按键模块和显示模块,按键模块输出端与主芯片模块的输入端连接,显示模块的输入端与主芯片模块的输出端连接,存储器与主芯片模块通信连接,主芯片模块与从芯片模块数据通讯连接,从芯片模块的输出端与数字sdd合成器的输入端连接,数字sdd合成器的输出端与滤波模块的输入端连接,滤波模块的输出端与数字功放模块的输入端连接,数字功放模块的输出端与扬声器的输入连接,数控电位器的输出端与数字功放模块的输入端连接,ad模块电压采样电路的检测端与扬声器的接收端连接。

6.优选的,所述主芯片模块和从芯片模块均为stc15w2k60s2型单片机。

7.优选的,所述数字sdd合成器为ad9854型数字sdd合成器。

8.优选的,所述按键模块包括74ls245型驱动器和多个按键,多个按键分别与74ls245型驱动器上对应的输入端连接,74ls245型驱动器的输出端与主芯片模块的输入端连接。

9.优选的,多个按键包括上限、下限、增加、减少、扫频、手动、速度和复位的功能按键。

10.优选的,所述滤波模块为低通滤波器。

11.优选的,所述数字功放模块为由lf347型运算放大器一、lm3886型功率音频放大集成电路组成的功率放大电路,lf347型运算放大器一中的一运算放大器模块输入端与滤波模块的输出端连接,该处的运算放大器模块的输出端串联幅度数控电位器后与lf347型运算放大器一中的另一运算放大器模块的输入端连接,该处的运算放大器模块的输出端与lm3886型功率音频放大集成电路的输入端连接,lm3886型功率音频放大集成电路的输出端与扬声器的接收端连接。

12.优选的,所述ad模块电压采样电路包括lf347型运算放大器二、lm336

‑

2.5电源基准芯片、cd4051多路选择开关和ads8326高速低功耗模拟数字转换器,lf347型运算放大器二包括4个运算放大器模块,4个运算放大器模块分别定义为运算放大器一、运算放大器二、运算放大器三、运算放大器四,运算放大器一的正极端连接扬声器的接收端,运算放大器一的输出端与运算放大器二的负极端连接,运算放大器二的输出端与运算放大器三的负极端连接,运算放大器三的输出端与运算放大器四的正极端连接,运算放大器四的输出端与cd4051多路选择开关的一输入端连接,cd4051多路选择开关的输出端与ads8326高速低功耗模拟数字转换器的输入端连接,ads8326高速低功耗模拟数字转换器的输出端与主芯片模块的输入端连接,lm336

‑

2.5电源基准芯片连接外部电源,lm336

‑

2.5电源基准芯片的输出端分别连接cd4051多路选择开关的输入端和ads8326高速低功耗模拟数字转换器的基准电压端。

13.优选的,所述显示模块为128*64点阵的dg12864液晶模块。

14.与现有技术相比,本发明的有益效果是:基于dds技术的信号发生器频率转换时间短、相对带宽宽、频率分辨率高、输出相位连续等优点,可以实现对信号的全数字调制;

15.本发明以stc15w2k60s2单片机为主控制器,基于dds芯片ad9854,采用数字模拟相结合的方式实现20hz

‑

20khz的音频正弦波输出,失真小,稳定性好,特别适合检听扬声器纯音。具有对数扫频和手动单频输出两种工作方式,每种扫频方式的扫频起点、终点及扫频时间均可任意设定。单频输出频率也可在音频范围内任意设定。人机界面采用128

×

64点阵液晶块显示,同时显示频率和电压值。具体特点如下:

16.(1)stc15w2k60s2单片机是宽电源电压mcu,可在3v电源下工作,与dds芯片ad9854相统一,不需要电平转换芯片(如74lvc245等),并且内设eeprom不需外接at24c02,使得系统结构更加简单紧凑,可靠性提高,成本降低。

17.(2)采用双mcu结构设计,主mcu主要负责人机界面功能,从mcu专职负责控制dds芯片输出正弦波信号,提高信号处理速度,提高频率精度和分辨率。

18.(3)设置多种扫频模式,包括普通扫频模式、ab扫频模式和abc扫频模式,满足检听扬声器纯音等特定产品生产的测试需要。

19.(4)设置手动单频和扫频输出两种模式,输出正弦波幅度也可以手动和自动两种方式控制,使用方便,便于生产自动测试和遥控需要。

附图说明

20.图1为本发明的系统原理结构框图;

21.图2为本发明的按键模块电路原理图;

22.图3为本发明的系统电源电路原理图;

23.图4为本发明的输出直流偏置保护电路原理图。

具体实施方式

24.以下结合附图1~4对本技术作进一步详细说明。

25.本技术实施例公开一种基于dds的高精度信号发生器。

26.参照图1~图4,一种基于dds技术的音频扫频信号发生器,包括主芯片模块、从芯片模块、数字sdd合成器、滤波模块、数字功放模块、数控电位器、扬声器、ad模块电压采样电路、存储器、按键模块和显示模块,按键模块输出端与主芯片模块的输入端连接,显示模块的输入端与主芯片模块的输出端连接,存储器与主芯片模块通信连接,主芯片模块与从芯片模块数据通讯连接,从芯片模块的输出端与数字sdd合成器的输入端连接,数字sdd合成器的输出端与滤波模块的输入端连接,滤波模块的输出端与数字功放模块的输入端连接,数字功放模块的输出端与扬声器的输入连接,数控电位器的输出端与数字功放模块的输入端连接,ad模块电压采样电路的检测端与扬声器的接收端连接。

27.所述主芯片模块和从芯片模块均为stc15w2k60s2型单片机。

28.所述数字sdd合成器为ad9854型数字sdd合成器。

29.所述按键模块包括74ls245型驱动器和多个按键,多个按键分别与74ls245型驱动器上对应的输入端连接,74ls245型驱动器的输出端与主芯片模块的输入端连接。

30.多个按键包括上限、下限、增加、减少、扫频、手动、速度和复位的功能按键。

31.所述滤波模块为低通滤波器。

32.所述数字功放模块为由lf347型运算放大器一、lm3886型功率音频放大集成电路组成的功率放大电路,lf347型运算放大器一中的一运算放大器模块输入端与滤波模块的输出端连接,该处的运算放大器模块的输出端串联幅度数控电位器后与lf347型运算放大器一中的另一运算放大器模块的输入端连接,该处的运算放大器模块的输出端与lm3886型功率音频放大集成电路的输入端连接,lm3886型功率音频放大集成电路的输出端与扬声器的接收端连接。

33.所述ad模块电压采样电路包括lf347型运算放大器二、lm336

‑

2.5电源基准芯片、cd4051多路选择开关和ads8326高速低功耗模拟数字转换器,lf347型运算放大器二包括4个运算放大器模块,4个运算放大器模块分别定义为运算放大器一、运算放大器二、运算放大器三、运算放大器四,运算放大器一的正极端连接扬声器的接收端,运算放大器一的输出端与运算放大器二的负极端连接,运算放大器二的输出端与运算放大器三的负极端连接,运算放大器三的输出端与运算放大器四的正极端连接,运算放大器四的输出端与cd4051多路选择开关的一输入端连接,cd4051多路选择开关的输出端与ads8326高速低功耗模拟数字转换器的输入端连接,ads8326高速低功耗模拟数字转换器的输出端与主芯片模块的输入端连接,lm336

‑

2.5电源基准芯片连接外部电源,lm336

‑

2.5电源基准芯片的输出端分别连接cd4051多路选择开关的输入端和ads8326高速低功耗模拟数字转换器的基准电压端。

34.所述显示模块为128*64点阵的dg12864液晶模块。

35.与现有技术相比,本发明的有益效果是:基于dds技术的信号发生器频率转换时间短、相对带宽宽、频率分辨率高、输出相位连续等优点,可以实现对信号的全数字调制。

36.扫频音频信号输出是在从单片机内设置需要的扫频点,这些扫频点按照对数规律

设置,存储在单片机内。由主单片机根据用户设置的内容将相关数据通过串口发送到从单片机,从单片机根据这些设置控制ad9854输出相对应频率和幅值的正弦波输出信号。扫频点数据设置依据如下扫频公式确定:

37.其中n=0,

±

1,

±2…

,n的每个取值就对应一个扫频点数据;k是倍频程,本设计选k=96,即按96倍频程扫频。

38.按公式1设置扫频点,即k=96,根据n=0,

±

1,

±2…

,满足从20

‑

20khz的范围,以1000hz为中心,设置816个频率点。

39.3.扫频速度实现

40.扫频速度是由主机发送过来的是扫频时间t决定的,由于从机中的扫频点数据表格长度是816个,即有816个频点,按照双向扫频,总共有(816

‑

1)*2=1630个间隙,每个间隙的等待时间是t/1630,由于扫频时间设置范围是0.2

‑

20s,而单片机的晶振频率选为22.1184mhz,则最快扫频时每个时间间隔是0.2/1730=0.1227ms,若设定时间隔为,选择定时器1实现定时功能,设初始值为x,则计算过程如下:

41.整理后可得定时器1的初值为:x=65535

‑

613.5t,t的时间单位是秒。

42.以上均为本技术的较佳实施例,并非依此限制本技术的保护范围,故:凡依本技术的结构、形状、原理所做的等效变化,均应涵盖于本技术的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。