1.本发明属于半导体封装技术领域,特别是涉及一种降低切筋应力影响的封装筛选方法。

背景技术:

2.半导体放电管tss(thyristor surge suppressor)应用于特殊行业应用时,如工业电子雷管,对产品性能的温度性要求很高,常常需要进行严酷的环境测试;并且由于出货数量巨大,对其产品成品的不良率ppm要求很高,常常要求50ppm以下。

3.半导体放电管tss在封装生产过程中,由于芯片较小,通过框架结构的方式进行sod

‑

123fl封装时,在切筋工序,如采用传统切筋工艺、切刀和夹持装置,容易引起芯片隐裂、芯片歪斜、包封体裂纹、引脚应力释放不足等众多常规电性无法检测或筛查的问题,不良率在千分之五以上。因此,优化切筋方式,创新切筋装置,以及提供优化的筛查方法,有利于减小产品失效ppm值,对于半导体行业具有重要意义。

技术实现要素:

4.本发明提供了一种降低切筋应力影响的封装筛选方法,解决了以上问题。

5.为解决上述技术问题,本发明是通过以下技术方案实现的:

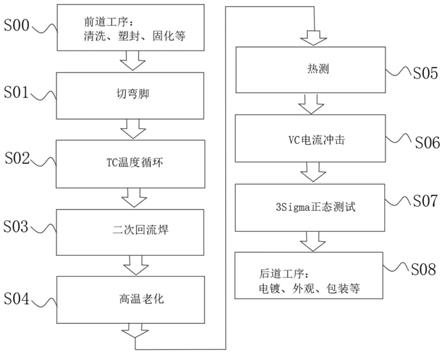

6.本发明的一种降低切筋应力影响的封装筛选方法,包括采用优化的筛选流程,包括如下步骤:

7.s00、对器件进行切筋前的前道工序:包括固晶点胶、高温焊接、清洗、塑封成型、塑封固化;

8.s01、切弯脚:使用切筋装置对塑封后的器件进行切筋、弯脚整形;

9.s02、tc温度循环,通过高低温进行多次温度循环对芯片损坏或隐裂的产品进行应力放大,使故障特征明显化,更易于电性筛查;

10.s03、二次回流焊:通过两次回流焊,模拟实际焊接温度要求,筛查内部虚焊和电性不稳定产品;

11.s04、高温老化:通过150℃高温几个小时至几十个小时的老化,让内部结构不稳定的临界产品失效,便于筛除;

12.s05、热测:让产品通过恒温热测轨道,对产品电性能,进行恒温热测;

13.s06、vc电流冲击:对产品进行80%额定值的浪涌电流冲击,筛除芯片潜在缺陷风险的产品;

14.s07、3sigma正态测试:利用测试系统的3σ界限控制,对产品的电参数一致性进行管控;

15.s08、后道工序,包括引脚电镀、电镀后电性的3sigma正态测试、成品外观检验、包装。

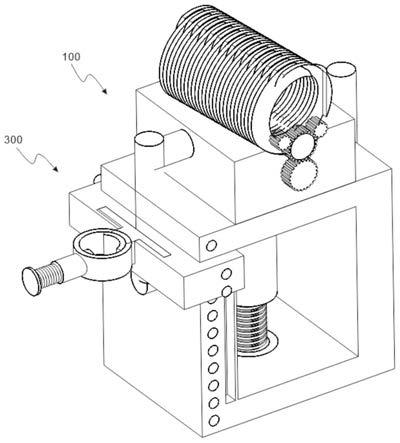

16.进一步地,所述s01中切筋装置包括下方支持结构体、设置于下方支持结构体上部

两侧的下外侧夹具、设置于下方支持结构体上且位于两下外侧夹具之间的“凵”字形下内侧夹具、设置于下外侧夹具上部的两上外侧夹具、设置于两上外侧夹具之间的上内侧夹具、分别设置于上内侧夹具与两上外侧夹具之间的切刀;所述器件包括夹持于上外侧夹具与下外侧夹具之间的器件金属引脚以及设置于器件金属引脚底部且位于“凵”字形下内侧夹具内的器件塑封体。

17.进一步地,所述器件金属引脚与切刀保持90

°

的垂直切角。

18.进一步地,所述s02步骤中温度循环采用双恒温箱的实验炉,低温

‑

55℃,高温 150℃,循环n次;其中,低温

‑

55℃保持5min,迅速切换至 150℃并保持5min。

19.进一步地,所述s03步骤中的二次回流焊,最高温区温度为260℃,两次回流焊之间,常温冷却15min。

20.进一步地,所述s04步骤中高温老化,具体为将s03步骤后的产品进行高温存放,在150℃温度下保持24小时。

21.进一步地,所述s05步骤中热测是指在高温老化结束后,将物料放入至恒温炉中,1小时后取料,进行tmtt电性测试。

22.进一步地,所述s06步骤,具体是采用80%额定的10/1000us浪涌电流对产品进行vc电流冲击。

23.进一步地,所述s07步骤的3sigma正态测试是指利用测控系统的3σ界限控制,对产品的电参数进行一致性管控。

24.进一步地,所述s08步骤中,筛查后道工序包括引脚电镀、电镀后进行3sigma正态电性测试、成品外观检验、产品包装。

25.本发明相对于现有技术包括有以下有益效果:

26.1、本发明提供的切筋装置,通过改变器件的夹持方式,在器件的四个着力点增加夹持器具,在切刀受力的内外侧同时进行夹持,改善了原有上下对冲的切筋方式,减小了巨大的切筋应力,从而减少了芯片碎裂的发生,从封装源头进行了改善;

27.2、本发明采用tc温度循环,二次回流焊,高温老化等温度冲击和温度循环试验,对产品施加环境应力,促使存在潜在缺陷的产品加速暴露,有利于早期失效筛除,保障了产品的可靠性,降低成品失效概率,提升成品良率;

28.3、本发明采用vc电流冲击测试,进一步模拟器件的实际使用情况,使用趋于产品极限阈值的电流来评估产品的实际能力;再配合3σ参数管控,进一步保证不良品不流入客户市场,保障成品的优秀品质;

29.4、本发明根据实际产品数据,在已完成的10kk以上的成品对照中,在相同的芯片情况下,优化筛选装置和筛选方法后的产品,相比优化前,失效率下降明显;同时成品的稳定性、可靠性也有了较大提升,因此,本发明是一种提高产品品质的有效优选方法。

30.当然,实施本发明的任一产品并不一定需要同时达到以上所述的所有优点。

附图说明

31.为了更清楚地说明本发明实施例的技术方案,下面将对实施例描述所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附

图。

32.图1为本发明的一种降低切筋应力影响的封装筛选方的步骤图;

33.图2为本发明的切筋装置的结构示意图;

34.图3为利用上限3sixma、下限3sixma产品进行测试获取软件测试图;

35.图4为基于3sixma品质管控法的步骤图;

36.图5为现有的切筋装置的结构示意图;

37.附图中,各标号所代表的部件列表如下:

38.101

‑

上外侧夹具,102

‑

上内侧夹具,103

‑

切刀,104

‑

器件金属引脚,105

‑

下外侧夹具,106

‑

下方支持结构体,107

‑“

凵”字形下内侧夹具,108

‑

器件塑封体。

具体实施方式

39.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其它实施例,都属于本发明保护的范围。

40.在本发明的描述中,需要理解的是,术语“两侧”、“下方”、“垂直”、“内侧”等指示方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的组件或元件必须具有特定的方位,以特定的方位构造和操作,因此不能理解为对本发明的限制。

41.如图5所示,为现有的切筋装置,其切刀和夹持装置,容易引起芯片隐裂、芯片歪斜、包封体裂纹、引脚应力释放不足等多常规电性无法检测或筛查的问题,不良率在千分之五以上,并且现有的筛选流程和工艺的检测效率和精度都相对较低。

42.因此针对以上问题,本发明提出了一种降低切筋应力影响的封装筛选方法,具体是采用优化的切筋装置,来实现减少由切筋应力产生的芯片碎裂、芯片隐裂、芯片歪斜、包封体裂纹等不良情况,同时创新筛选流程,通过严格的筛查,提升产品的可靠性,保证产品质量,具体方案如下。

43.请参阅图1

‑

4所示,本发明的一种降低切筋应力影响的封装筛选方法,采用优化的筛选流程,包括如下步骤:

44.s00、对器件进行切筋前的前道工序:包括固晶点胶、高温焊接、清洗、塑封成型、塑封固化;

45.s01、切弯脚:使用切筋装置对塑封后的器件进行切筋、弯脚整形;其中切筋具有较大冲击力,容易产生芯片隐裂、芯片歪斜、塑封体裂纹及其它封装应力问题,通过改进切筋装置有效降低切筋应力、减少切筋引起的芯片损坏问题;

46.s02、tc温度循环,通过高低温进行10次温度循环对芯片损坏或隐裂的产品进行应力放大,使故障特征明显化,更易于电性筛查;

47.s03、二次回流焊:通过两次回流焊,模拟实际焊接温度要求,筛查内部虚焊和电性不稳定产品;

48.s04、高温老化:通过150℃高温几个小时至几十个小时的老化,让内部结构不稳定的临界产品失效,便于筛除;

49.s05、热测:让产品通过恒温热测轨道,对产品电性能(尤其为漏电流),进行恒温热

测;恒温热测在一般产品封装中不会采用,只有在对产品质量有很高要求才采用;恒温炉让产品加温(温度达到120℃以上),并在恒温轨道进行温度保持的情况下,进行电性测试;

50.通过恒温热测,可以检测出产品在高温下的电性能稳定性;

51.s06、vc电流冲击:对产品进行80%额定值的浪涌电流(10/1000us)冲击,筛除芯片潜在缺陷风险的产品;

52.s07、3sigma正态测试:利用测试系统的3σ界限控制,对产品的电参数一致性进行管控;(3sigma属于较为严苛的参数管控手段,常规情况不会使用),产品质量符合正态分布,在

±

3σ范围参数内包含了99.73%的质量特征值;将超过

±

3σ范围的产品当做不合格品进行筛除;

53.s08、后道工序,包括引脚电镀、电镀后电性的3sigma正态测试、成品外观检验、包装。

54.其中,s01中切筋装置包括下方支持结构体106、设置于下方支持结构体106上部两侧的下外侧夹具105、设置于下方支持结构体106上且位于两下外侧夹具105之间的“凵”字形下内侧夹具107、设置于下外侧夹具105上部的两上外侧夹具101、设置于两上外侧夹具101之间的上内侧夹具102、分别设置于上内侧夹具102与两上外侧夹具101之间的切刀103;器件包括夹持于上外侧夹具101与下外侧夹具105之间的器件金属引脚104以及设置于器件金属引脚104底部且位于“凵”字形下内侧夹具107内的器件塑封体108。

55.其中,器件金属引脚104与切刀103保持90

°

的垂直切角。

56.其中,s02步骤中温度循环采用双恒温箱的实验炉,低温

‑

55℃,高温 150℃,循环10次;其中,低温

‑

55℃保持5min,迅速切换至 150℃并保持5min。

57.其中,s03步骤中的二次回流焊,最高温区温度为260℃,两次回流焊之间,常温冷却15min。

58.其中,s04步骤中高温老化,具体为将s03步骤后的产品进行高温存放,在150℃温度下保持24小时。

59.其中,s05步骤中热测是指在高温老化结束后,将物料放入至恒温炉中,1小时后取料,进行tmtt电性测试。

60.其中,s06步骤,具体是采用80%额定的10/1000us浪涌电流对产品进行vc电流冲击。

61.其中,s07步骤的3sigma正态测试是指利用测控系统的3σ界限控制,对产品的电参数进行一致性管控;具体的步骤是如图3和4所示:

62.首先,测试前参照规格书确定参数的标注;

63.然后,同一批次产品,选取前3000组数据;

64.接着,计算出来标准差s和平均值

65.再然后,测试机设定上限下限

66.最后,上下下限并且保证在规格范围;

67.具体计算公式是:

68.s:标准差,n:3000pcs设定样本,3000样本的平均数;3sixma

是优中选优,所有参数是良品,我们在良品中,软件动态地把合格参的产数指标进行计算,把集中在中心值,上限3sixma,下限3sixma的产品拿来使用。

69.其中,s08步骤中,筛查后道工序包括引脚电镀、电镀后进行3sigma正态电性测试、成品外观检验、产品包装。

70.本发明中,采用优化的切筋装置,来实现减少由切筋应力产生的芯片碎裂、芯片隐裂、芯片歪斜、包封体裂纹等不良情况,同时创新筛选流程,通过严格的筛查,提升产品的可靠性,保证产品质量。相比优化前,失效率下降明显;同时成品的稳定性、可靠性也有了较大提升,因此,本发明是一种提高产品品质的有效优选方法。

71.有益效果:

72.1、本发明提供的切筋装置,通过改变器件的夹持方式,在器件的四个着力点增加夹持器具,在切刀受力的内外侧同时进行夹持,改善了原有上下对冲的切筋方式,减小了巨大的切筋应力,从而减少了芯片碎裂的发生,从封装源头进行了改善;

73.2、本发明采用tc温度循环,二次回流焊,高温老化等温度冲击和温度循环试验,对产品施加环境应力,促使存在潜在缺陷的产品加速暴露,有利于早期失效筛除,保障了产品的可靠性,降低成品失效概率,提升成品良率;

74.3、本发明采用vc电流冲击测试,进一步模拟器件的实际使用情况,使用趋于产品极限阈值的电流来评估产品的实际能力;再配合3σ参数管控,进一步保证不良品不流入客户市场,保障成品的优秀品质;

75.4、本发明根据实际产品数据,在已完成的10kk以上的成品对照中,在相同的芯片情况下,优化筛选装置和筛选方法后的产品,相比优化前,失效率下降明显;同时成品的稳定性、可靠性也有了较大提升,因此,本发明是一种提高产品品质的有效优选方法。

76.以上公开的本发明优选实施例只是用于帮助阐述本发明。优选实施例并没有详尽叙述所有的细节,也不限制该发明仅为所述的具体实施方式。显然,根据本说明书的内容,可作很多的修改和变化。本说明书选取并具体描述这些实施例,是为了更好地解释本发明的原理和实际应用,从而使所属技术领域技术人员能很好地理解和利用本发明。本发明仅受权利要求书及其全部范围和等效物的限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。