1.本发明涉及一种半导体器件,尤其涉及一种碳化硅半导体器件及加工方法。

背景技术:

2.碳化硅作为第三代宽禁带半导体材料的典型代表,具有宽禁带宽度高临界击穿场强、高热导率及髙载流子饱和速率等特性。上述材料优势使得sic功率半导体器件在新能源发电、高铁牵引设备、混合动力汽车等中高耐压等级应用领域具有广阔的发展前景。

3.碳化硅功率器件通常包括jbs、mps、mosfet、jfet、igbt等器件种类,在器件完成芯片制造后,业界会进行cp测试标定芯片不良品。

4.作为高耐压产品,碳化硅目前应用在650v到1700v产品领域,对于1200v碳化硅成品,其反向雪崩电压通常在1400v以上,对于1700v碳化硅产品,其反向雪崩电压达到2000v以上,同时,市场上还存在3300v以及更高电压的sic器件,极高的电压给晶圆测试环节带来一定的难度。

5.晶圆cp(chip probe)测试是对半导体晶圆上的每个芯片进行检测,对于垂直型的碳化硅器件,一般模式是在cp测试台上安装探针卡,探卡与芯片上的正面电极直接接触,探针台与芯片的背面电极接触,形成完整回路进行测试,不合格的芯片在测试过程中被记录标定。而碳化硅作为耐高压产品,在晶圆高压点测时,当反向电压达到1200v以上时,由于芯片划片道与背面电极等势,会造成晶圆正面电极与划片道之间的空气电离,进而发生打火(arcing)现象,损坏晶圆和测试设备。在一般未做保护的情况下,因打火导致的良率损失可以达到20%以上。针对这一问题,传统测试方法是通过探卡在芯片表面吹n2或cda,降低芯片表面气压,从而提高空气击穿电压来避免打火现象;或者针对更高耐压的器件,会采用让芯片整体浸泡在氟油环境中来避免空气被高压电离。但是这两种方法不能从根本上解决打火问题,吹气法中,过大的气流量会吹飞芯片,尤其对于减薄晶圆,造成芯片损伤,而较小的气流量又几乎不能避免打火现象;而氟油法,对于如何量产化处理晶圆浸泡氟油和测试完后的氟油清洁都是业界难题。

技术实现要素:

6.本发明针对以上问题,提供了一种降低测试时的空气电场强度,避免打火现象的一种碳化硅半导体器件及加工方法。

7.本发明的技术方案是:一种碳化硅半导体器件,包括碳化硅衬底正面的外延层和背面依次设置的欧姆接触电极和加厚金属;还包括p型掺杂区一、p型掺杂区二、正面金属接触电极、加厚金属、钝化层和p型掺杂区三;所述p型掺杂区二、p型掺杂区一和p型掺杂区三依次设置在外延层上;所述正面金属接触电极和加厚金属从下而上依次设置在所述p型掺杂区二的上方;所述钝化层位于器件的顶部,底部分别与p型掺杂区一和p型掺杂区三接触,侧部

分别与正面金属接触电极和加厚金属接触。

8.所述钝化层包括氮化硅材料的无机钝化层和有机钝化层。

9.所述p型掺杂区三的截面呈矩形,与所述p型掺杂区一之间设有间距。

10.所述p型掺杂区三的截面呈若干间隔设置的矩形结构。

11.一种碳化硅半导体器件加工方法,包括以下步骤:1)在碳化硅衬底上生长一层外延层;2)在所述外延层中通过离子注入形成p型掺杂区一、p型掺杂区二和p型掺杂区三;3)在形成正面金属接触电极;4)在正面金属接触电极上沉积加厚金属作为电极引出;5)在器件终端位置制作钝化层;6)在碳化硅衬底的背面制作欧姆接触电极;7)在欧姆接触电极上沉积加厚金属,完成器件制作。

12.步骤2)中一次性离子注入形成p型掺杂区一、p型掺杂区二和p型掺杂区三,掺杂的杂质为al,注入温度在400

‑

600 ℃。

13.步骤2)中分开制作p型掺杂区一、p型掺杂区二和p型掺杂区三;先用al离子注入形成p型掺杂区一,形成p型掺杂区三;再重新光刻用al离子注入形成p型掺杂区二;注入完成后通过1600

‑

1900 ℃的高温退火进行离子激活。

14.步骤2)中分开制作p型掺杂区一、p型掺杂区二和p型掺杂区三;先用al离子注入形成p型掺杂区一;再重新光刻用al离子注入形成p型掺杂区二,离子注入制作p型掺杂区二的同时打开划片道窗口制作p型掺杂区三,形成p型掺杂区三;注入完成后通过1600

‑

1900 ℃的高温退火进行离子激活。

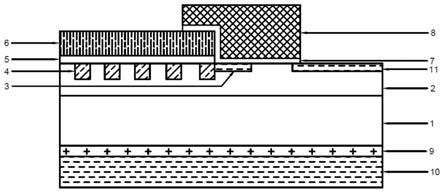

15.本发明制作的过程不增加工艺复杂度和制造成本,形成的划片道p区器件结构由于远离终端,反向高压甚至雪崩状态时几乎不影响器件的终端截止效率。同时,在反向加压时,尤其是加到1000v以上的高压时,背面电极的等势面将不在划片道表面,由于划片道pn结反向耗尽,其电场梯度几乎全部转移到耗尽区内,划片道表面电势将被极大限度的拉低,形成与正面加厚电极(6)之间的电势差被缩小到可以忽略的状态,因此,两者之间的电势差根本不足以激发空气电离,如此便可以避免上述打火现象的发生。

附图说明

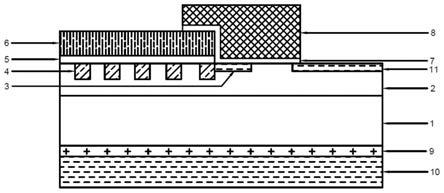

16.图1是本发明的结构示意图一,图2是图1的俯视结构示意图,图3是本发明的结构示意图二,图4是图3的俯视结构示意图,图5是步骤1)生长外延层的结构示意图,图6是步骤2)的结构示意图,图7是步骤3)形成正面金属接触电极的结构示意图,图8是步骤4)沉积加厚金属的结构示意图,

图9是步骤5)制作钝化层的结构示意图,图10是步骤6)制作欧姆接触电极的结构示意图,图11是步骤7)沉积加厚金属的结构示意图;图中1是碳化硅衬底,2是外延层,3是p型掺杂区一,4是p型掺杂区二,5是正面金属接触电极,6是加厚金属,7是无机钝化层,8是有机钝化层,9是欧姆接触电极,10是加厚金属,11是p型掺杂区三。

具体实施方式

17.下面详细描述本发明的实施例,所述实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施例是示例性的,仅用于解释本发明,而不能理解为对本发明的限制。

18.本发明如图1

‑

11所示,本案主要针对的器件可以是碳化硅sbd、jbs、mps、igbt、mosfet、jfet等一切垂直型功率器件。以sic jbs二极管为例,一个典型的器件制作过程包括:一种碳化硅半导体器件,包括碳化硅衬底1正面的外延层2和背面依次设置的欧姆接触电极9和加厚金属10;其特征在于,还包括p型掺杂区一3、p型掺杂区二4、正面金属接触电极5、加厚金属6、钝化层和p型掺杂区三11;所述p型掺杂区二4、p型掺杂区一3和p型掺杂区三11依次设置在外延层2上;所述正面金属接触电极5和加厚金属6从下而上(以图1方向为参考方向)依次设置在所述p型掺杂区二4的上方;所述钝化层位于器件的顶部(终端),底部分别与p型掺杂区一3和p型掺杂区三11接触,侧部分别与正面金属接触电极5和加厚金属6接触。

19.所述钝化层包括氮化硅材料的无机钝化层7和有机钝化层8。

20.所述p型掺杂区三11的截面呈矩形,与所述p型掺杂区一3之间设有间距。

21.关于划片道p型掺杂区三11的形貌,典型的设计是划片道p型掺杂区三11横向贯穿整个划片道图1,并且p型掺杂区三11的左侧与p型掺杂区一3右侧图1之间的距离目前保持在30um以上。

22.图1中划片道p型掺杂区三11的形貌,典型的设计是划片道p型掺杂区三11横向贯穿整个划片道,并且p型掺杂区三11的左侧与p型掺杂区一3右侧之间保持一定的间距,这个间距与产品的反向耐压值有关系,即p型掺杂一3终端的长度与产品的反向耐压值有关,耐压值越大,其终端长度越大,故p型掺杂区三11的左侧与p型掺杂区一3右侧其间距越小。

23.所述p型掺杂区三11的截面呈若干间隔设置的矩形结构。

24.把划片道p型掺杂区制作成间断结构(图3),降低划片道在反向承压时的耗尽影响,同时也可以抑制测试打火。

25.一种碳化硅半导体器件加工方法,包括以下步骤:1)如图5所示,在碳化硅衬底1上生长一层碳化硅外延层2;碳化硅衬底1和碳化硅外延层2导电类型通常都是n型;2)如图6所示,在所述外延层2中通过离子注入形成p型掺杂区一3、p型掺杂区二4和p型掺杂区三11;

离子注入的方式一般存在两种做法:第一种是一次性注入同时形成p型掺杂区一3与p型掺杂区二4结构,针对地设计为场限环终端,此步工艺采用的离子注入可以是单次注入,也可以多次注入,掺杂杂质一般是al,注入温度在400

‑

600 ℃,完成注入时一般形成0.4

‑

1.0um的p型掺杂结;如果采用p型掺杂区一3和p型掺杂区二4同时制作的方案,则在离子注入的过程中,在划片道位置同时形成p型掺杂区三11,注入方式和条件与p型掺杂区一3、p型掺杂区二4注入保持一致。

26.第二种做法是分开制作p型掺杂区一3和p型掺杂区二4,先用al离子注入形成p型掺杂区一3,再重新光刻用al离子注入形成p型掺杂区二4,这种设计一般针对jte终端,形成的p型掺杂区一3区呈现第一种方法的效果,而p型掺杂区二4区通常会比p型掺杂区一3掺杂更轻,结深更浅,例如典型地,p型掺杂区一3结深为0.7um,p型掺杂区二4区结深为0.4um。上述所有离子注入的注入能量范围覆盖30

‑

500 kev,注入剂量范围覆盖1e12

‑

1e16 cm

‑

2。完成注入后需要1600

‑

1900 ℃的高温退火进行离子激活。

27.采用p型掺杂区一3和p型掺杂区二4分步制作的方案,则可以在离子注入制作p型掺杂区一3的同时打开划片道窗口制作p型掺杂区三11,也可以在离子注入制作p型掺杂区二4的同时打开划片道窗口制作p型掺杂区三11。

28.3)如图7所示,在有源区图一5覆盖的范围形成正面金属接触电极5;例如在sbd、jbs、mps等器件中以肖特基金属形成正面电极肖特基接触,在igbt、fet、mps器件中以欧姆金属形成正面电极欧姆接触。

29.4)如图8所示,在正面金属接触电极5上沉积加厚金属6作为电极引出;5)如图9所示,在器件终端位置制作钝化层;普遍做法是双层结构,包括至少一层的氮化硅材料的无机钝化层7和一层以polyimide聚酰亚胺为主的有机钝化层8。

30.6)如图10所示,在碳化硅衬底1的背面制作欧姆接触电极9;制作位序需要根据是否进行晶圆减薄调整,典型的以减薄工艺为例,背面欧姆电极9会放在减薄工艺后通过激光退火完成欧姆合金。

31.7)如图11所示,在欧姆接触电极9上沉积加厚金属10,完成器件制作。

32.步骤2)中一次性离子注入形成p型掺杂区一3、p型掺杂区二4和p型掺杂区三11,掺杂的杂质为al,注入温度在400

‑

600 ℃。

33.步骤2)中分开制作p型掺杂区一3、p型掺杂区二4和p型掺杂区三11;先用al离子注入形成p型掺杂区一3,在离子注入制作p型掺杂区一3的同时打开划片道窗口制作p型掺杂区三11,形成p型掺杂区三11;再重新光刻用al离子注入形成p型掺杂区二4;在离子注入制作p型掺杂区一3的同时打开划片道窗口制作p型掺杂区三11,也可以在离子注入制作p型掺杂区二4的同时打开划片道窗口制作p型掺杂区三11注入完成后通过1600

‑

1900 ℃的高温退火进行离子激活。

34.步骤2)中分开制作p型掺杂区一3、p型掺杂区二4和p型掺杂区三11;先用al离子注入形成p型掺杂区一3;再重新光刻用al离子注入形成p型掺杂区二4,在离子注入制作p型掺杂区二4的同

时打开划片道窗口(划片道窗口是图3中标注11的区域,利用光刻技术打开窗口,通过高能离子注入机进行al离子注入)制作p型掺杂区三11,形成p型掺杂区三11;注入完成后通过1600

‑

1900 ℃的高温退火进行离子激活。

35.对于本案所公开的内容,还有以下几点需要说明:(1)、本案所公开的实施例附图只涉及到与本案所公开实施例所涉及到的结构,其他结构可参考通常设计;(2)、在不冲突的情况下,本案所公开的实施例及实施例中的特征可以相互组合以得到新的实施例;以上,仅为本案所公开的具体实施方式,但本公开的保护范围并不局限于此,本案所公开的保护范围应以权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。