cis传感器的sab工艺的改善方法

技术领域

1.本发明涉及半导体技术领域,尤其是涉及一种cis传感器的sab工艺的改善方法。

背景技术:

2.在集成电路ic 制造中,silicide(硅化物)的形成有助于降低电阻,改善rc delay的问题。cis(cmos image sensor,cmos图像传感器)包括逻辑(logic)区域和像素(pixel)区域,cis(cmos image sensor,cmos图像传感器)的像素区域因为考虑到透光性的效率,不需要形成silicide。而逻辑区域因为有运算速率要求,需要形成silicide,以改善rc delay的问题。而cis器件的逻辑区域和像素像素区域是在一芯片上同时形成,所以对于芯片而言,部分区域即逻辑区域需要形成silicide, 部分区域即像素区域需要通过介电层包围起来起来,不形成silicide。如图1所示,图1是cis中逻辑区和像素区划分的俯视图,从图中可以看出,逻辑区110a和像素区110b相邻并且在同一芯片上。请参照图2,形成cis的现有技术为,提供器件晶圆,器件晶圆包括衬底110,位于衬底110上的至少两个栅极结构,栅极结构之间露出衬底110。栅极结构包括栅极120以及位于栅极120的两侧的侧墙130,每个逻辑区110a和每个像素区110b均有栅极结构。在整个器件晶圆上形成氧化物层140,氧化物层140覆盖逻辑区110a和像素区110b的栅极结构,再在氧化物层140上形成光刻胶150,刻蚀去除逻辑区110a的光刻胶150,剩余的光刻胶150覆盖像素区110b,并以像素区110b的光刻胶150为掩膜,刻蚀去除逻辑区110a的氧化物层140。最后去除像素区110b的光刻胶150,像素区110b剩余的氧化物层140即可作为介质层160,以在逻辑区110a形成硅化物时保护像素区110b的栅极结构。

3.请继续参照图2,而现有技术的工艺流程是通过干法刻蚀(plasma dry etch)的方法刻蚀去除逻辑区110a的氧化物层140。但是随着工艺节点的推进,干法刻蚀容易导致额外的不需要的等离子体隧穿到器件晶圆内(pid),引起器件参数漂移和失效。部分现有工艺为了减缓遂穿效应,用干法刻蚀搭配湿法刻蚀这种两步刻蚀的方法代替传统的单一干法刻蚀。可是随着工艺节点的推进,sab器件的尺寸变小,湿法刻蚀容易出现光刻胶剥离的问题,即,湿法刻蚀容易引起像素区110b的氧化物层140上的光刻胶150的剥离,从而使得像素区的氧化物层140存在很高的风险。像素区110b的氧化物层140一旦被破坏,形成的介质层160在后续的逻辑区110a的硅化物的形成时,保护能力变弱,从而影响光电转换的效率。

技术实现要素:

4.本发明的目的在于提供一种cis传感器的sab工艺的改善方法,可以在像素区形成质量较高的介质层,不会引起器件参数漂移和失效也不会出现光刻胶剥离的问题,从而提高cis传感器的质量。

5.为了达到上述目的,本发明提供了一种cis传感器的sab工艺的改善方法,包括:提供器件晶圆,所述器件晶圆包括相邻的逻辑区和像素区;在所述器件晶圆的表面形成光刻胶层;

进行光刻曝光和显影处理,去除所述像素区的光刻胶层,所述逻辑区的光刻胶层作为辅助层;在所述辅助层和所述像素区的器件晶圆上形成氧化物层;使用丙酮去除所述辅助层,使得所述辅助层上的氧化物层自然脱落,以暴露出所述逻辑区的器件晶圆的表面;在所述逻辑区的器件晶圆的表面形成用于对准的硅化物,所述像素区的氧化物层作为保护像素区的介质层。

6.可选的,在所述的cis传感器的sab工艺的改善方法中,所述逻辑区和所述像素区的器件晶圆均包括:衬底、位于所述逻辑区的衬底表面的第一栅极结构以及位于所述像素区的衬底表面的第二栅极结构。

7.可选的,在所述的cis传感器的sab工艺的改善方法中,所述第一栅极结构和所述第二栅极结构均包括栅极和位于所述栅极的两侧的侧墙。

8.可选的,在所述的cis传感器的sab工艺的改善方法中,所述辅助层的厚度为800埃~1000埃。

9.可选的,在所述的cis传感器的sab工艺的改善方法中,所述氧化物层的厚度为200埃~300埃。

10.可选的,在所述的cis传感器的sab工艺的改善方法中,形成所述氧化物层的方法为cvd。

11.可选的,在所述的cis传感器的sab工艺的改善方法中,使用丙酮去除所述辅助层的方法包括:所述丙酮与光刻胶进行反应,将光刻胶溶解。

12.可选的,在所述的cis传感器的sab工艺的改善方法中,所述氧化物层的材料包括二氧化硅。

13.在本发明提供的一种cis传感器的sab工艺的改善方法中,包括:提供器件晶圆,器件晶圆包括相邻的逻辑区和像素区;在器件晶圆的表面形成光刻胶层;进行光刻曝光和显影处理,去除像素区的光刻胶层,逻辑区的光刻胶层作为辅助层;在辅助层和像素区的器件晶圆上形成氧化物层;使用丙酮去除辅助层,使得辅助层上的氧化物层自然脱落,以暴露出逻辑区的器件晶圆的表面;在逻辑区的器件晶圆的表面形成用于对准的硅化物,像素区的氧化物层作为保护像素区的介质层。形成的介质层不但可以在逻辑区形成硅化物时保护像素区不形成硅化物,并且,相对于现有技术,本发明形成介质层没有经过光刻,也没有经过湿刻,因此,不会出现器件参数漂移和失效的问题,也不会出现光刻胶剥离的问题。进一步的,在形成介质层之前,使用丙酮去除光刻胶会使得光刻胶去除得非常干净,所以形成了质量较高的介质层,更好地保护了逻辑区,提高了cis传感器的质量。

附图说明

14.图1是现有技术的cis传感器的逻辑区和像素区划分的俯视图;图2是现有技术的cis传感器的sab工艺的改善方法的示意图;图3是本发明实施例的cis传感器的sab工艺的改善方法的流程图;图4是本发明实施例的cis传感器的逻辑区和像素区划分的俯视图图5是本发明实施例的器件晶圆的示意图;

图6是本发明实施例的形成辅助层后的cis传感器的示意图;图7是本发明实施例的形成氧化物层后的cis传感器的示意图;图8是本发明实施例的形成介质层后的cis传感器的示意图;图中:110

‑

衬底、110a

‑

逻辑区、110b

‑

像素区、120

‑

栅极、130

‑

侧墙、140

‑

氧化物层、150

‑

光刻胶、160

‑

介质层、210

‑

衬底、210a

‑

逻辑区、210b

‑

像素区、220

‑

栅极、230

‑

侧墙、240

‑

辅助层、250

‑

氧化物层、260

‑

介质层。

具体实施方式

15.下面将结合示意图对本发明的具体实施方式进行更详细的描述。根据下列描述,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

16.在下文中,术语“第一”“第二”等用于在类似要素之间进行区分,且未必是用于描述特定次序或时间顺序。要理解,在适当情况下,如此使用的这些术语可替换。类似的,如果本文所述的方法包括一系列步骤,且本文所呈现的这些步骤的顺序并非必须是可执行这些步骤的唯一顺序,且一些所述的步骤可被省略和/或一些本文未描述的其他步骤可被添加到该方法。

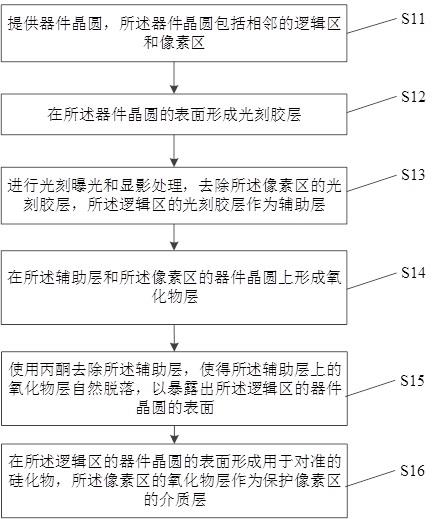

17.请参照图3,本发明提供了一种cis传感器的sab工艺的改善方法,包括:s11:提供器件晶圆,所述器件晶圆包括相邻的逻辑区和像素区;s12:在所述器件晶圆的表面形成光刻胶层;s13:进行光刻曝光和显影处理,去除所述像素区的光刻胶层,所述逻辑区的光刻胶层作为辅助层;s14:在所述辅助层和所述像素区的器件晶圆上形成氧化物层;s15:使用丙酮去除所述辅助层,使得所述辅助层上的氧化物层自然脱落,以暴露出所述逻辑区的器件晶圆的表面;s16:在所述逻辑区的器件晶圆的表面形成用于对准的硅化物,所述像素区的氧化物层作为保护像素区的介质层。

18.具体的,请参照图4和图5,本发明实施例的几个步骤均是在半成品的器件晶圆上形成的,主要是为了在形成用于自对准的硅化物时,保护不需要形成硅化物的地方。因此,需要首先提供器件晶圆,器件晶圆又分为逻辑区210a和像素区210b,具体的如图4,逻辑区210a和像素区210b相邻,其中,逻辑区210a用于计算,像素区210b用于进行光电转换,均运用在cis传感器中,逻辑区域上可以有mosfet。而逻辑区210a和所述像素区210b的器件晶圆均包括:衬底210、位于所述逻辑区210a的衬底210上的第一栅极结构以及位于所述像素区210b的衬底210上的第二栅极结构,同时,在衬底210和第一栅极结构以及衬底210和第二栅极结构之间还有栅极氧化物层250,所述第一栅极结构和所述第二栅极结构均包括栅极220和位于所述栅极220的两侧的侧墙230。即,逻辑区210a和像素区210b均有栅极结构,栅极结构之间又露出衬底210。而形成器件晶圆的步骤为,提供衬底210,衬底210可以是一晶圆,在衬底210上形成栅极氧化层,栅极氧化层可以使用化学气相沉积氧化物的方法形成。在栅极0氧化层上形成多晶硅层,刻蚀多晶硅层形成栅极220,在栅极220上形成氮化物层,刻蚀氮化物层形成位于栅极220两侧的侧墙230,每个栅极220的两侧均有一个侧墙230,在本发明

的其他实施例中,可能还包括通过离子注入形成源区和漏区。形成器件晶圆的方法为现有技术,在此不做赘述。

19.接着,请参照图6,在器件晶圆的表面形成一层光刻胶层,可以采用旋涂光刻胶的方式,光刻胶在器件晶圆的表面是均匀旋涂的,光刻胶层的厚度可以是800埃~1000埃。光刻胶覆盖栅极结构的表面以及栅极220结构之间的衬底210,更为具体的,光刻胶覆盖栅极220和侧墙230以及侧墙230和侧墙230之间的衬底210。接着,进行曝光和显影处理,去除所述像素区的光刻胶层,露出像素区210b的器件晶圆,也就是露出栅极结构的表面以及部分衬底210的表面,剩下逻辑区210a的光刻胶层作为辅助层240,辅助层240的厚度可以是800埃~1000埃。

20.接着,请参照图7,在辅助层240和像素区的器件晶圆的表面均形成一层氧化物层250,氧化物层250的厚度为300埃,氧化物层250的材料为二氧化硅。形成氧化物层250的方法为化学气相沉积的方法(cvd)。氧化物层250在像素区覆盖栅极结构以及部分衬底210,氧化物层250在逻辑区覆盖辅助层240。

21.接着,请参照图8,使用丙酮和光刻胶进行反应,溶解光刻胶,从而去除掉辅助层240,此时,辅助层240上的氧化物层250自然脱落,露出逻辑区的器件晶圆的表面也就是露出逻辑区的栅极结构的表面和部分衬底210的表面。像素区剩余的氧化物层250仍然覆盖栅极220结构和像素区的衬底210,剩余的氧化物层250作为介质层260。接着,在逻辑区210a的器件晶圆上形成用于后续形成的其他部件的对准用的硅化物。由于像素区210b不需要形成硅化物,并且需要在逻辑区形成硅化物的同时保护像素区210b。因此,本发明实施例的介质层260起到了在逻辑区形成硅化物的同时保护像素区的作用。同时,在形成介质层260时,不用通过干法刻蚀光刻胶也不用通过湿法刻蚀光刻胶的方法,可以减少干法刻蚀光刻胶时离子对其他部分的溅射,还可以减少湿法刻蚀时造成的过刻蚀。

22.综上,在本发明实施例提供的一种cis传感器的sab工艺的改善方法中,形成的介质层不但可以在逻辑区形成硅化物时保护像素区不形成硅化物,并且,相对于现有技术,本发明形成介质层没有经过光刻,也没有经过湿刻,因此,不会出现器件参数漂移和失效的问题,也不会出现光刻胶剥离的问题。进一步的,在形成介质层之前,使用丙酮去除光刻胶会使得光刻胶去除得非常干净,所以形成了质量较高的介质层,更好地保护了逻辑区,提高了cis传感器的质量。

23.上述仅为本发明的优选实施例而已,并不对本发明起到任何限制作用。任何所属技术领域的技术人员,在不脱离本发明的技术方案的范围内,对本发明揭露的技术方案和技术内容做任何形式的等同替换或修改等变动,均属未脱离本发明的技术方案的内容,仍属于本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。