复合钝化膜结构的光阻gpp芯片、制备方法及电子器件

技术领域

1.本发明属于光阻gpp芯片技术领域,尤其涉及一种复合钝化膜结构的光阻gpp芯片、制备方法及电子器件。

背景技术:

2.本部分的陈述仅仅是提供了与本发明相关的背景技术信息,不必然构成在先技术。

3.gpp是glassivation(玻璃化)passivation(钝化)parts(元件)or parts of an apparats(器件)词组的缩写,是玻璃钝化类器件的统称,它泛指引入或包含有结质膜保护工艺手段的所有有源器件。但是,由于玻璃钝化工艺措施对结界面裸露于体外的多种平面类二极管应用效果更为显著,并且已成为成功的典型应用,从而使gpp(glassivation passivation parts)逐渐成为了“玻璃钝化二极管”的代名词了。

4.光阻gpp芯片的生产是二极管业内成熟的工艺。光阻法使用最先进的光敏玻璃粉的光刻技术(photo glass技术),通过光刻技术,实现对钝化层覆盖区域的精确控制。传统的光阻gpp芯片具有三层钝化膜,由内及外分别为sipos(semi

‑

insulating polycrystalline

‑

silicon,半绝缘掺氧多晶硅)膜、玻璃和lto(low temperature oxide,低温氧化)膜(其主要成分是sio2)。其中,第一层钝化膜是sipos膜,是一种半绝缘掺氧多晶硅膜,厚度约0.4μm~0.6μm;sipos膜对表面(正/负)离子均起到补偿或消除的作用,具有对可动离子的捕捉能力。第二层钝化膜为玻璃,厚度约30μm~50μm;此玻璃层具有负电荷效应,对正离子起到一定的中和作用,介电强度高,抗辐射强,较高的机械强度和硬度,对提高反向击穿电压起到关键作用,但是对可动离子阻挡能力较弱。第三层钝化膜是lto膜,即一种化学气相沉积的sio2层,厚度约0.2μm~0.6μm;氧化层在阻挡可动离子方面的能力较差,不过氧化层对下面的钝化层起到覆盖保护作用,由于与焊锡不浸润,所以可以对焊锡起到阻挡作用,防止焊锡溢流,防止焊锡对钝化层的挤压与沾污。

5.传统光阻gpp芯片相对于刀刮gpp、电泳gpp芯片,具有高温漏电低、常温漏电一致性高、高温寿命长、明显降低玻璃裂纹发生几率的优势;所以光阻gpp是目前商品级产品中质量最稳定,可靠性最高的,不过光阻gpp芯片最大的劣势是成本会相应较高。

6.当前高端电子产品的应用市场,如汽车电子,客户对光阻gpp类二极管的要求越来越高,发明人发现,传统光阻gpp芯片封装成塑封二极管,比如sma封装形式的gpp二极管,由于sma封装过程的沾污较严重(可动离子沾污),产品在高温反偏实验中已经无法完全匹配这部分高端客户的需求。以sma封装的m7产品为例,汽车电子客户要求产品通过高温反偏150℃/80%反压/1000小时的考核,传统光阻gpp芯片封装的塑封二极管产品,无法保证每个生产批次均满足此可靠性要求。

技术实现要素:

7.为了解决上述背景技术中存在的技术问题,本发明提供一种复合钝化膜结构的光

阻gpp芯片、制备方法及电子器件,其在传统光阻gpp芯片钝化层设计的基础上,在玻璃表面增加氧化铝膜,在半绝缘掺氧多晶硅膜表面增加氮化硅膜,有这两层钝化层的保护,可完全避免可动离子移动到硅表面,加上半绝缘掺氧多晶硅膜对可动离子电场的中和作用,可确保产品高温反偏通过150℃/80%反压/1000小时的考核。

8.为了实现上述目的,本发明采用如下技术方案:

9.本发明的第一个方面提供了一种复合钝化膜结构的光阻gpp芯片,包括由内及外依次设置的半绝缘掺氧多晶硅膜、玻璃和低温氧化膜,所述低温氧化膜上设有氧化铝膜,所述半绝缘掺氧多晶硅膜上设有氮化硅膜。

10.进一步地,所述氧化铝膜的厚度为0.05μm

‑

0.15μm。

11.上述技术方案的优点在于,厚度为0.05μm

‑

0.15μm范围的氧化铝膜,对金属碱性阻挡与抗迁移能力很强;而且具有很高的机械强度与硬度,防止表面划伤或碰伤,提高生产加工的稳定性;还具有一定的抗辐射能力,能够增加产品的可靠性能力。

12.进一步地,所述氮化硅膜的厚度为0.2μm

‑

0.4μm。

13.上述技术方案的优点在于,厚度为0.2μm

‑

0.4μm范围的氮化硅膜对碱金属离子(如na

)阻挡与捕捉能力极强,可以显著提高对封装过程中可动离子的屏蔽作用。

14.本发明的第二个方面提供了一种复合钝化膜结构的光阻gpp芯片的制备方法,其包括:

15.在生长氧化层的扩散片上涂覆光刻胶;

16.在露出待蚀刻的区域上进行一次光刻沟槽,形成具有沟槽的硅片;

17.在具有沟槽的硅片上依次沉积半绝缘掺氧多晶硅膜和氮化硅膜;

18.在氮化硅膜上进行二次光刻涂覆玻璃光阻剂,烧结形成玻璃保护层;

19.在玻璃保护层上依次沉积低温氧化膜和氧化铝膜并形成晶片,对晶片的正面进行三次光刻露出焊接区域;

20.分别在晶片正面的焊接区域和晶片背面上镀金属;

21.将镀金属后的晶片背面进行划片处理,得到光阻gpp芯片。

22.进一步地,所述扩散片依次通过硼磷扩散、喷砂和清洗工艺获得。

23.进一步地,通过光刻工艺在生长氧化层的扩散片上涂覆负性光刻胶。

24.进一步地,使用混酸对待蚀刻的区域进行开沟腐蚀,形成具有沟槽的硅片。

25.进一步地,使用lpcvd沉积半绝缘掺氧多晶硅膜,使用磁控溅射沉积一层氧化铝膜。

26.进一步地,在晶片正面的焊接区域和晶片背面上镀的金属为镍与金。

27.本发明的第三个方面提供了一种电子器件,其包括如上述所述的复合钝化膜结构的光阻gpp芯片。

28.与现有技术相比,本发明的有益效果是:

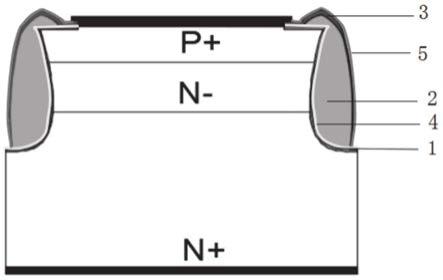

29.本发明在传统光阻gpp芯片包括由内及外依次设置的半绝缘掺氧多晶硅膜、玻璃和低温氧化膜这三层钝化层设计的基础上,在低温氧化膜表面增加氧化铝膜,在半绝缘掺氧多晶硅膜表面增加氮化硅膜,由于氧化铝膜和氮化硅膜这两层钝化层的保护,可完全避免可动离子移动到硅表面,加上半绝缘掺氧多晶硅膜对可动离子电场的中和作用,确保了产品高温反偏通过150℃/80%反压/1000小时的考核。

30.本发明附加方面的优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本发明的实践了解到。

附图说明

31.构成本发明的一部分的说明书附图用来提供对本发明的进一步理解,本发明的示意性实施例及其说明用于解释本发明,并不构成对本发明的不当限定。

32.图1是本发明实施例的一次光刻完成沟槽腐蚀后的结构示意图。

33.图2是本发明实施例的二次光刻完成光阻剂显影后的结构示意图。

34.图3是本发明实施例的三次光刻完成钝化层沉积并腐蚀出p面焊接区域的结构示意图。

35.图4是传统光阻法gpp芯片结构示意图。

36.图5是本发明实施例的gpp芯片结构示意图。

37.其中,1

‑

半绝缘掺氧多晶硅膜;2

‑

玻璃;3

‑

低温氧化膜;4

‑

氮化硅膜;5

‑

氧化铝膜。

具体实施方式

38.下面结合附图与实施例对本发明作进一步说明。

39.应该指出,以下详细说明都是例示性的,旨在对本发明提供进一步的说明。除非另有指明,本文使用的所有技术和科学术语具有与本发明所属技术领域的普通技术人员通常理解的相同含义。

40.需要注意的是,这里所使用的术语仅是为了描述具体实施方式,而非意图限制根据本发明的示例性实施方式。如在这里所使用的,除非上下文另外明确指出,否则单数形式也意图包括复数形式,此外,还应当理解的是,当在本说明书中使用术语“包含”和/或“包括”时,其指明存在特征、步骤、操作、器件、组件和/或它们的组合。

41.实施例一

42.背景技术提及到的传统光阻gpp芯片封装的塑封二极管产品,无法保证每个生产批次均满足此可靠性要求原因如下:

43.高温反偏实验可检验半导体器件是否存在严重的可动离子沾污。实验中,二极管芯片被施加反向偏置电压,在高温150℃下,施加80%反向偏置电压,实验可揭示在芯片边缘和钝化层中场耗尽结构的弱点和退化效应。

44.光阻法gpp芯片在装配和焊接过程中,会受到来自多方面的沾污,如助焊剂、锡膏、环境中的松香挥发物、焊接炉内的松香挥发物等,芯片表面被沾污大量的可动碱性金属离子(na

、k

等);这些可动离子在后续的高温工艺中逐渐移动到芯片的玻璃中,当沾污量较大时,大量可动离子会移动到sipos(半绝缘含氧多晶硅)膜表面。虽然理论上sipos膜对可动离子产生一定的阻挡作用,但是实际上sipos膜总会存在一定的结构缺陷,导致仍然会有一定量的可动离子会移动穿过sipos膜,最终移动到芯片沟槽的硅表面。

45.产品在做高温反偏实验时,由于芯片沟槽硅表面存在可动离子,少量表面的可动离子就会对pn结耗尽层宽度产生影响,并影响电场分布,从而导致沟槽硅表面局部电场集中,导致漏电集中,所以在高温反偏过程中,漏电集中的区域容易发生热电正反馈机制,表现为高温漏电持续升高,最终发生热击穿。当沟槽硅表面有大量可动离子时,甚至会导致n

型硅增强,导致p型硅反型为n型硅,从而导致沟槽硅表面出现漏电通道,产品常温下的漏电也会增大。

46.为了解决的背景技术提及到的传统光阻gpp芯片封装的塑封二极管产品,无法保证每个生产批次均满足此可靠性要求的技术问题,本实施例提供了一种复合钝化膜结构的光阻gpp芯片,包括由内及外依次设置的半绝缘掺氧多晶硅膜1、玻璃2和低温氧化膜3,所述低温氧化膜3上设有氧化铝膜5,所述半绝缘掺氧多晶硅膜1上设有氮化硅膜4,如图5所示。

47.其中,传统的光阻gpp芯片结构仅仅只包括由内及外依次设置的半绝缘掺氧多晶硅膜1、玻璃2和低温氧化膜3这三层钝化层。

48.在本实施例中,在半绝缘掺氧多晶硅膜1表面沉积(其中,沉积方法比如:通过lpcvd方法)一层(无定型)氮化硅膜4。

49.其中,所述氮化硅膜的厚度为0.2μm

‑

0.4μm。此厚度为0.2μm

‑

0.4μm范围的氮化硅膜对碱金属离子(如na

)阻挡与捕捉能力极强,可以显著提高对封装过程中可动离子的屏蔽作用。

50.当芯片在焊接过程中,助焊剂残留中的可动离子会附着到芯片钝化层上,产品经过塑封、固化、回流焊等过程时,由于低温氧化膜3与玻璃对可动离子的屏蔽作用很弱,可动离子很容易会移动到半绝缘掺氧多晶硅膜1表面。但是可动离子几乎无法在氮化硅膜4中移动,从而可动离子被屏蔽在氮化硅膜4表面,可动离子几乎无法移动到硅表面。

51.并且,由于半绝缘掺氧多晶硅膜1对可动离子的电场起到中和作用,导致氮化硅表面的可动离子对芯片沟槽表面pn结不产生任何的影响,从而显著降低高温反偏时的漏电。

52.在低温氧化膜3表面通过磁控溅射法沉积一层氧化铝膜5。由于磁控溅射温度低,对芯片的辐射损伤小,膜致密性高,膜与衬底低温氧化膜3的粘附力高等特点,故适用于表面钝化层的制作。

53.其中,所述氧化铝膜5的厚度为0.05μm

‑

0.15μm。此厚度为0.05μm

‑

0.15μm范围的氧化铝膜,对金属碱性阻挡与抗迁移能力很强;而且具有很高的机械强度与硬度,防止表面划伤或碰伤,提高生产加工的稳定性;还具有一定的抗辐射能力,能够增加产品的可靠性能力。

54.由于氧化铝膜5同样具有对可动离子的阻挡作用,所以芯片在焊接封装过程中沾污后,可动离子同样难以扩散移动到玻璃中,从而作为第一层屏障,即起到对沟槽硅表面的保护作用。

55.实施例二

56.本实施例提供了一种复合钝化膜结构的光阻gpp芯片的制备方法,其包括如下步骤:

57.步骤1:在生长氧化层的扩散片上涂覆光刻胶。

58.其中,所述扩散片依次通过硼磷扩散、喷砂和清洗工艺获得。

59.在具体实施中,先通过设定温度氧化工艺生长一层氧化层,并对扩散片进行退火;再通过光刻工艺在生长氧化层的扩散片上涂覆负性光刻胶,并进行曝光显影等,露出待蚀刻的区域。

60.步骤2:在露出待蚀刻的区域上进行一次光刻沟槽,形成具有沟槽的硅片,如图1所示。

61.在具体实施中,使用混酸对待蚀刻的区域进行开沟腐蚀,形成具有沟槽的硅片。

62.在其他实施例中,也可采用其他方法对待蚀刻的区域进行开沟腐蚀,形成具有沟槽的硅片。

63.步骤3:在具有沟槽的硅片上依次沉积半绝缘掺氧多晶硅膜和氮化硅膜;

64.具体地,可使用lpcvd沉积半绝缘掺氧多晶硅膜和氮化硅膜。

65.步骤4:在氮化硅膜上进行二次光刻涂覆玻璃光阻剂,烧结形成玻璃保护层。

66.具体地,通过光刻工艺涂覆玻璃光阻剂,并进行曝光显影等,如图2所示。

67.对晶片进行高温烧结,形成玻璃保护层。

68.步骤5:在玻璃保护层上依次沉积低温氧化膜和氧化铝膜并形成晶片,对晶片的正面进行三次光刻露出焊接区域;

69.具体地,使用lpcvd沉积半绝缘掺氧多晶硅膜,使用磁控溅射沉积一层氧化铝膜。

70.需要说明的是,在其他实施例中,沉积半绝缘掺氧多晶硅膜和氧化铝膜的方法也可采用现有的其他方法来实现,此处不再详述。

71.步骤6:分别在晶片正面的焊接区域和晶片背面上镀金属。

72.在优选的实施方式中,在晶片正面的焊接区域和晶片背面上镀的金属为镍与金。

73.可以理解的是,在其他实施例中,镀的金属也可只有镍;

74.镀的金属也可为钛镍银或镍银等。

75.步骤7:将镀金属后的晶片背面进行划片处理,得到光阻gpp芯片。

76.实施例三

77.本实施例提供了一种电子器件,其包括如上述实施例一所述的复合钝化膜结构的光阻gpp芯片。

78.需要说明的是,电子器件可为电源、适配器、照明、显示器或汽车整流设备等,所述的复合钝化膜结构的光阻gpp芯片通过封装成二极管或桥式整流器,在上述电子器件中主要起到整流与保护作用。

79.以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。