1.本发明涉及显示技术领域,特别涉及一种显示面板、其制作方法及显示装置。

背景技术:

2.作为新兴显示技术,微发光二极管(micro led)显示相较于lcd(液晶显示)、oled(有机发光二极管)显示有较多优势,如较低的功耗,较高的色域,较快的相应速率等,对封装水氧隔绝要求不高,被视为较有发展前景的一种显示技术。

3.但是micro led显示还有诸多技术难点需要克服,如在大尺寸显示上远离vdd(高电位走线)/vss(低电位走线)输入端的显示区域由于走线电阻导致vdd发生压降(ir drop)、vss压升,造成微发光二极管两端压差降低,亮度下降,整面亮度不均。因此,改善走线电阻引起的电流下降对micro led大尺寸化至关重要。同时vdd/vss作为输电线(power line),电流密度较大,电流热效应过大则可能造成二极管/晶体管器件特性漂移、走线过载、ra(reliability analysis,可靠性分析)特性恶化。

技术实现要素:

4.本发明目的在于,解决现有显示面板显示区域亮度不均的问题。

5.为实现上述目的,本发明提供一种显示面板,包括:显示基板和覆盖于所述显示基板上方的盖板,所述显示基板包括:衬底基板;形成于所述衬底基板上的薄膜晶体管层;间隔设置于所述薄膜晶体管层上的高电位连接垫、低电位连接垫及发光元件焊垫;以及设置于所述发光元件焊垫上的发光元件;所述盖板包括:高电位走线和低电位走线间隔设置于所述盖板朝向所述显示基板的一面;第一连接垫,设置于所述高电位走线下表面;以及第二连接垫,设置于所述低电位走线下表面,其中,所述第一连接垫与所述第二连接垫被配置为在所述盖板对合于所述显示基板时,所述第一连接垫对位于所述高电位连接垫且与所述高电位连接垫电连接,所述第二连接垫对位于所述低电位连接垫且与所述低电位连接垫电连接。

6.可选的,所述薄膜晶体管层中包含多个像素驱动电路,所述显示基板定义有多个阵列分布的像素区,每个像素区包括至少一个所述发光元件、一个所述像素驱动电路、一个所述高电位连接垫、以及一个所述低电位连接垫,其中,所述高电位连接垫被配置为提供所述像素驱动电路高电平,所述低电位连接垫被配置为提供所述像素驱动电路低电平。

7.可选的,所述高电位走线被配置为提供所述高电平,所述低电位走线被配置为提供所述低电平。

8.可选的,每个所述像素驱动电路包括至少一个驱动薄膜晶体管,所述驱动薄膜晶体管被配置为驱动所述发光元件发光。

9.可选的,所述高电位走线和所述低电位走线的材质包括铜或铝,且所述高电位走线和所述低电位走线对位于所述多个像素区之间的间隔位置。

10.可选的,所述发光元件包括微发光二极管。

11.可选的,所述高电位连接垫与所述第一连接垫之间设置有导电膏,所述低电位连接垫与所述第二连接垫之间设置有导电膏。

12.可选的,所述显示面板还包括填充于所述显示基板和所述盖板之间的光学胶。

13.为实现上述目的,本发明还提供一种显示装置,包括如前所述的显示面板以及控制单元,所述控制单元用以提供所述高电平与所述低电平。

14.为实现上述目的,本发明还提供一种显示面板的制备方法,包括:

15.提供显示底基板;

16.在所述显示基板一面形成薄膜晶体管层;

17.在所述薄膜晶体管层上间隔形成高电位连接垫、发光元件焊垫和低电位连接垫;

18.转移微发光二极管至所述发光元件焊垫上:

19.提供盖板;

20.在所述盖板一面上形成间隔排布的高电位走线和低电位走线;

21.在所述高电位走线上形成第一连接垫,在所述低电位走线形成第二连接垫;

22.将所述盖板对合于所述显示基板,其中所述第一连接垫与所述第二连接垫面向所述显示基板且所述第一连接垫与所述高电位连接垫对接,所述第二连接垫与所述低电位连接垫对接。

23.本发明的有益效果在于,本发明提供的显示面板,将vdd走线和vss走线分别分成两个部分,即,将vdd走线分成高电位连接垫和高电位走线两部分,将vss走线分成低电位连接垫和低电位走线两部分,将高电位走线和低电位走线布置于盖板上,在显示基板上仅保留高电位连接垫和低电位连接垫,将高电位走线和高电位连接垫通过第一连接垫形成电连接,将低电位走线和低电位连接垫通过第二连接垫形成电连接,从而将走线部分从显示基板上分离,改善因为压降导致的显示区域亮度不均的问题,提高信赖性,提升显示品味,并可增加显示基板的设计、结构以及制程余地。

附图说明

24.下面结合附图,通过对本发明的具体实施方式详细描述,将使本发明的技术方案及其它有益效果显而易见。

25.图1a是本发明一实施例中的显示面板的结构示意图;

26.图1b是本发明一实施例中的显示面板的结构示意图;

27.图1c是本发明一实施例中的显示装置的结构示意图;

28.图2是本发明一实施例中的像素驱动电路的等效电路图;

29.图3是本发明另一实施例中像素驱动电路的等效电路图;

30.图4是本发明一实施例中的显示面板的制作流程图;

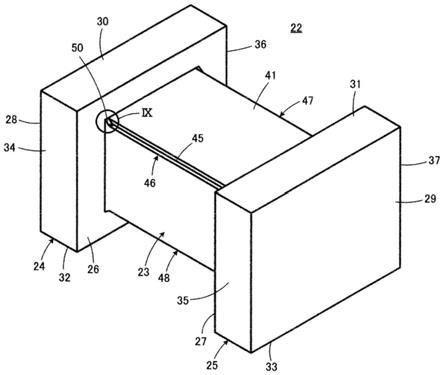

31.图5a~图5e是本发明一实施例中的显示面板的制作方法中盖板制作的结构示意图;

32.图中部件编号如下:

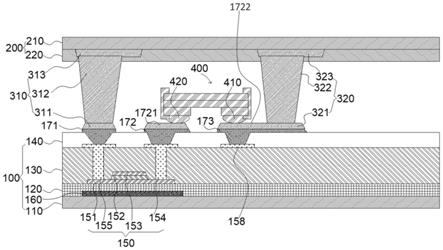

33.1、显示装置,10、显示面板,100、显示基板,110、衬底基板,120、缓冲层,130、层间介质层,140、第一保护层,150、驱动薄膜晶体管,151、有源层,52、栅极绝缘层,153、栅极,154、漏极,155、源极,158、接触电极,160、遮光层,171、第一导电层,172、第二导电层,1721/

1722、发光元件焊垫,173、第三导电层;

34.20、控制单元,200、盖板,210、底板,220、第二保护层,221、第一通孔,222、第二通孔,230、负性光阻层,240、金属膜层;

35.310、高电位输电线路,311、高电位连接垫,312、第一连接垫,313、高电位走线,320、低电位输电线路,321、低电位连接垫,322、第二连接垫,323、低电位走线;

36.400、发光元件,410、第一电极,420、第二电极;

37.tl、薄膜晶体管层,pd、像素驱动电路,pa、像素区,ia、间隔位置,fc、软性电路板。

具体实施方式

38.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

39.所述显示面板将vdd走线分成高电位连接垫和高电位走线两部分,将vss走线分成低电位连接垫和低电位走线两部分,将高电位走线和低电位走线布置于盖板上,在显示基板上仅保留高电位连接垫和低电位连接垫,将高电位走线和高电位连接垫通过第一连接垫形成电性连接,将低电位走线和低电位连接垫通过第二连接垫形成电性连接,从而将走线部分从显示基板上分离,改善因为压降导致的显示区域亮度不均的问题,提高信赖性,提升显示品味,并可增加显示基板的设计、结构以及制程余地。作为典型应用,所述显示面板可被应用于显示装置中,例如mini led显示器或micro led显示器。

40.本发明的一个实施例中,参照图1a,显示面板10包括显示基板100和盖板200。盖板200覆盖于显示基板100上方,显示基板100包括衬底基板110、形成于所述衬底基板110上的薄膜晶体管层tl、间隔设置于薄膜晶体管层tl上的高电位连接垫311、低电位连接垫321和发光元件焊垫1721、1722以及发光元件400设置于发光元件焊垫1721、1722上。盖板200朝向所述显示基板100的一面间隔设置有高电位走线313和低电位走线323,高电位走线313下表面(朝向显示基板100一面)设置有第一连接垫312,低电位走线323下表面设置有第二连接垫322。盖板200对合于显示基板100,第一连接垫312对位于高电位连接垫311并与高电位连接垫311电连接;第二连接垫322对位于低电位连接垫321并与低电位连接垫321电连接。其中,所述低电位连接垫321一部分与第二连接垫322连接,一部分与发光元件400连接,与发光元件400连接的低电位连接垫321部分为发光元件焊垫1722。

41.所述薄膜晶体管层tl中包含多个像素驱动电路pd,所述显示基板100定义有多个阵列分布的像素区pa,每个像素区pa包括至少一个所述发光元件400、一个所述像素驱动电路pd、一个所述高电位连接垫311、以及一个所述低电位连接垫321,其中,所述高电位连接垫311被配置为提供所述像素驱动电路高电平vdd,所述低电位连接垫321被配置为提供所述像素驱动电路低电平vss。

42.参照图1b,所述高电位走线313被配置为提供所述高电平vdd,所述低电位走线323被配置为提供所述低电平vss。具体的,高电位连接垫311、第一连接垫312和高电位走线313形成高电位输电线路310用以提供所述高电平vdd。低电位连接垫321、第二连接垫322和低电位走线323形成低电位输电线路320用以提供所述低电平vss。

43.每个所述像素驱动电路pd包括至少一个驱动薄膜晶体管150,所述驱动薄膜晶体管150被配置为驱动所述发光元件400发光。所述驱动薄膜晶体管150可以为顶栅结构也可以为底栅结构,本技术实施例对此不作任何限定,需要说明的是,本实施例是以驱动薄膜晶体管150为顶栅结构为例进行说明的。

44.所述高电位走线313和所述低电位走线323的材质包括铜或铝。参照图1a,所述高电位走线313和所述低电位走线323对位于所述多个像素区pa之间的间隔位置ia。具体的,所述高电位走线313和所述低电位走线323从所述间隔位置ia延伸突出至所述像素区pa中以便于设置第一连接垫312和第二连接垫322。

45.所述发光元件400包括微发光二极管(micro led)或迷你发光二极管(mini led)。

46.所述高电位连接垫311与所述第一连接垫312之间以及所述低电位连接垫321与所述第二连接垫322之间可以设置锡膏或锡球(图中未示出),使用焊接法进行电连接。或是所述高电位连接垫311与所述第一连接垫312之间设置有导电膏(图中未示出),所述低电位连接垫321与所述第二连接垫322之间设置有导电膏。导电膏的设计可保证电连接的稳定性,保证电流传输的稳定性。

47.显示基板100和所述盖板200之间填充有光学胶(图中未示出),除了提高所述发光元件400的光取出率,避免水气入侵到发光元件400或像素驱动电路pd,也可保持显示基板100和所述盖板200之间的距离,避免所述高电位连接垫311与所述第一连接垫312之间以及所述低电位连接垫321与所述第二连接垫322之间的导电连接脱落。

48.参照图1c,本发明还提供一种显示装置1,包括如前所述的显示面板10以及控制单元20,所述控制单元20用以提供所述高电平vdd与所述低电平vss。

49.具体的,所述控制单元20透过软性电路板fc连接至所述显示面板10的所述高电位走线313與所述低电位走线323,並向所述高电位走线313提供所述高电平vdd,向所述低电位走线323提供所述低电平vss。

50.参照图1b,在本实施例中,所述衬底基板100还包括设置于衬底基板110朝向盖板200一面的缓冲层120,设置于缓冲层120背离衬底基板110一面的层间介质层130,第一保护层140设置于层间介质层130背离缓冲层120一面,所述衬底基板110朝向盖板200一面还设置有遮光层160。所述盖板200还包括底板210,底板210朝向显示基板100一面设置有第二保护层220。

51.所述驱动薄膜晶体管150包括有源层151、栅极绝缘层152、栅极153、漏极154和源极155。所述驱动薄膜晶体管150可以为顶栅结构也可以为底栅结构,本技术实施例对此不作任何限定。接触电极158示意像素驱动电路pd的其他线路或换线层线路,本技术实施例对此不作任何限定。在本实施例中,所述像素驱动电路pd可参照图2或图3。图2或图3的像素驱动电路仅为一示例,本技术实施例对此不作任何限定。像素驱动电路中的高电平vdd透过高电位输电线路310提供,低电平vss透过低电位输电线路320提供。在本实施例中,高电位连接垫311和低电位连接垫321间隔排布于第一保护层140背离层间介质层130一面,高电位走线313和低电位走线323间隔设置于底板210朝向显示基板100一面。

52.作为一种改进,参照图1b,所述第一保护层140背离所述层间介质层130一面设置有间隔排布的第一导电层171、第二导电层172和第三导电层173,发光元件焊垫1721设置于第二导电层172背离所述第一保护层140一面,在本实施例中,高电位连接垫311通过第一导

电层171与驱动薄膜晶体管150的漏极154电性连接,低电位连接垫321通过第三导电层173与接触电极158电性连接,发光元件400的第二电极420通过发光元件焊垫1721、第二导电层172与驱动薄膜晶体管150的漏极154电连接,发光元件400的第一电极410透过发光元件焊垫1722、第三导电层173与接触电极158电连接。第一保护层140包覆所述漏极154、源极155和接触电极158。

53.其中,高电位连接垫311、低电位连接垫321以及发光元件焊垫1721位于同一层。所述第一导电层171、第二导电层172和第三导电层173均为金属材质。所述发光元件400的第一电极410为阴极,第二电极420为阳极。

54.第一连接垫312与第二连接垫322的高度相同,均高于发光元件400的高度。另一种方式中,第一连接垫312与第二连接垫322的高度可以不同,例如第一连接垫312的高度高于第二连接垫322的高度,或者,第一连接垫312的高度低于第二连接垫322的高度。但只需要满足高度较矮的一个的高度高于发光元件400的高度这个条件即可。从而使得当盖板200与显示基板100对接组装时,避免盖板200压到发光元件400。所述发光元件400位于第一连接垫312与第二连接垫322之间,即,发光元件400在底板210上的正投影位于高电位走线313与低电位走线323之间。

55.其中,参照图1b,在本实施例中,第一连接垫312与高电位走线313连接端的端面面积大于第一连接垫312与高电位连接垫311连接端的端面面积,形成第一连接垫312的倒梯形截面形状;第二连接垫322与低电位走线323连接端的端面面积大于第二连接垫322与低电位连接垫321连接端的端面面积,形成第二连接垫322的倒梯形截面形状。作为另一种可行方式,第一连接垫312与高电位走线313连接端的端面面积小于第一连接垫312与高电位连接垫311连接端的端面面积,第二连接垫322与低电位走线323连接端的端面面积小于第二连接垫322与低电位连接垫321连接端的端面面积。

56.本发明通过将高电位走线313在盖板200的底板210上走线,高电位连接垫311设置于显示基板100上,高电位走线313与高电位连接垫311通过第一连接垫312电连接导通,同理,将低电位走线323在盖板200的底板210上走线,低电位连接垫321设置于显示基板100上,低电位走线323与低电位连接垫321通过第二连接垫322电连接导通。由于将高电位输电线路310的走线部分和低电位输电线路320的走线部分转移至盖板200上,可以選用較粗較厚的走線,減少了现有因为在显示基板100上走线空間不足,導致走線過細,电阻過高以致压降過大的问题,保证发光元件400发光的均匀性,保证显示面板显示区域亮度的均匀性。而且,由于将高电位输电线路310的走线部分和低电位输电线路320的走线部分转移至盖板200上,可增加显示基板100上的其他结构以及制程余地(margin)。

57.参照图1a和图4,本发明还提供所述显示面板的制作方法,包括如下步骤:

58.s110、提供显示基板100;

59.s120、在所述显示基板100一面形成薄膜晶体管层tl;

60.s130、在所述薄膜晶体管层tl上间隔形成高电位连接垫311、发光元件焊垫1721/1722和低电位连接垫321;

61.s140、转移发光元件400至所述发光元件焊垫1721/1722上;

62.s150、提供盖板200;

63.s160、在所述盖板200一面上形成间隔排布的高电位走线313和低电位走线323;

64.s170、在所述高电位走线313上形成第一连接垫312,在所述低电位走线323形成第二连接垫322;

65.s180、将所述盖板200对合于所述显示基板100,其中所述第一连接垫312与所述第二连接垫322面向所述显示基板100且所述第一连接垫312与所述高电位连接垫311对接,所述第二连接垫322与所述低电位连接垫321对接。

66.其中,所述驱动薄膜晶体管150的漏极154通过过孔与有源层151连接,源极155通过过孔与有源层151连接。

67.其中,第一保护层140背离所述层间介质层130一面间隔形成有第一导电层171、第二导电层172和第三导电层173,第一导电层171通过过孔沉积至源极155并与源漏极155连接,第二导电层172通过过孔沉积至漏极154并与漏极154连接,第三导电层173通过过孔沉积至接触电极158并与接触电极158连接,第二导电层172背离第一保护层140一面形成有发光元件焊垫1721;第三导电层173背离第一保护层140一面形成有发光元件焊垫1722及低电位连接垫321。

68.在本实施例中,发光元件400的第一电极410与发光元件焊垫1722电性连接,第二电极420与驱动薄膜晶体管150的漏极154电性连接。

69.具体的,发光元件400的第二电极420通过发光元件焊垫1721和第二导电层172与驱动薄膜晶体管150的漏极154电性连接。

70.在本实施例中,盖板200的形成步骤如下:(参照图5a~5e)

71.提供底板210;

72.在底板210一面上进行金属成膜及图形化,形成间隔排布的高电位走线313和低电位走线323;

73.在形成高电位走线313和低电位走线323的底板210表面形成第二保护层220;

74.图形化第二保护层220以开设第一通孔221及第二通孔222,其中第一通孔221暴露至少部分高电位走线313,第二通孔222暴露至少部分低电位走线323;

75.在第二保护层220背离底板210一面涂布负性光阻并图形化,形成负性光阻层230;

76.在负性光阻层230背离第二保护层220一面蒸镀形成金属膜层240,部分金属膜层240通过第一通孔221沉积至高电位走线313形成第一连接垫312,部分金属膜层240通过第二通孔222沉积至低电位走线323形成第二连接垫322;

77.去除负性光阻层230及位于负性光阻层230上的金属膜层240。

78.其中,盖板200的底板210采用透明材质,可为玻璃或pet或其他材料。高电位走线313和低电位走线323的走线工艺也可采用印刷、打印、厚膜pvd等方式实现低电阻设计。

79.以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员,在不脱离本发明原理的前提下,还可以做出多个改进和润饰,这些改进和润饰也应视为本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。