1.本技术涉及显示技术领域,尤其涉及一种显示面板及其制备方法。

背景技术:

2.微发光二极体显示器(micro led display)为新一代的显示技术,micro led继承了led的特性,具有尺寸小、重量轻、亮度高、寿命长、功耗低、响应时间快及可控性强的优点,且micro led的色域能大于120%,ppi(像素密度)能达到1500。因此,较多面板厂家参与micro led技术开发之中。

3.但是,微发光二极体显示器还有诸多技术难点需要克服,如在大尺寸显示上远离vdd/vss输入端的区域,由于走线电阻导致vdd发生压降、vss压升,造成led芯片(即发光器件)两端压差降低,亮度下降,整面亮度不均。

4.因此,改善电阻引起的电流下降对micro led大尺寸化至关重要。

技术实现要素:

5.本发明的目的在于,提供一种显示面板及其制备方法,以解决走线电阻导致vdd发生压降、vss压升,发光器件的两端压差降低,导致显示面板亮度不均的技术问题。

6.为实现上述目的,本发明提供一种显示面板,包括:阵列基板,其表面图案化形成有第一vdd走线和第一vss走线;对置基板,与所述阵列基板相对设置,其表面图案化形成有第二vdd走线和第二vss走线;以及发光器件,设于所述阵列基板与所述对置基板之间,且与所述第二vdd走线及所述第二vss走线错位设置;其中,所述第一vdd走线通过第一导电层连接至所述第二vdd走线,所述第一vss走线通过第二导电层连接至所述第二vss走线。

7.进一步的,所述第一导电层和所述第二导电层均为金属连接块;或者,所述第一导电层和所述第二导电层均为各向异性导电层。

8.进一步的,所述对置基板包括:盖板,其中所述第二vdd走线和所述第二vss走线图案化设置于所述盖板的一侧表面;以及保护层,设于所述盖板上,其中所述保护层设置第一开口和第二开口,其中所述第一开口用以暴露出所述第二vdd走线,所述第二开口用以暴露出所述第二vss走线。

9.进一步的,所述阵列基板包括:玻璃基板;遮光层,设于所述玻璃基板上;缓冲层,设于所述玻璃基板上,且覆盖所述遮光层;薄膜晶体管层,设于所述缓冲层上,所述薄膜晶体管包括有源层、栅极层、以及源漏极层,其中所述有源层与所述栅极层、所述源漏极层之间设有层间绝缘层;走线层,与所述源漏极层同层设置;钝化层,设于所述薄膜晶体管层上,且覆盖部分所述源漏极层及部分所述走线层;导电连接层,穿过所述钝化层且连接至部分所述源漏极层及所述走线层;以及公共连接层,设于所述导电连接层上,其图案化形成第一电极、第二电极、所述第一vdd走线以及所述第一vss走线。

10.进一步的,所述发光器件的第一连接部连接至所述第一电极,所述发光器件的第二连接部连接至所述第二电极;所述第一导电层的一侧连接至所述第一vdd走线,另一侧通

过所述第一开口连接至所述第二vdd走线;所述第二导电层的一侧连接至所述第一vss走线,另一侧通过所述第二开口连接至所述第二vss走线。

11.为实现上述目的,本发明还提供一种显示面板的制备方法,包括如下制备步骤:形成阵列基板,所述阵列基板的表面图案化形成有第一vdd走线和第一vss走线;安装发光器件于所述阵列基板上;设置第一导电层于所述第一vdd走线上以及设置第二导电层于所述第一vss走线上;形成对置基板,所述对置基板的表面图案化形成有第二vdd走线和第二vss走线,所述发光器件与所述第二vdd走线及所述第二vss走线错位设置;将所述阵列基板与所述对置基板进行对位组合;其中,所述第一导电层和所述第二导电层设于所述阵列基板与所述对置基板之间;采用压合方法或者焊接方法,使得所述第一vdd走线通过所述第一导电层固定连接至所述第二vdd走线;所述第一vss走线通过所述第二导电层固定连接至第二vss走线。

12.进一步的,在所述形成对置基板的步骤中,包括:图案化形成所述第二vdd走线和所述第二vss走线于所述盖板上;以及形成保护层于盖板上,且覆盖部分所述第二vdd走线和所述第二vss走线,所述保护层设置第一开口和第二开口,其中所述第一开口用以暴露出所述第二vdd走线,所述第二开口用以暴露出所述第二vss走线。

13.进一步的,通过印刷方式、打印方式、物理气相沉积方式中的一种形成所述第二vdd走线和所述第二vss走线于所述盖板上。

14.进一步的,在所述形成阵列基板的步骤中,包括:形成遮光层于玻璃基板上;形成缓冲层于所述玻璃基板上,且覆盖所述遮光层;形成薄膜晶体管层于所述缓冲层上,所述薄膜晶体管形成有有源层、栅极层、源漏极层以及走线层,其中所述有源层与所述栅极层、所述源漏极层之间设有层间绝缘层,所述走线层与所述源漏极层同层设置;形成钝化层于所述薄膜晶体管层上,且覆盖部分所述源漏极层及部分所述走线层;对所述钝化层进行挖孔处理,形成第一过孔和第二过孔,所述第一过孔连通至所述源漏极层表面,所述第二过孔连通至所述走线层表面;形成导电连接层于所述钝化层上,其中所述导电连接层通过所述第一过孔连接至部分所述源漏极层,所述导电连接层通过所述第二过孔连接至所述走线层;以及形成公共连接层于所述导电连接层上,所述公共连接层包括第一电极、第二电极、所述第一vdd走线以及所述第一vss走线。

15.进一步的,在安装发光器件于所述阵列基板上的步骤中,所述发光器件的第一连接部连接至所述第一电极,所述发光器件的第二连接部连接至所述第二电极;在所述阵列基板与所述对置基板进行对位组合的步骤中,所述第一导电层的一侧连接至所述第一vdd走线,另一侧通过所述第一开口连接至所述第二vdd走线;所述第二导电层的一侧连接至所述第一vss走线,另一侧通过所述第二开口连接至所述第二vss走线。

16.本发明的技术效果在于,提供一种显示面板及其制备方法,所述显示面板包括相对设置的阵列基板和对置基板,以及安装于所述阵列基板上的发光器件。其中,所述阵列基板的表面图案化形成有第一vdd走线和第一vss走线,所述对置基板的表面图案化形成有第二vdd走线和第二vss走线。所述第一vdd走线通过第一导电层连接至所述第二vdd走线,所述第一vss走线通过第二导电层连接至所述第二vss走线,有利于大大降低显示面板的面内走线的电阻,从而使得显示面板各个位置的亮度均匀。

附图说明

17.下面结合附图,通过对本技术的具体实施方式详细描述,将使本技术的技术方案及其它有益效果显而易见。

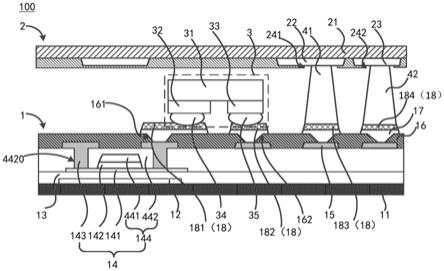

18.图1为本技术实施例1提供的显示面板的剖面图。

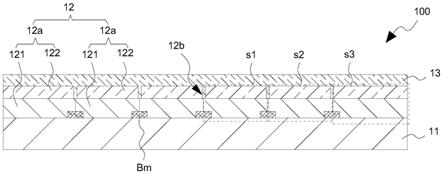

19.图2为本技术实施例1提供的连接点在显示面板的结构示意图。

20.图3为本技术实施例1提供的显示面板的制备方法的流程图。

21.图4为本技术实施例1提供的形成阵列基板的流程图。

22.图5为本技术实施例1提供的形成阵列基板的剖面意图。

23.图6为本技术实施例1提供的形成薄膜晶体管层的流程图。

24.图7为本技术实施例1提供的发光器件安装于阵列基板的结构示意图。

25.图8为本技术实施例1提供的形成对置基板的剖面意图。

26.图9为本技术实施例2提供的显示面板的剖面图。

27.附图部件标识如下:

28.1、阵列基板;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

2、对置基板;

29.3、发光器件;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

41、第一金属连接块;

30.42、第二金属连接块;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

43、第一各向异性导电层;

31.44、第二各向异性导电层;

ꢀꢀꢀꢀꢀ

11、玻璃基板;

32.12、遮光层;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

13、缓冲层;

33.14、薄膜晶体管层;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

15、走线层;

34.16、钝化层;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

17、导电连接层;

35.18、公共连接层;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

141、有源层;

36.142、栅极层;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

143、源漏极层;

37.144、层间绝缘层;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

441、栅极绝缘层;

38.442、介电层;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

4420、连接孔;

39.161、第一过孔;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

162、第二过孔;

40.181、第一电极;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

182、第二电极;

41.183、第一vdd走线;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

184、第一vss走线;

42.21、盖板;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

22、第二vdd走线;

43.23、第二vss走线;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

24、保护层;

44.241、第一开口;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

242、第二开口;

45.31、衬底层;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

32、n型半导体层;

46.33、p型半导体层;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

34、第一连接部;

47.35、第二连接部;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

10、连接点。

具体实施方式

48.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述。在本技术的描述中,需要理解的是,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个所述特征。在本技术的描述

中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

49.本技术实施例提供一种显示面板及其制备方法,所述显示面板包括相对设置的阵列基板和对置基板,以及安装于所述阵列基板上的发光器件。所述阵列基板的表面图案化形成有第一vdd走线和第一vss走线,所述对置基板的表面图案化形成有第二vdd走线和第二vss走线。所述第一vdd走线通过第一导电层连接至所述第二vdd走线,所述第一vss走线通过第二导电层连接至所述第二vss走线。其中,所述第一导电层和所述第二导电层均为金属连接块;或者,所述第一导电层和所述第二导电层均为各向异性导电层。下面将以实施例的方式对显示面板的结构以及制备方法展开详细的描述。

50.实施例1

51.如图1所示,本实施例提供一种显示面板100,其为micro led显示面板,包括相对设置的阵列基板1和对置基板2,以及安装于阵列基板1上的发光器件3。阵列基板1的表面图案化形成有第一vdd走线183和第一vss走线184,对置基板2的表面图案化形成有第二vdd走线22和第二vss走线23。其中,第一vdd走线183通过第一金属连接块41连接至第二vdd走线22,第一vss走线184通过第二金属连接块42连接至第二vss走线23,这样除了发光器件3对应发光区域外,其他区域(例如,薄膜晶体管及电容所在的区域)均可设置走线,从而有利于大大降低显示面板的面内走线的电阻。

52.具体的,阵列基板1包括玻璃基板11、遮光层12、缓冲层13、薄膜晶体管层14、走线层15、钝化层16、导电连接层17以及公共连接层18。

53.遮光层12设于玻璃基板11上,该遮光层12所用的材料可以为金属材料,或者其他的遮光材料,在此不做特别的限定。

54.缓冲层13设于玻璃基板11上,且覆盖遮光层12。缓冲层13所用的材料包括但不限于氮化硅、氧化硅。

55.薄膜晶体管层14设于缓冲层13上,其包括有源层141、栅极层142、源漏极层143以及设置在有源层141与栅极层142、所述源漏极层143之间的层间绝缘层144。其中,层间绝缘层144包括栅极绝缘层441以及介电层442。

56.具体的,有源层141设于缓冲层13上,且正对于遮光层12。有源层141所用的材料包括氧化铟镓锌(indium

‑

gallium

‑

zinc oxide,igzo)、氧化锌(zinc oxide,zno)、氧化锡(stannous oxide,sno)、氧化铟锌(indium

‑

zinc oxide,izo)、氧化镓锌(gallium

‑

zinc oxide,gazno)、氧化锌锡(zinc

‑

tinoxide,zto)、氧化铟锡(indium

‑

tin oxide,ito)及其混合所组成的群组之中的其中一种。

57.栅极绝缘层441设于有源层141上,其所用的材料包括但不限于氮化硅、氧化硅。

58.栅极层142图案化形成于栅极绝缘层441上。

59.介电层442设于缓冲层13上,且覆盖栅极层142及所述有源层141。介电层442所用的材料包括但不限于氮化硅、氧化硅。介电层442设置有两个连接孔4420,用以暴露有源层141。

60.同层设置的源漏极层143和走线层15均设于介电层442上。其中,源漏极层143填充两个连接孔4420,且连接至有源层141。

61.钝化层16设于薄膜晶体管层14上,且覆盖部分源漏极层143及部分走线层15。钝化层16所用的材料包括但不限于氮化硅、氧化硅。钝化层16设置有第一过孔161和第二过孔

162,第一过孔161用以暴露源漏极层143,第二过孔162用以暴露走线层15。

62.导电连接层17穿过钝化层16且连接至部分源漏极层143及走线层15。其中一部分导电连接层17填充第一过孔161,且连接至部分源漏极层143另一部分导电连接层17填充第二过孔162,且连接至走线层15。导电连接层17所采用的材质包括但不限于氧化铟锡(indium tin oxide,ito)。

63.公共连接层18设于导电连接层17上,其图案化形成第一电极181、第二电极182、第一vdd走线183以及第一vss走线184。

64.发光器件3设于阵列基板1与对置基板2之间,且与第二vdd走线22及第二vss走线23错位设置。发光器件3为micro led器件,其包括衬底层31、n型半导体层32、p型半导体层33、第一连接部34以及第二连接部35。其中,第一连接部34为n型电极,且连接至所述第一电极181。第二连接部35为p型电极,且连接至所述第二电极182。

65.在本实施例中,对置基板2包括盖板21、第二vdd走线22、第二vss走线23以及保护层24。

66.盖板21为透明盖板21,第二vdd走线22和第二vss走线23图案化设置在盖板21的一侧表面。

67.保护层24设于盖板21上,其中所述保护层24设置第一开口241用以暴露出所述第二vdd走线22,所述保护层24设置第二开口242用以暴露出所述第二vss走线23。

68.本实施例中,第一金属连接块41的一端通过第一开口241连接至第二vdd走线22,另一端直接连接至第一vdd走线183;第二金属块的一端通过第二开口242连接至第二vss走线23,另一端直接连接至第一vss走线184,以实现阵列基板1与对置基板2之间的信号连接。

69.如图2所示,透过盖板21可以看出,显示面板100具有多个矩阵式排布的连接点10,这些连接点10为第一vdd走线183通过第一金属块连接至第二vdd走线22的连接位置,以及第一vss走线184通过第二金属块连接至第二vss走线23的连接位置。其中,连接点10的数量可以根据用户的需求增加或减少。也就是说,用户可以根据实际需求实现第一vdd走线183与第二vdd走线22的连接,以及第一vss走线184与第二vss走线23的连接。

70.本实施例提供的显示面板100,在除了发光器件3对应发光区域外,其他区域(例如,薄膜晶体管及电容所在的区域)均可设置走线,有利于大大降低显示面板的面内走线的电阻,从而使得显示面板各个位置的亮度均匀。另外,本实施例通过印刷方式、打印方式、物理气相沉积方式中的一种形成第二vdd走线22和第二vss走线23于盖板21上,以增加线宽、膜厚等,实现电阻设计,同时不会对设于对置基板2下的阵列基板1造成负面影响。如图3所示,本实施例还提供一种显示面板的制备方法,包括如下制备步骤s11)

‑

s15)。

71.s11)形成阵列基板1,所述阵列基板1的表面图案化形成有第一vdd走线183和第一vss走线184。

72.具体的,如图4所示,在形成阵列基板1的步骤中,包括如下制备步骤s111)

‑

s118)。

73.s111)形成遮光层12于玻璃基板11上,参照图5。遮光层12所用的材料可以为金属材料,或者其他的遮光材料,在此不做特别的限定。

74.s112)形成缓冲层13于所述玻璃基板11上,且覆盖所述遮光层12,参照图5。缓冲层13所用的材料包括但不限于氮化硅、氧化硅。

75.s113)形成薄膜晶体管层14于所述缓冲层13上,所述薄膜晶体管形成有有源层

141、栅极层142、源漏极层143以及走线层15,其中所述有源层141与所述栅极层142、所述源漏极层143之间设有层间绝缘层144,所述走线层15与所述源漏极层143同层设置,参照图5。

76.具体的,如图6所示,在所述形成薄膜晶体管层14于所述缓冲层13上的步骤中,包括如下制备步骤s1131)

‑

s1136)。

77.s1131)形成所述有源层141于所述缓冲层13上,且正对于所述遮光层12,参照图5。具体的,在缓冲层13上沉积氧化铟镓锌(indium

‑

gallium

‑

zinc oxide,igzo)、氧化锌(zinc oxide,zno)、氧化锡(stannous oxide,sno)、氧化铟锌(indium

‑

zinc oxide,izo)、氧化镓锌(gallium

‑

zinc oxide,gazno)、氧化锌锡(zinc

‑

tinoxide,zto)、氧化铟锡(indium

‑

tin oxide,ito)及其混合所组成的群组之中的其中一种,形成有源层141。

78.s1132)形成所述栅极绝缘层441于所述有源层141上,参照图5。具体的,在有源层141上沉积无机材料(如氮化硅、氧化硅),形成栅极绝缘层441。

79.s1133)形成所述栅极层142于所述栅极绝缘层441上,参照图5。具体的,在栅极绝缘层441上沉积金属材料形成栅极层142。

80.s1134)形成所述介电层442于所述缓冲层13上,且覆盖所述栅极层142及所述有源层141,参照图5。具体的,在介电层442上沉积无机材料(如氮化硅、氧化硅),形成介电层442。

81.s1135)对所述介电层442进行挖孔处理,形成两个连接孔4420,用以暴露出所述有源层141,其中所述两个连接孔4420分别位于所述有源层141的两侧,参照图5。

82.s1136)形成所述源漏极层143及所述走线层15于所述介电层442上,其中所述源漏极层143填充所述两个连接孔4420,且连接至所述有源层141,参照图5。具体的,在介电层442上沉积金属材料,形成金属层,且对金属层图案化处理形成源漏极层143及走线层15。

83.s114)形成钝化层16于所述薄膜晶体管层14上,且覆盖部分所述源漏极层143及部分所述走线层15,参照图5。具体的,在薄膜晶体管层14上沉积无机材料(如氮化硅、氧化硅),形成钝化层16。

84.s115)对所述钝化层16进行挖孔处理,形成第一过孔161和第二过孔162,所述第一过孔161连通至所述源漏极层143表面,所述第二过孔162连通至所述走线层15表面,参照图5。

85.s116)形成导电连接层17于所述钝化层16上,其中一部分所述导电连接层17填充所述第一过孔161,且连接至部分所述源漏极层143,另一部分所述导电连接层17填充所述第二过孔162,且连接至所述走线层15,参照图5。导电连接层17所采用的材质包括但不限于氧化铟锡(indium tin oxide,ito)。

86.s117)形成公共连接层18于所述导电连接层17上,所述公共连接层18包括第一电极181、第二电极182、所述第一vdd走线183以及所述第一vss走线184,参照图5。具体的,在导电连接层17上沉积金属材料形成金属层,且对该金属层进行图案化处理,形成第一电极181、第二电极182、第一vdd走线183以及第一vss走线184。

87.s12)安装发光器件3于所述阵列基板1上,参照图7。具体的,发光器件3为微发光二极管(micro led),其具有第一连接部34和第二连接部35,第一连接部34连接至所述第一电极181,第二连接部35连接至所述第二电极182。

88.s13)设置第一导电层于所述第一vdd走线上以及设置第二导电层于所述第一vss

走线上。其中,所述第一导电层为第一金属连接块41,所述第二导电层为第二金属连接块42。

89.s14)形成对置基板2,所述对置基板2的表面图案化形成有第二vdd走线22和第二vss走线23,所述发光器件3与所述第二vdd走线22及所述第二vss走线23错位设置,参照图8。具体的,通过印刷方式、打印方式、物理气相沉积方式中的一种形成第二vdd走线22和第二vss走线23于盖板21上,以增加线宽、膜厚等,实现电阻设计。

90.s15)将所述阵列基板1与所述对置基板2进行对位组合,其中,所述第一导电层和所述第二导电层设于所述阵列基板1与所述对置基板2之间,参照图1。其中,第一金属连接块41的一侧连接至第一vdd走线183,另一侧通过第一开口241连接至第二vdd走线22;第二金属连接块42的一侧连接至第一vss走线184,另一侧通过第二开口242连接至第二vss走线23。

91.s16)采用焊接方法,使得所述第一vdd走线183通过所述第一导电层固定连接至所述第二vdd走线22,所述第一vss走线184通过所述第二导电层固定连接至第二vss走线23。

92.具体的,结合图1所示,采用焊接方法,使得阵列基板1的第一vdd走线183通过第一金属连接块41与对置基板2的第二vdd走线22实现相互连接,阵列基板1的第一vss走线184通过第二金属连接块42与对置基板2的第二vss走线23实现相互连接,这样除了发光器件3对应发光区域外,其他区域(例如,薄膜晶体管及电容所在的区域)均可设置走线,从而有利于大大降低显示面板的面内走线的电阻。另外,对置基板2不会对位于其下层的阵列基板1造成负面影响。

93.实施例2

94.本实施例提供一种显示面板,包括实施例1的大部分技术特征,其区别在于,所述第一vdd走线通过第一各向异性导电层连接至所述第二vdd走线,所述第一vss走线通过第二各向异性导电层连接至所述第二vss走线。

95.具体的,如图9所示,本实施例提供一种显示面板200,第一vdd走线183通过第一各向异性导电层43连接至第二vdd走线22,第一vss走线184通过第二各向异性导电层44连接至第二vss走线23,以实现阵列基板1与对置基板2之间信号连接。

96.本实施例提供的显示面板200,在除了发光器件3对应发光区域外,其他区域(例如,薄膜晶体管及电容所在的区域)均可设置走线,有利于大大降低显示面板的面内走线的电阻,从而使得显示面板各个位置的亮度均匀。另外,本实施例通过印刷方式、打印方式、物理气相沉积方式中的一种形成第二vdd走线22和第二vss走线23于盖板21上,以实现电阻设计,同时不会对设于对置基板2下方的阵列基板1造成负面影响。

97.本实施例还提供一种显示面板的制备方法,其包括实施例1显示面板的制备方法的大部技术特征,其区别在于,在设置第一导电层于所述第一vdd走线22上以及设置第二导电层于所述第一vss走线23上的步骤中,第一导电层和第二导电层所采用的材质为各向异性导电层(anisotropic conductive film,acf)。也就是说,在第一vdd走线22上涂布各向异性导电胶形成第一各向异性导电层43,使得第一vdd走线183通过第一各向异性导电层43连接至第二vdd走线22;以及在第一vss走线23上涂布各向异性导电胶形成第二vss走线23,使得第一vss走线184通过第二各向异性导电层44连接至第二vss走线23,参照图9。由于本实施例是通过各向异性导电层使得第一vdd走线183与第二vdd走线22实现相互连接,以及

第一vss走线184与第二vss走线23,因此在所述阵列基板1与所述对置基板2进行对位组合的步骤之后,采用加热及加压方法或者其他方法,取代焊接方法,使得所述第一vdd走线183通过所述第一导电层固定连接至所述第二vdd走线22,所述第一vss走线184通过所述第二导电层固定连接至第二vss走线23。

98.本发明的技术效果在于,提供一种显示面板及其制备方法,所述显示面板包括相对设置的阵列基板和对置基板,以及安装于所述阵列基板上的发光器件。其中,所述阵列基板的表面图案化形成有第一vdd走线和第一vss走线,所述对置基板的表面图案化形成有第二vdd走线和第二vss走线。所述第一vdd走线通过第一导电层连接至所述第二vdd走线,所述第一vss走线通过第二导电层连接至所述第二vss走线,有利于大大降低显示面板的面内走线的电阻,从而使得显示面板各个位置的亮度均匀。

99.以上对本技术实施例所提供的一种显示面板及其制备方法进行了详细介绍,本文中应用了具体个例对本技术的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本技术的技术方案及其核心思想;本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本技术各实施例的技术方案的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。