一种超结rb

‑

igbt器件结构及其制造方法

技术领域

1.本发明涉及功率半导体技术领域,特别涉及一种超结rb

‑

igbt器件结构及其制造方法。

背景技术:

2.rb

‑

igbt(reverse blocking insulated gate bipolar transistor,逆阻型绝缘栅双极晶体管)是一种具有反向阻断能力的igbt器件,正反向具有同等水平的耐压能力。受现代数字交流系统驱动和电能转换模块的发展和需求,r b

‑

igbt对于电能转换效率、能源利用率、系统可靠性等至关重要。两个rb

‑ꢀ

igbt反并联可以形成双向开关,能对双向流动的电流进行控制。相比于传统的两个普通igbt和两个frd构成的双向开关,使用rb

‑

igbt不需要额外的frd,节省元器件数量,同时减小了封装体积。因此rb

‑

igbt适合在矩阵变换器、交流斩波器等ac

‑

ac变换装置中应用。

3.传统的rb

‑

igbt采用非穿通型(non

‑

punch

‑

through,npt)igbt结构制造。但npt

‑

igbt反向耐压时没有结终端结构,无法达到与正向相同的耐压能力,因此当前处理方式是在器件的终端区域制造贯穿整个芯片上下的重掺杂p型区来作为反向耐压的终端结构(takei,m;natio,t;ueno,k.the r everse blocking igbt for matrix converter with ultra

‑

thin wafer technology.proceeding ispsd2003,pp.129

‑

132)。但对于600v及以上igbt器件,重掺杂p型区制造工艺复杂,且会占据巨大的芯片面积,增大了制造难度和成本。此外使用npt结构对igbt器件正向导通压降和关断损耗均有不利影响。

技术实现要素:

4.针对现有技术中存在的不足之处,本发明的目的是提供一种超结rb

‑

igbt 器件结构及其制造方法,具有承受反向耐压的能力,通过p型集电区设计可采取多种优化结构,提升超结rb

‑

igbt器件的电学性能和可靠性。为了实现根据本发明的上述目的和其他优点,提供了一种超结rb

‑

igbt器件结构及其制造方法,包括:

5.金属化集电极层;

6.p型集电区,所述p型集电区位于所述金属化集电极层的上方;

7.第一n型外延层,所述第一n型外延层位于p型集电区的上方;

8.第二n型外延层,所述第二n型外延层位于第一n型外延层的上方;

9.所述第一n型外延层中通过高能离子注入形成有p型埋层,且第一n型外延层中与p型埋层间隔设置有p柱,所述p柱通过深槽刻蚀和回填工艺形成。

10.优选的,所述第二n型外延层中通过反应离子刻蚀形成有槽栅,所述槽栅的表面热生长形成有栅氧化层,槽栅内淀积有重掺杂多晶硅。

11.优选的,位于所述第二n型外延层的上方通过自对准工艺离子注入退火形成有p型体区。

12.优选的,所述槽栅远离第一n型外延层的一端两侧设置有重掺杂n型发射区,且所

述第二n型外延层的上方淀积有硼磷硅玻璃,所述硼磷硅玻璃的上方设置有上表面金属化发射极。

13.优选的,所述p型埋层的厚度与掺杂浓度根据器件进行调整,且p型埋层相对于p型集电区的位置根据器件结构进行调整,p型埋层的宽度由第一 n型外延层中的p柱决定。

14.优选的,当器件架构为npt结构,p型埋层进行浮空设置,且p型埋层与p型集电区相连;

15.当器件架构为fs结构,p型埋层为浮空设置且位于fs层上方。

16.优选的,所述第一n型外延层中的p柱与第二n型外延层中的p型体区不相连。

17.一种超结rb

‑

igbt器件结构的制造方法,包括以下步骤:

18.s1、通过晶片采用外延片形成p型集电区与第一n型外延层;

19.s2、通过反应离子刻蚀工艺在第一n型外延层中形成深槽;

20.s3、利用硬掩模作为阻挡层,采用高能离子注入在第一n型外延层中形成p型掺杂层;

21.s4、采用回填工艺在第一n型外延层中形成超结结构p柱;

22.s5、通过外延形成第二n型外延层,且第二n型外延层的电阻率大于第一n型外延层;

23.s6、在第二n型外延层中通过反应离子刻蚀形成槽栅;

24.s7、在槽栅的表面通过干法氧化方式热生长栅氧化层;

25.s8、在槽栅内淀积重掺杂多晶硅并反刻形成栅极;

26.s9、在第二n型外延层的上方通过自对准工艺和离子注入及高温推阱形成p型体区,同时p型掺杂层产生扩散最终形成p型埋层;

27.s10、在p型体区通过光刻注入形成发射区;

28.s11、位于槽栅上方淀积硼磷硅玻璃,高温回流,进行接触孔光刻,并刻蚀3000

‑

5000a厚度的硅,并淀积上表面金属形成发射极;

29.s12、将晶片翻转后进行减薄,并淀积金属层形成集电极。

30.本发明与现有技术相比,其有益效果是:采用深槽刻蚀和回填工艺制造超结结构,可降低器件的正向导通压降,提高开关速度。在深槽刻蚀后通过高能离子注入来制造p型埋层获得器件的反向阻断能力,制造工艺简单,不占用额外面积,节省芯片成本。p型埋层浮空设计不影响igbt器件的集电极侧优化,可在器件集电极侧采用场阻止层(field stop,fs)、透明集电极等结构来优化igbt器件正向导通压降、关断损耗和安全工作区之间的折中关系。

附图说明

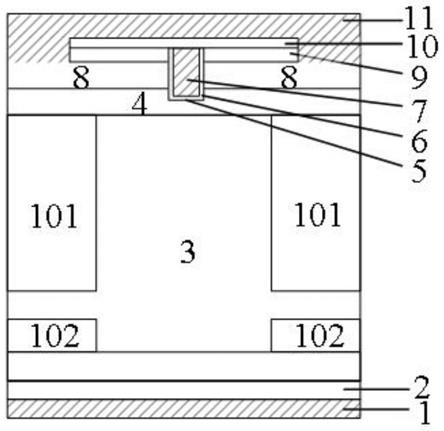

31.图1为传统npt

‑

igbt器件结构及其制造方法的结构示意图;

32.图2为根据本发明的超结rb

‑

igbt器件结构及其制造方法的第一实施例的结构示意图;

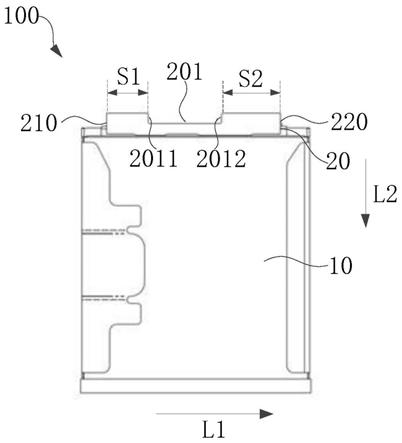

33.图3为根据本发明的超结rb

‑

igbt器件结构及其制造方法的第二实施例结构示意图;

34.图4为根据本发明的超结rb

‑

igbt器件结构及其制造方法的第三实施例结构示意

图;

35.图5

‑

1至图5

‑

12为根据本发明的超结rb

‑

igbt器件结构及其制造方法的步骤制造流程结构如。

具体实施方式

36.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

37.参照图1

‑

4,一种超结rb

‑

igbt器件结构及其制造方法,包括:金属化集电极层1;p型集电区2,所述p型集电区2位于所述金属化集电极层1的上方;第一n型外延层3,所述第一n型外延层3位于p型集电区2的上方;第二n型外延层4,所述第二n型外延层4位于第一n型外延层3的上方;所述第一n型外延层3中通过高能离子注入形成有p型埋层102,且第一n 型外延层3中与p型埋层102间隔设置有p柱101,所述p柱101通过深槽刻蚀和回填工艺形成,本发明的超结rb

‑

igbt器件正向耐压时,第一n型外延层3与第二n型外延层4中的p型体区产生纵向电场,由第一n型外延层3中p柱与n型外延层形成的超结结构产生横向电场,二者共同作用使得器件承受正向电压。当器件处于反向截至状态时,依然是由第一n型外延层3中p柱与n型外延层形成的超结结构产生横向电场,但纵向电场由第一n 型外延层3与p型埋层102、p型集电区共同形成,从而使得器件具有承受反向耐压的能力。浮空p型埋层102可在反向耐压时全部耗尽或者部分耗尽,优化p型埋层102的设计可使得相邻两个p型埋层102产生的耗尽层屏蔽p 型集电区2,从而反向耐压时p型集电区2可不参与耐压作用。因此p型集电区设计可采取多种优化结构,有利于提升超结rb

‑

igbt器件的电学性能和可靠性。

38.进一步的,所述第二n型外延层4中通过反应离子刻蚀形成有槽栅5,所述槽栅5的表面热生长形成有栅氧化层6,槽栅5内淀积有重掺杂多晶硅7。

39.进一步的,位于所述第二n型外延层4的上方通过自对准工艺离子注入退火形成有p型体区8。

40.进一步的,所述槽栅5远离第一n型外延层3的一端两侧设置有重掺杂 n型发射区9,且所述第二n型外延层4的上方淀积有硼磷硅玻璃10,所述硼磷硅玻璃10的上方设置有上表面金属化发射极11。

41.进一步的,所述p型埋层102的厚度与掺杂浓度根据器件进行调整,且 p型埋层102相对于p型集电区2的位置根据器件结构进行调整,p型埋层 102的宽度由第一n型外延层3中的p柱101决定。

42.进一步的,当器件架构为npt结构,p型埋层102进行浮空设置,且p 型埋层102与p型集电区2相连;

43.当器件架构为fs结构,p型埋层102为浮空设置且位于fs层上方。

44.进一步的,所述第一n型外延层3中的p柱101与第二n型外延层4中的p型体区8不相连。

45.参照图5

‑

1至图5

‑

12一种超结rb

‑

igbt器件结构的制造方法,包括以下步骤:

46.s1、通过晶片采用外延片形成p型集电区2与第一n型外延层3;

47.s2、通过反应离子刻蚀工艺在第一n型外延层3中形成深槽;

48.s3、利用硬掩模作为阻挡层,采用高能离子注入在第一n型外延层3中形成p型掺杂层;

49.s4、采用回填工艺在第一n型外延层3中形成超结结构p柱101;

50.s5、通过外延形成第二n型外延层4,且第二n型外延层4的电阻率大于第一n型外延层3;

51.s6、在第二n型外延层4中通过反应离子刻蚀形成槽栅5;

52.s7、在槽栅5的表面通过干法氧化方式热生长栅氧化层6;

53.s8、在槽栅5内淀积重掺杂多晶硅7并反刻形成栅极;

54.s9、在第二n型外延层4的上方通过自对准工艺和离子注入及高温推阱形成p型体区8,同时p型掺杂层产生扩散最终形成p型埋层102;

55.s10、在p型体区8通过光刻注入形成发射区9;

56.s11、位于槽栅5上方淀积硼磷硅玻璃10,高温回流,进行接触孔光刻,并刻蚀3000

‑

5000a厚度的硅,并淀积上表面金属形成发射极11;

57.s12、将晶片翻转后进行减薄,并淀积金属层形成集电极1。

58.这里说明的设备数量和处理规模是用来简化本发明的说明的,对本发明的应用、修改和变化对本领域的技术人员来说是显而易见的。

59.尽管本发明的实施方案已公开如上,但其并不仅限于说明书和实施方式中所列运用,它完全可以被适用于各种适合本发明的领域,对于熟悉本领域的人员而言,可容易地实现另外的修改,因此在不背离权利要求及等同范围所限定的一般概念下,本发明并不限于特定的细节和这里示出与描述的图例。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。