1.本发明涉及无线通信领域,尤其是一种高功率、双频双极化、高集成度的瓦式有源相控阵天线。

背景技术:

2.有源相控阵天线技术广泛应用在军用及民用无线通讯,如卫星通讯,车载移动通讯,终端通讯等。目前对于复杂通讯场景,在双频或多模状态下增加双极化天线,能大大提高整个相控阵天线性能,如抗干扰和目标识别等方面。越发复杂的通讯场景对产品高集成、小型化、低成本、工程化制造、测试维护等提出了更高的需求。

3.目前,有源相控阵系统多为砖式,瓦式有源相控阵天线也多为单频或双频小功率。并且,目前的有源相控阵天线若想设计为双频或者双极化,集成度也较低。

技术实现要素:

4.本发明的发明目的在于:针对上述存在的问题,提供一种高功率双频双极化瓦式有源相控阵天线,以提供一种高集成度、高功率的双频双极化瓦式有源相控阵天线。

5.本发明采用的技术方案如下:一种高功率双频双极化瓦式有源相控阵天线,包括逐层设置的波控电路层、馈电网络层、第一射频层、第二射频层和阵列天线层;所述波控电路层被配置为:向后层传递第一频率极化1信号、第一频率极化2信号、第二频率信号的接入口,以及电源与控制信号,第一频率较第二频率的频率低;所述馈电网络层被配置为:接入所述第一频率极化1信号、第一频率极化2信号,分别利用馈电网络扩展通道向后层传递;接入所述第二频率信号向后层传递;所述第一射频层和所述第二射频层整体被配置为:接入所述第一频率极化1信号、第一频率极化2信号、第二频率信号,经射频芯片组进行射频处理,其中,所述第二频率信号接入所述第二射频层;所述射频芯片组输出端连接所述阵列天线层;所述射频芯片组与第一散热结构接触,所述第一散热结构位于所述射频芯片组远离所述阵列天线层一侧;所述第一射频层和所述第二射频层分别直接或间接连接所述波控电路层以接入电源与控制信号。

6.第一射频层和第二射频层的设计思路为,在第一射频层(离阵列天线层较远的射频层)上尽可能接入低频率射频信号,在第一射频层上无法处理完所有低频率射频信号的通道数据时,再将剩余的通道数据接入第二射频层;而高频率射频信号接入第二射频层(离阵列天线层最近的射频层)处理。第二频率信号为高频率信号,将其从仅可能靠近阵列天线层的位置输出,可以降低传输损耗。

7.进一步的,所述射频芯片组包括设置于所述第一射频层上的第一射频芯片组,和设置于所述第二射频层上的第二射频芯片组;所述第一散热结构包括两个第二散热结构,两个所述第二散热结构分别位于所述馈电网络层和所述第一射频层上;

所述第一射频层被配置为:接入所述馈电网络层所输出信号中,第一频率极化1信号和第一频率极化2信号的至少一个通道输出信号,分别传递给第一射频芯片组,第一射频芯片组的输出端连接所述阵列天线层;所述第一射频芯片组与所述馈电网络层上的第二散热结构接触;所述第二射频层被配置为:接入第一频率极化1信号和第一频率极化2信号的所有通道输出信号中,除接入第一射频层外的其他通道输出信号(即第一频率信号未接入第一射频层的通道输出信号),以及所述第二频率信号,分别经功分网络传递给第二射频芯片组,第二射频芯片组输出端连接所述阵列天线层;所述第二射频芯片组与所述第一射频层上的第二散热结构接触;进一步的,所述馈电网络层上设置有第一频率极化1馈电网络、第一频率极化2馈电网络和第二频率馈电网络;所述第一频率极化1馈电网络接入所述第一频率极化1信号进行通道扩展,所述第一频率极化2馈电网络接入所述第一频率极化2信号进行通道扩展,所述第二频率馈电网络接入所述第二频率信号进行信号传递。

8.进一步的,所述馈电网络层和/或第一射频层和/或所述第二射频层上设置有对接入的至少一路信号进行功分的网络。

9.进一步的,所述第一射频层接入所述第一频率极化1信号的至少一个但非全部通道输出信号和所述第一频率极化2信号的全部通道输出信号;或者,所述第一射频层接入所述第一频率极化1信号的全部通道输出信号和所述第一频率极化2信号的至少一个但非全部通道输出信号。

10.进一步的,所述第二射频层包括第一频率功分网络和第二频率功分网络;接入所述第二射频层的第一频率信号接入所述第一频率功分网络的公共端,第一频率功分网络各输出端分别连接有被配置为对第一频率信号进行射频处理的第一射频结构;第二频率信号接入第二频率功分网络的公共端,第二频率功分网络各输出端分别连接有被配置为对第二频率信号进行射频处理的第二射频结构。

11.进一步的,所述第一射频层通过低频供电排针从所述波控电路层获取电源与控制信号;所述低频供电排针穿过所述馈电网络层,或者,所述低频供电排针经所述馈电网络层上的过渡结构连接所述波控电路层获取电源与控制信号。

12.进一步的,所述第一频率极化1信号与所述第一频率极化2信号接入所述阵列天线层的通道数相同,接入所述阵列天线层的第一频率极化1信号与第一频率极化2信号的通道两两共用一个天线辐射单元。

13.进一步的,射频芯片组采用封装后fc倒装表贴,导热方向为远离所述阵列天线层的方向。

14.进一步的,所述第二散热结构为微流道结构。

15.进一步的,所述微流道结构的入口和出口分别设置于所在层结构上的两相对侧面。

16.综上所述,由于采用了上述技术方案,本发明的有益效果是:1、本设计实现了双频双极化的瓦式有源相控阵天线。

17.2、本设计的有源相控阵天线通过在远离阵列天线层方向进行散热设计,不会对设计尺寸和工艺产生多大影响,便于工业化设计和生产,并且不会影响到芯片的性能。

18.3、本设计的有源相控阵天线在多层结构中,针对大功率芯片进行了针对性的散热设计,不会影响天线整体尺寸,并且能够对芯片进行良好散热,天线具备高功率的特点。

19.4、本设计的有源相控阵天线,每一层均可独立生产、测试、装配、返修;大大简化生产测试流程,提高产品可返修维护性。

附图说明

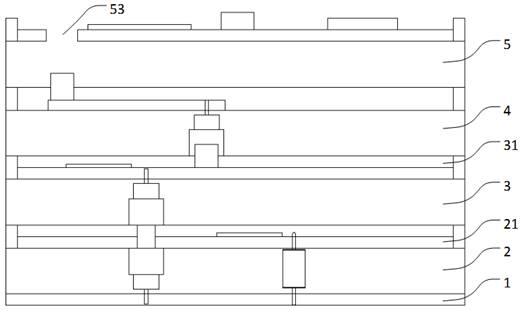

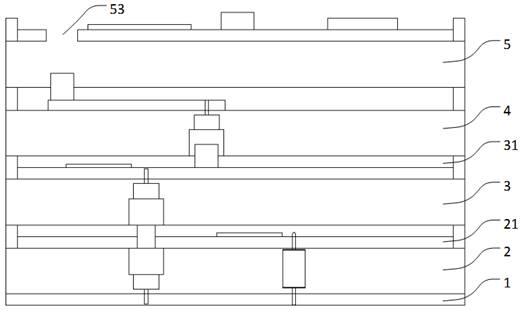

20.本发明将通过例子并参照附图的方式说明,其中:图1是本发明瓦式有源相控阵天线层级结构图。

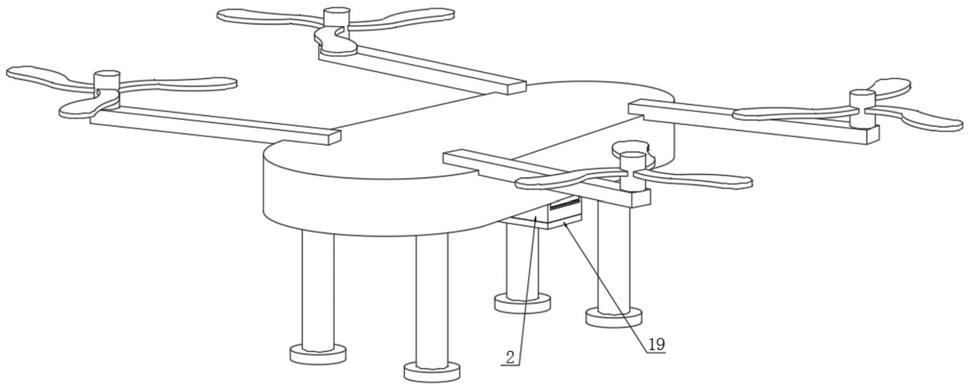

21.图2是瓦式有源相控阵天线剖面示意图。

22.图3是波控电路层结构俯视图。

23.图4是馈电网络层结构俯视图。

24.图5是第一射频层结构俯视图。

25.图6是第二射频层结构俯视图。

26.图7是阵列天线层结构俯视图。

27.图中,1为阵列天线层,2为第二射频层,3为第一射频层,4为馈电网络层,5为波控电路层,11为ku双极化天线,12为ka天线,21为第二多层微波板,221为第一射频绝缘子,222为第二射频绝缘子,24为ka频率8道多功能芯片,25为ka功分网络,26为ku功分网络,28为低频供电针,2231为第四射频smp连接器,2232为第八smp连接器,2271为第一射频垂直连接器,2272为第二射频垂直连接器,233为第二ku大功率tr芯片,234为第二ku频率4通道数字移相衰减芯片,31为第一多层微波板,32为低频供电排针,3231为第三射频smp连接器,3232为第七射频smp连接器,3331为第一ku大功率tr芯片,3332为第三ku大功率tr芯片,3341为第一ku频率4通道数字移相衰减芯片,3342为第三ku频率4通道数字移相衰减芯片,3361为第一射频同轴连接器,3362为第二射频同轴连接器,3363为第三射频同轴连接器,3364为第四射频同轴连接器,3371为第二射频表贴垂直连接器,3372为第三射频表贴垂直连接器,41为馈电层本体,42为ku极化1馈电网络,43为ku极化2馈电网络,44为ka馈电线,45为微流道入口,4231为第二射频smp连接器,4232为第五射频smp连接器,4233为第六射频smp连接器,4234为第十射频smp连接器,4371为第一射频表贴垂直连接器,4372为第四射频表贴垂直连接器,51为波控子板,52为电源与控制信号接口,53为结构开孔。

具体实施方式

28.本说明书中公开的所有特征,或公开的所有方法或过程中的步骤,除了互相排斥的特征和/或步骤以外,均可以以任何方式组合。

29.本说明书(包括任何附加权利要求、摘要)中公开的任一特征,除非特别叙述,均可被其他等效或具有类似目的的替代特征加以替换。即,除非特别叙述,每个特征只是一系列等效或类似特征中的一个例子而已。

30.为便于说明书,本发明实施例中,均以ku频段(对应第一频率)和ka频段(对应第二频率)作为双频为例,对瓦式有源相控阵天线进行说明。

31.实施例一瓦片式相控阵天线的散热方案按照导热方向来分,通常有两种:

一种为热量往天线方向传导。这种方式设计相对简单,但由于导热过程中会先经过微波多层板或ltcc再到结构腔体,但微波多层板导热系数为0.4w/m.k,ltcc导热系数为2w/m.k,加散热通孔也只能改善其导热特性,且大面积打散热孔会影响多层板的布局布线,局部嵌铜对尺寸和工艺要求也很严格,此方案芯片到散热面的热阻较大,若功率过大热量会积累在芯片下方的微波多层板或ltcc影响芯片性能。考虑到本设计的双频双极化天线总功率较大,热密度超过10w/cm2,因此,此种散热方案效果不佳,无法达到大功率的效果。

32.另一种散热方案则是将热量往远离天线方向传导。此种方案将芯片进行晶圆级封装,封装材料为si,导热系数为180w/m.k,芯片封装后采用flip

‑

chip的方式表贴在微波多层板/ltcc上,芯片的散热面调到远离天线方向,如此一来,便不需要考虑微波多层板/ltcc的导热,布局布线不受散热孔或嵌铜限制,且硅导热系数很大,能很好的将热量传导到上方结构件,再配合内部微流道等导热结构的设计带走热量,实现高密度散热能力。此种散热方案对本设计的双频双极化的产热量高的天线较为适用,本实施例的有源相控阵天线则围绕此种散热结构进行高集成设计。并且,芯片采用晶圆级封装,通过芯片内部rdl走线及植球,可节省芯片布局面积,单位尺寸模块下能布局更多芯片,提升相控阵天线威力及天线性能;且生产时可采用批量smt表贴,节省传统芯片焊接、粘接、键合等工序,大大降低生产成本。

33.高功率双频双极化瓦式有源相控阵天线采用多层瓦片垂直叠装结构,如图1、图2所示,由上而下包括波控电路层5、馈电网络层4、第一射频层3、第二射频层2和阵列天线层1,该阵列天线层为双频双极化共口径阵列天线。除第二射频层2与阵列天线层1之间为面对面连接外,对于其余各层,相邻层之间过盈配合,具体的,位于上侧的层结构腔体底部设计凸台、位于下侧的层结构腔体顶部设计围框(或者反之),上、下层结构腔体对接连接。凸台与射频芯片组接触,以对射频芯片组进行良好地散热。

34.如图3所示,波控电路层5包括波控子板51,波控子板51上表面设置有ku极化1信号接口、ku极化2信号接口和ka射频信号接口,以及电源与控制信号接口52。具体的,ku极化1信号接口、ku极化2信号接口和ka射频信号接口均为在波控子板51上预留的结构开孔53。ku极化1信号通过外接第一射频smp连接器(未示出)从波控子板51上的结构开孔53接入馈电网络层,ku极化2信号通过外接第十一射频smp连接器(未示出)从波控子板51上的结构开孔53接入馈电网络层,ka射频信号通过外接第九射频smp连接器(未示出)从波控子板51上的结构开孔53接入馈电网络层。

35.如图4所示,馈电网络层4包括馈电层本体41,馈电层本体41上设置两个第一射频表贴垂直连接器4371、一个第四射频表贴垂直连接器4372、ku极化1馈电网络42、ku极化2馈电网络43和ka馈电线44。一个第一射频表贴垂直连接器4371与ku极化1馈电网络42的耦合端连接,该ku极化1馈电网络42分3路通道,其中两路通道末端分别连接一第二射频smp连接器4231,一路通道末端连接一第五射频smp连接器4232,该第一射频表贴垂直连接器4371用于与第一射频smp连接器连接。另一个第一射频表贴垂直连接器4371与ku 极化2馈电网络43的耦合端连接,该ku 极化2馈电网络43分4路通道,各通道末端分别连接一第六射频smp连接器4233,该第一射频表贴垂直连接器4371用于与第十一smp连接器连接。第四射频表贴垂直连接器4372与ka馈电线44连接,ka馈电线44末端与第十射频smp连接器4234连接,该第四射频表贴垂直连接器4372用于与第九smp连接器连接。馈电层本体41上还设置有供低频供电排针32穿过的过孔,或者为低频供电排针32转接电信号的过渡结构。馈电层本体41内

设置有第一微流道结构,如图1所示,该第一微流道结构的入口和出口分别设置于馈电层本体41的两相对侧面,例如图中所示的前、后两侧面。

36.如图5所示,第一射频层3包括第一多层微波板31,第一多层微波板31上设置有两组ku极化1通道射频结构和四组ku极化2通道射频结构。ku极化1通道射频结构包括第二射频表贴垂直连接器3371、第一ku频率4通道数字移相衰减芯片3341、第一ku大功率tr芯片3331和第三射频smp连接器3231;第二射频表贴垂直连接器3371连接第一ku频率4通道数字移相衰减芯片3341,第一ku频率4通道数字移相衰减芯片3341的每一输出通道分别连接一第一ku大功率tr芯片3331,每一第一ku大功率tr芯片3331分别通过微带同轴过渡以连接一第三射频smp连接器3231。两个第二射频表贴垂直连接器3371分别与两个第二射频smp连接器4231一一对应。ku极化2通道射频结构包括第三射频表贴垂直连接器3372、第三ku频率4通道数字移相衰减芯片3342、第三ku大功率tr芯片3332和第七射频smp连接器3232;第三射频表贴垂直连接器3372连接第三ku频率4通道数字移相衰减芯片3342,第三ku频率4通道数字移相衰减芯片3342的每一输出通道分别连接一第三ku大功率tr芯片3332,每一第三ku大功率tr芯片3332分别通过微带同轴过渡以与一第七射频smp连接器3232连接。两组ku极化1通道射频结构和四组ku极化2通道射频结构中的芯片即构成了第一射频芯片组,即各第一ku频率4通道数字移相衰减芯片3341、第一ku大功率tr芯片3331、第三射频表贴垂直连接器3372、第三ku频率4通道数字移相衰减芯片3342共同构成第一射频芯片组。四个第三射频表贴垂直连接器3372分别与四个第六射频smp连接器4233一一对应。第一多层微波板31上还设置有第二射频同轴连接器3362、第四射频同轴连接器3364和低频供电排针32,第二射频同轴连接器3362与第五射频smp连接器4232对应,第四射频同轴连接器3364与第十射频smp连接器4234对应,低频供电排针32经过馈电层本体41上的过孔或过渡结构与波控子板51连接以获得电源与控制信号。第一多层微波板31内设置有第二微流道结构,如图1所示,该第二微流道结构的入口和出口分别设置于第一多层微波板31的两相对侧面,例如图中所示的前、后两面。第一微流道结构和第二微流道结构的微流道入口45在图1示出。

37.如图6所示,第二射频层2包括第二多层微波板21,第二多层微波板21上设置有第一射频垂直连接器2271、第二射频垂直连接器2272,第一射频垂直连接器2271与第二射频同轴连接器3362对应连接,第二射频垂直连接器2272与第四射频同轴连接器3364对应连接。第一射频垂直连接器2271连接ku功分网络26的公共端,经ku功分网络26一分为二,ku功分网络26的两末端分别连接一第二ku频率4通道数字移相衰减芯片234,第二ku频率4通道数字移相衰减芯片234的4个输出通道分别连接一第二ku大功率tr芯片233,各第二ku大功率tr芯片233分别通过微带同轴过渡到一第一射频绝缘子221。第二射频垂直连接器2272连接ka功分网络25的公共端,经ka功分网络25一分为四,ka功分网络25的四个末端分别连接一ka频率8通道多功能芯片24,对ka频率信号进行调幅调相、放大,ka频率8通道多功能芯片24的8个输出端分别通过微带同轴过渡到一第二射频绝缘子222。各第二ku频率4通道数字移相衰减芯片234、第二ku大功率tr芯片233、ka频率8通道多功能芯片24共同构成第二射频芯片组。第二多层微波板21上还设置有低频供电针28,该低频供电针28连接到第一射频层3/第一多层微波板31以获得电源与控制信号。第二多层微波板21上,与各第三射频smp连接器3231一一对应设置有第四射频smp连接器,与各第七射频smp连接器3232一一对应设置有第八smp连接器2232,第三射频smp连接器3231通过第一射频同轴连接器3361与对应第四射

频smp连接器连接,第七射频smp连接器3232通过第三射频同轴连接器3363与对应第八smp连接器2232连接。

38.上述公开了馈电网络层4、第一射频层3、第二射频层2的一种组合设计方式,实际上,此三层结构还可组合设计为其他结构,在三层结构上,可以全部或部分设计功分网络,配合射频芯片组、信号过渡结构,完成对三路信号的功分、射频处理以及输出。

39.如图7所示,阵列天线层1由ku双极化天线11和ka天线12以及内层馈电网络组成,通过馈电口接入到ku双极化天线11或者ka天线12。本实施例附图示意的天线设计方式为ku双极化通道共用天线辐射层,ka天线12为单极化32通道天线单元,采用稀疏布局的方式。各路第四射频smp连接器2231、第一射频绝缘子221分别与阵列天线层1中的ku双极化天线11中极化1馈电口相连通,第八smp连接器2232与阵列天线层1中的ku双极化天线11中极化2馈电口相连通,共计16个ku极化1通道和16个ku极化2通道,共计32通道,两个极化的通道两两共用一个天线辐射单元。各路第二射频绝缘子222分别与阵列天线层1中的ka天线12连接,共计32个ka天线单元。

40.实施例二本实施例公开了另一种高功率双频双极化瓦式有源相控阵天线,其与实施例一所公开的结构大致相同,唯一不同之处在于,波控电路层5上设置第一频率信号的接入口、第二频率信号的接入口和电源与控制信号接口,波控电路层5上设置有对第一频率信号进行功分的功分器,第一频率信号接入该功分器后,得到第一频率极化1信号和第一频率极化2信号,波控电路层5向后层输出第一频率极化1信号、第一频率极化2信号、第二频率信号及电源与控制信号。

41.实施例三本实施例公开了另一种高功率双频双极化瓦式有源相控阵天线,其与实施例一所公开的结构大致相同,唯一不同之处在于,第一射频层3和第二射频层2的结构。本实施例中,第一射频层3上的第一射频芯片组仅对第一频率信号进行射频处理,即第一频率极化1信号和第二频率极化2信号的各通道均仅接入第一射频层3。可以将上述实施例中位于第二射频层2中的第二ku大功率tr芯片233、,第二ku频率4通道数字移相衰减芯片234设法移到第一射频层3,或者在第一射频层3上设置ku频率8道多功能芯片,将原接入第二射频层2中的通道信号接入该ku频率8道多功能芯片(构成第一射频芯片组中的一部分),或者将第一射频芯片组全部设计为ku频率8道多功能芯片,将第一频率极化1信号、第一频率极化2信号的所有通道分别接入对应的ku频率8道多功能芯片。第一射频芯片组的输出端穿过第二射频层2连接阵列天线层1/或经第二射频层2转接阵列天线层1;第二射频层2上的第二射频芯片组仅对第二频率信号进行射频处理,即第二射频层2上仅接入第二频率信号,第二射频芯片组的输出端连接阵列天线层1。

42.实施例四双频为ku频率和ka频率,ku频率为双极化工作,每种极化16个通道,共计32通道,两种极化两两共用一天线辐射面,共16个ku天线单元。ka频率为单极化工作,同样为32通道,天线辐射面不进行共用,共32个ka天线单元。

43.ka射频信号、ku射频信号、电源与控制信号均从波控电路层5接入。

44.参见附图2,ku射频信号的ku极化1信号和ku极化2信号分别经第一射频smp连接器

和第十一射频smp连接器从波控电路层5上不同的结构开孔53接入到馈电网络层4上的两个第一射频表贴垂直连接器4371。馈电网络层4包含3路ku极化1通道和4路ku极化2通道。

45.由于本发明中使用的大功率ku频率tr芯片匹配4通道移相衰减芯片,考虑布局面积和电磁兼容性问题,本实施例将ku极化1的16个通道分两层布置。

46.结合附图4~附图6,馈电网络层4中的3路ku极化1通道,其中两路经第二射频smp连接器4231垂直连接到第一射频层3的第二射频表贴垂直连接器3371,信号经第一ku频率4通道数字移相衰减芯片3341的调幅调相、第一ku大功率tr芯片3331放大,由第一多层微波板31中的微带同轴过渡到第三射频smp连接器3231,第三射频smp连接器3231垂直向下通过第一射频同轴连接器3361插接到第二射频层2上的第四射频smp连接器2231,第四射频smp连接器2231再与双频双极化共口径阵列天线层1中的ku双极化天线11中极化1馈电口相连通,共8个ku极化1通道。3路ku极化1通道中剩下的一路经第五射频smp连接器4232与第二射频同轴连接器3362插接到第二射频层2上的第一射频垂直连接器2271,经过ku功分网络26一分为二后,分别经第二ku频率4通道数字移相衰减芯片234的调幅调相、第二ku大功率tr芯片233放大,由第二多层微波板21中的微带同轴过渡到第一射频绝缘子221,第一射频绝缘子221再与双频双极化共口径阵列天线层1中的ku双极化天线11中极化1馈电口相连通,ku极化1共16个通道。

47.馈电网络层4中的4路ku极化2通道经第六射频smp连接器4233垂直连接到第一射频层3的第三射频表贴垂直连接器3372,信号经第三ku频率4通道数字移相衰减芯片3342的调幅调相、第三ku大功率tr芯片3332放大,通过第一多层微波板31中的微带同轴过渡焊接到第七射频smp连接器3232,信号垂直向下通过第三射频同轴连接器3363插接第二射频层2上的第八smp连接器2232,第八smp连接器2232与双频双极化共口径阵列天线层1中的ku双极化天线11中极化2馈电口相连通,共16个ku极化2通道。如此一来,共有16个ku极化1通道和16个ku极化2通道分别接入到相应的天线馈电口,最后两个极化的通道两两共用一个天线辐射单元。

48.ka射频信号经第九射频smp连接器从波控电路层5的另一结构开孔接入到馈电网络层4上的第四射频表贴垂直连接器4372,馈电网络层4上包含1路ka信号通道,第四射频表贴垂直连接器4372通过ka馈电线44与第十射频smp连接器4234相连,ka信号经馈电网络层4上的第十射频smp连接器4234与第一射频层3上的第四射频同轴连接器3364连接到第二射频层2上的第二射频垂直连接器2272,经ka功分网络25分为4路后,由ka频率8通道多功能芯片24调幅调相、放大后,通过第二多层板21内的微带同轴过渡焊接到第二射频绝缘子222,32路第二射频绝缘子222分别连接到双频双极化共口径阵列天线层1中的ka天线12。

49.第二射频层2的芯片供电由第一射频层3通过低频供电针28提供,低频供电针28最终通过腔体底部空间与第一射频层3底层相连。第一射频层3及其第一多层微波板31上的芯片供电均由波控电路层5通过低频供电排针32提供,低频供电排针32穿过馈电网络层4,与波控电路城5底层相连。需要说明的是,第一多层微波板31和第二多层微波板21内部均包含射频走线和低频供电控制走线。

50.本发明阐述的频率为ku频段和ka频段,但不限于该两个频率段,也可以多个不同频段组合使用;芯片封装形式不仅限于文中所述的硅基晶圆级封装,也可以采用导热性能较好的sic或者氮化铝等材料进行芯片封装。封装后fc倒装表贴,导热方向为远离所述阵列

天线层1的方向,不会影响天线性能,对封装尺寸也无影响。

51.本发明并不局限于前述的具体实施方式。本发明扩展到任何在本说明书中披露的新特征或任何新的组合,以及披露的任一新的方法或过程的步骤或任何新的组合。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。