1.本技术涉及芯片封装技术领域,具体涉及一种封装芯片。

背景技术:

2.存储器是计算机系统中的记忆设备,用来存放程序和数据。计算机中全部信息,包括输入的原始数据、计算机程序、中间运行结果和最终运行结果都保存在存储器中。近年来,在半导体存储器迅速发展的过程中,闪存(flash)由于具有高密度、低功耗和低价格的优点,已经成为了计算机、移动通信终端中普遍采用的存储器。

3.包括应答保护单调计数器(replay protection monotonic counter,rpmc)的增强型闪存芯片,是把flash芯片和rpmc芯片集成在一颗裸芯片上,其中,flash芯片可以用来存储中央处理单元(central processing unit,cpu)的基本输入输出系统(basic input output system,bios)的代码和数据;rpmc芯片可以用来保证读写数据的机密性和完整性。flash芯片和rpmc芯片一起构成了个人计算机(personal computer,pc)系统中bios的硬件平台。

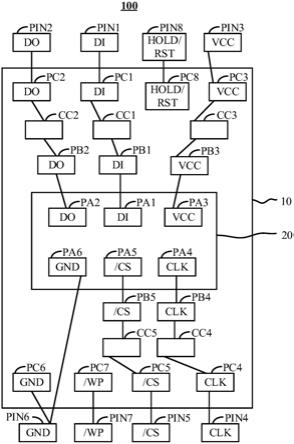

4.请参阅图1,图1为传统技术方案的增强型闪存芯片的逻辑连接示意图,增强型闪存芯片一般是将flash芯片和rpmc芯片分别通过外部共享引脚接收外部输入数据,即增强型闪存芯片的同一外部共享引脚分别直接与flash芯片的对应引脚和rpmc芯片的对应引脚连接,如图1中的外部共享引脚a、b

……

n。但是,该种方案在处理抗静电干扰中需要较多的电路,例如,flash芯片的任一对应引脚需要设置一抗静电干扰电路,同时,rpmc芯片的任一对应引脚也需要设置一抗静电干扰电路,极大增加了flash芯片的面积和/或体积,以及rpmc芯片的面积和/或体积,最终导致封装芯片的面积或者体积过大。

5.同时,图1所示的增强型闪存芯片在外部输入数据进入后,flash芯片或者rpmc芯片需要分别对该外部输入数据进行处理,即flash芯片或者rpmc芯片需要分别设置对应的控制电路对该外部输入数据进行处理,进一步导致了封装芯片的面积或者体积过大。

6.需要注意的是,上述关于背景技术的介绍仅仅是为了便于清楚、完整地理解本技术的技术方案。因此,不能仅仅由于其出现在本技术的背景技术中,而认为上述所涉及到的技术方案为本领域所属技术人员所公知。

技术实现要素:

7.本技术提供一种封装芯片,以缓解封装芯片的面积或者体积过大的技术问题。

8.第一方面,本技术提供一种封装芯片,其包括第一裸片、第二裸片以及第一封装引脚,第一裸片包括第一主焊盘、第一辅焊盘以及第一控制电路,第一主焊盘与第一控制电路的输入端/输出端中的一个电性连接,第一辅焊盘与第一控制电路的输入端/输出端中的另一个电性连接;第二裸片包括第一子焊盘,第一子焊盘与第一辅焊盘电性连接;第一封装引脚与第一主焊盘电性连接。

9.在其中一些实施方式中,第一封装引脚用于传输输入信号。

10.在其中一些实施方式中,第一裸片还包括第二主焊盘、第二辅焊盘以及第二控制电路,第二主焊盘与第二控制电路的输入端/输出端中的一个电性连接,第二辅焊盘与第二控制电路的输入端/输出端中的另一个电性连接;第二裸片还包括第二子焊盘,第二子焊盘与第二辅焊盘电性连接;封装芯片还包括第二封装引脚,第二封装引脚与第二主焊盘电性连接。

11.在其中一些实施方式中,第二封装引脚用于传输输出信号。

12.在其中一些实施方式中,第一裸片还包括第三主焊盘、第三辅焊盘以及第三控制电路,第三主焊盘与第三控制电路的输入端/输出端中的一个电性连接,第三辅焊盘与第三控制电路的输入端/输出端中的另一个电性连接;第二裸片还包括第三子焊盘,第三子焊盘与第三辅焊盘电性连接;封装芯片还包括第三封装引脚,第三封装引脚与第三主焊盘电性连接。

13.在其中一些实施方式中,第三封装引脚用于传输直流电源正信号,第三控制电路为升压电路和/或降压电路。

14.在其中一些实施方式中,封装芯片还包括第一抗静电干扰电路,第一抗静电干扰电路与第一主焊盘、第一辅焊盘中的任一个电性连接。

15.在其中一些实施方式中,第一子焊盘至第一封装引脚的外接端的距离大于第一辅焊盘至第一封装引脚的外接端的距离,且第一辅焊盘至第一封装引脚的外接端的距离大于第一主焊盘至第一封装引脚的外接端的距离。

16.在其中一些实施方式中,第一裸片为存储芯片,第二裸片为应答保护单调计数器;存储芯片用于根据接入的外部输入数据生成对应的第一内部输出数据,且转存外部输入数据至应答保护单调计数器;应答保护单调计数器与存储芯片通信连接,用于根据外部输入数据生成对应的第二内部输出数据,且转存第二内部输出数据至存储芯片;其中,存储芯片还用于输出第一内部输出数据和第二内部输出数据。

17.在其中一些实施方式中,存储芯片包括第一输入控制器、第一输入缓冲器、第一输出缓冲器以及第一输出控制器,第一输入控制器用于接入外部输入数据;第一输入缓冲器与第一输入控制器和应答保护单调计数器连接,用于在第一输入控制器的控制下,缓存外部输入数据,并转存外部输入数据至应答保护单调计数器;第一输出缓冲器与应答保护单调计数器连接,用于缓存第一内部输出数据和第二内部输出数据;第一输出控制器与第一输出缓冲器连接,用于输出第一内部输出数据和/或第二内部输出数据至存储芯片的外部。

18.在其中一些实施方式中,应答保护单调计数器包括第二输入控制器、第二输入缓冲器、缓冲控制器、第二输出缓冲器以及第二输出控制器,第二输入控制器与第一输入缓冲器连接,用于接入外部输入数据;第二输入缓冲器与第二输入控制器连接,用于在第二输入控制器的控制下缓存外部输入数据;缓冲控制器与第二输入缓冲器连接,用于根据外部输入数据生成第二内部输出数据;第二输出缓冲器与缓冲控制器连接,用于缓存第二内部输出数据;第二输出控制器与第二输出缓冲器和第一输出缓冲器连接,用于输出第二内部输出数据至第一输出缓冲器。

19.在其中一些实施方式中,存储芯片还包括状态寄存器,与第一输出控制器和第二输出控制器连接,用于寄存应答保护单调计数器的工作状态数据。

20.在其中一些实施方式中,应答保护单调计数器叠加放置于存储芯片之上。

21.本技术提供的封装芯片,通过第一子焊盘、第一辅焊盘、第一控制电路、第一主焊盘以及第一封装引脚的依次电性连接,第一裸片与第二裸片中的共用引脚可以共用同一控制电路,减少了封装芯片中控制电路的使用数量,可以减小封装芯片的面积或者体积;同时,同一封装引脚仅需要配置一个抗静电干扰电路即可实现第一裸片与第二裸片中共用引脚的抗静电干扰,进一步减少了封装芯片中抗静电干扰电路的使用数量,能够进一步减小封装芯片的面积或者体积。

附图说明

22.下面结合附图,通过对本技术的具体实施方式详细描述,将使本技术的技术方案及其它有益效果显而易见。

23.图1为传统技术方案中封装芯片的结构示意图。

24.图2为本技术实施例提供的封装芯片的第一种结构示意图。

25.图3为本技术实施例提供的封装芯片的第二种结构示意图。

26.图4为本技术实施例提供的封装芯片的第三种结构示意图。

27.图5为本技术实施例提供的封装芯片的第四种结构示意图。

具体实施方式

28.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

29.请参阅图2至图5,如图2所示,本实施例提供了一种封装芯片100,其包括用于传输输入信号di的第一封装引脚pin1、用于传输输出信号do的第二封装引脚pin2、用于传输直流电源正信号vcc的第三封装引脚pin3、用于传输时钟信号clk的第四封装引脚pin4、用于传输片选信号/cs的第五封装引脚pin5、用于传输直流电源负信号gnd的第六封装引脚pin6、用于传输写保护信号/wp的第七封装引脚pin7以及用于传输挂起信号hold或者复位信号rst的第八封装引脚pin8。

30.需要进行说明的是,第一封装引脚pin1可以作为封装芯片100的外接引脚5。第二封装引脚pin2可以作为封装芯片100的外接引脚2。第三封装引脚pin3可以作为封装芯片100的外接引脚8。第四封装引脚pin4可以作为封装芯片100的外接引脚6。第五封装引脚pin5可以作为封装芯片100的外接引脚1。第六封装引脚pin6可以作为封装芯片100的外接引脚4。第七封装引脚pin7可以作为封装芯片100的外接引脚3。第八封装引脚pin8可以作为封装芯片100的外接引脚7。

31.其中,如图3所示,上述封装芯片100还包括第一裸片10和第二裸片20,第一裸片10包括第一主焊盘pc1、第一辅焊盘pb1以及第一控制电路cc1,第一主焊盘pc1与第一控制电路cc1的输入端/输出端中的一个电性连接,第一辅焊盘pb1与第一控制电路cc1的输入端/输出端中的另一个电性连接;第二裸片20包括第一子焊盘pa1,第一子焊盘pa1与第一辅焊盘pb1电性连接;第一封装引脚pin1与第一主焊盘pc1电性连接。

32.可以理解的是,本实施例提供的封装芯片100通过第一子焊盘pa1、第一辅焊盘

pb1、第一控制电路cc1、第一主焊盘pc1以及第一封装引脚pin1的依次电性连接,第一裸片10与第二裸片20中的共用引脚可以共用第一控制电路cc1,减少了封装芯片100中第一控制电路cc1的使用数量,可以减小封装芯片100的面积或者体积;同时,第一封装引脚pin1仅需要配置一个抗静电干扰电路即可实现第一裸片10与第二裸片20中共用引脚的抗静电干扰,进一步减少了封装芯片100中抗静电干扰电路的使用数量,能够进一步减小封装芯片100的面积或者体积。

33.在其中一个实施例中,封装芯片100还包括第一抗静电干扰电路,第一抗静电干扰电路可以但不限于直接电性连接于第一主焊盘pc1、第一辅焊盘pb1中的任一个;第一抗静电干扰电路也可以直接电性连接于第一辅焊盘pb1与第一主焊盘pc1之间的任一处;优选的,第一抗静电干扰电路可以位于第一主焊盘pc1和第一控制电路cc1之间,这样可以有效保护整个相关通路免受外部静电的影响。

34.在其中一个实施例中,第一裸片10还包括第二主焊盘pc2、第二辅焊盘pb2以及第二控制电路cc2,第二主焊盘pc2与第二控制电路cc2的输入端/输出端中的一个电性连接,第二辅焊盘pb2与第二控制电路cc2的输入端/输出端中的另一个电性连接;第二裸片20还包括第二子焊盘pa2,第二子焊盘pa2与第二辅焊盘pb2电性连接;第二封装引脚pin2与第二主焊盘pc2电性连接。

35.可以理解的是,本实施例提供的封装芯片100通过第二子焊盘pa2、第二辅焊盘pb2、第二控制电路cc2、第二主焊盘pc2以及第二封装引脚pin2的依次电性连接,第一裸片10与第二裸片20中的共用引脚可以共用第二控制电路cc2,减少了封装芯片100中第二控制电路cc2的使用数量,可以减小封装芯片100的面积或者体积;同时,第二封装引脚pin2仅需要配置一个抗静电干扰电路即可实现第一裸片10与第二裸片20中共用引脚的抗静电干扰,进一步减少了封装芯片100中抗静电干扰电路的使用数量,能够进一步减小封装芯片100的面积或者体积。

36.在其中一个实施例中,封装芯片100还包括第二抗静电干扰电路,第二抗静电干扰电路可以但不限于直接电性连接于第二主焊盘pc2、第二辅焊盘pb2中的任一个;第二抗静电干扰电路也可以直接电性连接于第二辅焊盘pb2与第二主焊盘pc2之间的任一处;优选的,第二抗静电干扰电路可以位于第二主焊盘pc2和第二控制电路cc2之间,这样可以有效保护整个芯片相关通路免受外部静电的影响。

37.在其中一个实施例中,第一裸片10还包括第三主焊盘pc3、第三辅焊盘pb3以及第三控制电路cc3,第三主焊盘pc3与第三控制电路cc3的输入端/输出端中的一个电性连接,第三辅焊盘pb3与第三控制电路cc3的输入端/输出端中的另一个电性连接;第二裸片20还包括第三子焊盘pa3,第三子焊盘pa3与第三辅焊盘pb3电性连接;第三封装引脚pin3与第三主焊盘pc3电性连接。

38.可以理解的是,本实施例提供的封装芯片100通过第三子焊盘pa3、第三辅焊盘pb3、第三控制电路cc3、第三主焊盘pc3以及第三封装引脚pin3的依次电性连接,第一裸片10与第二裸片20中的共用引脚可以共用第三控制电路cc3,减少了封装芯片100中第三控制电路cc3的使用数量,可以减小封装芯片100的面积或者体积;同时,第三封装引脚pin3仅需要配置一个抗静电干扰电路即可实现第一裸片10与第二裸片20中共用引脚的抗静电干扰,进一步减少了封装芯片100中抗静电干扰电路的使用数量,能够进一步减小封装芯片100的

面积或者体积。

39.在其中一个实施例中,第三封装引脚pin3用于传输直流电源正信号vcc,第三控制电路cc3为升压电路和/或降压电路。

40.需要进行说明的是,供电该封装芯片100的电源可以为直流电源,该直流电源的正极输出的信号则为直流电源正信号vcc。

41.在其中一个实施例中,封装芯片100还包括第三抗静电干扰电路,第三抗静电干扰电路可以但不限于直接电性连接于第三主焊盘pc3、第三辅焊盘pb3中的任一个;第三抗静电干扰电路也可以直接电性连接于第三辅焊盘pb3与第三主焊盘pc3之间的任一处;优选的,第三抗静电干扰电路可以位于第三主焊盘pc3和第三控制电路cc3之间,这样可以有效保护整个芯片相关通路免受外部静电的影响。

42.在其中一个实施例中,第一裸片10还包括第四主焊盘pc4、第四辅焊盘pb4以及第四控制电路cc4,第四主焊盘pc4与第四控制电路cc4的输入端/输出端中的一个电性连接,第四辅焊盘pb4与第四控制电路cc4的输入端/输出端中的另一个电性连接;第二裸片20还包括第四子焊盘pa4,第四子焊盘pa4与第四辅焊盘pb4电性连接;第四封装引脚pin4与第四主焊盘pc4电性连接。

43.可以理解的是,本实施例提供的封装芯片100通过第四子焊盘pa4、第四辅焊盘pb4、第四控制电路cc4、第四主焊盘pc4以及第四封装引脚pin4的依次电性连接,第一裸片10与第二裸片20中的共用引脚可以共用第四控制电路cc4,减少了封装芯片100中第四控制电路cc4的使用数量,可以减小封装芯片100的面积或者体积;同时,第四封装引脚pin4仅需要配置一个抗静电干扰电路即可实现第一裸片10与第二裸片20中共用引脚的抗静电干扰,进一步减少了封装芯片100中抗静电干扰电路的使用数量,能够进一步减小封装芯片100的面积或者体积。

44.在其中一个实施例中,第四控制电路cc4可以为逻辑电路,该逻辑电路可以对时钟信号clk进行逻辑运算。

45.在其中一个实施例中,逻辑电路为反相器,可以理解的是,该反相器可以对时钟信号clk的电位取反,例如,当时钟信号clk的电位为高电位时,经过该逻辑电路后,则该时钟信号clk的电位跳变为低电位;当时钟信号clk的电位为低电位时,经过该逻辑电路后,则该时钟信号clk的电位跳变为高电位。

46.在其中一个实施例中,封装芯片100还包括第四抗静电干扰电路,第四抗静电干扰电路可以但不限于直接电性连接于第四主焊盘pc4、第四辅焊盘pb4中的任一个;第四抗静电干扰电路也可以直接电性连接于第四辅焊盘pb4与第四主焊盘pc4之间的任一处;优选的,第四抗静电干扰电路可以位于第四主焊盘pc4和第四控制电路cc4之间,这样可以有效保护整个相关通路免受外部静电的影响。

47.在其中一个实施例中,第一裸片10还包括第五主焊盘pc5、第五辅焊盘pb5以及第五控制电路cc5,第五主焊盘pc5与第五控制电路cc5的输入端/输出端中的一个电性连接,第五辅焊盘pb5与第五控制电路cc5的输入端/输出端中的另一个电性连接;第二裸片20还包括第五子焊盘pa5,第五子焊盘pa5与第五辅焊盘pb5电性连接;第五封装引脚pin5与第五主焊盘pc5电性连接。

48.可以理解的是,本实施例提供的封装芯片100通过第五子焊盘pa5、第五辅焊盘

pb5、第五控制电路cc5、第五主焊盘pc5以及第五封装引脚pin5的依次电性连接,第一裸片10与第二裸片20中的共用引脚可以共用第五控制电路cc5,减少了封装芯片100中第五控制电路cc5的使用数量,可以减小封装芯片100的面积或者体积;同时,第五封装引脚pin5仅需要配置一个抗静电干扰电路即可实现第一裸片10与第二裸片20中共用引脚的抗静电干扰,进一步减少了封装芯片100中抗静电干扰电路的使用数量,能够进一步减小封装芯片100的面积或者体积。

49.在其中一个实施例中,第五控制电路cc5可以为逻辑电路,该逻辑电路可以对片选信号/cs进行逻辑运算。

50.在其中一个实施例中,逻辑电路为反相器,可以理解的是,该反相器可以对片选信号/cs的电位取反,例如,当片选信号/cs的电位为高电位时,经过该逻辑电路后,则该片选信号/cs的电位跳变为低电位;当片选信号/cs的电位为低电位时,经过该逻辑电路后,则该片选信号/cs的电位跳变为高电位。

51.其中,该片选信号/cs可以用于选择存储芯片和应答保护单调计数器中的一个处于工作状态,例如,该片选信号/cs为高电位时,存储芯片处于工作状态,应答保护单调计数器处于非工作状态;反之,该片选信号/cs为低电位时,存储芯片处于非工作状态,应答保护单调计数器处于工作状态。

52.在其中一个实施例中,封装芯片100还包括第五抗静电干扰电路,第五抗静电干扰电路可以但不限于直接电性连接于第五主焊盘pc5、第五辅焊盘pb5中的任一个;第五抗静电干扰电路也可以直接电性连接于第五辅焊盘pb5与第五主焊盘pc5之间的任一处;优选的,第五抗静电干扰电路可以位于第五主焊盘pc5和第五控制电路cc5之间,这样可以有效保护整个相关通路免受外部静电的影响。

53.在其中一个实施例中,第一裸片10还包括第六主焊盘pc6,第二裸片20还包括第六子焊盘pa6,第六封装引脚pin6与第六主焊盘pc6和第六子焊盘pa6电性连接。

54.在其中一个实施例中,该封装芯片100还包括第六控制电路和第七控制电路,第六控制电路与第六主焊盘pc6电性连接,第七控制电路与第六子焊盘pa6电性连接。

55.在其中一个实施例中,封装芯片100还包括第六抗静电干扰电路和第七抗静电干扰电路,第六抗静电干扰电路电性连接于第六主焊盘pc6,第七抗静电干扰电路电性连接于第六子焊盘pa6。

56.在其中一个实施例中,第六封装引脚pin6与第六主焊盘pc6电性连接,第六抗静电干扰电路与第六主焊盘pc6电性连接。第六主焊盘pc6与第六子焊盘pa6电性连接,第七抗静电干扰电路与第六子焊盘pa6电性连接。

57.在其中一个实施例中,第一裸片10还包括第七主焊盘pc7,第七封装引脚pin7与第七主焊盘pc7电性连接。

58.在其中一个实施例中,该封装芯片100还包括第八控制电路,第八控制电路与第七主焊盘pc7电性连接。

59.在其中一个实施例中,封装芯片100还包括第八抗静电干扰电路,第八抗静电干扰电路电性连接于第七主焊盘pc7。

60.在其中一个实施例中,第一裸片10还包括第八主焊盘pc8,第八封装引脚pin8与第八主焊盘pc8电性连接。

61.在其中一个实施例中,该封装芯片100还包括第九控制电路,第九控制电路与第八主焊盘pc8电性连接。

62.在其中一个实施例中,封装芯片100还包括第九抗静电干扰电路,第九抗静电干扰电路电性连接于第八主焊盘pc8。

63.在其中一个实施例中,第一子焊盘pa1至第一封装引脚pin1的外接端的距离大于第一辅焊盘pb1至第一封装引脚pin1的外接端的距离,且第一辅焊盘pb1至第一封装引脚pin1的外接端的距离大于第一主焊盘pc1至第一封装引脚pin1的外接端的距离。

64.可以理解的是,本实施例可以以最短距离实现第一子焊盘pa1、第一辅焊盘pb1、第一控制电路cc1、第一主焊盘pc1以及第一封装引脚pin1的依次电性连接,可以降低封装的难度,避免集中过多的走线于一个焊盘或一个封装引脚,从而避免或降低了短路的风险。其中,第一封装引脚pin1的外接端可以为第一封装引脚pin1远离封装芯片100的一端。

65.在其中一个实施例中,第二子焊盘pa2至第二封装引脚pin2的距离大于第二辅焊盘pb2至第二封装引脚pin2的距离,且第二辅焊盘pb2至第二封装引脚pin2的距离大于第二主焊盘pc2至第二封装引脚pin2的距离。

66.可以理解的是,本实施例可以以最短距离实现第二子焊盘pa2、第二辅焊盘pb2、第二控制电路cc2、第二主焊盘pc2以及第二封装引脚pin2的依次电性连接,可以降低封装的难度,避免集中过多的走线于一个焊盘或一个封装引脚,从而避免或降低了短路的风险。

67.在其中一个实施例中,第三子焊盘pa3至第三封装引脚pin3的距离大于第三辅焊盘pb3至第三封装引脚pin3的距离,且第三辅焊盘pb3至第三封装引脚pin3的距离大于第三主焊盘pc3至第三封装引脚pin3的距离。

68.可以理解的是,本实施例可以以最短距离实现第三子焊盘pa3、第三辅焊盘pb3、第三控制电路cc3、第三主焊盘pc3以及第三封装引脚pin3的依次电性连接,可以降低封装的难度,避免集中过多的走线于一个焊盘或一个封装引脚,从而避免或降低了短路的风险。

69.在其中一个实施例中,第四子焊盘pa4至第四封装引脚pin4的距离大于第四辅焊盘pb4至第四封装引脚pin4的距离,且第四辅焊盘pb4至第四封装引脚pin4的距离大于第四主焊盘pc4至第四封装引脚pin4的距离。

70.可以理解的是,本实施例可以以最短距离实现第四子焊盘pa4、第四辅焊盘pb4、第四控制电路cc4、第四主焊盘pc4以及第四封装引脚pin4的依次电性连接,可以降低封装的难度,避免集中过多的走线于一个焊盘或一个封装引脚,从而避免或降低了短路的风险。

71.在其中一个实施例中,第五子焊盘pa5至第五封装引脚pin5的距离大于第五辅焊盘pb5至第五封装引脚pin5的距离,且第五辅焊盘pb5至第五封装引脚pin5的距离大于第五主焊盘pc5至第五封装引脚pin5的距离。

72.可以理解的是,本实施例可以以最短距离实现第五子焊盘pa5、第五辅焊盘pb5、第五控制电路cc5、第五主焊盘pc5以及第五封装引脚pin5的依次电性连接,可以降低封装的难度,避免集中过多的走线于一个焊盘或一个封装引脚,从而避免或降低了短路的风险。

73.如图4所示,在其中一个实施例中,第一裸片10为存储芯片,第二裸片20为应答保护单调计数器。

74.需要进行说明的是,存储芯片可以但不限于为闪存芯片,也可以为nor flash。

75.在其中一个实施例中,存储芯片用于根据接入的外部输入数据生成对应的第一内

部输出数据,且转存外部输入数据至应答保护单调计数器;应答保护单调计数器与存储芯片通信连接,用于根据外部输入数据生成对应的第二内部输出数据,且转存第二内部输出数据至存储芯片;其中,存储芯片还用于输出第一内部输出数据和第二内部输出数据。

76.可以理解的是,在本实施例中,应答保护单调计数器的输入输出数据总是通过存储芯片转存后输入或者输出,而不直接与封装芯片100的外部进行交互,对于应答保护单调计数器与存储芯片的共用封装引脚中的任一个,同样可以仅设置一个抗静电干扰电路,进而减小封装芯片100的面积或者体积。

77.需要进行说明的是,外部输入数据可以为指令信号、地址信号、片选信号/cs、时钟信号clk以及数据信号中的至少一个。

78.需要进行说明的是,存储芯片和应答保护单调计数器的存储容量可以自行选择,例如,8m、16m、32m、64m、128m、256m或者更高,存储芯片和应答保护单调计数器的数量也可为多个,以实现对存储芯片和应答保护单调计数器的存储容量的进一步扩展,其中每个应答保护单调计数器均通过至少一个存储芯片接收外部输入数据以及输出对应的第二内部输出数据。

79.如图4所示,在其中一个实施例中,存储芯片包括第一输入控制器101、第一输入缓冲器102、第一输出缓冲器104以及第一输出控制器103,第一输入控制器101用于接入外部输入数据;第一输入缓冲器102与第一输入控制器101和应答保护单调计数器连接,用于在第一输入控制器101的控制下,缓存外部输入数据,并转存外部输入数据至应答保护单调计数器;第一输出缓冲器104与应答保护单调计数器连接,用于缓存第一内部输出数据和第二内部输出数据;第一输出控制器103与第一输出缓冲器104连接,用于输出第一内部输出数据、第二内部输出数据至存储芯片的外部。

80.在其中一个实施例中,应答保护单调计数器包括第二输入控制器201、第二输入缓冲器202、缓冲控制器205、第二输出缓冲器203以及第二输出控制器204,第二输入控制器201与第一输入缓冲器102连接,用于接入外部输入数据;第二输入缓冲器202与第二输入控制器201连接,用于在第二输入控制器201的控制下缓存外部输入数据;缓冲控制器205与第二输入缓冲器202连接,用于根据外部输入数据生成第二内部输出数据;第二输出缓冲器203与缓冲控制器205连接,用于缓存第二内部输出数据;第二输出控制器204与第二输出缓冲器203和第一输出缓冲器104连接,用于输出第二内部输出数据至第一输出缓冲器104。

81.可以理解的是,本实施例可以简化应答保护单调计数器的构造,进一步缩小应答保护单调计数器的面积或者体积。

82.需要说明的是,第一输入控制器101和第二输入控制器201中分别集成有用于解码外部输入数据的指令译码器,第一输入控制器101的指令译码器解码并传输外部输入数据至第一输入缓冲器102中,第二输入控制器201的指令译码器解码并传输外部输入数据至第二输入缓冲器202中。

83.在其中一个实施例中,存储芯片还包括状态寄存器105,与第一输出控制器103和第二输出控制器204连接,用于寄存应答保护单调计数器的工作状态数据。该工作状态数据可以通过第一输出控制器103输出至封装芯片100的外部,以便于外部实时监控应答保护单调计数器的工作状态。

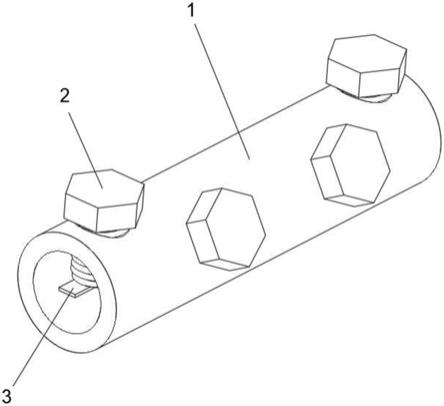

84.在其中一个实施例中,存储芯片叠加放置于应答保护单调计数器之上,或者应答

保护单调计数器叠加放置于存储芯片之上。可以理解的是,两者叠加放置可以较小两者封装后的总面积,可以适用于安装在空间面积较小的环境。

85.在其中一个实施例中,存储芯片的面积大于应答保护单调计数器的面积,且应答保护单调计数器叠加放置于存储芯片之上。可以理解的是,本实施例可以简化应答保护单调计数器的构造。

86.如图5所示,在其中一个实施例中,封装芯片100中的第一封装引脚pin1、第二封装引脚pin2、第四封装引脚pin4以及第五封装引脚pin5可以构成第一串行外设接口30,第一串行外设接口30用于封装芯片100接入外部输入数据,以及封装芯片100输出第一内部输出数据和第二内部输出数据。封装芯片100中的第一子焊盘pa1、第一辅焊盘pb1、第二子焊盘pa2、第二辅焊盘pb2、第四子焊盘pa4、第四辅焊盘pb4、第五子焊盘pa5以及第五辅焊盘pb5可以构成第二串行外设接口40,第二串行外设接口40用于通信连接存储芯片与应答保护单调计数器。

87.需要进行说明的是,第一串行外设接口30、第二串行外设接口40均可以为串行外设接口(spi,serial peripheral interface),第一串行外设接口30、第二串行外设接口40均包括用于传输片选信号/cs的总线、用于传输时钟信号clk的总线、用于传输输入信号di的总线以及用于传输输出信号do的总线。spi接口是一种高速的、全双工、同步的通信总线。

88.在上述实施例中,对各个实施例的描述都各有侧重,某个实施例中没有详述的部分,可以参见其他实施例的相关描述。

89.以上对本技术实施例所提供的封装芯片100进行了详细介绍,本文中应用了具体个例对本技术的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本技术的技术方案及其核心思想;本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本技术各实施例的技术方案的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。