1.本发明的实施例涉及一种触发器电路。

背景技术:

2.触发器电路用于存储数据。通过控制触发器的功率、性能和制造区域特性(例如,通过限制用于实现触发器的组件的数量),可以使用较少的电路制造空间来实现更快、功率效率更高的触发器。

技术实现要素:

3.根据本发明实施例的一个方面,提供了一种触发器电路,包括:第一主部分,被配置为在第一模式下操作以及接收第一输入并生成第一主输出;第二主部分,被配置为在第二模式下操作以及接收第二输入并生成第二主输出;至少一个判定部分,被配置为接收至少一个使能信号,并且具有判定输入和判定输出,判定输入连接至第一主输出和第二主输出,判定部分被配置为根据至少一个使能信号判定判定输出为第一主输出或第二主输出;以及从部分,被配置为接收判定输出并生成输出信号。

4.根据本发明实施例的另一个方面,提供了一种触发器电路,包括:第一主部分,被配置为在第一模式下操作以及接收第一输入并生成第一主输出,第一主部分具有用于根据至少一个使能信号来使能第一主部分的第一使能部分;第二主部分,被配置为在第二模式下操作以及接收第二输入并生成第二主输出,第二主部分具有用于根据至少一个使能信号来使能第二主部分第二使能部分的第二使能部分;以及从部分,被配置为接收第一主输出或第二主输出并生成输出信号。

5.根据本发明实施例的又一个方面,提供了一种触发器电路,包括:主部分,被配置为接收至少一个第一输入、至少一个第二输入和至少一个使能信号,并生成主输出,主部分包括多个控制部分,多个控制部分被配置为根据至少一个第一输入、至少一个第二输入和至少一个使能信号控制主部分以第一模式或第二模式操作;以及从部分,被配置为接收主输出并生成输出信号。

附图说明

6.当结合附图进行阅读时,从以下详细描述可最佳理解本发明的各个方面。应该强调,根据工业中的标准实践,各个部件未按比例绘制并且仅用于说明的目的。实际上,为了清楚的讨论,各个部件的尺寸可以任意地增大或减小。

7.图1示出了根据本公开的一些实施例的触发器电路的门级电路图。

8.图2示出根据本公开的一些实施例的或与反相器(oai)逻辑门和与或反相器(aoi)逻辑门的示例性电路图以及相应的真值表。

9.图3示出了根据本公开的一些实施例的触发器电路的晶体管级电路图。

10.图4示出了根据本公开的一些实施例的触发器电路的晶体管级电路图。

11.图5示出了根据本公开的一些实施例的触发器电路的晶体管级电路图。

12.图6示出了根据本公开的一些实施例的触发器电路的晶体管级电路图。

13.图7示出了根据本公开的一些实施例的触发器电路的晶体管级电路图。

14.图8示出了根据本公开的一些实施例的触发器电路的晶体管级电路图。

15.图9示出了根据本公开的一些实施例的触发器电路的晶体管级电路图。

16.图10示出了根据本公开的一些实施例的触发器电路的晶体管级电路图。

17.图11示出了根据本公开的一些实施例的触发器电路的晶体管级电路图。

18.图12示出了根据本公开的一些实施例的触发器电路的晶体管级电路图。

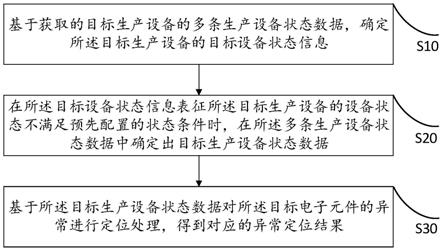

19.图13是示出根据本公开的一些实施例的用于操作触发器电路的方法的流程图。

20.图14是示出根据本公开的一些实施例的用于操作触发器电路的方法的流程图。

21.图15是示出根据本公开的一些实施例的用于操作触发器电路的方法的流程图。

具体实施方式

22.以下公开内容提供了许多用于实现本发明的不同特征不同的实施例或实例。下面描述了组件和布置的具体实施例或实例以简化本发明。当然,这些仅是实例而不旨在限制。例如,在以下描述中,在第二部件上方或者上形成第一部件可以包括第一部件和第二部件直接接触形成的实施例,并且也可以包括在第一部件和第二部件之间可以形成额外的部件,从而使得第一部件和第二部件可以不直接接触的实施例。此外,本公开可以在各个示例中重复参考数字和/或字母。该重复是为了简单和清楚的目的,并且其本身不指示讨论的各个实施例和/或配置之间的关系。

23.此外,为了便于描述,本文中可以使用诸如“在

…

下方”、“在

…

下面”、“下部”、“在

…

上面”、“上部”等的间隔关系术语,以描述如图中所示的一个元件或部件与另一元件或部件的关系。除了图中所示的方位外,间隔关系术语旨在包括器件在使用或操作工艺中的不同方位。器件可以以其它方式定位(旋转90度或在其它方位),并且在本文中使用的间隔关系描述符可以同样地作相应地解释。

24.尽管阐述本发明的广泛范围的数值范围和参数是近似值,但是在具体示例中阐述的数值被尽可能精确地报告。但是,任何数值都固有地包含某些误差,这些误差必定是由各个测试测量中的标准偏差引起的。同样,如本文所用,术语“约”通常是指在给定值或范围的10%、5%、1%或0.5%之内。可选地,术语“约”是指当由本领域的普通技术人员考虑时在平均值的可接受的标准误差内。除了在操作/工作示例中,或者除非另有明确说明,否则所有数值范围、数量、值和百分比,例如材料数量、持续时间、温度、操作条件、数量比等的数值范围,数量、值和百分比本文所公开的术语“在任何情况下都应理解为被术语“约”修饰。因此,除非有相反的指示,否则本公开和所附权利要求书中阐述的数值参数是可以根据需要变化的近似值。至少,每个数字参数至少应根据报告的有效数字的数量并通过应用普通的舍入技术来解释。范围可以在本文中表示为从一个端点到另一端点或在两个端点之间。除非另有说明,否则本文公开的所有范围均包括端点。

25.触发器电路实现可以使用来自扫描多路复用器的一个或多个信号反相,该扫描信号多路复用用于选择扫描输入和数据输入。扫描多路复用器的这种反转需要花费时间和精力来完成,而用于实现这些反转的组件和用于实现触发器的传输门则需要电路面积。限制

电路组件可以提高电路功率、性能和面积特性。根据本公开的一些实施例,触发器电路可以通过替换或合并扫描多路复用器来减少信号路径上的信号反相,以使触发器电路的速度更快并且降低功耗和设计复杂度。

26.图1示出了根据本公开的一些实施例的触发器电路的门级电路图。参照图1,触发器电路10包括第一主部分11、第二主部分12、至少一个判定部分13、14和从部分15。第一主部分11被配置为以第一模式操作并接收第一输入111,并生成第一主输出112。第二主部分12被配置为在第二模式下操作并接收第二输入121,并生成第二主输出122。根据本公开的一些实施例,第一模式可以是测试模式,第二模式可以是普通模式。第一输入111可以是扫描信号(si),第二输入121可以是数据信号(d)。

27.根据本公开的一些实施例,当第一主部分11在测试模式下操作时,第一主部分11接收扫描输入信号111并生成第一主输出112(扫描输出信号)。在一些实施例中,可通过比较扫描输入信号111和扫描输出信号112之间的一个或多个差异来检测一个或多个触发器电路(即,一个或多个故障触发器电路)的故障。这样的故障触发器电路可用于查明逻辑门的哪个相应子集正在故障。根据本公开的一些实施例,扫描进入信号111可以用于提供上述扫描测试。在一些实施例中,如上所述,扫描输入信号111可以包括一个或多个用于检测触发器电路的故障的测试图案。可以通过自动测试图案生成(atpg)技术来提供这种扫描输入信号111。

28.根据本公开的一些实施例,当第二主部分12在普通模式下操作时,第二主部分12接收从待测试电路的逻辑门的相应子集提供的数据信号121。根据本公开的一些实施例,数据信号121可以包括基于逻辑门的相应子集的逻辑操作生成的数据。

29.根据本公开的一些实施例,第一主部分11包括第一交叉耦合的或与反相器(oai)逻辑门对113和第一主反相器114,以及第二主部分12包括第二交叉耦合的或与反相器(oai)逻辑门对123和第二主反相器124,从部分15包括交叉耦合的与或反相器(aoi)逻辑门对153和从反相器154。这里使用的术语“交叉耦合”是指第一对交叉耦合的或与反相器(oai)逻辑门113中的两个oai各自包括耦合到另一个的输入的输出。类似地,第二交叉耦合的或与反相器(oai)逻辑门对123中的两个oai各自包括耦合至另一方输入的输出,以及交叉耦合的或与反相器(aoi)逻辑门对153均包括耦合至另一输入的输出。

30.根据本公开的一些实施例,第一交叉耦合的或与反相器(oai)逻辑门对113耦合到第一输入(扫描输入信号)111、第一反相器114的输出和时钟信号cp。类似地,第二交叉耦合的或与反相器(oai)逻辑门对123耦合至第二输入(数据信号)121、第一反相器124的输出以及时钟信号cp。第一交叉耦合的或反相器(oai)逻辑门对113和第二交叉耦合的或反相器(oai)逻辑门对123被配置为执行“oai”逻辑功能。交叉耦合的与或反相器(aoi)逻辑门对153耦合到从输入151和时钟信号cp。交叉耦合的与或反相器(aoi)逻辑门对153被配置为执行aoi逻辑功能。

31.图2示出了根据本公开的一些实施例的或与反相器(oai)逻辑门和与或反相器(aoi)逻辑门的示例性电路图以及相应的真值表。在图2中,示出了oai和aoi以及它们各自的真值表(oai真值表和aoi真值表)。根据本公开的一些实施例,第一交叉耦合的或与反相器(oai)逻辑门对113中的两个oai各自具有与图2中的oai基本上类似的功能。如图2所示,第二交叉耦合的或与反相器(oai)逻辑门对123中的两个oai分别具有与图2中的oai基本上

类似的功能。因此,每个oai可以使用如图2所示的对应的真值表(即,“oai真值表”)执行上述oai逻辑功能。类似地,交叉耦合的与或反相器(aoi)逻辑门对153中的每个aoi具有与图2中的aoi基本上类似的功能。因此,每个aoi可以使用如图2所示的真值表(即,“aoi真值表”)执行上述aoi逻辑功能。

32.根据本公开的一些实施例,参考图1和图2,第一交叉耦合的或与反相器(oai)逻辑门对中的一个oai可以将第一输入(扫描信号)111用作a

11

,将时钟信号cp用作a

12

,并且其中一个主输出112作为b

11

,另一个第一主输出112作为输出c

11

,其中另一个第一主输出112的逻辑状态由oai真值表以及信号111、cp和112的逻辑状态的组合判定。例如,根据oai真值表,当信号111、cp和112的逻辑状态分别为逻辑“1”、逻辑“0”和逻辑“1”时,另一个主输出112为逻辑“0”。第二交叉耦合的“与与反相器”(oai)逻辑门对123中的一个oai可以将第二输入(数据信号)121用作a

11

,将时钟信号cp用作a

12

,并将第二主输出122中的一个用作b

11

,另一个第二主输出122作为输出c

11

,其中另一个第二主输出122的逻辑状态由oai真值表以及信号121、cp和122的逻辑状态的组合判定。交叉耦合的与或反相器”(aoi)逻辑门对153的aoi可以使用一个从输入151作为a

21

,使用时钟信号cp作为a

22

,使用一个从输出155作为b

21

,另一个使用从输出155作为输出c

21

,其中另一个从输出155的逻辑状态由aoi真值表以及信号151、cp和155的逻辑状态的组合判定。

33.根据本公开的一些实施例,至少一个判定部分13、14被配置为接收至少一个使能信号se/seb,并且具有判定输入和判定输出。判定输入连接到第一主输出和第二主输出。至少一个判定部分被配置为根据至少一个使能信号se/seb判定判定输出是第一主输出还是第二主输出。

34.根据本公开的一些实施例,触发器电路10包括第一判定部分13和第二判定部分14。第一判定部分13具有第一判定输入131和第一判定输出132。第一判定输入131连接到第一主输出112。第一判定输出132连接到判定输出eo。第二判定部分14具有第二判定输入141和第二判定输出142。第二判定输入141连接到第二主输出122。第二判定输出142连接到判定输出eo。

35.根据本公开的一些实施例,至少一个使能信号包括扫描使能信号(se)和反相扫描使能信号(seb)。

36.根据本公开的一些实施例,第一判定部分13包括由扫描使能信号(se)和反相扫描使能信号(seb)控制的多个晶体管。第二判定部分14包括由扫描使能信号(se)和反相扫描使能信号(seb)控制的多个晶体管。因此,第一判定部分13和第二判定部分14被配置为根据扫描使能信号(se)和反相扫描使能信号(seb)判定作为第一主输出112或第二主输出122的判定输出eo。例如,当扫描使能信号(se)被断言为逻辑高状态(例如,逻辑“1”)时,第一判定部分13可以将第一主输出112耦合到第一判定输出132。第二判定部分14被去激活。因此,判定输出eo是第一主输出112。当扫描使能信号(se)被断言为逻辑低状态(例如,逻辑“0”)时,第二判定部分14可以耦合第二主输出122到第二判定输出142。第一判定部分13被去激活。因此,判定输出eo是第二主输出122。

37.根据本公开的一些实施例,判定输出eo连接到从部分15的从输入151。从部分15被配置为基于从输入151和时钟信号cp生成输出信号152。

38.根据本公开的一些实施例,第一交叉耦合的或与反相器(oai)逻辑门对113和第二

交叉耦合的或与反相器(oai)的oai逻辑门对123和交叉耦合的与或反相器(aoi)逻辑门对153的aoi可以根据时钟信号cp互补地被激活。当时钟信号cp从低逻辑状态转变为高逻辑状态(即,时钟信号cp处于高逻辑状态)时,第一交叉耦合的或与反相器(oai)逻辑门对113和第二交叉耦合的或与反相器(oai)逻辑门对123被激活,而交叉耦合的或与反相器(aoi)逻辑门对153被去激活。这样,第一主部分11可以将第一输入(扫描信号)111锁存到输出信号152,或者第二主部分12可以将第二输入(数据信号)121锁存到输出信号152。交叉耦合的和或反相器(aoi)逻辑门对153可以用作透明电路。当时钟信号cp从高逻辑状态转变为低逻辑状态(即,时钟信号cp处于低逻辑状态)时,第一交叉耦合的或与反相器(oai)逻辑门对113和第二交叉耦合的或与反相器(oai)逻辑门对123被去激活,另一方面,交叉耦合的或与反相器(aoi)逻辑门对153被激活。这样,从部分15可以将第一输入(扫描信号)111或第二输入(数据信号)121直接锁存到输出信号152,而第一主部分11和第二主部分12可以用作透明电路。

39.根据本公开的一些实施例,通过在触发器电路10中使用第一交叉耦合的或与反相器(oai)逻辑门对113、第二交叉耦合的或与反相器(oai)逻辑门对123和交叉耦合的与或反相器(aoi)逻辑门对153,触发器电路10的时钟信号cp可以被第一交耦合的或与反相器(oai)逻辑门对113、第二交叉耦合的或与反相器(oai)逻辑门对123和交叉耦合的或与反相器(aoi)逻辑门对153共同使用。这样,可能不需要逻辑反相时钟信号和用于生成这种逻辑反相时钟信号的相应组件(例如,一个或多个反相器),这可以有利地降低功耗和触发器电路10的设计复杂度。此外,如图1所示,第一交叉耦合的或与反相器(oai)逻辑门对113中的两个oai彼此对称,第二交叉耦合的或与反相器(oai)逻辑门对123中的两个oai也彼此对称,并且交叉耦合的与或反相器(aoi)逻辑门对153中的两个aoi也彼此对称。通过分别使用触发器电路10的交叉耦合的oai和aoi的这种对称特性,与传统使用传输门的触发器电路相比,可以分别大大减少用于分别实现oai和aoi的晶体管的数量。晶体管数量的减少可进一步降低触发器电路10的功耗和设计复杂度。

40.根据本公开的一些实施例,通过使用第一判定部分13和第二判定部分14,可以判定来自第一主部分11的第一主输出112或来自第二主部分12的第二主输出122。因此,可能不需要设置在常规主锁存电路之前的常规多路复用器,这可以有利地使触发器电路10的速度更快(例如大约7%)。

41.图3示出了根据本公开的一些实施例的触发器电路的晶体管级电路图。参照图3,触发器电路20包括第一主部分21、第二主部分22、第一判定部分23、第二判定部分24和从部分25。第一主部分21被配置为以第一模式操作并接收第一输入211,并生成第一主输出212。第二主部分22被配置为在第二模式下操作并接收第二输入221,并生成第二主输出222。第一模式可以是测试模式,第二模式可以是普通模式。第一输入211可以是扫描信号(si),第二输入221可以是数据信号(d)。参考图1和图3,图1中的触发器电路10的每个门级组件(11、12和15)都被配置为与图3中的每个门级组件(11、12和15)相对应。可以通过图3中的一个或多个晶体管来实现图1的实施例。可以理解,图3所示的电路图仅是实现触发器电路10的门级组件的示例。可以通过多种电路设计中的任一个来实现触发器电路10的每个门级组件,而这仍在本发明的范围之内。

42.根据本公开的一些实施例,第一主部分21包括第一交叉耦合的或与反相器(oai)

逻辑门对213和第一主反相器214,以及第二主部分22包括第二交叉耦合的或与反相器(oai)逻辑门对223和第二主反相器224,从部分25包括交叉耦合的与或反相器(aoi)逻辑门对253和从反相器254。第一交叉耦合的或与反相器(oai)逻辑门对213可以由多个晶体管实现以执行“oai”逻辑功能,第一主反相器214可以由两个从晶体管254实现以执行“反相器”逻辑功能。例如,第一主反相器214的两个晶体管串联连接在第一电源电压(例如,vdd)和第二电源电压(例如,地)之间。在一些实施例中,两个晶体管中的一个包括p型金属氧化物半导体(pmos)晶体管,而另一个晶体管包括n型金属氧化物半导体(nmos)晶体管。此外,晶体管的栅极共同耦合到第一输入211(扫描信号si),并且耦合到晶体管的相应漏极的共同节点被配置成提供与第一输入211逻辑上反相的信号。

43.根据本公开的一些实施例,类似地,第二交叉耦合的或与反相器(oai)逻辑门对223可以由多个晶体管实现以执行“oai”逻辑功能,第二主反相器224可以由两个晶体管实现以执行“反相器”逻辑功能。此外,交叉耦合的与或反相器(aoi)逻辑门对253可以由多个晶体管实现以执行“aoi”逻辑功能,从反相器254可以由两个晶体管实现以执行“反相器”逻辑功能。

44.根据本公开的一些实施例,第一判定部分23具有第一判定输入231和第一判定输出232。第一判定输入231连接到第一主输出212。第一判定输出232连接到判定输出eo。第二判定部分24具有第二判定输入241和第二判定输出242。第二判定输入241连接到第二主输出222。第二判定输出242连接到判定输出eo。

45.根据本公开的一些实施例,第一判定部分23包括由扫描使能信号(se)和反相扫描使能信号(seb)控制的多个晶体管。第二判定部分24包括由扫描使能信号(se)和反相扫描使能信号(seb)控制的多个晶体管。因此,第一判定部分23和第二判定部分24被配置为根据扫描使能信号(se)和反相扫描使能信号(seb)判定判定输出eo为第一主输出212或第二主输出222的。例如,当扫描使能信号(se)被断言为逻辑高状态(例如,逻辑“1”)时,第一判定部分23可以将第一主输出212耦合到第一判定输出232。因此,判定输出eo是第一主输出212。当扫描使能信号(se)被断言为逻辑低状态(例如,逻辑“0”)时,第二判定部分24可以将第二主输出222耦合到第二判定输出242。因此,判定输出eo是第二主输出222。

46.根据本公开的一些实施例,判定输出eo被连接到从部分25的从输入251。从部分25被配置为基于从输入251和时钟信号cp来生成输出信号252。

47.根据本公开的一些实施例,通过使用第一判定部分23和第二判定部分24,可以判定来自第一主部分21的第一主输出212或来自第二主部分22的第二主输出222。因此,可能不需要设置在常规主锁存电路之前的常规多路复用器,这可以有利地使触发器电路20的速度更快,例如大约7%。

48.注意,本文描述的上述结构和其他结构是示例性的,并且本公开的范围包括其他示例。例如,可以如在213、223处所描述的那样来实现或与反相器(oai)逻辑门,或者可以使用诸如在题为“低功率触发器电路”的美国专利申请第15/485,595号或名称为“基于低功率aoi的触发器”的美国专利申请第16/870,001号中描述的其他结构来实现,在此通过引用将其全部内容并入。与或反相器(aoi)逻辑门可以类似地如本文中所描绘的或在上述申请中所描述的那样实现。

49.例如在美国专利申请第15/485,595号中,公开一种被配置成将输入信号锁存至输

出信号的触发器电路。所述电路包括:第一锁存电路;以及第二锁存电路,耦合至所述第一锁存电路。在某些实施例中,响应于时钟信号,所述第一锁存电路与所述第二锁存电路被互补地激活以将所述输入信号锁存至所述输出信号,且所述第一锁存电路及所述第二锁存电路分别包括至多两个被配置成接收所述时钟信号的晶体管。所述第一锁存电路包括一对交叉耦合的与

‑

或

‑

反相器(aoi)逻辑门,且所述第二锁存电路包括一对交叉耦合的或

‑

与

‑

反相器(oai)逻辑门。

50.例如在美国专利申请第16/870,001号中,公开一种使用与或非(aoi)门及或与非(oai)门的触发器电路,所述电路包括:多路复用器单元,具有在第一信号与第二信号之间进行选择的多路复用器;主单元,具有两个或与非(oai)门,其中所述两个或与非(oai)门中的第一或与非门耦合在第一节点(n1)与第三节点(n3)之间,所述两个或与非(oai)门中的第二或与非门耦合在第二节点(n2)与第四节点(n4)之间;从单元,具有两个与或非(aoi)门,其中所述两个与或非(aoi)门中的第一与或非门耦合在所述第三节点(n3)与第五节点(n5)之间,所述两个与或非(aoi)门中的第二与或非门耦合在所述第四节点(n4)与第六节点(n6)之间;以及时钟,用于控制所述两个与或非门及所述两个或与非门,其中所述时钟连接到所述第一与或非门及所述第二与或非门以及所述第一或与非门及所述第二或与非门。

51.图4示出了根据本公开的一些实施例的触发器电路的晶体管级电路图。参照图4,触发器电路30包括第一主部分31、第二主部分32、第一判定部分33、第二判定部分34和从部分35。第一主部分31被配置为以第一模式操作并接收第一输入311,并生成第一主输出312。第二主部分32被配置为在第二模式下操作并接收第二输入321,并生成第二主输出322。第一模式可以是测试模式,第二模式可以是普通模式。第一输入311可以是扫描信号(si),第二输入321可以是数据信号(d)。

52.根据本公开的一些实施例,第一主部分31包括第一交叉耦合的与或反相器(aoi)逻辑门对313和第一主反相器314,以及第二主部分32包括第二交叉耦合的与或反相器(aoi)逻辑门对323和第二主反相器324,并且从部分35包括交叉耦合的或与反相器(oai)逻辑门对353和第二对主反相器。第一交叉耦合的与或反相器(aoi)逻辑门对313可以由多个晶体管实现以执行“aoi”逻辑功能,第一主反相器314可以由多个从晶体管354实现以执行“反相器”逻辑功能。类似地,第二交叉耦合的与或反相器(aoi)逻辑门对323可以由多个晶体管实现以执行“aoi”逻辑功能,第二主反相器324可以由两个晶体管实现以执行“反相器”逻辑功能。此外,交叉耦合的或与反相器(oai)逻辑门对353可以由多个晶体管实现以执行“oai”逻辑功能,从反相器354可以由两个晶体管实现以执行“反相器”逻辑功能。

53.根据本公开的一些实施例,参考图3和图4,触发器电路30与触发器电路20基本上类似,不同之处在于触发器电路30的第一主部分31包括第一交叉耦合的与或反相器(aoi)逻辑门对313,触发器电路30的第二主部分32包括第二交叉耦合的与或反相器(aoi)逻辑门对314,并且触发器电路30的从部分35包括交叉耦合的或与反相器(oai)逻辑门对353。换句话说,图4中的交叉耦合的或与反相器(oai)逻辑门对353可以基本上类似于图3中的第一交叉耦合的或与反相器(oai)逻辑门对213或第二交叉耦合的或与反相器(oai)逻辑门对223。因此,为了清楚起见,省略了对第一主部分31、第二主部分32和从部分35的讨论。通过将aoi布置到第一主部分31和第二主部分32以及将oai布置到从部分35(即,交换aoi和oai),可以将一个或多个附加时钟缓冲器电路集成到触发器电路中。从而减少了对时钟电路30的负

担,从而减少了对时钟电路(即提供时钟信号cp的电路)的负担。

54.根据本公开的一些实施例,为了通过aoi实现第一主部分31和第二主部分32,并且通过oai实现从部分35,触发器电路30还包括反相器36,其被配置为接收时钟信号cp并且将逻辑反相的信号分别提供给第一主部分31和第二主部分32以及从部分35。

55.根据本公开的一些实施例,第一判定部分33具有第一判定输入331和第一判定输出332。第一判定输入331连接到第一主输出312。第一判定输出332连接到判定输出eo。第二判定部分34具有第二判定输入341和第二判定输出342。第二判定输入341连接到第二主输出322。第二判定输出342连接到判定输出eo。

56.根据本公开的一些实施例,第一判定部分33包括由扫描使能信号(se)和反相扫描使能信号(seb)控制的多个晶体管。第二判定部分34包括由扫描使能信号(se)和反相扫描使能信号(seb)控制的多个晶体管。因此,第一判定部分33和第二判定部分34被配置为根据扫描使能信号(se)和反相扫描使能信号(seb)判定判定输出eo为第一主输出312或第二主输出322。例如,当扫描使能信号(se)被断言为逻辑高状态(例如,逻辑“1”)时,第一判定部分33可以将第一主输出312耦合到第一判定输出332。因此,判定输出eo是第一主输出312。当扫描使能信号(se)被断言为逻辑低状态(例如,逻辑“0”)时,第二判定部分34可以将第二主输出322耦合到第二判定输出342。因此,判定输出eo是第二主输出322。

57.根据本公开的一些实施例,通过使用第一判定部分33和第二判定部分34,可以判定来自第一主部分31的第一主输出312或来自第二主部分32的第二主输出322。因此,可能不需要设置在常规主锁存电路之前的常规多路复用器,这可以有利地使触发器电路30的速度更快(例如大约7%)。

58.图5示出了根据本公开的一些实施例的触发器电路的晶体管级电路图。参考图。参照图3和图5所示,触发器电路20a与图1的触发器电路20基本上类似,除了触发器电路20a还包括时移电路26之外。时移部分26耦合到第一主部分21和第二主部分22,用于对第一主部分21和第二主部分22的时钟信号cp延迟预定时间,时钟信号cp连接到没有时移部分26的从部分25。为清楚起见,对触发器电路20a的组件的讨论基本上类似于触发器电路20(例如21、22和25)的那些,其被省略。

59.根据本公开的一些实施例,时移电路26包括彼此串联耦合的一个或多个反相器。尽管图5示出了时移电路26包括4个反相器,时移电路26中可以包括任何期望数量的反相器(例如2~8个),而这仍然在本公开的范围内。在触发器电路20a中包括这样的时移电路26,可以通过与时移电路26中包括的反相器数量相对应的多个门延迟,来延迟要被第一主部分21和第二主部分22接收的时钟信号cp,而从部分25无延迟地接收时钟信号cp。根据本公开的一些实施例,延迟第一主部分21和第二主部分22的时钟信号cp可以有利地减少触发器电路20a的建立时间。由于时钟信号cp被延迟以被第一主部分21和第二主部分22接收,并且时钟信号cp被从部分25立即接收而没有延迟,因此在一些实施例中,从部分25可以提供透明窗口且较早释放数据,这导致第一主部分21和第二主部分22在当前周期中有更多时间接收输入数据,从而减少了建立时间。

60.根据本公开的一些实施例,时移电路26包括4个反相器,并且时移电路26的每个反相器基本上类似于反相器214、224和252。因此,将省略对时移电路26的反相器的讨论。这样,由第一主部分21和第二主部分22接收的延迟的时钟信号可以在时钟信号cp之后具有大

约四个门延迟。

61.图6示出了根据本公开的一些实施例的触发器电路的晶体管级电路图。参照图6,触发器电路40包括第一主部分41、第二主部分42和从部分43。第一主部分41被配置为在第一模式下操作并接收第一输入411,并生成第一主输出412。第二主部分42被配置为在第二模式下操作并接收第二输入421,并生成第二主输出422。根据本公开的一些实施例,第一模式可以是测试模式,并且第二模式可以是普通模式。第一输入411可以是扫描信号(si)、第二输入421可以是数据信号(d)。

62.根据本公开的一些实施例,当第一主部分41在测试模式下操作时,第一主部分41接收扫描输入信号411并生成第一主输出412(扫描输出信号)。在一些实施例中,可通过比较扫描输入信号411和扫描输出信号之间的一个或多个差异来检测一个或多个触发器电路(即,一个或多个故障触发器电路)的故障。这样的故障触发器电路可以用于查明逻辑门的哪个相应子集正在故障。根据本公开的一些实施例,第一主部分41具有第一使能部分413,用于根据至少一个使能信号来使能第一主部分41。至少一个使能信号包括扫描使能信号(se)和反相扫描使能信号(seb)。

63.根据本公开的一些实施例,当第二主部分42在普通模式下操作时,第二主部分42接收从待测试电路的逻辑门的相应子集提供的数据信号421。根据本公开的一些实施例,数据信号421可以包括基于逻辑门的相应子集的逻辑操作生成的数据。根据本公开的一些实施例,第二主部分42具有第二使能部分423,第二使能部分423用于根据至少一个使能信号使能第二主部分42。至少一个使能信号包括扫描使能信号(se)和反相扫描使能信号(seb)。

64.根据本公开的一些实施例,从部分43被配置为接收第一主输出412或第二主输出422并生成输出信号432。从部分43包括连接到第一主输出412的第一主输出412和第二主输出422。

65.根据本公开的一些实施例,第一主部分41包括第一交叉耦合的或与反相器(oai)逻辑门对414和第一主反相器415,以及第二主部分42包括第二交叉耦合的或与反相器(oai)逻辑门对424和第二主反相器425,从部分45包括交叉耦合的与或反相器(aoi)逻辑门对453和从反相器454。

66.根据本公开的一些实施例,第一使能部分413包括由扫描使能信号(se)和反相扫描使能信号(seb)控制的多个晶体管,以使能第一主部分41。第一使能部分413设置在第一主部分21中。第二使能部分423包括由扫描使能信号(se)和反相扫描使能信号(seb)控制的多个晶体管,以使能第二主部分42。第二使能部分423设置在第二主部分42中。因此,第一使能部分413和第二使能部分423被配置为根据扫描使能信号(se)和反相扫描使能信号(seb)判定从输入431是第一主输出112还是第二主输出122。例如,当扫描使能信号(se)被断言为逻辑高状态(例如,逻辑“1”)时,第一交叉耦合的或与反相器(oai)逻辑门对414被激活,并且第二交叉耦合的或与反相器(oai)逻辑门对424被停用。因此,从输入431是第一主输出412。当扫描使能信号(se)被断言为逻辑低状态(例如,逻辑“0”)时,第一交叉耦合的或与反相器(oai)逻辑门对414被去激活,并且第二交叉耦合的或与反相器(oai)逻辑门对424被激活。因此,从输入431是第二主输出422。

67.根据本公开的一些实施例,通过使用第一使能部分413和第二使能部分423,可以判定来自第一主部分41的第一主输出412或来自第二主部分42的第二主输出422,以发送到

从输入431。因此,可能不需要设置在常规主锁存电路之前的常规多路复用器,这可以有利地改善触发器电路40的性能。

68.图7示出了根据本公开的一些实施例的触发器电路的晶体管级电路图。参考图。参照图7,触发器电路50包括第一主部分51、第二主部分52和从部分53。第一主部分51被配置为在第一模式下操作并接收第一输入511,并生成第一主部分。第二主部分52被配置为在第二模式下操作并接收第二输入521,并生成第二主输出522。根据本公开的一些实施例,第一模式可以是测试模式,并且第二模式可以是普通模式。第一输入511可以是扫描信号(si),第二输入421可以是数据信号(d)。

69.根据本公开的一些实施例,第一主部分51包括第一交叉耦合的与或反相器(aoi)逻辑门对514和第一主反相器515,以及第二主部分52包括第二交叉耦合的与或反相器(aoi)逻辑门对524和第二主反相器525,而从部分53包括交叉耦合的或与反相器(oai)逻辑门对533和第二对。第一交叉耦合的与或反相器(aoi)逻辑门对514可以由多个晶体管实现以执行“aoi”逻辑功能,第一主反相器515可以由两个晶体管实现以执行“反相器”逻辑功能。类似地,第二交叉耦合的与或反相器(aoi)逻辑门对524可以由多个晶体管实现以执行“aoi”逻辑功能,第二主反相器525可以由两个晶体管实现以执行“反相器”逻辑功能。此外,交叉耦合的或与反相器(oai)逻辑门对533可以由多个晶体管实现以执行“oai”逻辑功能,从反相器534可以由两个晶体管实现以执行“反相器”逻辑功能。

70.根据本公开的一些实施例,参考图6和图7,触发器电路50与触发器电路40基本上类似,除了触发器电路50的第一主部分51包括第一交叉耦合的与或反相器(aoi)逻辑门对,触发器电路50的第二主部分52包括第二交叉耦合的与或反相器(aoi)逻辑门对524,并且触发器电路50的从部分53包括交叉耦合的或与反相器(oai)逻辑门对533。换句话说,图7中的交叉耦合的或与反相器(oai)逻辑门对533基本上类似于图6中的第一交叉耦合的或与反相器(oai)逻辑门对414或第二交叉耦合的或与反相器(oai)逻辑门对424。此外,图7中的第一交叉耦合的与或反相器(aoi)逻辑门对514或第二交叉耦合的与或反相器(aoi)逻辑门对524基本上类似于图6中的交叉耦合的与或反相器(aoi)逻辑门对433。因此,为了清楚起见,省略了对第一主部分51、第二主部分52和从部分55的讨论。通过对第一主部分51和第二主部分52设置aio以及对从部分53设置oai(即,交换aoi和oai),可以将一个或多个附加时钟缓冲器电路集成到触发器电路50中。从而减少了对时钟电路(即,提供时钟信号cp的电路)的负担。

71.根据本公开的一些实施例,为了通过aoi实现第一主部分51和第二主部分52,并且通过oai实现从部分53,触发器电路50还包括反相器54,反相器54被配置为接收时钟信号cp并且将逻辑反相的信号分别提供给第一主部分51和第二主部分52和从部分53。

72.根据本公开的一些实施例,第一主部分51具有第一使能部分513,用于根据至少一个使能信号来使能第一主部分51。根据本公开的一些实施例,第二主部分52具有第二使能部分523,用于根据至少一个使能信号使能第二主部分52。至少一个使能信号包括扫描使能信号(se)和反相扫描使能信号(seb)。

73.根据本公开的一些实施例,从部分53被配置为接收第一主输出512或第二主输出522,并生成输出信号532。从部分53包括连接到第一主输出512和第二主输出522的从输入531。

74.根据本公开的一些实施例,第一使能部分513包括由扫描使能信号(se)和反相扫描使能信号(seb)控制的多个晶体管以使能第一主部分51。第一使能部分513设置在第一主部分51中。第二使能部分523包括由扫描使能信号(se)和反相扫描使能信号(seb)控制的多个晶体管,以使能第二主部分52。第二使能部分523设置在第二主部分52中。因此,第一使能部分513和第二使能部分523被配置为根据扫描使能信号(se)和反相扫描使能信号(seb)判定从输入531是第一主输出512还是第二主输出522。例如,当扫描使能信号(se)被断言为逻辑高状态(例如,逻辑“1”)时,第一交叉耦合的或与反相器(oai)逻辑门对514被激活,并且第二交叉耦合的或与反相器(oai)逻辑门对524被去激活。因此,从输入431是第一主输出512。当扫描使能信号(se)被断言为逻辑低状态(例如,逻辑“0”)时,第一交叉耦合的或与反相器”(oai)逻辑门对514被去激活,并且第二交叉耦合的或与反相器(oai)逻辑门对524被激活。因此,从输入531是第二主输出522。

75.根据本公开的一些实施例,通过使用第一使能部分513和第二使能部分523,可以判定来自第一主部分51的第一主输出512或来自第二主部分52的第二主输出522以发送到从输入531。因此,可能不需要设置在常规主锁存电路之前的常规多路复用器,这可以有利地改善触发器电路50的性能。

76.图8示出了根据本公开的一些实施例的触发器电路的晶体管级电路图。参照图6和图8所示,触发器电路40a与图6的触发器电路40基本上类似,除了触发器电路40a还包括时移电路44。时移部分44耦合到第一主部分41和第二主部分42,用于将到第一主部分41和第二主部分42的时钟信号cp延迟预定时间。并且时钟信号cp连接到没有时移部分44的从部分43。为清楚起见,对触发器电路40a的组件的讨论基本上类似于触发器电路40(例如41、42和43)的那些,其被省略。

77.根据本公开的一些实施例,时移电路44包括彼此串联耦合的一个或多个反相器。尽管图8的实施例示出了时移电路44包括4个反相器,然而时移电路44中可以包括任何期望数量的反相器(例如2~8个),而这仍然在本公开的范围内。在触发器电路40a中包括这样的时移电路44,可以通过与时移电路44中包括的反相器数量相对应的多个门延迟,来延迟要被第一主部分41和第二主部分42接收的时钟信号cp,而从部分43无延迟地接收时钟信号cp。根据本公开的一些实施例,延迟到第一主部分41和第二主部分42的时钟信号cp可以有利地减少触发器电路40a的建立时间。由于时钟信号cp被延迟以被第一主部分41和第二主部分42接收,并且时钟信号cp被从部分43立即接收而没有延迟,因此在一些实施例中,从部分43可以提供透明窗口且较早释放数据,这导致第一主部分41和第二主部分42在当前周期中有更多时间接收输入数据,从而减少了建立时间。

78.根据本公开的一些实施例,时移电路44包括4个反相器,并且时移电路44的每个反相器基本上类似于反相器415、425和434。因此,将省略对时移电路44的反相器的讨论。这样,由第一主部分41和第二主部分42接收的延迟的时钟信号可以在时钟信号cp之后具有大约四个门延迟。

79.图9示出了根据本公开的一些实施例的触发器电路的晶体管级电路图。参照图9,触发器电路60包括主部分61和从部分62。主部分61被配置为接收至少一个第一输入、至少一个第二输入和至少一个使能信号并生成主输出615,主部分61包括多个控制部分611、612、613、614,多个控制部分611、612、613、614被配置为根据至少一个第一输入、至少一个

第二输入和至少一个使能信号来控制主部分61以第一模式或第二模式操作。根据本公开的一些实施例,第一模式可以是测试模式,并且第二模式可以是普通模式。至少一个第一输入包括扫描输入信号(si)和反相的扫描输入信号(sib),并且至少一个第二输入包括数据信号(d)和反相的数据信号(db)。至少一个使能信号包括扫描使能信号(se)和反相扫描使能信号(seb)。

80.根据本公开的一些实施例,从部分62被配置为接收主输出615并生成输出信号622。从部分62包括连接到主输出615的从输入621。

81.根据本公开的一些实施例,主部分61包括第一控制部分611,第二控制部分612、第三控制部分613和第四控制部分614。第一控制部分611包括由反相扫描输入信号(sib)、反相数据信号(db)、扫描使能信号(se)和反相扫描使能信号(seb)控制的多个晶体管。即,第一控制部611可以包括四个pmos晶体管,其栅极由反相扫描输入信号(sib)、反相数据信号(db)、扫描使能信号(se)和反相扫描使能信号(seb)控制。第二控制部分612包括由反相扫描输入信号(sib)、反相数据信号(db)、扫描使能信号(se)和反相扫描使能信号(seb)控制的多个晶体管。即,第二控制部分612可以包括四个nmos晶体管,其栅极由反相扫描输入信号(sib)、反相数据信号(db)、扫描使能信号(se)和反相扫描使能信号(seb)控制。第三控制部分613包括由扫描输入信号(si)、数据信号(d)、扫描使能信号(se)和反相扫描使能信号(seb)控制的多个晶体管。也就是说,第三控制部分613可以包括四个pmos晶体管,其栅极由扫描输入信号(si)、数据信号(d)、扫描使能信号(se)和反相扫描使能信号(seb)控制。第四控制部分614可以包括由扫描输入信号(si)、数据信号(d)、扫描使能信号(se)和反相扫描使能信号(seb)控制的多个晶体管。也就是说,第四控制部分614可以包括四个nmos晶体管,其栅极由扫描输入信号(si)、数据信号(d)、扫描使能信号(se)和反相扫描使能信号(seb)控制。

82.根据本公开的一些实施例,主部分61包括交叉耦合的或与反相器(oai)逻辑门对616,从部分62包括交叉耦合的与或反相器(aoi)逻辑门对623和从反相器624。交叉耦合的或与反相器(oai)逻辑门对616可以由多个晶体管实现以执行“oai”逻辑功能。此外,交叉耦合的与或反相器(aoi)逻辑门对623可以由多个晶体管实现以执行“aoi”逻辑功能,从反相器624可以由两个晶体管实现以执行“反相器”逻辑功能。

83.根据本公开的一些实施例,第一控制部分611、第二控制部分612、第三控制部分613和第四控制部分614可以判定主部分61以测试模式或普通模式操作。当主部分61在测试模式下操作时,扫描使能信号(se)被断言为逻辑高状态(例如,逻辑“1”),并且扫描输入信号(si)和反相扫描输入信号(sib)被输入到交叉耦合的或与反相器”(oai)逻辑门对616。因此,主部分61生成主输出615(扫描输出信号)。当主部分61在普通模式下操作时,扫描使能信号(se)被断言为逻辑低状态(例如,逻辑“0”),并且数据信号(d)和反相数据信号(db)被输入到交叉耦合的或与反相器(oai)逻辑门对616。

84.根据本公开的一些实施例,触发器电路60的时钟信号cp可以由交叉耦合的或与反相器(oai)逻辑门对616和交叉耦合的和或反相器(aoi)逻辑门对623分别共同使用。这样,可能不需要逻辑反相时钟信号和用于生成这种逻辑反相时钟信号的相应组件(例如,一个或多个反相器),这可以有利地降低功耗和触发器电路60的设计复杂度。

85.根据本公开的一些实施例,通过使用第一控制部分611、第二控制部分612、第三控

制部分613和第四控制部分614,主部分61可以在测试模式下或普通模式操作。因此,可能不需要设置在常规主锁存电路之前的常规多路复用器,这可以有利地使触发器电路60的速度更快,并减少触发器电路60的功耗,例如大约17%。

86.图10示出了根据本公开的一些实施例的触发器电路的晶体管级电路图。参照图10,触发器电路70包括主部分71和从部分72。主部分71被配置为接收至少一个第一输入、至少一个第二输入和至少一个使能信号,并生成主输出715。主部分71包括多个控制部分711、712、713、714,多个控制部分711、712、713、714被配置为根据至少一个第一输入、至少一个第二输入和至少一个使能信号来控制主部分71以第一模式或第二模式操作。根据本公开的一些实施例,第一模式可以是测试模式,并且第二模式可以是普通模式。至少一个第一输入包括扫描输入信号(si)和反相的扫描输入信号(sib),并且至少一个第二输入包括数据信号(d)和反相的数据信号(db)。至少一个使能信号包括扫描使能信号(se)和反相扫描使能信号(seb)。

87.根据本公开的一些实施例,从部分72被配置为接收主输出715并生成输出信号722。从部分72包括连接到主输出715的从输入721。

88.根据本公开的一些实施例,主部分71包括交叉耦合的与或反相器(aoi)逻辑门对716,而从部分72包括交叉耦合的或与反相器(oai)逻辑门对723和从反相器724。交叉耦合的与或反相器(aoi)逻辑门对716可以由多个晶体管实现以执行“aoi”逻辑功能。此外,交叉耦合的或与反相器(oai)逻辑门对723可以由多个晶体管实现以执行“oai”逻辑功能,从反相器724可以由两个晶体管实现以执行“反相器”逻辑功能。

89.根据本公开的一些实施例,参照图9和图10,触发器电路70与触发器电路60基本上类似,除了触发器电路70的主部分71包括交叉耦合的与或反相器(aoi)逻辑门对716,触发器电路70的从部分72包括交叉耦合的或与反相器(oai)逻辑门对723。换句话说,图10中的交叉耦合的或与反相器(oai)逻辑门对723与图9中的交叉耦合的或与反相器(oai)逻辑门对616基本上类似。此外,图10中的交叉耦合的与或反相器(aoi)逻辑门对716与图9中的交叉耦合的与或反相器(aoi)逻辑门对623基本上类似。因此,通过将aoi布置到第一主部分71并且将oai布置到从部分72(即,交换aoi和oai),可以将一个或多个附加时钟缓冲器电路集成到触发器电路70中,因此减少对时钟电路(即,提供时钟信号cp的电路)的负载。

90.根据本公开的一些实施例,为了通过aoi来实现主部分71和通过oai来实现从部分72,触发器电路70还包括反相器74,反相器74被配置为接收时钟信号cp并分别向主部分71和从部分72提供逻辑反相的信号。

91.根据本公开的一些实施例,第一控制部分711、第二控制部分712、第三控制部分713和第四控制部分714可以判定主部分71在测试模式或普通模式操作。当主部分71在测试模式下操作时,扫描使能信号(se)被断言为逻辑高状态(例如,逻辑“1”),并且扫描输入信号(si)和反相扫描输入信号(sib)被输入到交叉耦合的与或反相器(aoi)逻辑门对716。因此,主部分71生成主输出715(扫描输出信号)。当主部分71在普通模式下操作时,扫描使能信号(se)被断言为逻辑低状态(例如,逻辑“0”),并且数据信号(d)和反相数据信号(db)被输入到交叉耦合的与或反相器(aoi)逻辑门对716。

92.根据本公开的一些实施例,通过使用第一控制部分711、第二控制部分712、第三控制部分713和第四控制部分714,主部分71可以在测试模式下或普通模式操作。因此,可能不

需要设置在常规主锁存电路之前的常规多路复用器,这可以有利地使触发器电路70的速度更快,并降低触发器电路70的功耗(例如,大约17%)。

93.图11示出了根据本公开的一些实施例的触发器电路的晶体管级电路图。参考图。参照图9和图11,触发器电路60a与图9的触发器电路60基本上类似,除了触发器电路60a还包括时移电路63之外。时移部分63耦接到主部分61,以将到主部分61的时钟信号cp延迟预定时间。信号cp被连接到不具有时移部分63的从部分62。为清楚起见,对触发器电路60a的组件的讨论基本上类似于触发器电路60(例如61和62)的那些,其被省略。

94.根据本公开的一些实施例,时移电路63包括彼此串联耦合的一个或多个反相器。尽管图11示出了时移电路63包括4个反相器,然而时移电路63中可以包括任何期望数量的反相器(例如2~8个),而这仍然在本公开的范围内。在触发器电路60a中包括这样的时移电路63,来延迟要被主部分61接收的时钟信号cp,而从部分62无延迟地接收时钟信号cp。根据本公开的一些实施例,延迟到主部分61的时钟信号cp可以有利地减少触发器电路60a的建立时间。由于时钟信号cp被延迟以被主部分61接收,并且时钟信号cp被从部分62立即接收而没有延迟,因此在一些实施例中,从部分62可以提供透明窗口且较早释放数据,这使得主部分61在当前周期中有更多的时间接收输入数据,从而减少了建立时间。

95.根据本公开的一些实施例,时移电路63包括4个反相器,并且时移电路63的每个反相器基本上类似于反相器624。主部分61可以在时钟信号cp之后具有大约四个门延迟。

96.图12示出了根据本公开的一些实施例的触发器电路的晶体管级电路图。参考图。参照图9和图12,触发器电路80可以是多位触发器电路。触发器电路80可以包括第一位触发器电路81和第二位触发器电路86。第二位触发器电路86是第一位触发器电路81的副本。触发器电路81包括主部分82和从部分83。主部分82与图9中的主部分61相同。从部分83与图9中的从部分62相同。第一位触发器电路81包括主部分82和从部分83。主部分82与图9中的主部分61相同。从部83与图9中的从部分62相同。第二位触发器电路86包括主部分87和从部分88。主部分87与图9中的主部分61相同。从部88与图9中的从部分62相同。触发器电路80的时钟信号cp可以分别由第一位触发器电路81和第二位触发器电路86共同使用。

97.图13是示出根据本公开的一些实施例的用于操作触发器电路的方法的流程图。而图的过程可以使用各种结构来执行图13的结构,为了便于理解,引用了本文描述的现有结构。参考图13,用于操作触发器的方法包括:第一步骤1301,部署第一主部分11,其被配置为以第一模式操作并接收第一输入,并生成第一主输出,第二步骤1302,部署第二主部分12,其被配置为在第二模式下操作并接收第二输入,并生成第二主输出,第三步骤1303,部署至少一个判定部分13、14,其被配置为接收至少一个使能信号,并具有判定输入和判定输出,判定输入连接至第一主输出和第二主输出,判定部分用于根据所述至少一个使能信号判定判定输出为第一主输出或第二主输出,第四步骤1304,从部分15被配置为接收判定输出并生成输出信号。

98.图14是示出根据本公开的一些实施例的用于操作触发器电路的方法的流程图。而图的过程可以使用多种结构来执行图14的结构,为了便于理解,引用了本文描述的现有结构。参考图14,用于操作触发器的方法包括第一步骤1401,部署第一主部分41,其被配置为以第一模式操作并接收第一输入,并生成第一主输出,第一主部分具有第一使能部分413,第一使能部分413用于根据至少一个使能信号使能第一主部分,第二步骤1402,部署第二主

部分42,其被配置为在第二模式下操作并接收第二输入,并生成第二主输出,第二主部分具有第二使能部分423,第二使能部分423用于根据至少一个使能信号使能第二主部分,第三步骤1403,部署从部分43,其被配置为接收第一主输出或第二主输出,并生成输出信号。

99.图15是示出根据本公开的一些实施例的用于操作触发器电路的方法的流程图。参考图15,用于操作触发器的方法包括第一步骤1501,部署主部分61,其被配置为接收至少一个第一输入、至少一个第二输入和至少一个使能信号,并生成主输出,主部分包括多个控制部件611、612、613、614,多个控制部件611、612、613、614被配置为根据所述至少一个第一输入、所述至少一个第二输入和所述至少一个使能信号来控制所述主部分以第一模式或第二模式操作,第二步骤1502,部署从部分62,其被配置为接收主输出并生成输出信号。

100.在一些实施例中,公开了一种触发器电路,包括第一主部分、第二主部分、至少一个判定部分和从部分。第一主部分被配置为在第一模式下操作并接收第一输入并生成第一主输出。第二主部分被配置为在第二模式下操作并接收第二输入并生成第二主输出。至少一个判定部分被配置为接收至少一个使能信号,并且具有判定输入和判定输出。判定输入连接到第一主输出和第二主输出。判定部分用于根据至少一个使能信号,判定判定输出为第一主输出或第二主输出。从部分被配置为接收判定输出并生成输出信号。

101.在上述触发器电路中,第一模式是测试模式,并且第二模式是普通模式,第一输入是扫描输入信号,并且第二输入是数据信号,至少一个使能信号包括扫描使能信号和反相扫描使能信号。

102.在上述触发器电路中,第一主部分包括第一对交叉耦合的或与反相器(oai)逻辑门和第一主反相器,并且第二主部分包括第二对交叉耦合的或与反相器(oai)逻辑门和第二主反相器,并且从部分包括交叉耦合的与或反相器(aoi)逻辑门对和从反相器。

103.在上述触发器电路中,第一主部分包括第一对交叉耦合的与或反相器(aoi)逻辑门和第一主反相器,并且第二主部分包括第二对交叉耦合的与或反相器(aoi)逻辑门和第二主反相器,并且从部分包括交叉耦合的或与反相器(oai)逻辑门对和从反相器。

104.在上述触发器电路中,触发器电路包括第一判定部分和第二判定部分,第一判定部分具有第一判定输入和第一判定输出,第一判定输入连接到第一主输出,第一判定输出连接到判定输出,第二判定部分具有第二判定输入和第二判定输出,第二判定输入连接到第二主输出,第二判定输出连接到判定输出。

105.在上述触发器电路中,第一判定部分包括由至少一个使能信号控制的多个晶体管,并且第二判定部分包括由至少一个使能信号控制的多个晶体管,至少一个使能信号包括扫描使能信号和反相扫描使能信号。

106.在上述触发器电路中,还包括:时移部分,其耦合到第一主部分和第二主部分,用于延迟到第一主部分和第二主部分的时钟信号的预定时间。信号连接到没有时移部分的从部分。

107.在一些实施例中,公开了一种触发器电路,包括:第一主部分、第二主部分和从部分。第一主部分被配置为在第一模式下操作并接收第一输入并生成第一主输出。第一主部分具有第一使能部分,用于根据至少一个使能信号来使能第一主部分。第二主部分被配置为在第二模式下操作并接收第二输入并生成第二主输出。第二主部分具有第二使能部分,用于根据至少一个使能信号来使能第二主部分。从部分被配置为接收第一主输出或第二主

输出并生成输出信号。

108.在上述触发器电路中,第一模式是测试模式,并且第二模式是普通模式,第一输入是扫描信号,并且第二输入是数据信号,至少一个使能信号包括扫描使能信号和反相扫描使能信号。

109.在上述触发器电路中,第一主部分包括第一对交叉耦合的或与反相器(oai)逻辑门和第一主反相器,并且第二主部分包括第二对交叉耦合的或与反相器(oai)逻辑门和第二主反相器,并且从部分包括交叉耦合的与或反相器(aoi)逻辑门对和从反相器。

110.在上述触发器电路中,第一主部分包括第一对交叉耦合的与或反相器(aoi)逻辑门和第一主反相器,并且第二主部分包括第二对交叉耦合的与或反相器(aoi)逻辑门和第二主反相器,并且从部分包括交叉耦合的或与反相器(oai)逻辑门对和从反相器。

111.在上述触发器电路中,第一使能部分包括由至少一个使能信号控制的多个晶体管,至少一个使能信号包括扫描使能信号和反相扫描使能信号。

112.在上述触发器电路中,第二使能部分包括由至少一个使能信号控制的多个晶体管。

113.在上述触发器电路中,还包括:时移部分,耦合到第一主部分和第二主部分,用于延迟到第一主部分和第二主部分的时钟信号的预定时间,时钟信号连接到没有时移部分的从部分。

114.在一些实施例中,公开了一种触发器电路,包括:主部分,被配置为接收至少一个第一输入、至少一个第二输入和至少一个使能信号,并生成主输出,主部分包括多个控制部分,多个控制部分被配置为根据至少一个第一输入、至少一个第二输入和至少一个使能信号控制主部分以第一模式或第二模式操作;以及从部分,被配置为接收主输出并生成输出信号。

115.在上述触发器电路中,第一模式是测试模式,并且第二模式是普通模式,至少一个第一输入包括扫描输入信号和反相扫描输入信号,并且至少一个第二输入包括数据信号和反相数据信号,并且至少一个使能信号包括扫描使能信号和反相扫描使能信号。

116.在上述触发器电路中,主部分包括第一控制部分、第二控制部分、第三控制部分和第四控制部分,第一控制部分包括由反相扫描信号、反相数据信号,扫描使能信号和反相扫描使能信号控制的多个晶体管,第二控制部分包括由反相扫描输入信号、反相数据信号、扫描使能信号和反相扫描使能信号控制的多个晶体管,第三控制部分包括由扫描输入信号、数据信号、扫描使能信号和反向扫描使能信号控制的多个晶体管,第四控制部分包括由扫描输入信号、数据信号、扫描使能信号和反相扫描使能信号控制的多个晶体管。

117.在上述触发器电路中,主部分包括交叉耦合的或与反相器(oai)逻辑门对,并且从部分包括交叉耦合的与或反相器”(aoi)逻辑门对和从反相器。

118.在上述触发器电路中,主部分包括交叉耦合的与或反相器(aoi)逻辑门对,并且从部分包括交叉耦合的或与反相器(oai)逻辑门对和从反相器。

119.在上述触发器电路中,还包括:时移部分,耦合到主部分,用于延迟到主部分的时钟信号的预定时间,时钟信号连接到没有时移部分的从部分。

120.本领域的普通技术人员将容易地看出,所公开的实施例中的一个或多个实现了以上阐述的一个或多个优点。在阅读了前述说明书之后,本领域的普通技术人员将能够影响

本文广泛公开的各种变化,等同物的替代以及各种其他实施例。因此,旨在于此授予的保护仅受所附权利要求及其等同物中包含的定义的限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。