1.本公开涉及电路领域,尤其涉及一种消除毛刺的电路。

背景技术:

2.通常的芯片设计包括多个模块,各个模块可能处于不同的时钟域。也就是说,多个模块可能是由不同频率的用户时钟信号驱动的。在对芯片设计进行硬件仿真时,仿真系统通常会使用一个频率较快的系统时钟来代替这些不同的用户时钟。这样就可能引入毛刺(glitch)问题。

技术实现要素:

3.有鉴于此,本公开提出了一种消除毛刺的电路。

4.本公开提供了一种消除毛刺的电路,包括:第一锁存器、第二锁存器、选择器以及第三锁存器,其中,所述选择器包括第一输入端、第二输入端、选通输入端和选通输出端,所述第一锁存器包括用于接收数据的第一数据输入端、用于接收第一时钟的第一时钟输入端、以及连接到所述第一输入端的第一数据输出端,所述第二锁存器包括与所述选通输出端连接的第二数据输入端、用于接收第一时钟的第二时钟输入端、以及连接到所述第二输入端的第二数据输出端,所述第三锁存器包括用于接收第二时钟的第三数据输入端、用于接收第一时钟的第三时钟输入端、以及连接到反相器的第三数据输出端,其中,所述反相器和所述第二时钟用作一与门单元的输入,所述与门单元的输出端连接到所述选通输入端。

5.本公开实施例提供的一种消除毛刺的电路,第一锁存器的第一数据输入端接收数据,第一时钟输入端接收第一时钟,当处于第一时钟的上升沿时,第一锁存器能够将数据接入电路,并过滤数据中的毛刺;第二锁存器的第二数据输入端能够将选通输出端的输出存储于电路中,用于保护电路,避免组合逻辑环的产生;第三锁存器的第二时钟输入端接入第一时钟,第三数据输入端接入第二时钟,当处于第一时钟的上升沿时,接入第二时钟,接入第一时钟和第二时钟后的输出结果通过反向器后和第二时钟通过与门,进而消除第二时钟中的毛刺。这样,在第一时钟处于上升沿时,能够消除第二时钟以及数据中的毛刺,而当第一时钟处于低电平时,则能够由选择器将选通输出端的输出数据经过第二锁存器进行数据的保持,保证通过选通输出端输出的数据都已经消除了毛刺。

附图说明

6.为了更清楚地说明本公开或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本公开,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

7.图1示出了本公开实施例所提供的一种产生毛刺的示例性电路结构示意图。

8.图2a示出了本公开实施例所提供的第一种消除毛刺的示例性电路结构示意图。

9.图2b示出了根据本公开实施例的一种消除毛刺的电路的示例性波形图。

10.图3示出了本公开实施例所提供的第二种消除毛刺的示例性电路结构示意图。

11.图4示出了本公开实施例所提供的第三种消除毛刺的示例性电路结构示意图。

12.图5示出了本公开实施例所提供的第四种消除毛刺的示例性电路结构示意图。

具体实施方式

13.为使本公开的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本公开进一步详细说明。

14.需要说明的是,除非另外定义,本公开使用的技术术语或者科学术语应当为本公开所属领域内具有一般技能的人士所理解的通常意义。本公开中使用的“第一”、“第二”以及类似的词语并不表示任何顺序、数量或者重要性,而只是用来区分不同的组成部分。“包括”或者“包含”等类似的词语意指出现该词前面的元件或者物件涵盖出现在该词后面列举的元件或者物件及其等同,而不排除其他元件或者物件。“连接”或者“相连”等类似的词语并非限定于物理的或者机械的连接,而是可以包括电性的连接,不管是直接的还是间接的。

15.图1示出了一种产生毛刺的示例性电路结构100。

16.如图1所示,锁存器fd的时钟是信号ck1和ck2的与信号。由于信号ck1和ck2可能会在不同的时间到达,锁存器的时钟就可能出现毛刺,并且导致q的输出错误。

17.针对这种问题,本公开的实施例提供了一种可以消除毛刺的电路。

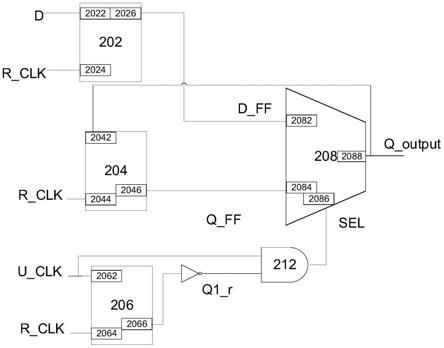

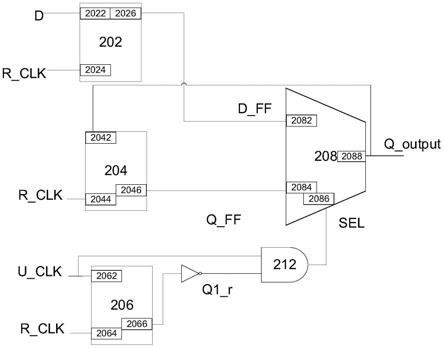

18.图2a示出了一种消除毛刺的电路200的示意性电路图。

19.如图2a所示,电路200可以包括锁存器202、锁存器204、锁存器206以及选择器208。其中,选择器208可以包括输入端2082、输入端2084、选通输入端2086和选通输出端2088,锁存器202可以包括用于接收数据d的数据输入端2022、用于接收时钟r_clk的时钟输入端2024以及连接到输入端2082的数据输出端2026。而锁存器204则可以包括与选通输出端2088连接的数据输入端2042、用于接收时钟r_clk的时钟输入端2044以及连接到输入端2084的数据输出端2046,锁存器206可以包括用于接收时钟u_clk的数据输入端2062、用于接收时钟r_clk的时钟输入端2064以及连接到反相器210的数据输出端2066。其中,时钟r_clk为通过计算得到的高频率时钟信号。

20.电路200还可以包括与门212,反相器210的输出q1_r和时钟u_clk用作与门212的输入,与门212的输出端2122连接到选通输入端2086。可以看到,与门212和反相器210构成了一个与门单元。

21.由于数据d可以根据时钟u_clk产生,也可以是来自任何一个逻辑的信号,所以数据d中也存在毛刺。对于锁存器202而言,锁存器202可以用于过滤数据d中的毛刺,因为只有在处于时钟r_clk的上升沿时,锁存器202才通过数据输入端2022将数据d接入电路200。也就是说当时钟r_clk处于高电平时,锁存器202将数据d接入电路,而时钟r_clk处于低电平时,锁存器202不工作。并且,锁存器202能够将消除毛刺后的数据d的输出d_ff通过数据输出端2026传输至选择器208的输入端2082,输出d_ff进一步可以被选择器208选择是否输出。

22.对于锁存器206而言,锁存器206通过数据输入端2062接入时钟u_clk,通过时钟输入端2064接入时钟r_clk,通过根据频率较高的时钟r_clk去采样频率较低的时钟u_clk,从

而来过滤时钟u_clk中可能存在的毛刺。具体地,只有在时钟r_clk处于上升沿时,才会通过数据输入端2062采集时钟u_clk。需要说明的是,时钟r_clk的频率是时钟u_clk的频率的至少2倍。

23.数据输出端2066的输出可以通过反相器210取反后和时钟u_clk经过与门212,通过与门212的输出端2122将与门212的输出sel传递至选通输入端2086,作为选择信号。

24.对于锁存器204而言,当时钟r_clk为低电平时,由选通输出端2088输出的信号q_output传递至数据输入端2042,经过锁存器204后通过数据输出端2046得到输出q_ff。相当于在时钟r_clk为低电平时对信号q_output进行了保持,从而避免组合逻辑环的产生,保护电路200。需要说明的是,如果输出sel为0,则数据输入端2042就没有输入,如果没有到达时钟r_clk的上升沿,则数据输出2046一直保持为0。假设输出sel初始为0,则到了高电平时,也就是处于时钟r_clk的上升沿时,数据输入端2042接入第一次的信号q_output,当输出sel又变为低电平时,数据输入端2042接入的信号q_output就是第一次的信号q_output,而不是最初保持的0。

25.图2b示出了电路200的示意性波形230。

26.如图2b所示,其中rck表示时钟r_clk的波形,uck表示时钟u_clk的波形,uck_ff表示锁存器206的数据输出端2066的输出,ckout表示选择器208的选通输出端2088输出的信号q_output。时钟u_clk的频率为时钟r_clk的频率的1/8,并且时钟u_clk相比于时钟r_clk有延迟,信号q_output的高电平的宽度为时钟r_clk的一个周期。由于时钟u_clk和取反后的数据输出端2066的输出需要一同经过与门212,所以根据与门的原理,只要有一个输入为0,则与门输出0,所以在时钟u_clk出现的毛刺均在通过与门212之后被滤除了。

27.图3示出了另一种消除毛刺的电路300的示意性电路图。

28.相比于图2a的电路200,电路300进一步可以包括锁存器214和与门216。其中,锁存器214可以包括用于接收使能信号ce的数据输入端2142、用于接收时钟r_clk的时钟输入端2144以及连接到与门216的数据输出端2146。具体地,与门212的输出2122和数据输出端2146用作与门216的输入,与门216的输出2162连接到选通输入端2086。

29.需要说明的是,当使能信号ce为高时,则锁存器214的数据输出端2146则输出0,也就是说可以通过接入使能信号ce能够实现对输出sel的置0,从而控制选择器208的输入,进而控制选择器208输出的信号q_output。

30.可以看到在图3的示例中,与门单元进一步包括锁存器214和与门216。

31.图4示出了又一种消除毛刺的电路400的示意性电路图。

32.相比于图2a的电路200,电路400进一步可以包括锁存器218和复位逻辑单元。其中,复位逻辑单元可以包括反相器和与门220,锁存器218可以包括用于接收复位信号res的数据输入端2182、用于接收时钟r_clk的时钟输入端2184以及连接到与门220的数据输出端2186。具体地,数据输出端2184可以经由反相器和选通输出端2088连接到与门220的输入,由与门220的输出端2202输出过滤毛刺后的信号。

33.其中复位信号res能够触发低电平复位,其中时钟r_clk的低电平需要维持至少一个时钟周期,从而保证电路在运行过程中能够检测到信号的变化,电路在检测到复位信号res之后就会进行复位。

34.图5示出了又一种消除毛刺的电路500的示意性电路图。

35.相比于图2a的电路200,电路500中,复位逻辑单元进一步可以为或门222,其中,数据输出端2186和选通输出端2088可以连接到或门222的输入。

36.其中,或门222能够在两个输入的电平相异时,输出高电平1,若两个输入的电平相同,则输出低电平0。数据输入端2182还可以接入pre信号,从而将锁存器218的输出置1,进而对或门222的输出产生影响,使得选通输出端2088输出为高电平时,或门222的输出也为高电平,选通输出端2088输出为低电平时,或门222的输出为低电平0。

37.本公开实施例提供的一种消除毛刺的电路,第一锁存器的第一数据输入端接收数据,第一时钟输入端接收第一时钟,当处于第一时钟的上升沿时,第一锁存器能够将数据接入电路,并过滤数据中的毛刺;第二锁存器的第二数据输入端能够将选通输出端的输出存储于电路中,用于保护电路,避免组合逻辑环的产生;第三锁存器的第二时钟输入端接入第一时钟,第三数据输入端接入第二时钟,当处于第一时钟的上升沿时,接入第二时钟,接入第一时钟和第二时钟后的输出结果通过反向器后和第二时钟通过与门,进而消除第二时钟中的毛刺。这样,在第一时钟处于上升沿时,能够消除第二时钟以及数据中的毛刺,而当第一时钟处于低电平时,则能够由选择器将选通输出端的输出数据经过第二锁存器进行数据的保持,保证通过选通输出端输出的数据都已经消除了毛刺。

38.上述对本公开特定实施例进行了描述。其他实施例在所附权利要求书的范围内。在一些情况下,在权利要求书中记载的动作或步骤可以按照不同于实施例中的顺序来执行并且仍然可以实现期望的结果。另外,在附图中描绘的过程不一定要求示出的特定顺序或者连续顺序才能实现期望的结果。在某些实施方式中,多任务处理和并行处理也是可以的或者可能是有利的。

39.所属领域的普通技术人员应当理解:以上任何实施例的讨论仅为示例性的,并非旨在暗示本公开的范围(包括权利要求)被限于这些例子;在本公开的思路下,以上实施例或者不同实施例中的技术特征之间也可以进行组合,步骤可以以任意顺序实现,并存在如上所述的本公开的不同方面的许多其它变化,为了简明它们没有在细节中提供。

40.另外,为简化说明和讨论,并且为了不会使本公开难以理解,在所提供的附图中可以示出或可以不示出与集成电路(ic)芯片和其它部件的公知的电源/接地连接。此外,可以以框图的形式示出装置,以便避免使本公开难以理解,并且这也考虑了以下事实,即关于这些框图装置的实施方式的细节是高度取决于将要实施本公开的平台的(即,这些细节应当完全处于本领域技术人员的理解范围内)。在阐述了具体细节(例如,电路)以描述本公开的示例性实施例的情况下,对本领域技术人员来说显而易见的是,可以在没有这些具体细节的情况下或者这些具体细节有变化的情况下实施本公开。因此,这些描述应被认为是说明性的而不是限制性的。

41.尽管已经结合了本公开的具体实施例对本公开进行了描述,但是根据前面的描述,这些实施例的很多替换、修改和变型对本领域普通技术人员来说将是显而易见的。例如,其它存储器架构(例如,动态ram(dram))可以使用所讨论的实施例。

42.本公开旨在涵盖落入所附权利要求的宽泛范围之内的所有这样的替换、修改和变型。因此,凡在本公开的精神和原则之内,所做的任何省略、修改、等同替换、改进等,均应包含在本公开的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。