具有esd功能的沟槽型功率器件

技术领域

1.本发明涉及半导体技术领域,特别涉及一种具有esd功能的沟槽型功率器件。

背景技术:

2.静电放电(electrostatic discharge,esd)是集成电路器件在制造、生产、组装、测试及运送等过程中的常见现象。静电放电时会在短时间内产生的大电流,对集成电路产生致命的损伤,是集成电路生产应用中造成失效的重要问题。

3.沟槽型功率器件以其优越的性能,得到了非常广泛的应用。其中沟槽型功率器件由于栅氧层较薄,且应用于大功率场景的特点,决定了其为静电敏感型器件。业内通常采用增设esd保护单元以改善沟槽型功率器件的esd保护效果。

4.然而,esd保护单元往往设置于衬底表面上,而沟槽型功率器件的栅极设置于沟槽内,致使覆盖于其上的ild(层间介质层)形成较大的台阶,致使后工序(例如通孔的形成、金属互连的形成)良率不高,不利于后续制程。并且,随着集成电路制造工艺水平进入集成电路线宽的深亚微米时代,功率器件的工艺特征尺寸不断缩小,上述台阶的存在对后续工序的影响日趋严重,愈加不利于沟槽型功率器件的进一步微型化。

技术实现要素:

5.本发明的目的在于提供一种具有esd功能的沟槽型功率器件,以解决上述功率器件的esd保护单元的台阶问题。

6.为解决上述技术问题,本发明提供一种具有esd功能的沟槽型功率器件,包括衬底、器件单元及esd保护单元;所述衬底中包括器件单元区及esd保护区,所述esd保护区中形成有至少一个第一沟槽,所述器件单元区形成有至少一个第二沟槽;所述esd保护单元位于所述第一沟槽中,所述器件单元的栅极位于所述第二沟槽中,且所述esd保护单元及所述栅极均与所述衬底的表面齐平,所述esd保护单元连接所述器件单元的栅极和所述器件单元的源极。可选的,所述沟槽型功率器件为n型沟槽dmos器件。

7.可选的,所述器件单元为n型沟槽型dmos器件。

8.可选的,所述esd保护单元包括若至少两个二极管,至少两个所述二极管构成npn或npnpn型结构。

9.可选的,所述esd保护单元中二极管的数量为两个,所述esd保护单元连接于所述器件单元的栅极和源极之间。

10.可选的,所述第一沟槽中形成esd保护单元过程为:形成第一介质层,所述第一介质层覆盖所述第一沟槽的内壁;形成导电层,所述导电层填充所述第一沟槽并与所述衬底的表面的高度差在预设范围内;执行多次p型离子注入,依次形成p区、p 区,其中所述p区相接于所述p 区的上方;执行n型离子注入,在所述p区中形成两个n 区,两个所述n 区位于所述p区的顶部。

11.可选的,所述第一介质层为teos层。

12.可选的,所述导电层的材质为多晶硅。

13.可选的,所述层间介质层为bpsg层。

14.可选的,所述第一沟槽的开口宽度大于所述第二沟槽的开口宽度。

15.综上所述,本发明提供的一种具有esd功能的沟槽型功率器件,通过将esd保护单元形成于沟槽中,并回蚀刻使得esd保护单元与器件单元的顶面齐平,从而有利于其上的层间介质层及金属互连层的形成,解决了功率器件esd保护单元的台阶问题,提高了器件的良率。

附图说明

16.本领域的普通技术人员应当理解,提供的附图用于更好地理解本发明,而不对本发明的范围构成任何限定。其中:

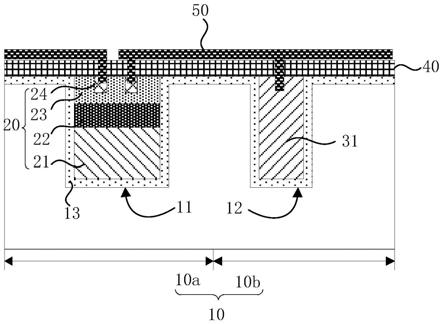

17.图1为本技术实施例提供的具有esd功能的沟槽型功率器件的结构示意图;

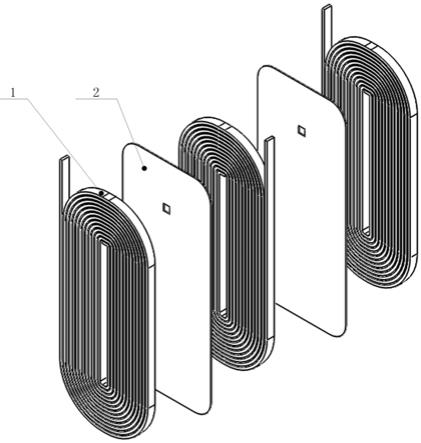

18.图2为本实施提供的esd保护单元的形成方法的流程图;

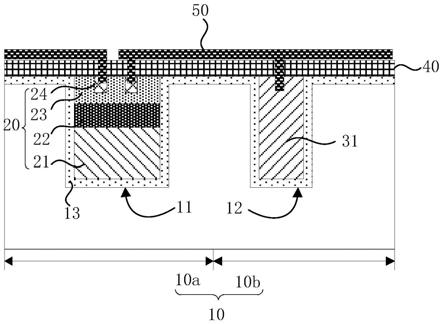

19.图3~图6为本实施提供的esd保护单元的形成方法相应步骤对应的结构示意图。

20.附图中:

21.10

‑

衬底;10a

‑

esd保护区;10b

‑

器件单元区;11

‑

第一沟槽;12

‑

第二沟槽;13

‑

第一介质层;

22.21

‑

导电层;22

‑

p 区;23

‑

p区;24

‑

n 区;

23.31

‑

栅极;

24.40

‑

层间介质层;50

‑

金属层。

具体实施方式

25.为使本发明的目的、优点和特征更加清楚,以下结合附图和具体实施例对本发明作进一步详细说明。需说明的是,附图均采用非常简化的形式且未按比例绘制,仅用以方便、明晰地辅助说明本发明实施例的目的。此外,附图所展示的结构往往是实际结构的一部分。特别的,各附图需要展示的侧重点不同,有时会采用不同的比例。

26.如在本发明中所使用的,单数形式“一”、“一个”以及“该”包括复数对象,术语“或”通常是以包括“和/或”的含义而进行使用的,术语“若干”通常是以包括“至少一个”的含义而进行使用的,术语“至少两个”通常是以包括“两个或两个以上”的含义而进行使用的,此外,术语“第一”、“第二”、“第三”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”、“第三”的特征可以明示或者隐含地包括一个或者至少两个该特征,除非内容另外明确指出外。

27.本技术实施例提供一种具有esd功能的沟槽型功率器件,以解决上述功率器件的esd保护单元与器件单元的台阶问题。

28.图1为本技术实施例提供的具有esd功能的沟槽型功率器件的结构示意图。

29.如图1所示,本技术实施例提供的具有esd功能的沟槽型功率器件包括:包括衬底10、器件单元及esd保护单元20。衬底10中包括器件单元区10b及esd保护区10a,esd保护区10a中形成有至少一个第一沟槽11,器件单元区10b形成有至少一个第二沟槽12。esd保护单元20位于第一沟槽11中,器件单元的栅极31位于第二沟槽12中,且esd保护单元20及栅极31

均与衬底10的表面齐平,esd保护单元20连接器件单元的栅极31和器件单元的源极。

30.在本实施例中,沟槽型功率器件为沟槽型dmos器件,例如沟槽型ldmos器件或沟槽型vdmos器件,在本技术的其他具体实施例中,还可以其他沟槽型功率器件,例如晶闸管(scr)、igbt、igct、gto等。

31.具体的,衬底10可以为硅基半导体或绝缘体上硅(soi)衬底,本技术实施例中衬底10的材料以硅为例加以说明。衬底10表面中形成有外延层(图1中未示出),第一沟槽11及第二沟槽12均形成与外延层中。以n型dmos器件为例,衬底10和外延层的掺杂类型均是n型,且衬底10的掺杂浓度高于外延层的掺杂浓度。

32.如图1所示,衬底10中具有器件单元区10b及esd保护区10a。在本实施例中,为便于说明,esd保护区10a与器件单元区10b相邻设置,用于对器件单元区10b中的器件单元进行esd保护。在本技术的其他实施例中,esd保护区10a还可远离器件单元区10b设置,例如设置于功率器件的gate pad区(栅极焊盘区)。在实际中,栅极焊盘区作为功率器件的控制端,具有esd保护的较高优先级。

33.请继续参照图1,在器件单元区10b中形成有与功率器件相应的器件单元,在本实施例中,器件单元为n型沟槽型dmos器件单元。第二沟槽12形成于器件单元区10b的外延层中,器件单元的栅极31形成于第二沟槽12中,可以为普通栅极结构或屏蔽栅结构,栅极31的顶面与衬底10的表面齐平。需要说明的是,本实施例中的顶面齐平是指栅极31与衬底10表面的高度差在预设的范围之内。在第二沟槽12的周围还形成有器件单元的源极或漏极。应理解,若功率器件为ldmos器件,器件单元的源极、漏极及栅极31均位于衬底10的同一侧,若功率器件为vdmos器件,则器件单元的源极及栅极31位于衬底10的一侧,而器件单元的漏极则为于衬底10相对的另一侧。当然,在器件单元区10b中设置有多个器件单元(元胞),以提高相应的导通能力。

34.请继续参照图1,在esd保护区10a中形成有esd保护单元。具体的,esd保护单元20形成于esd保护区10a的第一沟槽11内,esd保护单元20的顶面与衬底10表面齐平,也即esd保护单元20与衬底10表面的高度差在预设范围之内。由此,即可形成器件单元与esd保护单元20的高度差在预设范围之内,降低甚至消除esd保护单元20与器件单元的台阶差,有利于位于衬底10上的层间介质层40的形成,并提高层间介质层40的平坦度,进而有利于设置于层间介质层40之上的金属互连层50的形成,提高器件的良率。

35.其中,esd保护单元可以为任意合适的esd保护单元,例如分压电阻、二极管、mos管、scr等,esd保护单元可以为其中一类的一个、或其中一类中的若干个的组合,或其中几类中的几个的组合。与之相应的,esd保护区10a中也可以具有一个或多个第一沟槽11,一个或多个esd保护单元设置于上述的一个或多个第一沟槽11中。其中,多个esd保护单元可以形成单向或双向的esd保护。优选的,多个esd保护单元还可形成多级的不同等级阈值电压(泄电电压)的esd保护。

36.在本技术实施例中esd保护单元包括至少两个二极管,至少两个二极管构成npn或npnpn型结构,用于esd保护,其中,pn结串联的个数取决于esd保护的击穿电压需求。在一具体实施例中,二极管的数量为两个,且阳极相连,连接器件单元20的栅极31和源极,用于器件单元20的栅极31和源极之间的esd保护。

37.图2为本实施提供的esd保护单元的形成方法的流程图。

38.如图2所示,本实施例提供的esd保护单元的形成方法,包括:

39.s01:形成第一介质层,所述第一介质层覆盖所述第一沟槽的内壁;

40.s02:形成导电层,所述导电层填充所述第一沟槽并与所述衬底的表面齐平;

41.s03:执行多次p型离子注入,依次形成p区、p 区,其中所述p区相接于所述p 区的上方;

42.s04:执行n型离子注入,在所述p区中形成两个n 区,两个所述n 区位于所述p区的顶部。

43.图3~图6为本实施提供的esd保护单元的形成方法相应步骤对应的结构示意图,接下来,将结合图3~图6对esd保护单元的形成方法进行详细说明。

44.请参照图3,执行步骤s01,形成第一介质层13,第一介质层13覆盖第一沟槽11的内壁。在实际中,在形成第一介质层之前还可执行热氧化工艺,以在第一沟槽11及位于esd保护区10a的衬底表面形成一层更为致密的氧化层。应理解,第一介质层13还覆盖于esd保护区10a的衬底表面(示意图中未示出)。第一介质层可为teos层,例如可通过lpcvd工艺以形成氧化硅,所形成氧化硅的厚度例如为1500埃~2000埃,以提高隔离效果。

45.请参照图4,执行步骤s02,形成导电层21,回蚀刻导电层21使得导电层21填充第一沟槽11并与位于esd保护区10a的衬底表面齐平。具体的,导电层21的材质可以为多晶硅。

46.请参照图5,对导电层21执行多次p型离子注入,依次形成p区23、p 区22,p区23相接于p 区22的上方。具体的,先形成p区23,,再形成p 区22,p 区22的结深深于p区23,并与p区22相接,其中,p区23的掺杂浓度为中掺杂浓度,p 区22的掺杂浓度高于p区23的掺杂浓度,以整体加强p型离子注入区的浓度,提高抗压能力。

47.请参照图6,执行步骤s03,执行n型离子注入,在p区23中形成两个n 区24,两个n 区24位于p区23中且位于p区23的顶部。具体的,n 区24的结深浅于p区23的结深,并靠近导电层21的表面,两个n 区24间隔设置于第一沟槽11表面的两端。其中第一沟槽11的开口宽度设置大于第二沟槽12的开口宽度,以便于后续的互连工艺将两个n 区分别引出。由此,便在第一沟槽11中形成npn结构的esd保护单元,其中,p区23与p 区22的浓度以及厚度(结深)均可根据实际功率产品的需求而进行具体设定。

48.在上述所形成的esd保护单元20中,采用对称的结构,并连接于器件单元的栅极31和源极之间,可同时形成对正向esd脉冲或负向正向esd脉冲对称的泄放通路,进而对双向脉冲进行esd保护。而且,esd保护单元的对称结构,还可补偿esd保护单元的温漂,提高esd保护单元的热稳定性。

49.优选的,还可在esd保护区10a形成多个第一沟槽11,例如两个第一沟槽11,也即是在esd保护区10a形成两个上述esd保护单元20,并且两个esd保护单元20的掺杂浓度及深度可不同而具有不同的击穿阈值电压(泄电阈值电压),从而可形成两级esd泄电,达到双重esd保护的目的。当然,上述两个esd保护单元还可以是其他具有esd保护功能结构的组合,例如二极管与分压电阻的组合。请继续参照图1,衬底10的表面还覆盖有层间介质层40用于隔离,并在层间介质层40中设置有用于互连的通孔。优选的,为提高层间介质层40的台阶填充性能及钠离子吸收阻隔效果,层间介质层40可为bpsg层。其中,衬底10的表面还覆盖有第一介质层13(teos层),bpsg层覆盖teos层、器件单元及esd保护单元20之上。

50.请继续参照图1,金属互连层50设置于层间介质层40之上,并利用贯穿层间介质层

40的通孔连接器件单元和esd保护单元,以及器件单元之间的局部互连。其中,一个esd保护单元的两端(两个n 区)连接于器件单元的栅极31和源极之间,或多个esd保护单元的两端并联于两者之间,用于两者的esd防护。不难理解,由于器件单元与esd防护单元20的顶面与衬底10表面齐平(高度差在预设范围之内)使得所形成的层间介质层40具有较为平坦的表面,从而有利于在层间介质层40之上的金属互连层50的形成,提高制造良率。

51.综上所述,本发明提供的一种具有esd功能的沟槽型功率器件,通过将esd保护单元形成于第一沟槽中,并回蚀刻使得esd保护单元与器件单元的顶面齐平,从而有利于其上的层间介质层及金属互连层的形成,解决了功率器件的esd保护单元的台阶问题,提高了后工序良率。

52.上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。