1.以下实施方式涉及一种三维闪存以及制造该三维闪存的方法。

背景技术:

2.闪存是一种电可擦除可编程只读存储器(eeprom),其数据的输入和输出通过f

‑

n隧穿(fowler

‑

nordheim隧穿)或热电子注入而被电控制。

3.在最近的闪存中,已经应用三维结构,其中单元被垂直地堆叠以增大集成度,以便提供高性能并实现消费者所要求的低价格。参照图1和图2(其示出根据相关技术的三维闪存),三维闪存100具有包括至少一个存储单元串110、多个电极层120和多个绝缘层130的结构,该至少一个存储单元串110包括在垂直方向上延伸的沟道层111和形成为围绕沟道层111的电荷存储层112,该多个电极层120在水平方向上连接到该至少一个存储单元串110并堆叠,该多个绝缘层130交替地形成在该多个电极层120之间。在下文,由于该多个电极层120中的每个被用作字线,所以该多个电极层120将被描述为多条字线120。

4.这里,要连接到外部布线的接触121将形成在所述多条字线120中的每条上,因此,所述多条字线120具有包括台阶部分122和平面部分123的阶梯结构,如所示的。

5.这里,仅所述多条字线120的接触121分别形成在台阶部分122中,并且仅所述至少一个存储单元串110形成在平面部分123中。也就是,具有存储功能的所述至少一个存储单元串110将仅形成在平面部分123上,因此,浪费了三维闪存100的大量面积。此外,三维闪存100的台阶数越多,台阶部分122的面积相对于总存储器面积的比例就越高,从而降低整体集成度。

6.因此,需要提出一种三维闪存技术,以通过有效率地使用台阶部分122来提高集成度。

7.此外,所述多条字线120的接触121分别形成在所述多条字线120的总的阶梯形区域上,因此,浪费三维闪存100的大量面积。此外,三维闪存100的台阶数越多,接触121的面积相对于总存储器面积的比例就越高,从而降低整体集成度。

8.因此,需要提出一种三维闪存技术,以通过减小用于形成接触的面积来实现集成。

9.参照关于根据相关技术的制造三维闪存的方法的图10a至图10d,根据该方法,如图10a所示,光致抗蚀剂1030形成在其中多条字线1010和多个绝缘层1020交替堆叠的模具结构上,并且光致抗蚀剂1030被修整,然后如图10b所示,对所述多条字线1010当中的最上面的字线1011执行蚀刻操作以形成阶梯形状的一部分。接下来,在根据相关技术的制造三维闪存的方法中,如图10c所示,光致抗蚀剂1030被修整,然后,如图10d所示,对字线1011和字线1012(其表面被暴露)执行蚀刻操作以形成具有阶梯形状的两个部分。在根据相关技术的制造三维闪存的方法中,通过如一直到图10j所示重复修整操作和蚀刻操作、然后如图10k所示去除光致抗蚀剂1030,可以完成具有阶梯形状的字线1010。

10.然而,在根据相关技术的制造三维闪存的方法中,存在需要重复执行蚀刻操作比字线1010的台阶数量少一次的缺点。

11.因此,需要提出一种通过减少蚀刻操作的重复次数来简化字线的制造工艺的技术。

技术实现要素:

12.技术问题

13.根据实施方式,提出一种三维闪存及其制造方法,以通过有效率地使用台阶部分来实现集成。

14.具体地,根据实施方式,提出一种三维闪存以及制造该三维闪存的方法,其中至少一个存储单元串形成在包括于多条字线的阶梯形状中的平面部分和台阶部分两者中。

15.此外,根据实施方式,提出一种三维闪存以及制造该三维闪存的方法,以通过减小用于形成接触的面积来实现集成。

16.具体地,根据实施方式,提出一种三维闪存以及制造该三维闪存的方法,其中所述多条字线中的每条字线的接触仅形成在所述多条字线中的每条字线的整个区域中的最小化的部分区域(minimized partial area)中。

17.此外,根据实施方式,提出一种制造三维闪存的方法,其中通过减少对字线的蚀刻操作的重复次数来简化制造工艺。

18.具体地,根据实施方式,提出一种制造三维闪存的方法,其中通过将多条字线分为以阶梯形状依次堆叠的上字线组和下字线组来制备多条字线,然后对上字线组和下字线组中的每个同时执行蚀刻操作,从而显著减少对字线的蚀刻操作的重复次数。

19.此外,根据实施方式,提出根据上述制造三维闪存的方法制造的三维闪存。

20.具体地,根据实施方式,提出一种具有如下结构的三维闪存,当通过使用多条字线形成具有等间距宽度和等间距高度的阶梯形状时,该结构包括与该阶梯形状中的其它部分具有不同的高度的部分。

21.此外,根据实施方式,提出一种具有如下结构的三维闪存,当通过使用多条字线形成具有等间距宽度和等间距高度的阶梯形状时,该结构包括与该阶梯形状中的其它部分具有不同的宽度的部分。

22.此外,根据实施方式,提出一种具有如下结构的三维闪存,当通过使用多条字线形成具有等间距宽度和等间距高度的阶梯形状时,该结构包括与该阶梯形状中的其它部分具有不同的高度的部分和具有不同的宽度的部分。

23.对问题的方案

24.根据一实施方式,一种用于实现集成的三维闪存包括:至少一个存储单元串,垂直地延伸并包括至少一个沟道层和围绕所述至少一个沟道层的至少一个电荷存储层;以及多条字线,正交地连接到所述至少一个存储单元串并堆叠,并且在水平方向上延伸,其中所述多条字线以彼此不同的长度延伸以形成阶梯形状,该阶梯形状包括台阶部分和平面部分,其中所述至少一个存储单元串形成在平面部分和台阶部分两者中。

25.所述多条字线中的每条字线的接触可以仅形成在台阶部分的多个台阶中的每个的最小化的部分区域中。

26.最小化的部分区域可以包括与所述多条字线中的每条字线的接触的横截面积相对应的区域。

27.对于台阶部分的每个台阶,形成在台阶部分中的所述至少一个存储单元串可以位于与形成在台阶部分中的每条字线的接触相同的列中。

28.根据一实施方式,一种用于实现集成的三维闪存,该三维闪存包括:至少一个存储单元串,在一方向上延伸并包括至少一个沟道层和围绕所述至少一个沟道层的至少一个电荷存储层;以及多条字线,垂直地连接到所述至少一个存储单元串,其中所述多条字线中的每条字线的接触仅形成在所述多条字线中的每条字线的整个区域的最小化的部分区域中。

29.由于所述多条字线中的每条字线的接触仅形成在所述多条字线中的每条字线的整个区域的最小化的部分区域中,所以所述多条字线可以提供一空间,在该空间处形成不与所述至少一个存储单元串布置在相同的阵列中的至少一个另外的存储单元串。

30.由于所述至少一个另外的存储单元串形成在该空间中,所以所述多条字线可以由所述至少一个存储单元串和所述至少一个另外的存储单元串共用。

31.在该处形成所述多条字线中的每条字线的接触的所述最小化的部分区域可以包括与所述多条字线中的每条字线的整个区域位于相同的行中的区域。

32.根据一实施方式,一种制造三维闪存的方法,用于有效率地形成字线,包括:通过将多条字线分为上字线组和下字线组而制备在水平方向上的堆叠的多条字线,其中上字线组和下字线组具有不同的水平尺寸并以阶梯形状依次堆叠,使得上字线组和下字线组中的每个的上表面的至少一部分被暴露;在上字线组的上表面的至少一部分和下字线组的上表面的至少一部分上形成光致抗蚀剂;以及同时对其上形成有光致抗蚀剂的上字线组和下字线组的每个执行蚀刻操作。

33.下字线组可以具有比上字线组更大的水平尺寸。

34.通过将所述多条字线分成上字线组和下字线组来制备所述多条字线可以包括将下字线组的水平尺寸确定为包括蚀刻停止距离以在对下字线组执行蚀刻操作时防止蚀刻上字线组中的最下面的字线。

35.通过将所述多条字线分成上字线组和下字线组来制备所述多条字线可以包括在上字线组和下字线组之间布置蚀刻停止保护层以在对上字线组执行蚀刻操作时防止蚀刻下字线组中的最上面的字线。

36.对上字线组和下字线组中的每个同时执行蚀刻操作可以基于上字线组中包括的字线由此堆叠的台阶数量以及下字线组中包括的字线由此堆叠的台阶数量而被重复地执行。

37.公开的有益效果

38.根据实施方式,可以提出一种三维闪存以及制造该三维闪存的方法,以通过有效率地使用台阶部分来实现集成。

39.具体地,根据实施方式,可以提出一种三维闪存以及制造该三维闪存的方法,其中至少一个存储单元串形成在包括于多条字线的阶梯形状中的平面部分和台阶部分两者中。

40.此外,根据实施方式,可以提出一种三维闪存以及制造该三维闪存的方法,以通过减小用于形成接触的面积来实现集成。

41.具体地,根据实施方式,可以提出一种三维闪存以及制造该三维闪存的方法,其中所述多条字线中的每条字线的接触仅形成在所述多条字线中的每条字线的整个区域中的最小化的部分区域中。

42.此外,根据实施方式,可以提出一种制造三维闪存的方法,其中通过减少对字线的蚀刻操作的重复次数来简化制造工艺。

43.具体地,根据实施方式,可以提出一种制造三维闪存的方法,根据该方法,通过将多条字线分为以阶梯形状依次堆叠的上字线组和下字线组来制备多条字线,然后同时对上字线组和下字线组中的每个执行蚀刻操作,从而显著减少对字线的蚀刻操作的重复次数。

44.此外,根据实施方式,可以提出根据上述制造三维闪存的方法制造的三维闪存。

45.具体地,根据实施方式,可以提出具有如下结构的三维闪存,当通过使用多条字线形成具有等间距宽度和等间距高度的阶梯形状时,该结构包括与该阶梯形状中的其它部分具有不同的高度的部分。

46.此外,根据实施方式,可以提出具有如下结构的三维闪存,当通过使用多条字线形成具有等间距宽度和等间距高度的阶梯形状时,该结构包括与该阶梯形状中的其它部分具有不同的宽度的部分。

47.此外,根据实施方式,可以提出一种具有如下结构的三维闪存,当通过使用多条字线形成具有等间距宽度和等间距高度的阶梯形状时,该结构包括与该阶梯形状中的其它部分具有不同的高度的部分和具有不同的宽度的部分。

附图说明

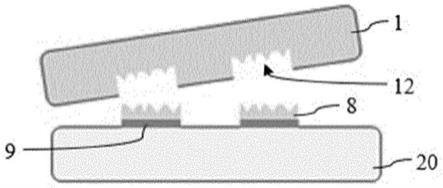

48.图1是根据相关技术的三维闪存的平面图。

49.图2是根据相关技术的三维闪存的截面图。

50.图3是根据一实施方式的三维闪存的平面图。

51.图4是根据一实施方式的三维闪存的截面图。

52.图5是根据一实施方式的制造三维闪存的方法的流程图。

53.图6a至图6i是用于描述根据一实施方式的制造三维闪存的方法的图。

54.图7是根据一实施方式的三维闪存的平面图。

55.图8a和图8b是根据一实施方式的三维闪存的截面图。

56.图9是根据一实施方式的制造三维闪存的方法的流程图。

57.图10a至图10k是用于描述根据相关技术的制造三维闪存的方法的图。

58.图11是根据一实施方式的制造三维闪存的方法的流程图。

59.图12a至图12k是用于描述根据一实施方式的制造三维闪存的方法的图。

60.图13a至图13c示出使用参照图11描述的制造三维闪存的方法制造的三维闪存。

具体实施方式

61.在下文,将参照附图详细描述实施方式。然而,本发明构思不受实施方式限制。此外,在每个附图中示出的相同的附图标记表示相同的元件。

62.本说明书中使用的术语是用于适当表达本发明构思的实施方式的那些术语,并且该术语可以根据本领域普通技术人员的意图、先例或惯例而变化。因此,说明书中使用的术语应当基于本发明构思的描述来定义。

63.图3是根据一实施方式的三维闪存的平面图,图4是根据一实施方式的三维闪存的截面图。

64.参照图3和图4,三维闪存300可以包括垂直地延伸的至少一个存储单元串310、320、330以及正交地连接到所述至少一个存储单元串310、320、330并被堆叠并且在水平方向上延伸的多条字线340。

65.所述至少一个存储单元串310、320、330可以包括至少一个沟道层311和围绕所述至少一个沟道层311的至少一个电荷存储层312。所述至少一个沟道层311可以包括在垂直方向上延伸的单晶硅或多晶硅,并可以使用其中基板(未示出)被用作籽晶的选择性外延生长工艺或相变外延工艺形成。此外,所述至少一个沟道层311可以具有中空管形状并且还包括在其中的掩埋层(未示出)。

66.所述至少一个电荷存储层312可以包括具有存储来自流过所述多条字线340的电流的电荷的存储功能的元件,并可以具有例如氧化物

‑

氮化物

‑

氧化物(ono)结构。在下文,尽管所述至少一个电荷存储层312被描述为仅包括垂直元件,但是本发明构思不限于此,所述至少一个电荷存储层312还可以包括水平元件。

67.此外,尽管没有在附图中示出,但是围绕所述至少一个存储单元串310、320、330并垂直地延伸的至少一个隧穿绝缘层(未示出)可以布置在所述至少一个存储单元串310、320、330的外部。所述至少一个隧穿绝缘层可以包括具有高k特性的绝缘材料(例如,诸如al2o3、hfo2、tio2、la2o5、bazro3、ta2o5、zro2、gd2o3或y2o3的绝缘材料)。

68.所述多条字线340具有向所述至少一个存储单元串310、320、330施加电压的功能,并可以包括诸如w、ti、ta、cu或au的导电材料。所述多条字线340可以以彼此不同的长度延伸以形成包括台阶部分350和平面部分360的阶梯形状。例如,在所述多条字线340当中,在最下部分中的第一字线341可以具有最长的水平长度,位于第一字线341上方的第二字线341可以具有第二长的水平长度,在最上部分中的第三字线343可以具有最短的水平长度,从而形成包括台阶部分350和平面部分360的阶梯形状。

69.具体地,根据实施方式的三维闪存300的特征在于所述至少一个存储单元串310、320、330形成在平面部分360和台阶部分350两者中。例如,第一存储单元串310和第二存储单元串320可以形成在台阶部分350中,第三存储单元串330可以形成在平面部分360中。因此,不同于根据相关技术的三维闪存(其中至少一个存储单元串仅形成在平面部分360中),根据实施方式的三维闪存300的整体集成度可以提高。

70.这里,所述多条字线340的接触341

‑

1、342

‑

1可以仅形成在构成台阶部分350的多个台阶351、352中的每个中的最小化的部分区域中。在下文,该最小化的部分区域可以指对应于所述多条字线340的接触341

‑

1和341

‑

2中的每个的横截面积的区域,例如,所述多个台阶351和352中的每个的总面积当中的具有与所述多条字线340的接触341

‑

1和341

‑

2中的每个的横截面积相等的面积的区域。

71.此外,对于构成台阶部分350的所述多个台阶351和352中的每个台阶,形成在台阶部分350中的至少一个存储单元串310、320可以与字线341、342的形成在台阶部分350中的接触341

‑

1、342

‑

1位于相同的列中。例如,形成在第一字线341的台阶351中的第一存储单元串310和第一字线341的接触341

‑

1可以位于相同的列中,并且形成在第二字线342的台阶352中的第二存储单元串320和第二字线342的接触342

‑

1可以位于相同的列中。

72.由于对于构成台阶部分350的多个台阶351、352中的每个台阶,形成在台阶部分350中的至少一个存储单元串310、320与每条字线341、342的形成在台阶部分350中的每个

接触341

‑

1、342

‑

1位于相同的列中,所以连接到字线341、342的形成在台阶部分350中的每个接触341

‑

1、342

‑

1的外部布线370和连接到形成在台阶部分350中的至少一个存储单元串310、320的漏极线380也可以位于相同的列中。

73.此外,三维闪存300还可以包括在所述多条字线340之间的多个层间绝缘层390。然而,本发明构思不限于此,并且代替所述多个层间绝缘层380,可以布置使所述多条字线340彼此间隔开的多个气隙。

74.如上所述,根据实施方式的三维闪存300可以包括也在所述多条字线340的台阶部分350中的至少一个存储单元串310、320,因此,与根据现有技术的结构(其中在台阶部分350中没有形成存储单元串)相比,可以包括更多的存储单元串310、320、330。因此,可以显著增大三维闪存300的集成度。

75.图5是根据一实施方式的制造三维闪存的方法的流程图。图6a至图6i是用于描述根据一实施方式的制造三维闪存的方法的图。在下文,作为用于执行制造三维闪存的方法的主体,可以使用自动化和机械化制造系统,并且在以下描述的操作(s510至s540)中制造的三维闪存具有参照图3和图4描述的结构。

76.参照图5,在操作s510中,根据实施方式的制造系统制备在其中多条字线610和多个绝缘层620交替堆叠的半导体结构600,如图6a所示。

77.接着,在操作s520中,在半导体结构600的整个区域中,除了在其中将要分别形成所述多条字线610的接触611、612、613的最小化的部分区域601、602、603之外,该制造系统形成垂直地延伸的至少一个存储单元串630(该至少一个存储单元串630包括至少一个沟道层和围绕该至少一个沟道层的至少一个电荷存储层)。

78.在下文,该最小化的部分区域601、602、603可以指分别对应于所述多条字线610的接触611、612、613的横截面积的区域,例如,将要包括在阶梯形状中的多个台阶614、615、616中的每个的整个区域中的具有与所述多条字线610的接触611、612、613的横截面积相等的面积的区域。

79.例如,通过考虑到该最小化的部分区域601、602、603的布置,该制造系统可以在半导体结构600的除了该最小化的部分区域601、602、603之外的整个区域中在垂直方向上形成至少一个垂直孔604、605、606,使得该最小化的部分区域601、602、603分别被包括在将要包括在阶梯形状(所述多条字线610将具有该阶梯形状)中的多个台阶614、615、616中,如图6b和图6c所示,然后在所述至少一个垂直孔604、605、606中形成至少一个存储单元串630,如图6d和图6e所示。

80.这里,在形成所述至少一个垂直孔604、605、606的操作中,该制造系统可以在垂直方向上为所述多个台阶604、605、606中的每个形成至少一个垂直孔604、605、606,使得所述至少一个垂直孔604、605、606与分别包括在将要在操作s530(将在后面描述)中形成的所述多个台阶614、615、616中的最小化的部分区域601、602、603位于相同的列中。

81.接下来,在操作s530中,如图6f和图6g所示,该制造系统以阶梯形状蚀刻包括最小化的部分区域601、602、603的特定区域。例如,该制造系统可以通过以阶梯形状蚀刻包括最小化的部分区域601、602、603的特定区域来形成阶梯形状,该阶梯形状包括台阶部分640和平面部分650,该台阶部分640包括多个台阶614、615、616。

82.操作s530可以通过基于将要形成的多个台阶614、615、616的台阶数量重复执行修

整操作和蚀刻操作来执行,并且在操作s530中使用的蚀刻方法可以是允许同时蚀刻所述至少一个存储单元串630和所述多条字线610的蚀刻方法。也就是,在操作s530中,该制造系统可以使用允许以相同的深度同时蚀刻所述至少一个存储单元串630的材料和所述多条字线610的材料的蚀刻方法。

83.接下来,在操作s540中,该制造系统可以在最小化的部分区域601、602、603中形成所述多条字线610的相应接触611、612、613,如图6h和图6i所示。这里,该制造系统可以在形成所述多条字线610的接触611、612、613的同时形成连接到所述多条字线610的相应接触611、612、613的外部布线和连接到所述至少一个存储单元串630的漏极线。

84.图7是根据一实施方式的三维闪存的平面图,图8a和图8b是根据一实施方式的三维闪存的截面图。

85.参照图7至图8b,根据一实施方式的三维闪存700在基板710上包括在一方向上延伸的至少一个存储单元串720和多条字线730。在三维闪存700中,漏极线可以布置在所述至少一个存储单元串720上并且连接到所述至少一个存储单元串720,并且所述多条字线730中的每条可以通过接触731连接到外部布线。在下文,漏极线和外部布线仅在图7中示出,并在图8a和图8b中被省略。

86.所述至少一个存储单元串720可以包括至少一个沟道层721和围绕该至少一个沟道层721的至少一个电荷存储层722。所述至少一个沟道层721可以包括单晶硅或多晶硅,并可以使用其中基板710用作籽晶的选择性外延生长工艺或相变外延工艺形成。

87.所述至少一个电荷存储层722可以包括存储来自流过所述多条字线730的电流的电荷的元件,并可以具有例如氧化物

‑

氮化物

‑

氧化物(ono)结构。尽管下面将所述至少一个电荷存储层722描述为仅包括在正交于基板710的方向上延伸的垂直元件,但是本发明构思不限于此,所述至少一个电荷存储层722还可以包括平行于多条字线730并接触多条字线730的水平元件。

88.所述多条字线730在垂直方向上连接到所述至少一个存储单元串720并可以相对于多个绝缘层740交替布置。所述多条字线730可以包括导电材料诸如钨、钛、钽,所述多个绝缘层740可以包括各种绝缘材料。

89.所述多条字线730形成为阶梯形状,并可以经由形成在阶梯形状中的每个接触731连接到外部布线。具体地,所述多条字线730的接触731的特征在于它们分别仅形成在所述多条字线730中的每条字线的整个区域的最小化的部分区域中。所述多条字线730中的每条字线的形成在如下所述的最小化的部分区域中的接触731是指仅形成在所述多条字线730中的每条字线的整个区域中的与接触731的横截面相对应的区域中的接触731。

90.此外,所述多条字线730中的每条字线的接触731形成在其中的最小化的部分区域可以是在所述多条字线730中的每条字线的整个区域中位于相同行中的区域。也就是,当接触731仅形成在所述多条字线730中的每条字线的整个区域中的与接触731的横截面相对应的区域中时,接触731可以形成在所述多条字线730中的每条字线中的位于相同行中的区域中。

91.如上所述,由于所述多条字线730中的每条字线的接触731仅形成在所述多条字线730中的每条字线的整个区域的最小化的部分区域中,所以可以提供空间751,在空间751处形成与所述至少一个存储单元串720不布置在相同的阵列中的至少一个其它存储单元串

750。因此,三维闪存700可以包括更多的存储单元串720、750,因此具有更高的集成度。以下与所述至少一个存储单元串720相同的阵列是指一组存储单元串,其包括所述至少一个存储单元串720以及与所述至少一个存储单元串720布置在相同的列中的存储单元串,因此,与所述至少一个存储单元串720不布置在相同的阵列中的所述至少一个其它存储单元串750可以指布置在与所述至少一个存储单元串720不同的列中的存储单元串。

92.这里,由于所述至少一个其它存储单元串750形成在空间751中,所以所述多条字线730可以由所述至少一个存储单元串720和所述至少一个其它存储单元串750共用。在下文,由所述至少一个存储单元串720和所述至少一个其它存储单元串750共用的所述多条字线730表示所述多条字线730用于向所述至少一个存储单元串720和所述至少一个其它存储单元串750两者提供电流。

93.根据按照实施方式的三维闪存700,由于所述多条字线730中的每条字线的接触731如所述地仅形成在所述多条字线730中的每条字线的整个区域的最小化的部分区域中,所以提供空间751,在该处形成与所述至少一个存储单元串720不布置在相同的阵列中的所述至少一个其它存储单元串750,因此,三维闪存700可以包括大量存储单元串720、750。因此,可以显著增大三维闪存700的集成度。

94.图9是根据一实施方式的制造三维闪存的方法的流程图。在下文,作为用于执行制造三维闪存的方法的主体,可以使用自动化和机械化制造系统,并且在以下描述的操作(s910至s940)中制造的三维闪存具有参照图7至图8b描述的结构。

95.参照图9,根据实施方式的制造系统在操作s910中制备在其中多条字线和多个绝缘层交替堆叠的模具结构。

96.接着,在操作s920中,在模具结构中的除了在其中将要形成所述多条字线的接触的最小化的部分区域之外的区域中,该制造系统形成在一方向上延伸的至少一个存储单元串(该至少一个存储单元串包括至少一个沟道层和围绕该至少一个沟道层的至少一个电荷存储层)。

97.例如,该制造系统可以在除了在该处将要形成所述多条字线中的每条字线的接触的最小化的部分区域之外的其余区域中形成垂直孔,使得包括在模具结构中的基板被暴露,然后可以在垂直孔中沉积至少一个电荷存储层以及在垂直孔中填充至少一个沟道层,从而形成至少一个存储单元串。

98.这里,其中将要形成所述多条字线中的每条字线的接触的最小化的部分区域可以是所述多条字线中的每条字线的整个区域中的与该接触的横截面相对应的区域,并可以是所述多条字线中的每条字线的区域上的位于相同行中的区域。

99.此外,在操作s920中,为了提供在其中将要形成与所述至少一个存储单元串不布置在相同的阵列中的至少一个其它存储单元串的空间,该制造系统可以在其余区域中形成在一方向上延伸的至少一个存储单元串、然后在一方向上在该空间中形成所述至少一个其它存储单元串。

100.因此,在操作s920中,所述至少一个其它存储单元串可以在一方向上延伸,使得所述多条字线在所述至少一个存储单元串和所述至少一个其它存储单元串之间共用。

101.如上所述,在操作s920中,该制造系统仅留下所述多条字线中的每条字线的整个区域的最小化的部分区域作为用于形成接触的区域,因此,可以在除了最小化的部分区域

之外的整个区域中形成存储单元串,从而进一步提高存储单元串的集成度。

102.接下来,在操作s930中,该制造系统以阶梯形状蚀刻其中将要形成所述多条字线中的每条字线的接触的最小化的部分区域。

103.接下来,在操作s940中,该制造系统在被蚀刻的区域中形成所述多条字线中的每条字线的接触。

104.图11是根据一实施方式的制造三维闪存的方法的流程图。图12a至图12k是用于描述根据一实施方式的制造三维闪存的方法的图。在下文,作为用于执行制造三维闪存的方法的主体,可以使用自动化和机械化的制造系统。

105.参照图11至图12k,该制造系统在操作s1110中通过将多条字线1210分成上字线组1220和下字线组1230而制备在水平方向上的堆叠的多条字线1210,如图12a所示。

106.上字线组1220和下字线组1230可以通过将具有不同水平尺寸的它们依次堆叠为阶梯形状来制备,使得其上表面1221和1231的至少部分被暴露。例如,上字线组1220和下字线组1230可以通过依次堆叠它们来分别提供,其中下字线组1230的水平尺寸大于上字线组1220的水平尺寸,使得上表面1221、1231的至少部分被暴露。

107.这里,操作s1110不仅指制备仅仅所述多条字线1210的操作,而且指制备模具结构的操作,该模具结构包括多个绝缘层1223、1233和垂直串1240,该多个绝缘层1223、1233被交替地包括在所述多条字线1210之间,该垂直串1240包括沟道层1241和电荷存储层1242。因此,上字线组1220可以包括上字线1222以及被交替地包括在上字线1222之间的上绝缘层1223,下字线组1230可以包括下字线1232以及被交替地包括在下字线1232之间的下绝缘层1233,上字线组1220和下字线组1230可以共用一个垂直串1240。

108.例如,在操作s1110中,该制造系统可以通过如图12b和图12c所示蚀刻模具结构(在其中多条字线1222、1232和多个绝缘层1223、1233交替地堆叠并且垂直串1240形成在垂直方向上)的部分1211、1212而制备如图12a所示的具有台阶形式并被分为上字线组1220和下字线组1230的所述多条字线1210。

109.作为另一示例,在操作s1110中,该制造系统可以通过如图12d和图12e所示在下模具结构(在下模具结构中,下字线1232和下绝缘层1233交替堆叠并且下垂直串形成在垂直方向上)上堆叠上模具结构(在上模具结构中,具有比下字线1232小的水平尺寸的上字线1222和上绝缘层1223交替地堆叠并且上垂直串形成在垂直方向上)而制备如图12a所示的具有台阶形式并被分为上字线组1220和下字线组1230的所述多条字线1210。

110.具体地,在操作s1110中,该制造系统可以将下字线组1230的水平尺寸确定为包括蚀刻停止距离1250以在稍后描述的操作s1130中对下字线组1230执行蚀刻操作时防止上字线组1220中的最下面的字线被蚀刻。这将在下面更详细地描述。

111.此外,在操作s1110中,该制造系统可以在上字线组1220和下字线组1230之间布置蚀刻停止保护层1260以在稍后描述的操作s1130中对上字线组1220执行蚀刻操作时防止下字线组1230中的最上面的字线被蚀刻。这也将在下面更详细地描述。

112.接下来,在操作s1120中,该制造系统在上字线组1220的上表面1221的至少一部分和下字线组1230的上表面1231的至少一部分上形成光致抗蚀剂1270、1280,如图12f所示。

113.接下来,在操作s1130中,该制造系统同时对在其上形成有光致抗蚀剂1270、1280的上字线组1220和下字线组1230执行蚀刻操作,如图12h所示。

114.这里,在操作s1130之前,该制造系统可以将光致抗蚀剂1270、1280修整等间距的宽度,将要由所述多条字线1210形成的阶梯形状将具有该等间距的宽度,如图12g所示。

115.操作s1130可以基于包括在上字线组1220中的上字线1222由此堆叠的台阶数量和包括在下字线组1230中的下字线1232由此堆叠的台阶数量而重复执行,因此,可以制造包括具有阶梯形状的字线1210的三维闪存。

116.同样地,当重复执行操作s1130时,该制造系统可以另外地重复修整光致抗蚀剂1270、1280的操作,如图12h至图12j所示,从而允许字线1210具有阶梯形状。

117.如上所述,由于下字线组1230的水平尺寸被确定为包括蚀刻停止距离1250,如图12h所示,所以当对下字线组1230执行蚀刻操作时,可以防止上字线组1220中的最下面的字线1224的错误蚀刻。

118.此外,如上所述,由于蚀刻停止保护层1260在上字线组1220和下字线组1230之间,如图12h所示,所以当对上字线组1220执行蚀刻操作时,可以防止下字线组1230中的最上面的字线1234的错误蚀刻。

119.尽管将下字线组1230的水平尺寸确定为包括蚀刻停止距离1250以及在上字线组1220和下字线组1230之间布置蚀刻停止保护层1260两者被描述为在操作s1110中执行,但是本发明构思不限于此,也可以执行它们中的任何一个。

120.当在操作s1110中仅执行将下字线组1230的水平尺寸确定为包括蚀刻停止距离1250时,完成的三维闪存如图13a所示。当在操作s1110中仅执行在上字线组1220和下字线组1230之间布置蚀刻停止保护层1260时,完成的三维闪存如图13b所示。当在操作s1110中执行将下字线组1230的水平尺寸确定为包括蚀刻停止距离1250以及在上字线组1220和下字线组1230之间布置蚀刻停止保护层1260两者时,完成的三维闪存如图13c所示。这将在下面更详细地描述。

121.接下来,在操作s1140中,该制造系统可以去除光致抗蚀剂1270、1280,如图12k所示,以完成包括具有阶梯形状的字线1210的三维闪存的制造。

122.图13a至图13c示出使用参照图11描述的制造三维闪存的方法制造的三维闪存。

123.参照图13a,根据一实施方式的三维闪存1310包括具有台阶并在以上参照图11至图12f描述的操作s1110至s1130中制造的字线。具体地,由于该制造系统在操作s1110中将下字线组的水平尺寸确定为包括蚀刻停止距离1311,当使用多条字线1320形成具有等间距宽度和等间距高度的阶梯形状时,三维闪存1310包括具有与该阶梯形状的其它部分不同的宽度的部分1321。

124.也就是,具有与其它部分不同的宽度的部分1321可以由蚀刻停止距离1311形成,以在对所述多条字线1320执行蚀刻操作的工艺中防止所述多条字线1320当中的被包括在上字线组中的最下面的字线1322的不必要蚀刻。

125.参照图13b,根据另一实施方式的三维闪存1330包括具有阶梯形状并在以上参照图11至图12f描述的操作s1110至s1130中制造的字线。具体地,由于该制造系统在操作s1110中在上字线组和下字线组之间布置蚀刻停止保护层1331,所以当使用多条字线1340形成具有等间距宽度和等间距高度的阶梯形状时,三维闪存1310包括具有与该阶梯形状的其它部分不同的高度的部分1341。

126.也就是,具有与其它部分不同的高度的部分1341可以由蚀刻保护层1331形成,以

在对所述多条字线1340执行蚀刻操作的工艺中防止所述多条字线1340当中的被包括在下字线组中的最上面的字线1342的不必要蚀刻。

127.参照图13c,根据一实施方式的三维闪存1350包括具有阶梯形状并在以上参照图11至图12f描述的操作s1110至s1130中制造的字线。具体地,由于该制造系统在操作s1110中在将下字线组的水平尺寸确定为包括蚀刻停止距离1351的同时在上字线组和下字线组之间布置了蚀刻停止保护层1352,所以当使用多条字线1360形成具有等间距宽度和等间距高度的阶梯形状时,三维闪存1350包括具有与该阶梯形状的其它部分不同的宽度的部分1361以及具有与该阶梯形状的其它部分不同的高度的部分1362。

128.具有不同宽度的部分1361可以由蚀刻停止距离1351形成以在对所述多条字线1360执行蚀刻操作的工艺中防止所述多条字线1360当中的被包括在上字线组中的最下面的字线1363的不必要的蚀刻,具有不同高度的部分1362可以由蚀刻停止保护层1352形成以在对所述多条字线1360执行蚀刻操作的工艺中防止所述多条字线1360当中的被包括在下字线组中的最上面的字线1364的不必要的蚀刻。

129.如上所述,根据本实施方式的制造三维闪存的方法,当制造包括总共六个台阶的字线的三维闪存时,仅执行两次蚀刻操作(在根据相关技术的制造三维闪存的方法中执行五次蚀刻操作),因此,可以显著减少蚀刻操作的重复次数,因此简化制造工艺。

130.尽管已经参照其示例具体地示出和描述了本发明构思,但是本领域普通技术人员将理解,在不脱离如由以下权利要求限定的本发明构思的精神和范围的情况下,可以在其中进行形式和细节上的各种改变。例如,即使当以与上述方法不同的顺序执行上述技术和/或诸如上述系统、结构、器件和电路的部件以不同于上述方法的形式被结合或组合或者被其它部件或其等同物取代或替换时,也可以获得适当的结果。

131.因此,其它实现方式、其它实施方式以及权利要求和等同物也落入以下描述的权利要求的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。