1.本发明涉及将块从被称为“供体衬底”的第一衬底转移到被称为“受体衬底”的第二衬底的方法。

背景技术:

2.在半导体领域中,半导体结构的设计有时需要将呈旨在用于生产电子组件的薄层的部分形式的块转移到载体衬底或受体衬底。

3.这种类型的方法通常称为平铺方法(tiling process),并且涉及部分地转移层以在载体衬底上形成给定图案。换句话说,载体衬底被所述层(块或片)的部分平铺(或覆盖),所述层通常是薄层。

4.薄层可以由块状晶体材料(诸如,半导体)或包括功能结构的层(外延层、无源器件等)制成。当前的示例性应用是用iii

‑

v族材料块覆盖经预处理的硅衬底,这些iii

‑

v族材料块被构造成在硅光子学平台上并入激光器件。

5.有几种技术可用于平铺载体衬底。

6.第一种技术是局部化外延,其在于通过在载体衬底上的外延生长来局部形成平铺结构。这使得可以获得薄层或甚至复杂结构。

7.该技术的主要限制在于外延结构的晶体质量,如果外延材料的晶格参数与载体衬底的晶格参数不同,则实际上该晶体质量相对较低。另一限制与相对较高的外延温度有关,相对较高的外延温度可能会损坏载体衬底中已经存在的任何电子器件。

8.第二种技术是将平铺层转移到载体衬底上,然后进行局部蚀刻平铺层的操作。转移操作可以根据smart cut

tm

方法进行,通过将离子植入平铺层以形成脆化区,然后进行分离平铺层的一部分的操作,或者通过结合,然后进行从与结合界面相反的面减薄平铺层的操作。

9.这种技术有两个主要缺点:第一,供体衬底必须与载体衬底的尺寸相同,第二,这种技术需要牺牲大量的供体衬底,当供体衬底的价值很高时这是一个问题,例如,当供体衬底由iii

‑

v族半导体材料(诸如,iii族氮化物(例如,氮化铟镓(ingan))、iii族砷化物(例如,砷化铟镓(ingaas))和iii族磷化物(例如,磷化铟镓(ingap)))制成时。

10.第三种技术(被称为“管芯到晶片”技术)基于将有用材料的部分(称为“管芯(dice)”)从供体衬底转移到受体衬底。根据该技术,将供体衬底切割成管芯,然后使用机器人将各个管芯设置在载体衬底的表面上。将此技术与smart cut

tm

方法相结合尤其可以在受体衬底上沉积材料的薄层。

11.这种技术是最通用的,特别是因为供体衬底和受体衬底可能具有不同的尺寸,但是它非常慢并且需要非常高的生产成本。

12.还有另一种技术,称为“微转移印刷”技术。

13.使用由聚二甲基硅氧烷(pdms)制成的印章,将一组电子芯片从供体衬底上提起,然后转移到受体衬底上。印章的拓扑结构使得可以在每次操作中仅拾取选定的芯片,芯片

按照印章凸起部分的分布进行分布。更具体地,印章包括多行块,各个块都旨在可拆卸地接受待转移的芯片。在转移第一组芯片的第一操作之后,第二组芯片可以通过将同一印章应用到同一供体衬底来转移,但是印章被定位在相对于第一组芯片偏移的另一组芯片上。使用将芯片或图案的蚀刻不足和机械分离组合的操作将芯片从供体衬底提起。

14.然而,分离操作可能导致供体衬底和转移的电子芯片的表面劣化,可能影响它们的操作。此外,这种技术需要牺牲大量的供体衬底,这在供体衬底具有高价值时是一个问题。此外,印章的块以给定的固定图案组织,使得转移到受体衬底的芯片必须根据印章的结构进行组织,这对于要生产的图案提供非常小的自由度。

技术实现要素:

15.本发明的一个目的是提供一种将块从供体衬底转移到受体衬底的方法,该方法允许克服上述缺点。

16.特别地,本发明的目的特别是提供这样一种方法,该方法与薄层的转移和使用高价值供体衬底兼容,并且该方法允许供体衬底的尺寸更自由,特别是使用直径小于受体衬底的供体衬底。

17.本发明的另一目的是允许供体衬底被回收和再利用,这在高价值供体衬底的情况下是非常特别有利的。

18.为此,本发明提供一种将块从供体衬底转移到受体衬底的方法,所述方法包括以下步骤:

19.‑

布置面向所述供体衬底的自由表面的掩模,所述掩模具有使所述供体衬底的所述自由表面暴露的一个或更多个开口,这些开口根据给定图案分布,以便形成所述供体衬底的所述自由表面的至少一个暴露区域以及由所述掩模覆盖的至少一个区域,

20.‑

通过穿过所述掩模的离子植入形成脆化面,所述脆化面在所述供体衬底中与所述至少一个暴露区域竖向对齐地定位,所述脆化面在所述供体衬底的厚度中界定相应的表面区域,

21.‑

形成块,所述块相对于所述供体衬底的与各个相应的脆化面竖向对齐地定位的自由表面凸起,所述块包括所述相应的表面区域,

22.‑

在已经去除所述掩模之后,经由位于结合界面处的各个块将所述供体衬底结合到所述受体衬底,

23.‑

沿着定位的各个局部脆化面分离所述供体衬底,以便将各个相应块转移到所述受体衬底。

24.在本文中,术语“竖向对齐”是指在衬底的厚度方向上(即,在垂直于衬底的主表面的方向上)面向另一区域定位的区域。术语“竖向对齐地定位”是指在平行于衬底主表面的方向上由另一区域的范围界定的区域;换句话说,与另一区域竖向对齐地定位的区域不在平行于衬底的主表面的方向上延伸超过所述另一区域。

25.因此,特别地,在本方法中,通过在平行于供体衬底的主表面的方向上由相应的脆化面界定来在供体衬底中单个化各个块。这允许将各个块局部转移到受体衬底。

26.根据其它方面,所提出的方法具有以下多个特征,这些特征可以单独实现或以其技术上可行的组合实现:

27.‑

根据所述方法:

28.‑

在同一供体衬底上重复一次或更多次布置所述掩模、离子植入和形成各个块的步骤,以便形成至少第二图案,所述第二图案相对于被称为第一图案的先前图案偏移,以及

29.‑

重复去除所述掩模、结合和分离的步骤,以便将各个块从所述供体衬底转移到同一受体衬底或不同的受体衬底;

30.‑

为了形成所述第二图案,所述掩模被布置成覆盖由各个先前转移的块在所述供体衬底的厚度中留下的凹部;

31.‑

根据所述方法:

32.‑

在至少第二供体衬底上重复一次或更多次布置所述掩模、离子植入和形成各个块的步骤,以便形成至少第二图案,以及

33.‑

重复去除所述掩模、结合和分离的步骤,以便将各个块从所述第二供体衬底转移到同一受体衬底或不同的受体衬底;

34.‑

形成各个块的操作包括以下操作:在离子植入的作用下使所述供体衬底的材料从所述供体衬底的所述自由表面膨胀;

35.‑

形成各个块的操作包括以下操作:通过相应开口在所述供体衬底的所述自由表面上沉积附加层;

36.‑

沉积所述附加层的操作是在离子植入后在200℃至250℃之间的温度下执行的;

37.‑

所述方法还包括表面处理,所述表面处理旨在使转移的块的暴露表面平坦并降低其粗糙度;

38.‑

结合所述块的操作伴随有对所述供体衬底和所述受体衬底进行热退火的操作;

39.‑

分离所述供体衬底的操作是以热或机械的方式通过施加机械应力而发起的,以便将所述供体衬底与所述受体衬底分开;

40.‑

所述方法还包括以下步骤:在转移所述块之后通过处理所述供体衬底的所述自由表面以便使所述供体衬底平坦并降低其粗糙度来回收所述供体衬底;

41.‑

所述受体衬底由硅制成,并且所述供体衬底的块由iii

‑

v族半导体材料制成。

附图说明

42.参考以下附图,在阅读通过例示性和非限制性示例的方式给出的以下描述后,本发明的其它优点和特征将变得显而易见:

43.‑

图1a、图1b、图1c、图1d、图1e、图1f、图1g、图1h、图1i和图1j例示了根据一个实施方式的将块从供体衬底转移到受体衬底的方法;

44.‑

图2a、图2b、图2c、图2d和图2e例示了供体衬底的再利用;

45.‑

图3例示了从上方观察的将块从供体衬底转移到受体衬底的第一操作;

46.‑

图4例示了从上方观察的将块转移到另一受体衬底同时重复使用来自图3的供体衬底的第二操作;

47.‑

图5例示了供体衬底的回收;

48.‑

图6、图7、图8和图9例示了在供体衬底的直径小于受体衬底的直径的情况下根据不同图案布置的转移块的操作。

具体实施方式

49.本发明涉及将块从供体衬底转移到受体衬底的方法。该方法允许通过将一个或更多个块转移到受体衬底来制造半导体结构。优选地,受体衬底由硅制成。

50.块采用供体衬底的薄层的多个部分的形式,所有这些块被转移到受体衬底,并且在这些块上可以制造电子组件,或者在这些块中已经形成无源或有源电子组件。具体地,薄层可以由块状晶体材料(诸如,半导体)或包含功能结构的层(外延层、外延层的堆叠、无源或有源器件等)制成。这些块在受体衬底上形成给定图案。块可以例如由iii

‑

v族半导体材料制成。

51.除了所述薄层的一部分之外,块还可以包括附加层,在转移到受体衬底之前,该附加层通过在供体衬底的薄层的所述部分上沉积或外延来形成。

52.一般来说,转移方法是基于当供体衬底结合至受体衬底时,块相对于供体衬底表面的其余部分凸起。因此,供体衬底与受体衬底之间的粘附仅在块处发生。对于该目的,约10nm的高度相对增加被认为是足够的。

53.如下面将进一步详细描述的,存在用于产生这种高度相对增加的各种手段。特别地,这种高度的相对增加可以通过增加供体衬底的薄层的该部分的厚度(通过使所述层的材料膨胀和/或通过在旨在形成块的各个部分上局部沉积或外延附加层)和/或通过去除块周围的供体衬底的表面区域来产生。

54.在图1a至图1j中例示了转移方法的一个实施方式。参考图1a,最初提供称为供体衬底的衬底1,在衬底1中,将形成待转移的块。掩模2被布置成面向供体衬底的自由表面3。

55.根据图1b所示的第一实施方式,例如通过沉积掩模,将掩模2布置在供体衬底的自由表面3上并与供体衬底的自由表面3接触。掩模2可以是例如基于氧化物或氮化物的树脂或固体掩模。

56.掩模2具有暴露供体衬底的自由表面3的一个或更多个开口4。开口4根据与待形成的块的图案10对应的给定图案分布。该步骤因此被称为“图案化”,是指图案的形成。

57.由此形成由掩模覆盖的一个或更多个区域5,这些区域由开口4界定,开口4对应于使供体衬底的自由表面3暴露的未覆盖区域。

58.该形成图案的步骤可以通过除了上述手段的其它手段执行,例如通过平版印刷术或通过印刷。

59.另选地,根据图1i所示的第二实施方式,掩模2是不固定到供体衬底的固体掩模。掩模被构造成形成图案10,并且掩模可以是例如离子植入掩模。根据该实施方式,掩模2被设置在距供体衬底的自由表面3给定距离处。当试图防止与供体衬底的自由表面相互作用以便不改变其物理和/或化学性质时,该第二实施方式是有利的。另外,该实施方式通过省略在供体衬底上布置掩模的步骤而简化了根据本发明的方法。

60.图1c和图1d例示了该方法的后续步骤,其中,示出了被定位在供体衬底的自由表面上并与供体衬底的自由表面接触的掩模2。然而,这些步骤可以通过将掩模定位在距供体衬底的自由表面一距离处来执行。

61.参考图1c,衬底的自由表面3接下来通过掩模2暴露于一束离子物质6。

62.离子物质经由开口4渗入供体衬底1,并以由植入参数确定的深度植入供体衬底的下层区域。离子物质在供体衬底中形成局部脆化面7,在图1c中用虚线表示。各个脆化面7面

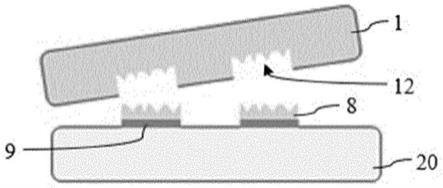

向掩模中的相应开口4定位,并且与自由表面3一起界定衬底厚度中的表面区域8。

63.遇到掩模2的那些离子物质被所述掩模阻挡并且不穿透到供体衬底1中。

64.优选地,植入的离子物质是氢离子和/或氦离子。本领域技术人员能够确定植入参数,特别是离子物质的性质、物质的剂量和能量,以便将离子物质按照期望的深度植入到供体衬底中。

65.另外,各个表面区域8相对于供体衬底的自由表面3凸起,以便形成相对于所述表面3具有增加的高度的相应块9。

66.根据第一实施方式(未例示),在离子植入之前,在单独的步骤中执行形成块9的操作。换句话说,表面区域8凸起,然后对凸起的表面区域8进行离子植入。

67.为此,例如可以通过掩模中的相应开口4在各个表面区域的自由表面上沉积附加层。在适于避免供体衬底变性的温度下沉积附加层。附加层的沉积温度还取决于供体衬底的材料和待转移块的材料。

68.附加层的材料被选择成允许块被结合到受体衬底。因此,附加层的材料是结合材料,优选地选自:sio2、si3n4、金属或非晶硅。

69.另选地,可以从表面区域8执行外延以形成块。

70.根据图1d所示的第二实施方式,在离子植入之后,在单独的步骤中执行形成块9的操作。换句话说,已经进行了离子植入的表面区域8凸起。

71.为此,例如可以通过掩模中的相应开口4在各个表面区域的自由表面上沉积附加层。在低于植入离子的熟化温度(maturation temperature)的温度(即,低于250℃、优选在200℃至250℃之间的温度)下沉积附加层。附加层的沉积温度还取决于供体衬底的材料和待转移块的材料。

72.另选地,可以从表面区域8执行外延以形成块。

73.在这两个实施方式中,各个块由表面区域8和附加层组成。另外,当沉积掩模时,有利地从相对于植入和相对于沉积/外延执行掩模功能的材料中选择。因此,单个掩模足以形成块,这最小化了方法中的步骤数并避免了当使用多于一个掩模时可能遇到的对准缺陷。

74.根据图1j所示的第三实施方式,形成块9的操作与离子植入同时执行。换句话说,通过在离子植入的作用下使供体衬底1的材料从所述供体衬底的自由表面3膨胀而形成各个凸起的块。具体地,已知例如硅的离子植入通常导致材料的膨胀并因此导致植入表面的高度增加。这种膨胀可达到几纳米或几十纳米。由于膨胀引起的植入表面高度的增加取决于植入条件,特别是取决于植入的物质、剂量和植入能量。

75.根据第四实施方式,可以不仅通过蚀刻先前沉积在供体衬底上的掩模,而且通过按照对应于期望的高度增加的厚度蚀刻供体衬底的表面区域来间接地使表面区域凸起。

76.第一示例包括在先前布置的掩模(称为第一掩模)的顶部上布置第二掩模。第二掩模与第一掩模互补,即第二掩模覆盖由第一掩模界定的开口,但不覆盖由第一掩模覆盖的区域。接着,在由第一掩模覆盖的所述区域中蚀刻第一掩模以及供体衬底的表面区域。第二示例包括在掩模的开口中沉积牺牲材料层,然后选择性地蚀刻掩模,牺牲材料保护旨在形成块的区域。在先前由掩模覆盖的区域中,继续蚀刻到供体衬底的厚度中,以便在供体衬底的厚度中形成界定牺牲材料层的腔。接着,去除牺牲材料以使块的表面暴露,然后使其相对于供体衬底的蚀刻表面凸起。

77.前述实施方式中的所有或一些实施方式可以被组合。

78.例如,可以在各个表面区域的自由表面上沉积附加层,然后通过该附加层执行离子植入以形成表面区域8,并且使表面区域8凸起,以便形成凸起的块9。

79.根据另一示例,可以执行离子植入以同时形成块9,然后在离子植入之后进一步使块9凸起。

80.在去除掩模2之后,所获得的是具有块9的供体衬底1,所述块9相对于供体衬底1的自由表面(原始的或由蚀刻产生的,视情况而定)凸起,该自由表面用于将这些块9中的全部或一些块转移到一个或更多个受体衬底20。图1f、图1g和图1h例示了块转移方法的一个实施方式。

81.参考图1f,供体衬底1结合到受体衬底20。

82.供体衬底1和受体衬底20首先面对彼此定位。经由形成结合界面的块9执行结合。更具体地,结合仅发生在块9处。供体衬底1的自由表面的先前被掩模2覆盖的区域6远离受体衬底20。

83.然后沿着脆化面7分离供体衬底1,如图1g所示。发起断裂,然后在脆化面的部位处扩展,根据定义,脆化面是衬底的较弱区域。供体衬底1的块9因此被转移到受体衬底20。断裂可以通过将衬底组件加热到给定温度而自发地触发,和/或可以通过向供体衬底施加机械应力来触发。

84.假定供体衬底1在脆化面7的部位处断裂,块9的表面区域8的自由表面3(其相对于块9与受体衬底20相对)通常表现出高的粗糙度。因此,优选地,例如通过化学机械抛光(cmp)或化学和/或热处理,对各个转移的表面区域的所述自由表面进行处理,以便使其光滑并降低其粗糙度。

85.获得的受体衬底20在图1h中示出。获得的受体衬底20包括块9,块9包括表面区域8,表面区域8的自由表面3优选地被处理。

86.本发明的方法使得在完成结合步骤和分离步骤之后,可以在该方法的单次迭代中将图案10的所有组成块9从供体衬底1转移到受体衬底20,相对于已知方法,这减少了生产时间并因此降低了以这种方式制造的半导体结构的生产成本。

87.本发明方法的一个优点在于可以不止一次使用同一供体衬底,而无需将其回收。

88.供体衬底的再利用和回收是两个不同的方面,现在将在下面描述。

89.供体衬底1的再利用包括上述步骤的一次或更多次附加迭代。换句话说,沉积掩模2和形成各个块的步骤在同一供体衬底上,在供体衬底的未在方法的第一次迭代中使用的区域中重复一次或更多次,以便形成至少第二图案10b,第二图案10b相对于称为第一图案10a的先前图案偏移(参见图3和图4)。也重复去除掩模2、结合和分离的步骤,以便将各个块9a从供体衬底1转移到同一受体衬底20或不同的受体衬底。

90.在图2a至图2e中示意性地示出了一个实施方式,该实施方式示了在从图1g中的受体衬底20分离之后获得的供体衬底1的再利用。

91.图2a例示了待再利用的供体衬底1。掩模2被布置成面向供体衬底的自由表面3。

92.掩模2具有使供体衬底的自由表面暴露的一个或更多个开口4。开口4根据给定的第二图案10b分布,第二图案10b对应于将在所述供体衬底上形成的块图案。该第二图案10b在供体衬底的自由表面3的平面中相对于先前在该方法的第一次迭代中形成的第一图案

10a偏移。

93.掩模2可以根据掩模被布置在供体衬底的自由表面3上并且与供体衬底的自由表面3接触的上述第一实施方式来布置,或者根据掩模被布置成距供体衬底的自由表面给定距离的上述第二实施方式来布置。

94.无论使用哪个实施方式来布置掩模,掩模2优选地被布置成覆盖由各个先前转移的块9b留在供体衬底1的厚度中的凹部12,如图2b所示。

95.参考图2c,沉积有掩模2的供体衬底的自由表面3然后暴露于一束离子物质。因此在供体衬底中形成脆化面7,在图2c中由虚线示意性地表示。各个脆化面7面向掩模中的相应开口4定位,并且与衬底的自由表面界定表面区域8。

96.各个表面区域8相对于供体衬底的自由表面3凸起,以便形成根据第二图案10b布置的相对于所述表面3具有增加的高度的一个或更多个块9b。

97.有利地根据一个实施方式或上述实施方式的组合,以类似于第一图案的方式实现高度的增加。

98.一旦形成了块9b,就获得图2d所示的供体衬底1,该供体衬底1包括由掩模覆盖的区域5和第二块图案10b。

99.在去除掩模2之后,图2e中所示的供体衬底1用于将第二块图案10b转移到与之前在方法的第一次迭代中相同的受体衬底20,或者转移到不同的受体衬底。

100.图3和图4例示了一个且相同的供体衬底的再利用,以将多个块图案转移到不同的受体衬底。

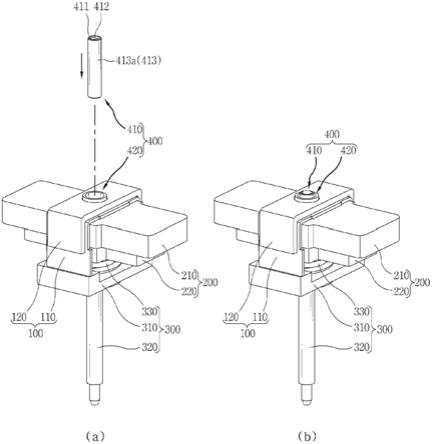

101.参考图3,在供体衬底1上形成第一块图案10a,然后通过将块9a结合到受体衬底20的自由表面3并且然后分离供体衬底,来将所述块图案10a转移到受体衬底20。所获得的是具有转移的块9a的图案的受体衬底20,以及具有来自所述转移的块9a的凹部12a的供体衬底1,所述凹部12a从所述供体衬底的自由表面延伸到其厚度中。

102.参考图4,并且仅作为示例,通过相对于垂直于衬底的自由表面的轴将同一供体衬底1枢转180

°

来再利用它,并且在其中形成第二块图案10b。第二块图案10b在衬底的自由表面3的平面中相对于第一图案10a偏移,并且与第一图案类似地形成。通过将块9b结合到受体衬底的自由表面上并且然后分离供体衬底,来将第二块图案10b转移到不同于前述受体衬底的受体衬底20上。所获得的是具有第二转移的块图案10b的受体衬底20以及具有来自转移的第一块图案10a和第二块图案10b的凹部12b的供体衬底1,该凹部12b从所述供体衬底的自由表面延伸到其厚度中。

103.图4的实施方式例示了在多个连续的转移操作中不止一次再利用同一供体衬底而不必回收它的可能性。

104.根据另一实施方式,图案10b可以被转移到已经包括不干扰图案10b的图案10a或另一图案的受体衬底20。

105.回收供体衬底1包括处理其先前用于转移块图案的自由表面3,以便在将块9转移到受体衬底20之前去除包括块9的损坏区域。供体衬底的自由表面基本上是平坦的,并且相对于其回收之前的状态表现出减小的粗糙度。以这种方式,重建了供体衬底的表面状态,该表面状态与在本发明的转移方法中使用供体衬底之前的状态相当。

106.通过限制浪费,回收允许最大限度地利用整个供体衬底,当供体衬底具有高价值

时,例如当它由iii

‑

v族半导体材料制成时,这是非常特别有利的。

107.回收是可能的且有利的,因为离子植入和分离仅消耗衬底厚度中的小材料层。

108.适于回收供体衬底的表面处理是化学机械抛光/平面化(cmp)。

109.在图5a、图5b和图5c中示意性地示出了一个实施方式,该实施方式示了在从图1g中的受体衬底20分离之后获得的供体衬底1的回收。

110.图5a例示了待回收的供体衬底1。参考图5b,接着将平滑器件30的平坦表面31施加到供体衬底的受损自由表面3,然后在垂直于衬底平面的轴上旋转该器件,以便平滑所述自由表面。平滑后获得的供体衬底1如图5c所示。

111.当然,为了执行根据本发明的转移方法的多次迭代,可以组合回收和再利用。例如,供体衬底可以在多次再利用之后回收以转移若干块图案。所述衬底然后可以再利用于该方法的一个或更多个其它迭代,然后再次回收。

112.图6至图9例示了根据本发明的转移方法的多次迭代中的块转移。四个不同的图案10a、10b、10c和10d通过对每次转移使用不同的供体衬底而转移到同一受体衬底上。供体衬底1a、1b、1c和1d都具有基本上相同的直径,该直径小于受体衬底20的直径。

113.因为供体衬底的直径小于受体衬底的直径,所以它允许所有块在单次转移中从各个供体衬底转移到受体衬底的自由表面的给定区域。因此,通过组合由本发明的方法的若干连续迭代所转移的多个块图案,可以构造最终的块图案。

114.根据另一实施方式,该方法还使得可以从不同衬底转移块,以便将不同性质或具有不同功能的块转移到受体衬底。

115.参考图6,在第一供体衬底1a上形成第一块图案10a,然后将所述块图案转移到受体衬底的自由表面的给定第一区域。当结合时,供体衬底1a被面向受体衬底20定位,使得所有块9a与受体衬底的自由表面3接触并被转移到所述受体衬底。在图6中,供体衬底1a稍微延伸超过受体衬底20的外围。

116.一旦转移完成,受体衬底的自由表面在第一区域中被第一转移块图案10a部分地覆盖。

117.参考图7,在第二供体衬底1b上形成第二块图案10b,然后将该第二块图案10b转移到同一受体衬底20的自由表面的给定第二区域。转移到受体衬底的第二图案10b与第一图案10a互补,使得第二图案10a的块9a的行和列分别至少部分地与第一图案10b的行和列互补。在图7中,供体衬底1b稍微延伸超过受体衬底20的外围。

118.参考图8,在第三供体衬底1c上形成第三块图案10c,然后将该第三块图案10c转移到同一受体衬底20的自由表面的给定第三区域。转移到受体衬底的第三图案10c与第一图案10a和第二图案10b互补,使得第三图案10c的块的行和列分别至少部分地与第一图案10a和第二图案10b的行和列互补。在图8中,供体衬底1c延伸超过受体衬底20的外围。

119.参考图9,在第四供体衬底1d上形成第四块图案10d,然后将该第四块图案10d转移到同一受体衬底20的自由表面的给定第四区域。转移到受体衬底的第四图案10d与第一图案10a、第二图案10b和第三图案10c互补,使得第四图案10d的块9d的行和列分别至少部分地与第一图案10a、第二图案10b和第三图案10c的行和列互补。在图9中,供体衬底1d延伸超过受体衬底20的外围。

120.一旦完成了四个转移步骤,就在受体衬底20上形成最终的块图案11,该最终的块

图案11由连续转移的四个块图案10a、10b、10c和10d组成。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。