1.本发明涉及一种用于在混合集成方法中与硅平台一起使用的装置试样(device coupon)、包括所述装置试样的光电装置、制造装置试样的方法、制造光电装置的方法以及通过所述方法制造的光电装置。

背景技术:

2.基于iii

‑

v半导体的电光装置(例如,调制器)与硅平台(例如,绝缘体上硅平台)通过芯片结合进行的混合集成具有组合两种材料系统的最佳部分的优势。即,基于iii

‑

v半导体的电光装置通常比基于硅的装置快,而基于硅的装置更易于制造并且具有更高的制造良率。

3.先前在混合集成方面的努力导致装置具有非常高的光学损耗,这限制了它们的潜在应用。

技术实现要素:

4.因此,总的来说,本发明的实施方案提供一种装置试样,其中包含电光装置的波导与一个或多个无源波导分开。

5.在第一方面,本发明的实施方案提供一种用于在混合集成方法中与硅平台一起使用的装置试样,所述装置试样包括:

6.输入波导,所述输入波导包括输入小面;

7.有源波导,所述有源波导耦合到所述输入波导,所述有源波导包括基于iii

‑

v半导体的电光装置;以及

8.输出波导,所述输出波导被配置来在所述有源波导与输出小面之间耦合光;

9.其中所述输入波导和所述输出波导是无源波导。

10.有利地,通过提供耦合到所述有源波导的迥异的无源波导,使用所述装置试样制造的光电装置具有较低的光学损耗。此外,本发明的实施方案允许所述有源波导与soi波导之间的iii

‑

v rf带宽和光学耦合损耗解耦。换句话说,有源波导与soi波导之间的iii

‑

v rf带宽和光学耦合损耗可分开设计,使得rf带宽和光学耦合损耗两者可单独地优化。例如,可将有源波导的光路长度保持为最小值(即,仅装置功能所需的光路长度),因此可使传输损耗最小化。

11.所谓有源波导,是指波导包含一个或多个电光有源装置。即,除传输损耗之外还影响通过它的光的装置。例如,包含调制器(相位或振幅)的波导或光电二极管将是有源波导。相反,所谓无源波导是指不包含一个或多个电光有源装置因此仅以无源方式(例如通过传输损耗)影响通过它的光的波导。无源波导可由以下形成:alingaas、ingaasp、alinas或折射率大于inp的折射率且带隙等于或超过1.1ev的另一种iii

‑

v半导体材料。

12.所述装置试样可具有以下任选特征中的任何一个或在它们兼容的范围内的任何组合。

13.所述输入波导和所述输出波导中的一者或两者可包含弯曲部。通过在所述输入波导和所述输出波导中的一者或两者中提供弯曲部,可使光学损耗最小化,因为所述弯曲部的几何形状可被优化的程度超出所述弯曲部包含在有源波导内的情况下所能达到的程度。

14.在一些实例中,所述输入波导和所述输出波导中的仅一者包含弯曲部。在此类实例中,弯曲部可描述180

°

弧,因为离开弯曲部的光以与进入弯曲部的光反平行的方向行进。

15.在一些实例中,所述输入波导和所述输出波导两者都包含相应弯曲部。在此类实例中,每个弯曲部可描述90

°

弧。所述有源波导可位于所述两个弯曲部之间,因此离开所述装置试样的光可以与进入所述装置试样的光反平行的方向行进。

16.所述弯曲部的宽度可小于所述有源波导的宽度。在光传输通过弯曲部时,这种弯曲部可进一步减少光学损耗。在一些实例中,所述弯曲部具有不超过1μm的宽度。

17.所述输入波导和所述输出波导中的一者或两者可由iii

‑

v半导体形成。

18.所述有源波导可由iii

‑

v半导体形成。

19.所述输入波导和所述输出波导中的一者或两者可包括模式转换器,所述模式转换器被配置来转换从中传输通过的光的光学模式。所述光学模式由此可得以优化以使通过装置的损耗最小化。

20.所述基于iii

‑

v半导体的电光装置可以是电吸收调制器。例如,所述装置可以是利用量子约束斯塔克效应或弗朗兹

‑

凯尔迪什效应的振幅调制器。

21.有源波导可以是具有直线几何形状的直波导。这可进一步减少光学损耗,因为直波导的损耗通常比弯曲波导的损耗小。

22.有源波导的光路长度可小于输入波导和/或输出波导的光路长度。由于有源波导通常具有比无源波导高的传输损耗,因此通过使有源波导的光路长度最小化,可减少传输损耗。

23.输入小面和输出小面可位于装置试样的同一横向侧上。因此,连接到装置试样和从装置试样连接的硅平台中的波导可以在空间上相邻,这可减少光电装置的总体占用面积。

24.所述装置试样可包括设置在所述装置试样的一个或多个横向侧之上的抗反射涂层。此抗反射涂层具有两个优点:(i)从硅平台到装置试样中的耦合损耗减少;以及(ii)在混合集成过程中保护装置试样,因此装置良率提高。

25.所述装置试样可包括第一接触焊盘和第二接触焊盘,每个接触焊盘可电连接到所述电光有源装置中的相应层。通过在所述装置试样上提供所述接触焊盘,可避免另外的制造步骤。

26.所述输入小面和/或所述输出小面可以是丁字架小面。已经发现,当将光从硅平台中的波导耦合到输入波导和/或输出波导时,丁字架小面可进一步减少光学损耗。

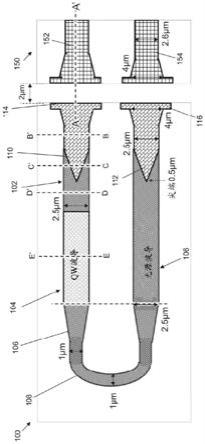

27.输入波导和/或输出波导可具有不超过4μm的宽度。已经发现该尺寸可进一步减少传输损耗。

28.在第二方面,本发明的实施方案提供一种光电装置,所述光电装置包括硅平台和第一方面的装置试样,其中

29.所述装置试样结合到所述硅平台;

30.所述装置试样的所述输入波导通过所述输入小面耦合到所述硅平台的输入波导;

并且

31.所述装置试样的所述输出波导通过所述输出小面耦合到所述硅平台的输出波导。

32.已经发现这种光电装置相比由其他装置试样形成的光电装置具有更低的光学损耗。

33.第二方面的装置试样可具有第一方面的任选特征中的任何一个,或在它们兼容的范围内的任何组合。

34.在第三方面,本发明的实施方案提供一种制造用于在混合集成方法中与硅平台一起使用的装置试样的方法,所述方法包括以下步骤:

35.生长基于多层iii

‑

v半导体的堆叠;

36.从所述堆叠制造有源波导,所述有源波导包括基于iii

‑

v半导体的电光有源装置;

37.在所述堆叠上制造输入波导,所述输入波导被配置来在输入小面与所述有源波导之间耦合光;以及

38.在所述堆叠上制造输出波导,所述输出波导被配置来在所述有源波导与输出小面之间耦合光;

39.其中所述输入波导和所述输出波导是无源波导。

40.有利地,通过与所述有源波导分开地制造所述无源波导,使用所述器件试样制造的光电装置具有较低的光学损耗。

41.所述方法可具有以下任选特征中的任何一个或在它们兼容的范围内的任何组合。

42.所述基于iii

‑

v半导体的电光装置可包括多个iii

‑

v半导体层。层可包含多量子阱。

43.制造所述输入波导和/或所述输出波导可包括以下步骤:蚀刻掉所述堆叠的一部分,并且从所述堆叠的暴露表面外延生长所述输入波导和/或所述输出波导。

44.制造所述有源波导可包括:蚀刻掉所述堆叠的一个或多个部分,以便限定所述有源波导。

45.在第四方面,本发明的实施方案提供一种制造光电装置的方法,所述方法包括:将第一方面的装置试样结合到硅平台。

46.第四方面的装置试样可具有第一方面的任选特征中的任何一个或在它们兼容的范围内的任何组合。

47.所述方法可包括倒装芯片结合工艺。

48.所述方法可包括微转移印刷工艺。

49.在第五方面,本发明的实施方案提供一种通过第四方面的方法制造的光电装置。

50.本发明的另外的方面提供:一种计算机程序,所述计算机程序包括代码,所述代码当在计算机上运行时致使所述计算机执行第三方面或第四方面的方法;一种计算机可读介质,所述计算机可读介质存储包括代码的计算机程序,所述代码当在计算机上运行时致使所述计算机执行第三方面或第四方面的方法;以及一种计算机系统,所述计算机系统被编程来执行第三方面或第四方面的方法。

附图说明

51.现将通过实例参考附图来描述本发明的实施方案,在附图中:

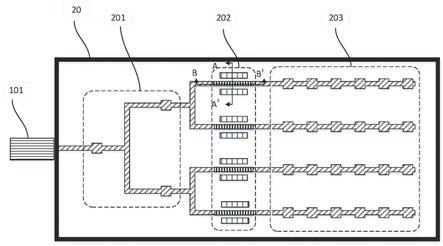

52.图1示出微转移印刷工艺中所使用的装置试样以及硅平台的俯视图;

53.图2a至图2e分别是沿线a

‑

a'、b

‑

b

′

、c

‑

c

′

、d

‑

d

′

和e

‑

e

′

的图1的装置试样的剖视图;

54.图3示出在倒装芯片工艺中使用之后的具有蚀刻小面的图1的装置试样的俯视图;

55.图4示出在倒装芯片工艺中使用之后的具有切割小面的变体装置试样的俯视图;

56.图5a至图5e分别是沿线a

‑

a

′

、b

‑

b

′

、c

‑

c

′

、d

‑

d

′

和e

‑

e

′

的图3和图4的装置试样的剖视图;

57.图6a和图6b分别示出变体装置试样;

58.图7示出装置试样的输入波导的模拟的结果;

59.图8示出装置试样的输入波导的模拟的结果;

60.图9示出模拟输入波导的示意性剖面;

61.图10示出连接到硅平台中的硅波导的模拟输出波导;

62.图11是示出当输出波导和硅波导具有3μm的高度时,作为波长的函数的耦合损耗的曲线图;

63.图12是示出当输出波导和硅波导具有1.8μm的高度时,作为波长的函数的耦合损耗的曲线图;

64.图13(i)(a)至图13(xix)(b)示出装置试样的各种制造步骤;

65.图14(a)和图14(b)分别示出用于在倒装芯片结合工艺中使用的包含eam的装置试样的剖面和俯视图;并且

66.图15(a)和图15(b)分别示出用于在倒装芯片结合工艺中使用的包含eam的变体装置试样的剖面和俯视图。

具体实施方式

67.现在将参考附图论述本发明的方面和实施方案。另外的方面和实施方案对于本领域技术人员而言将是显而易见的。

68.图1示出微转移印刷工艺中所使用的装置试样100以及硅平台150的俯视图。装置试样包括输入波导102、有源波导104和输出波导106。输入波导和有源波导耦合,有源波导和输出波导也是如此。输出波导包括弯曲部108,使得光从同一横向侧进入和离开装置试样。

69.输入波导102耦合到输入小面114,所述输入小面114存在于试样100的横向侧上。输出波导106耦合到输出小面116,所述输出小面116位于与输入小面114相同的横向侧上。输入波导和输出波导各自包括相应的模式转换器110和112。在从硅平台150的输入波导152传输的光从输入小面114传递到输入波导102时,光从4μm光学模式转换为2.5μm光学模式(在此实例中)。类似地,在光从输出波导106传递到输出小面116时,光从2.5μm光学模式转换为4μm光学模式,以用于传输到硅平台150中的输出波导154。

70.因此,在使用中,光从硅平台150的输入波导152横跨约2μm的间隙进行传输。光通过输入小面114进入装置试样100,并且由包含在输入波导102内的模式转换器110进行转换。然后,光被耦合到有源波导104中,所述有源波导104包含一个或多个基于iii

‑

v半导体的装置。现在调制的光离开有源波导进入输出波导106中。输出波导包含与有源波导相邻的锥形区域,所述锥形区域的宽度从2.5μm逐渐变窄到1μm。然后,光进入输出波导内的弯曲部

108,所述弯曲部描述180

°

弧。然后,输出波导与输入和输出波导平行运行,并且光进入输出波导模式转换器112。模式转换器扩大光的模式,使得其被有效地从硅平台的输出小面116耦合到输出波导154。

71.图2a至图2e分别是沿线a

‑

a'、b

‑

b

′

、c

‑

c

′

、d

‑

d

′

和e

‑

e

′

的图1的装置试样的剖视图。如图2a所示,硅平台150包括硅衬底202(装置试样结合到硅衬底202)。在硅衬底上方是掩埋氧化物204,在一些实例中是sio2。在掩埋氧化物层上方的是高度可为3μm或1.8μm的绝缘体上硅波导206。在硅波导与alingaas无源输入波导216之间的是以下层:第一抗反射涂层208;苯并环丁烯填料210;以及第二抗反射涂层212。这些层具有约2μm的组合深度(即,从soi波导206到alingaas波导216)。alingaas波导216在下表面(即,最靠近硅衬底202的一个表面)上由inp底部覆层214界定,并且在上表面上由inp上覆层218界定。同样,alingaas波导216的高度为3μm或1.8μm。

72.图2b是沿图1的b

‑

b

′

线的剖面图。图从前方视角示出无源alingaas波导216,因为光被引导进/出图的平面。可以看出,alingaas波导216具有约2.5μm的宽度。这是在波导从与丁字架输入小面相邻的4μm处横向逐渐变窄之后的宽度。模式转换器110的剖面图在图2c中示出,并且示出波导216的宽度从约2.5μm至约0.5μm的变化。波导的模式转换器部分由与inp层214相邻且具有约600nm高度的下平板区域和具有约2.4μm或1.2μm高度的直立脊或肋区域形成。输入波导216的在模式转换器110和有源波导104之间的区域在图2d中示出。可以看出,此时沿输入波导,该区域具有约600nm的高度和约2.5μm的宽度。

73.最后,图2e示出有源波导104的剖视图。有源波导包括电光有源装置220,所述电光有源装置220包括多个基于iii

‑

v半导体的层。紧邻inp底部覆层214的是n掺杂inp层222。接下来,从inp底部覆层移开的是iii

‑

v半导体量子阱层224并且在其上方的是p掺杂inp或其他基于iii

‑

v半导体的层226。同样,有源波导具有约2.5μm的宽度。

74.应当注意,虽然图2a、图2b、图2c和图2d是通过输入波导(soi和装置试样)的剖视图,但是这些剖视图有效地反映在输出波导(soi和装置试样)中。

75.图3示出在倒装芯片工艺中使用之后的具有蚀刻小面的图1的装置试样的俯视图。在该图中,标识了与装置试样的各种区域相关联的损耗。对于3μm波导系统(即,其中与小面114、116相邻的soi波导和无源波导102、106的高度为3μm的系统),横跨soi芯片与装置试样之间的2μm间隙的单向耦合损耗约为0.4db。对于1.8μm波导系统,间隙可减小到约1.5μm,并且单向损耗约为0.7db。每个模式耦合器110、112各自引发另外的0.1db,并且有源波导引发3.0db的损耗。弯曲损耗约为0.3db,并且对于输入波导和输出波导中的每一者,各种模式失配引发另外的0.1db。各种波导中由于散射造成的总损耗共计为0.5db。

76.因此,对于3μm波导系统,从soi芯片通过装置试样并且传递回的光的总损耗共计为:(0.1db

×

2) 0.3db 3.0db (0.1db

×

2) (0.4db

×

2) 0.5db=5.0db。类似地,对于1.8μm波导系统,从soi芯片通过装置试样并且传递回的光的总损耗总计为:(0.1db

×

2) 0.3db 3.0db (0.1db

×

2) (0.7db

×

2) 0.5db=5.6db。

77.图4示出倒装芯片工艺中所使用的具有切割小面的变体装置试样400的俯视图。在变体装置试样400与图1和图3中所示的试样100共享特征的情况下,相似特征由相似附图标号表示。主要地,试样400与先前示出的试样的不同之处在于,其输入小面402与输出小面404是切割的而不是蚀刻的。相应地,从soi芯片往返装置试样的单向耦合损耗减少到小于

0.4db。

78.图5a至图5e分别是沿线a

‑

a

′

、b

‑

b

′

、c

‑

c

′

、d

‑

d

′

和e

‑

e

′

的图3和图4的装置试样的剖视图。如图5a所示,倒装芯片结合装置试样中的alingaas波导216与soi波导206对齐。然而,与先前示出的装置相比,波导216在上侧上由inp衬底502界定。由于装置试样在结合之前已经翻转,因此衬底(先前位于装置试样的底部上)现为最上层。类似地,图5b至图5e所示的元件相对于图2b至图2e所示的相同元件旋转了180

°

。因此,例如,模式转换器具有在脊或肋部分上方(即,与之相比离衬底更远)的600nm平板部分。类似地,电光有源装置具有下部p掺杂inp/iii

‑

v层224以及上部n掺杂inp层222。将了解,为了清晰起见,图5a至图5e中已经省略了各种支撑结构和金属结合结构。

79.同样,应当注意,虽然图5a至图5c是穿过输入波导102的剖面,但这些剖面有效地反映在输出波导106中。

80.图6a和图6b分别示出变体装置试样600和650。在这些试样与先前示出的试样共享特征的情况下,相似特征由相似附图标号表示。主要地,两个装置试样600和650与先前示出的那些试样的不同之处在于,输入波导102和输出波导106中的每一者具有相应弯曲部。输入波导102具有描述90

°

弧的输入波导弯曲部602。与图1、图3和图4中示出的试样相比,输入波导102耦合到现在垂直于输入小面和输出小面延伸的有源波导104。输出波导106也包含也描述90

°

弧的输出波导弯曲部604。然后如之前一样,光通过装置试样的同一横向侧进入和离开装置。图6a中示出的试样600与图6b中示出的试样650的不同之处在于,输入小面402和输出小面404是切割小面而不是蚀刻小面114和116。

81.图7示出具有600nm的高度和2.5um的宽度的alingaas无源波导的模拟光学横向电场(te)模式。图8示出alingaas无源波导模式(左侧带框架)与qw有源波导模式(右侧不带框架)之间的模拟te光学模式耦合效率。如下面更详细论述的,输入波导通过重新生长具有约1127nm的带隙波长的alingaas层(与多量子阱层的阻挡层相同)而形成。如图9(其为模拟输入波导的示意性剖面)所示,无源alingaas波导具有至少600nm且不超过3μm的高度以及约2.5μm的宽度。模拟是在假设inp衬底中5

×

10

18

cm

‑3的掺杂浓度下执行。发现基本横向电场模式的传播损耗为0.11db/cm,并且发现与有源波导的模式耦合效率为0.9759(对应于约0.1db的损耗)。因此,对于600nm高的无源波导,发现从无源波导到有源波导的模式失配损耗为0.1db。

82.图10示出连接到硅平台中硅波导的输出波导的fdtd模拟模型。在装置试样的输入小面与硅平台中对应面之间的间隙取为2.0μm。将soi波导模拟为具有以下尺寸:3μm的高度;4μm的宽度;以及1μm宽的丁字架。将alingaas无源波导模拟为具有以下尺寸:3μm的高度;4μm的宽度;以及2μm宽的丁字架。将抗反射涂层模拟为具有约180nm的光学深度(即,厚度)的si3n4层。如图11(其为示出作为波长的函数的耦合损耗的曲线图)所示,发现1310nm的波长下的耦合损耗小于0.4db。

83.图12是示出当输出波导和硅波导具有1.8μm的高度并且小面之间的间隙为1.5μm时作为波长的函数的耦合损耗的曲线图。除此之外,所有其他尺寸都与图10所示的装置相同。如该曲线图所示,发现1310nm的波长下的耦合损耗小于0.7db。

84.迄今图示的电光有源装置包括了三个层:p掺杂层;多量子阱层;以及n掺杂层。然而,本文示出的装置可具有以下表格中所示的任何组成:

[0085][0086]

表1

[0087][0088][0089]

表2

[0090][0091]

表3

[0092][0093]

表4图13(i)(a)至图13(xix)(b)示出装置试样的各种制造步骤。在整个图中,(a)图代表剖面,并且(b)图代表俯视图。

[0094]

在图13(i)(a)和图13(i)(b)所示的第一步中,提供了iii

‑

v多层堆叠并将其在图13(i)(a)中示意性地示出。堆叠包括一个或多个p掺杂inp层702、一个或多个量子阱(qw)有源层704、一个或多个n掺杂inp层706、一个或多个无意掺杂的inp层708、牺牲层710和inp衬底层712。堆叠可以是以上关于表1—表4论述的堆叠中的任一者。

[0095]

接下来,在称为

‘

选项1’并在图13(ii)(a)和图13(ii)(b)中示出的方法的第一变体中,穿过一个或多个p

‑

inp层702和一个或多个qw有源层704执行蚀刻,在一个或多个n

‑

inp层706处停止。该蚀刻步骤包括在堆叠的上表面之上沉积二氧化硅硬掩模714,所述硬掩模的几何形状限定随后形成的无源波导区域(如图13(ii)(b)的俯视图所示)。

[0096]

替代地,在被称为

‘

选项2’并在图13(ii')(a)和图13(ii')(b)中示出的方法的第二变体中,穿过一个或多个p

‑

inp层702、一个或多个qw有源层704以及一个或多个n

‑

inp层706执行蚀刻,在一个或多个uid

‑

inp层708处停止。与选项1一样,该步骤包括在堆叠的上表面之上沉积硅硬掩模714,所述硬掩模的几何形状限定随后形成的无源波导区域(如图13

(ii')(b)的俯视图所示)。与选项1相比,变体选项2消除了一旦光学有源装置形成就需要以对其进行隔离的后续处理。

[0097]

对于选项1变体,方法然后移动到图13(iii)(a)和图13(iii)(b)所示的步骤,其中从暴露的n

‑

inp层706处重新生长alingaas无源波导层716。在该实例中,该无源波导约3μm高,并且覆有未掺杂/无意掺杂的inp层718,以便uid inp层718的上表面与一个或多个p

‑

inp层702齐平。虽然在该实例中,无源波导层由alingaas形成,但是它也可由以下中的任一者形成:ingaasp、alinas或带隙大于或等于1.1ev并且折射率大于inp的折射率的任何其他iii

‑

v材料。

[0098]

对于选项2变体,方法然后移动到图13(iii’)(a)和图13(iii’)(b)所示的步骤,其中首先从暴露的uid

‑

inp层708处生长inp层720。inp层720生长成具有与相邻的n

‑

inp层706相等的厚度。此后,按照选项1生长无源波导层716。inp层720可以是为掺杂或掺杂有铁。

[0099]

以下步骤适用于两种变体,但为了方便起见,仅针对选项1示出。在图13(iv)(a)和图13(iv)(b)所示的步骤中,去除二氧化硅硬掩模并沉积金属籽电极。该沉积可通过剥离(lift off)工艺执行,并且位于将成为有源波导的内容物上方。在该实例中,籽电极具有的厚度约为0.2μm,并且主要由金形成。

[0100]

接下来,在图13(v)(a)和图13(v)(b)所示的步骤中,将另外的二氧化硅714沉积并图案化,以便限定用于以下的掩模:n

‑

焊盘台面724;p焊盘台面726;波导锥形区域728;以及有源波导730。在图案化sio2之后,氮化硅732沉积在sio2之上并图案化,如图13(vi)(a)和图13(vi)(b)所示。氮化硅可具有组合物si3n4,并且由于其对sio2和iii

‑

v半导体具有良好的选择性而进行使用。

[0101]

然后蚀刻未掩模的部分,以提供n

‑

焊盘和p

‑

焊盘、波导锥形区域以及有源波导的台面。这种蚀刻的结果在图13(vii)(a)和图13(vii)(b)中示出。蚀刻深度约为700nm,这表示100nm的过蚀刻。然后去除氮化硅,并且蚀刻继续以对iii

‑

v材料的sio2硬掩模714去除约2.4μm(或对于1.8μm无源波导去除1.2μm),因此到达一个或多个n

‑

inp层706。通常执行100nm的过蚀刻以确保暴露一个或多个n

‑

inp层706。这在图13(viii)(a)和图13(viii)(b)中示出。值得注意的是,将台阶731蚀刻到装置的一部分中,这有助于随后沉积籽电极,以消除由于大的台阶深度而导致电极在边缘上断开的可能性。

[0102]

接下来,在选项1变体的实例中,将另外的二氧化硅714沉积并图案化,以便限定穿过一个或多个n

‑

inp层706的隔离区域。对于选项2实例,省略了该步骤,因为穿过一个或多个n

‑

inp层706的先前蚀刻消除了对随后的隔离蚀刻的需要。这在图13(ix)(a)和图13(ix)(b)中示出。

[0103]

在两种变体中,方法移动到图13(x)(a)和图13(x)(b)所示的步骤,其中将另外的二氧化硅714沉积并图案化,以打开与有源波导相邻地穿过n

‑

inp层706的过孔。接下来,如图13(xi)(a)和图13(xi)(b)所示,通过剥离工艺沉积金属电极734。在此实例中,电极主要由金形成并且约0.4μm厚。

[0104]

在形成籽电极之后,沉积另外的二氧化硅,并且将结构旋涂在苯并环丁烯(bcb)736或另一种合适的电介质中。在bcb固化并回蚀之后,沉积另一层二氧化硅。其结果在图13(xii)(a)和图13(xii)(b)中示出。然后,打开过孔738以接触n籽电极722和p籽电极734,如图13(xiii)(a)和图13(xiii)(b)所示。这允许沉积p电极742和n电极740,使得它们与对应

的籽电极进行电通信,如图13(xiv)(a)和图13(xiv)(b)所示。

[0105]

对于要用于倒装芯片结合工艺中的具有切割小面的装置试样,方法然后移动到晶片薄化和装置切割步骤(在图14(a)和图14(b)中示出)。

[0106]

否则,方法移动到图13(xv)(a)和图13(xv)(b)所示的步骤,其中将另外的二氧化硅沉积并图案化,以便限定波导小面114和116,然后蚀刻未掩模区域以提供小面。接下来,在图13(xvi)(a)和图13(xvi)(b)所示的步骤中,在转移模的暴露的横向侧和上侧之上提供抗反射涂层744。对于要用于倒装芯片结合工艺的具有蚀刻小面的装置试样,方法然后包括划片或切割步骤(在图15(a)和图15(b)中示出)。否则,方法移动到图13(xvii)(a)和图13(xvii)(b)所示的步骤,其中执行保护蚀刻以暴露一个或多个uid

‑

inp层708和牺牲层710的横向侧。此后,在图13(xviii)(a)和图13(xviii)(b)所示的步骤中,将光刻胶系绳746沉积在装置试样的暴露表面之上。这允许执行随后的剥离蚀刻(在图13(xix)(a)和图13(xix)(b)中示出)(其去除牺牲层710)。然后装置试样准备好用于微转移印刷。

[0107]

图14(a)和图14(b)分别示出用于在倒装芯片结合工艺中使用的包含eam的装置试样的剖面图和俯视图。

[0108]

图15(a)和图15(b)分别示出用于倒装芯片结合工艺的包含eam的变体装置试样的剖面图和俯视图。

[0109]

虽然已经结合上述示例性实施方案描述了本发明,但是当给出本公开时,许多等效的修改和变化对于本领域技术人员将是显而易见的。因此,以上阐述的本发明的示例性实施方案应视为说明性的而不是限制性的。在不脱离本发明的精神和范围的情况下可对描述的实施方案作出各种改变。

[0110]

特征列表

[0111]

100

ꢀꢀꢀꢀꢀ

装置试样

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

702

ꢀꢀ

一个或多个p

‑

inp层

[0112]

102

ꢀꢀꢀꢀꢀ

输入波导

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

704

ꢀꢀ

一个或多个qw有源层

[0113]

104

ꢀꢀꢀꢀꢀ

有源波导

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

706

ꢀꢀ

一个或多个n

‑

inp层

[0114]

106

ꢀꢀꢀꢀꢀ

输出波导

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

708

ꢀꢀ

一个或多个uid

‑

inp层

[0115]

108

ꢀꢀꢀꢀꢀ

弯曲部

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

710

ꢀꢀ

牺牲层

[0116]

110

ꢀꢀꢀꢀꢀ

输入波导模式转换器

ꢀꢀꢀꢀꢀ

712

ꢀꢀ

in

‑

p衬底

[0117]

112

ꢀꢀꢀꢀꢀ

输出波导模式转换器

ꢀꢀꢀꢀꢀ

714

ꢀꢀ

sio2[0118]

114

ꢀꢀꢀꢀꢀ

输入小面

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

716

ꢀꢀ

alingaas

[0119]

116

ꢀꢀꢀꢀꢀ

输出小面

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

718

ꢀꢀ

uid

‑

inp

[0120]

150

ꢀꢀꢀꢀꢀ

硅平台

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

720

ꢀꢀ

inp

[0121]

152

ꢀꢀꢀꢀꢀ

硅输入波导

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

722

ꢀꢀ

au籽电极

[0122]

154

ꢀꢀꢀꢀꢀ

硅输出波导

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

724

ꢀꢀ

n焊盘台面掩模

[0123]

202

ꢀꢀꢀꢀꢀ

硅衬底

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

726

ꢀꢀ

p

‑

焊盘台面掩模

[0124]

204

ꢀꢀꢀꢀꢀ

掩埋氧化物层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

728

ꢀꢀ

锥度掩模

[0125]

206

ꢀꢀꢀꢀꢀ

绝缘体上硅波导

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

730

ꢀꢀ

有源波导掩模

[0126]

208,212 抗反射涂层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

731

ꢀꢀ

台阶

[0127]

210

ꢀꢀꢀꢀꢀ

苯并环丁烯填料

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

732

ꢀꢀ

si3n4硬掩模

[0128]

214

ꢀꢀꢀꢀꢀ

磷化铟底部覆层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

734

ꢀꢀ

au籽电极

[0129]

216

ꢀꢀꢀꢀꢀ

alingaas无源波导

ꢀꢀꢀꢀꢀꢀꢀ

736

ꢀꢀ

苯并环丁烯填料

[0130]

218

ꢀꢀꢀꢀꢀ

磷化铟上覆层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

738

ꢀꢀ

过孔

[0131]

220

ꢀꢀꢀꢀꢀ

电光有源装置

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

740

ꢀꢀ

n电极

[0132]

222

ꢀꢀꢀꢀꢀ

n掺杂磷化铟层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

742

ꢀꢀ

p电极

[0133]

224

ꢀꢀꢀꢀꢀ

iii

‑

v半导体量子阱层

ꢀꢀꢀꢀ

744

ꢀꢀ

抗反射涂层

[0134]

226

ꢀꢀꢀꢀꢀ

p掺杂inp/iii

‑

v半导体层 746

ꢀꢀ

光刻胶系绳

[0135]

400

ꢀꢀꢀꢀꢀꢀ

装置试样

[0136]

402

ꢀꢀꢀꢀꢀꢀ

切割输入小面

[0137]

404

ꢀꢀꢀꢀꢀꢀ

切割输出小面

[0138]

502

ꢀꢀꢀꢀꢀꢀ

磷化铟衬底

[0139]

600,650

ꢀꢀ

装置试样

[0140]

602

ꢀꢀꢀꢀꢀꢀ

输入波导弯曲部

[0141]

604

ꢀꢀꢀꢀꢀꢀ

输出波导弯曲部。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。