1.本发明涉及一种显示装置,尤其涉及一种时钟数据恢复电路、包括所述时钟数据恢复电路的显示装置及所述时钟数据恢复电路的驱动方法。

背景技术:

::2.显示装置的数据驱动器可以利用时钟数据恢复(cdr:clockdatarecovery)电路基于从所述显示装置的控制器接收的输入数据恢复时钟信号及数据。另外,所述输入数据可以根据显示面板的分辨率及帧频率而以多个数据速率中的一个数据速率进行传送,据此,要求所述cdr电路支持对应于所述多个数据速率的多速率。3.这样的多速率cdr电路可以划分为利用多速率相位检测器的多速率cdr电路以及利用多速率压控振荡器的多速率cdr电路。另外,与所述利用多速率压控振荡器的多速率cdr电路相比,所述利用多速率相位检测器的多速率cdr电路具有尺寸小且功耗低的优点。然而,在所述利用多速率相位检测器的多速率cdr电路中存在时钟信号可能被锁定在死区内的问题。技术实现要素:4.本发明的一目的在于提供一种能够防止时钟信号被锁定在死区内的时钟数据恢复电路。5.本发明的另一目的在于提供一种包括能够防止时钟信号被锁定在死区内的时钟数据恢复电路的显示装置。6.本发明的又一目的在于提供一种能够防止时钟信号被锁定在死区内的时钟数据恢复电路的驱动方法。7.但是,本发明所要解决的技术问题并不限于上述技术问题,本发明可以在不脱离本发明的思想及构思的范围内实现多种扩展。8.为了达成本发明的一目的,根据本发明的实施例的一种显示装置的数据驱动器中所包括的时钟数据恢复电路包括:锁相环电路,输入数据生成多相位时钟信号,并且包括能够以多个速率进行操作并在初始区间以作为所述多个速率中的预定的一个速率的初始速率进行操作的多速率相位检测器;锁定检测器,检测所述锁相环电路的锁定状态而生成锁定使能信号;死区校准电路,响应于所述锁定使能信号而确定所述多个速率中与所述输入数据的数据速率对应的最终速率;以及数字块,控制所述多速率相位检测器以所述最终速率进行操作,并且生成校准使能信号。所述死区校准电路响应于所述校准使能信号而判断所述多相位时钟信号是否在死区内被锁定,并且在所述多相位时钟信号在所述死区内被锁定的情况下,变更所述多相位时钟信号的相位。9.在一实施例中,所述多个速率可以包括所述多速率相位检测器在所述多相位时钟信号的每个周期执行相位检测的全速率、所述多速率相位检测器在所述多相位时钟信号的每半个周期执行所述相位检测的半速率以及所述多速率相位检测器在所述多相位时钟信号的每1/4个周期执行所述相位检测的四分之一速率,所述初始速率为所述全速率。10.在一实施例中,所述输入数据的所述数据速率可以为第一数据速率、作为所述第一数据速率的两倍的第二数据速率以及作为所述第二数据速率的两倍的第三数据速率中的一个数据速率,在所述输入数据的所述数据速率为所述第一数据速率的情况下,所述死区校准电路响应于所述锁定使能信号而将所述最终速率确定为所述全速率,在所述输入数据的所述数据速率为所述第二数据速率的情况下,所述死区校准电路响应于所述锁定使能信号而将所述最终速率确定为所述半速率,在所述输入数据的所述数据速率为所述第三数据速率的情况下,所述死区校准电路响应于所述锁定使能信号而将所述最终速率确定为所述四分之一速率。11.在一实施例中,与所述多相位时钟信号的一个周期对应的所述多相位时钟信号的相位范围可以被划分为第一相位范围、第二相位范围、第三相位范围及第四相位范围,所述多相位时钟信号通过以所述初始速率进行操作的所述多速率相位检测器在所述第一相位范围内被锁定,所述死区校准电路检测所述输入数据在所述第二相位范围内的第一边沿以及所述输入数据在所述第三相位范围内的第二边沿,在未检测到所述第一边沿及所述第二边沿的情况下,所述死区校准电路响应于所述锁定使能信号而将所述最终速率确定为所述全速率,在未检测到所述第一边沿并检测到所述第二边沿的情况下,所述死区校准电路响应于所述锁定使能信号而将所述最终速率确定为所述半速率,在检测到所述第一边沿及所述第二边沿的情况下,所述死区校准电路响应于所述锁定使能信号而将所述最终速率确定为所述四分之一速率。12.在一实施例中,所述死区校准电路还可以检测所述输入数据在所述第四相位范围内的第三边沿,在所述最终速率被确定为所述全速率的情况下,所述死区校准电路响应于所述校准使能信号而在检测到所述第一边沿、所述第二边沿和所述第三边沿中的至少一个边沿时判断所述多相位时钟信号在所述死区内被锁定,在所述最终速率被确定为所述半速率的情况下,所述死区校准电路响应于所述校准使能信号而在检测到所述第一边沿和所述第三边沿中的至少一个边沿时判断所述多相位时钟信号在所述死区内被锁定,在所述最终速率被确定为所述四分之一速率的情况下,所述死区校准电路响应于所述校准使能信号而判断所述多相位时钟信号未在所述死区内被锁定。13.在一实施例中,在所述多相位时钟信号被判断为在所述死区内被锁定的情况下,所述死区校准电路可以向所述锁相环电路中所包括的环路滤波器提供附加电荷泵电流,来变更所述多相位时钟信号的所述相位。14.在一实施例中,与所述多相位时钟信号的一个周期对应的所述多相位时钟信号的相位范围可以被划分为第一相位范围、第二相位范围、第三相位范围及第四相位范围,所述死区校准电路包括:边沿检测块,检测所述输入数据在所述第二相位范围内的第一边沿、所述输入数据在所述第三相位范围内的第二边沿以及所述输入数据在所述第四相位范围内的第三边沿;速率确定块,基于所述锁定使能信号、所述第一边沿、所述第二边沿而确定所述最终速率;死区检测块,基于所述校准使能信号、所述最终速率、所述第一边沿、所述第二边沿及所述第三边沿判断所述多相位时钟信号是否在所述死区内被锁定;以及死区电荷泵,在所述多相位时钟信号被判断为在所述死区内被锁定的情况下,向所述锁相环电路中所包括的环路滤波器提供附加电荷泵电流。15.在一实施例中,所述多相位时钟信号包括具有彼此不同的相位的第一时钟信号、第二时钟信号、第三时钟信号、第四时钟信号、第五时钟信号、第六时钟信号、第七时钟信号、第八时钟信号,所述边沿检测块包括:第一触发器,响应于所述第三时钟信号而对所述输入数据进行采样;第二触发器,响应于所述第五时钟信号而对所述输入数据进行采样;第三触发器,响应于所述第七时钟信号而对所述输入数据进行采样;第四触发器,响应于所述第一时钟信号而对所述输入数据进行采样;第一异或门,对所述第一触发器的输出信号及所述第二触发器的输出信号执行异或运算而检测所述第一边沿;第二异或门,对所述第二触发器的所述输出信号及所述第三触发器的输出信号执行异或运算而检测所述第二边沿;以及第三异或门,对所述第三触发器的所述输出信号及所述第四触发器的输出信号执行异或运算而检测所述第三边沿。16.在一实施例中,所述边沿检测块还可以包括:第五触发器,位于所述第一触发器与所述第一异或门之间,并且响应于所述第四时钟信号而对所述第一触发器的所述输出信号进行采样;第六触发器,位于所述第二触发器与所述第一异或门之间,并且响应于所述第六时钟信号而对所述第二触发器的所述输出信号进行采样;第七触发器,位于所述第二触发器与所述第二异或门之间,并且响应于所述第六时钟信号而对所述第二触发器的所述输出信号进行采样;第八触发器,位于所述第三触发器与所述第二异或门之间,并且响应于所述第六时钟信号而对所述第三触发器的所述输出信号进行采样;第九触发器,位于所述第三触发器与所述第三异或门之间,并且响应于所述第八时钟信号而对所述第三触发器的所述输出信号进行采样;以及第十触发器,位于所述第四触发器与所述第三异或门之间,并且响应于所述第八时钟信号而对所述第四触发器的所述输出信号进行采样。17.在一实施例中,所述速率确定块可以包括:第一多路复用器,响应于所述锁定使能信号而选择性地输出所述第一异或门的输出信号或低电源电压;第二多路复用器,响应于所述锁定使能信号而选择性地输出所述第二异或门的输出信号或所述低电源电压;第十一触发器,响应于所述第一多路复用器的输出信号而对高电源电压进行采样而生成第一速率检测信号;以及第十二触发器,响应于所述第二多路复用器的输出信号而对所述高电源电压进行采样而生成第二速率检测信号。18.在一实施例中,在所述第一速率检测信号及所述第二速率检测信号全部具有低电平的情况下,所述数字块可以控制所述多速率相位检测器以全速率作为所述最终速率进行操作,在所述第一速率检测信号具有所述低电平且所述第二速率检测信号具有高电平的情况下,所述数字块控制所述多速率相位检测器以半速率作为所述最终速率进行操作,在所述第一速率检测信号及所述第二速率检测信号全部具有所述高电平的情况下,所述数字块控制所述多速率相位检测器以四分之一速率作为所述最终速率进行操作。19.在一实施例中,所述死区检测块可以包括:第三多路复用器,响应于所述校准使能信号而选择性地输出所述第一异或门的输出信号或低电源电压作为第一校准信号;第四多路复用器,响应于所述校准使能信号而选择性地输出所述第二异或门的输出信号或所述低电源电压作为第二校准信号;第五多路复用器,响应于所述校准使能信号而选择性地输出所述第三异或门的输出信号或所述低电源电压作为第三校准信号;第一或门,对所述第一校准信号、所述第二校准信号及所述第三校准信号执行或运算而输出全速率校准信号;第二或门,对所述第一校准信号及所述第三校准信号执行或运算而输出半速率校准信号;以及第六多路复用器,响应于与所述最终速率对应的最终速率信号而选择性地输出所述全速率校准信号、所述半速率校准信号或所述低电源电压作为死区检测信号。20.在一实施例中,所述死区电荷泵可以在所述死区检测信号具有低电平的情况下不向所述环路滤波器提供所述附加电荷泵电流,而在所述死区检测信号具有高电平的情况下向所述环路滤波器提供所述附加电荷泵电流。21.在一实施例中,所述附加电荷泵电流可以为负的电流,所述锁相环电路基于由所述死区电荷泵提供的所述附加电荷泵电流而增加所述多相位时钟信号的所述相位。22.在一实施例中,所述多速率相位检测器可以检测所述输入数据与所述多相位时钟信号的相位差,所述锁相环电路还包括:电荷泵,响应于由所述多速率相位检测器检测的所述相位差而生成电荷泵电流;环路滤波器,对所述电荷泵电流进行滤波而生成控制电压;以及压控振荡器,基于所述控制电压生成所述多相位时钟信号。23.在一实施例中,所述多相位时钟信号包括具有彼此不同的相位的第一时钟信号、第二时钟信号、第三时钟信号、第四时钟信号、第五时钟信号、第六时钟信号、第七时钟信号、第八时钟信号,所述多速率相位检测器包括:第一触发器第二触发器、第三触发器、第四触发器、第五触发器、第六触发器、第七触发器、第八触发器,分别响应于所述第一时钟信号至第八时钟信号而对所述输入数据进行采样;第一异或门,包括第一输入端子、第二输入端子以及输出上行信号的第一输出端子;第二异或门,包括第三输入端子、第四输入端子以及输出下行信号的第二输出端子;第一开关块,响应于从所述数字块接收的数字码而向所述第一输入端子提供所述第一触发器的输出信号、所述第三触发器的输出信号、所述第五触发器的输出信号或所述第七触发器的输出信号;第二开关块,响应于所述数字码而向所述第二输入端子及所述第三输入端子提供所述第二触发器的输出信号、所述第四触发器的输出信号、所述第六触发器的输出信号或所述第八触发器的输出信号;以及第三开关块,响应于所述数字码而向所述第四输入端子提供所述第三触发器的所述输出信号、所述第五触发器的所述输出信号、所述第七触发器的所述输出信号或所述第一触发器的所述输出信号。24.在一实施例中,在所述最终速率被确定为全速率的情况下,所述多速率相位检测器可以输出所述第六触发器的所述输出信号作为恢复的数据,在所述最终速率被确定为半速率的情况下,所述多速率相位检测器输出所述第四触发器的所述输出信号及所述第八触发器的所述输出信号作为所述恢复的数据,在所述最终速率被确定为四分之一速率的情况下,所述多速率相位检测器输出所述第一触发器的所述输出信号、所述第三触发器的所述输出信号、所述第五触发器的所述输出信号及所述第七触发器的所述输出信号作为所述恢复的数据。25.为了达成本发明的另一目的,根据本发明的实施例的一种显示装置包括:显示面板,包括多个像素;数据驱动器,包括基于输入数据生成多相位时钟信号及恢复的数据的时钟数据恢复电路,并且向所述多个像素提供与所述恢复的数据对应的数据信号;以及控制器,向所述数据驱动器提供所述输入数据。所述时钟数据恢复电路包括:锁相环电路,基于所述输入数据生成所述多相位时钟信号,并且包括能够以多个速率进行操作并在初始区间以作为所述多个速率中的预定的一个速率的初始速率进行操作的多速率相位检测器;锁定检测器,检测所述锁相环电路的锁定状态而生成锁定使能信号;死区校准电路,响应于所述锁定使能信号而确定所述多个速率中与所述输入数据的数据速率对应的最终速率;以及数字块,控制所述多速率相位检测器以所述最终速率进行操作,并且生成校准使能信号。所述死区校准电路响应于所述校准使能信号而判断所述多相位时钟信号是否在死区内被锁定,并且在所述多相位时钟信号在所述死区内被锁定的情况下,变更所述多相位时钟信号的相位。26.为了达成本发明的又一目的,根据本发明的实施例的一种显示装置的数据驱动器中所包括的时钟数据恢复电路的驱动方法,包括如下步骤:使能够以多个速率进行操作的多速率相位检测器在初始区间以作为所述多个速率中的预定的一个速率的初始速率进行操作,来基于输入数据生成多相位时钟信号;检测包括所述多速率相位检测器的锁相环电路的锁定状态;确定所述多个速率中与所述输入数据的数据速率对应的最终速率;控制所述多速率相位检测器以所述最终速率进行操作;判断所述多相位时钟信号是否在死区内被锁定;以及在所述多相位时钟信号在所述死区内被锁定的情况下,变更所述多相位时钟信号的相位。27.在一实施例中,所述多速率相位检测器的所述多个速率可以包括全速率、半速率及四分之一速率,所述初始速率为所述全速率。28.在根据本发明的实施例的时钟数据恢复电路、显示装置及时钟数据恢复电路的驱动方法中,多速率相位检测器可以在初始区间以全速率进行操作,死区校准电路响应于锁定使能信号而确定与数据速率对应的最终速率,所述多速率相位检测器在所述初始区间后以所述最终速率进行操作,并且所述死区校准电路响应于校准使能信号而在判断多相位时钟信号在死区内被锁定的情况下执行变更所述多相位时钟信号的相位的死区校准操作。据此,可以防止所述多相位时钟信号在所述死区内被锁定,并防止恢复的数据的错误,并且可以减小所述时钟数据恢复电路的尺寸及功耗。29.然而,本发明的效果并不限于上述效果,其可以在不脱离本发明的思想及构思的范围内实现多种扩展。附图说明30.图1是示出根据本发明的实施例的时钟数据恢复电路的框图。31.图2是示出根据本发明的实施例的时钟数据恢复电路中所包括的锁相环电路的一示例的框图。32.图3是示出图2的锁相环电路中所包括的多速率相位检测器的一示例的框图。33.图4是示出根据相位检测速率的数字码的示例的图。34.图5是用于说明以全速率、半速率和四分之一速率进行操作的多速率相位检测器的相位检测的示例的时序图。35.图6是示出不包括死区校准电路的时钟数据恢复电路的多相位时钟信号的锁定点及死区的示例的图。36.图7是用于说明根据本发明的实施例的时钟数据恢复电路中所包括的多速率相位检测器在初始区间的操作的时序图。37.图8是示出根据本发明的实施例的时钟数据恢复电路中所包括的死区校准电路的一示例的框图。38.图9是示出根据第一速率检测信号及第二速率检测信号的最终速率的一示例的图。39.图10是用于说明根据最终速率信号、第一校准信号、第二校准信号及第三校准信号的死区检测信号的一示例的图。40.图11是示出根据本发明的实施例的时钟数据恢复电路的多相位时钟信号的锁定点及死区的示例的图。41.图12是示出根据本发明的实施例的时钟数据恢复电路的驱动方法的流程图。42.图13是示出根据本发明的实施例的显示装置的框图。43.图14是示出根据本发明的实施例的包括显示装置的电子设备的框图。44.附图标记说明45.100:时钟数据恢复电路ꢀꢀꢀꢀꢀꢀꢀꢀ110:锁相环电路46.120:多速率相位检测器ꢀꢀꢀꢀꢀꢀꢀꢀ140:电荷泵47.150:环路滤波器ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ160:压控振荡器48.170:锁定检测器ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ180:数字块49.200:死区校准电路ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ210:边沿检测块50.230:速率确定块ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ250:死区检测块51.280:死区电荷泵ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ800:显示装置52.810:显示面板ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ820:栅极驱动器53.830:数据驱动器ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ840:时钟数据恢复电路54.850:控制器具体实施方式55.以下,参照附图对本发明的优选实施例进行更详细的说明。针对附图上相同的构成要素使用相同的附图标记,并且省略针对相同的构成要素的重复说明。56.图1是示出根据本发明的实施例的时钟数据恢复电路的框图,图2是示出根据本发明的实施例的时钟数据恢复电路中所包括的锁相环电路的一示例的框图,图3是示出图2的锁相环电路中所包括的多速率相位检测器的一示例的框图,图4是示出根据相位检测速率的数字码的示例的图,图5是用于说明以全速率、半速率和四分之一速率进行操作的多速率相位检测器的相位检测的示例的时序图,图6是示出不包括死区校准电路的时钟数据恢复电路的多相位时钟信号的锁定点及死区的示例的图,图7是用于说明根据本发明的实施例的时钟数据恢复电路中所包括的多速率相位检测器在初始区间的操作的时序图,图8是示出根据本发明的实施例的时钟数据恢复电路中所包括的死区校准电路的一示例的框图,图9是示出根据第一速率检测信号及第二速率检测信号的最终速率的一示例的图,图10是用于说明根据最终速率信号、第一校准信号、第二校准信号及第三校准信号的死区检测信号的一示例的图,图11是示出根据本发明的实施例的时钟数据恢复电路的多相位时钟信号的锁定点及死区的示例的图。57.参照图1,根据本发明的实施例的显示装置的数据驱动器中所包括的时钟数据恢复电路100可以包括:锁相环电路110,基于输入数据dat生成多相位时钟信号mpck;锁定检测器170,检测锁相环电路110的锁定状态;数字块180,向锁相环电路110中所包括的多速率相位检测器120提供数字码dcode;以及死区校准电路200,执行针对多相位时钟信号mpck的死区校准(deadzonecalibration)操作。58.锁相环电路110可以从所述显示装置的控制器(例如,时序控制器(timingcontroller;tcon))接收输入数据dat,并基于输入数据dat生成多相位时钟信号mpck,并且响应于多相位时钟信号mpck而对输入数据dat进行采样来生成恢复的数据rdat。多相位时钟信号mpck可以包括具有彼此不同的相位的多个时钟信号。例如,多相位时钟信号mpck可以包括第一时钟信号至第八时钟信号,所述第一时钟信号至第八时钟信号在将一个周期等分为8份的时间点处具有边沿,即,具有将对应于所述一个周期的360度的相位等分为8份的相位。59.在一实施例中,锁相环电路110可以根据由所述数据驱动器驱动的显示面板的分辨率和/或帧频率而以多种数据速率dr1、dr2、dr3中的一个速率接收输入数据dat。例如,锁相环电路110可以在所述显示面板具有4k超高清晰度(uhd:ultrahighdefinition)分辨率并以约60hz的帧频率被驱动的情况下以约1gbps的第一数据速率dr1接收输入数据dat,在所述显示面板具有所述4kuhd分辨率并以约120hz的帧频率被驱动的情况下以作为第一数据速率dr1的两倍的约2gbps的第二数据速率dr2接收输入数据dat,在所述显示面板具有8kuhd分辨率并以约120hz的所述帧频率被驱动的情况下以作为第二数据速率dr2的两倍的约4gbps的第三数据速率dr3接收输入数据dat。为了支持这样的输入数据dat的多种数据速率dr1、dr2、dr3,锁相环电路110可以包括能够以多个速率进行操作的多速率相位检测器120。60.在一实施例中,如图2所示,锁相环电路110可以包括多速率相位检测器120、电荷泵140、环路滤波器150及压控振荡器160。多速率相位检测器120可以检测输入数据dat与多相位时钟信号mpck的相位差,并生成对应于所述相位差的信号(例如,上行信号up和/或下行信号dn)。例如,多速率相位检测器120可以在输入数据dat领先(lead)多相位时钟信号mpck的情况下生成上行信号up,而在多相位时钟信号mpck领先输入数据dat的情况下生成下行信号dn。电荷泵140可以响应于由多速率相位检测器120检测的所述相位差而生成电荷泵电流icp。例如,电荷泵140可以响应于上行信号up而向环路滤波器150提供正的电荷泵电流icp,而响应于下行信号dn而向环路滤波器150提供负的电荷泵电流icp,即,从环路滤波器150吸引(draw)电荷泵电流icp。环路滤波器150可以对电荷泵电流icp进行滤波而生成控制电压vc。例如,环路滤波器150可以响应于正的电荷泵电流icp而增加控制电压vc,而响应于负的电荷泵电流icp而减小控制电压vc。并且,在一实施例中,环路滤波器150可以去除多相位时钟信号mpck的高频噪声成分。压控振荡器160可以基于控制电压vc生成多相位时钟信号mpck。例如,压控振荡器160可以在控制电压vc增加时减小多相位时钟信号mpck的相位,而在控制电压vc减小时增加多相位时钟信号mpck的相位。在一实施例中,压控振荡器160可以是8‑相位(8‑phase)压控振荡器,所述8‑相位(8‑phase)压控振荡器生成具有彼此不同的相位的第一时钟信号ck0、第二时钟信号ck45、第三时钟信号ck90、第四时钟信号ck135、第五时钟信号ck180、第六时钟信号ck225、第七时钟信号ck270、第八时钟信号ck315作为多相位时钟信号mpck。例如,第一时钟信号ck0可以具有约0度的相位,第二时钟信号ck45具有约45度的相位,第三时钟信号ck90具有约90度的相位,第四时钟信号ck135具有约135度的相位,第五时钟信号ck180具有约180度的相位,第六时钟信号ck225具有约225度的相位,第七时钟信号ck270具有约270度的相位,第八时钟信号ck315具有约315度的相位。61.多速率相位检测器120可以以多个速率中的一个速率进行操作。在一实施例中,多速率相位检测器120可以以与输入数据dat的第一数据速率dr1对应的全速率fullrate、与作为第一数据速率dr1的两倍的第二数据速率dr2对应的半速率halfrate以及与作为第二数据速率dr2的两倍的第三数据速率dr3对应的四分之一速率quarterrate进行操作。在一实施例中,为了能够以全速率fullrate、半速率halfrate及四分之一速率quarterrate进行操作,如图3所示,多速率相位检测器120可以包括第一触发器121至第八触发器128、第一开关块131、第二开关块133、第三开关块135以及第一异或门137及第二异或门139。62.第一触发器121至第八触发器128可以分别响应于第一时钟信号ck0、第二时钟信号ck45、第三时钟信号ck90、第四时钟信号ck135、第五时钟信号ck180、第六时钟信号ck225、第七时钟信号ck270、第八时钟信号ck315对输入数据dat进行采样。例如,第一触发器121可以响应于具有约0度的相位的第一时钟信号ck0而对输入数据dat进行采样,第二触发器122响应于具有约45度的相位的第二时钟信号ck45而对输入数据dat进行采样,第三触发器123响应于具有约90度的相位的第三时钟信号ck90而对输入数据dat进行采样,第四触发器124响应于具有约135度的相位的第四时钟信号ck135而对输入数据dat进行采样,第五触发器125响应于具有约180度的相位的第五时钟信号ck180而对输入数据dat进行采样,第六触发器126响应于具有约255度的相位的第六时钟信号ck225而对输入数据dat进行采样,第七触发器127响应于具有约270度的相位的第七时钟信号ck270而对输入数据dat进行采样,第八触发器128响应于具有约315度的相位的第八时钟信号ck315而对输入数据dat进行采样。63.第一开关块131可以响应于从数字块180接收的数字码dcode向第一异或门137的第一输入端子提供第一触发器121的输出信号、第三触发器123的输出信号、第五触发器125的输出信号或第七触发器127的输出信号。例如,数字码dcode可以包括第一数字信号d1至第四数字信号d4,第一开关块131包括第一开关sw1至第四开关sw4。第一开关sw1可以响应于第一数字信号d1向所述第一输入端子传送第一触发器121的所述输出信号,第二开关sw2响应于第二数字信号d2向所述第一输入端子传送第三触发器123的所述输出信号,第三开关sw3响应于第三数字信号d3向所述第一输入端子传送第五触发器125的所述输出信号,第四开关sw4响应于第四数字信号d4向所述第一输入端子传送第七触发器127的所述输出信号。64.第二开关块133可以响应于数字码dcode向第一异或门137的第二输入端子及第二异或门139的第三输入端子提供第二触发器122的输出信号、第四触发器124的输出信号、第六触发器126的输出信号或第八触发器128的输出信号。例如,第二开关块133可以包括第五开关sw5至第八开关sw8。第五开关sw5可以响应于第一数字信号d1向所述第二输入端子及第三输入端子传送第二触发器122的所述输出信号,第六开关sw6响应于第二数字信号d2向所述第二输入端子及第三输入端子传送第四触发器124的所述输出信号,第七开关sw7响应于第三数字信号d3向所述第二输入端子及第三输入端子传送第六触发器126的所述输出信号,第八开关sw8响应于第四数字信号d4向所述第二输入端子及第三输入端子传送第八触发器128的所述输出信号。65.第三开关块135可以响应于数字码dcode向第二异或门139的第四输入端子提供第三触发器123的所述输出信号、第五触发器125的所述输出信号、第七触发器127的所述输出信号或第一触发器121的所述输出信号。例如,第三开关块135可以包括第九开关sw9至第十二开关sw12。第九开关sw9可以响应于第一数字信号d1向所述第四输入端子传送第三触发器123的所述输出信号,第十开关sw10响应于第二数字信号d2向所述第四输入端子传送第五触发器125的所述输出信号,第十一开关sw11响应于第三数字信号d3向所述第四输入端子传送第七触发器127的所述输出信号,第十二开关sw12响应于第四数字信号d4向所述第四输入端子传送第一触发器121的所述输出信号。66.第一异或门137可以在所述第一输入端子接收第一开关块131的输出信号,在所述第二输入端子接收第二开关块133的输出信号,并且对第一开关块131的所述输出信号及第二开关块133的所述输出信号执行异或运算而生成上行信号up,并在第一输出端子输出上行信号up。67.并且,第二异或门139可以在所述第三输入端子接收第二开关块133的所述输出信号,在所述第四输入端子接收第三开关块135的输出信号,并且对第二开关块133的所述输出信号及第三开关块135的所述输出信号执行异或运算而生成下行信号dn,并在第二输出端子处输出下行信号dn。68.为了以与输入数据dat的第一数据速率dr1对应的全速率fullrate驱动多速率相位检测器120,如图4所示,数字块180可以向多速率相位检测器120提供“1000”的数字码dcode。例如,多速率相位检测器120可以接收高电平的第一数字信号d1以及低电平的第二数字信号d2、第三数字信号d3及第四数字信号d4。响应于所述高电平的第一数字信号d1以及所述低电平的第二数字信号d2、第三数字信号d3及第四数字信号d4,第一开关块131可以输出第一触发器121的所述输出信号(即,在约0度的相位采样的输入数据dat),第二开关块133输出第二触发器122的所述输出信号(即,在约45度的相位采样的输入数据dat),第三开关块135输出第三触发器123的所述输出信号(即,在约90度的相位采样的输入数据dat)。第一异或门137可以对第一开关块131的所述输出信号(即,在约0度的相位采样的输入数据dat)以及第二开关块133的所述输出信号(即,在约45度的相位采样的输入数据dat)执行异或运算而生成上行信号up。据此,上行信号up可以在输入数据dat在多相位时钟信号mpck的约0度至约45度的相位范围内具有边沿的情况下具有高电平。另外,具有所述高电平的上行信号up表示输入数据dat领先多相位时钟信号mpck(即,具有约45度的相位的第二时钟信号ck45),并且锁相环电路110可以响应于具有所述高电平的上行信号up而减小多相位时钟信号mpck的相位。并且,第二异或门139可以对第二开关块133的所述输出信号(即,在约45度的相位采样的输入数据dat)以及第三开关块135的所述输出信号(即,在约90度的相位采样的输入数据dat)执行异或运算而生成下行信号dn。据此,下行信号dn可以在输入数据dat在多相位时钟信号mpck的约45度至约90度的相位范围内具有边沿的情况下具有高电平。另外,具有所述高电平的下行信号dn表示多相位时钟信号mpck(即,具有约45度的相位的第二时钟信号ck45)领先输入数据dat,并且锁相环电路110可以响应于具有所述高电平的下行信号dn增加多相位时钟信号mpck的相位。以这种方式,如图5的附图标记310所示,多速率相位检测器120在以与输入数据dat的约1gbps的第一数据速率dr1对应的全速率fullrate被驱动时,可以在多相位时钟信号mpck(例如,第一时钟信号ck0)的每个周期ped执行一次检测输入数据dat和多相位时钟信号mpck的相位差的相位检测。并且,在一实施例中,当多速率相位检测器120以全速率fullrate被驱动时,例如在多相位时钟信号mpck的相位被调整为输入数据dat在约45度的相位处具有边沿的情况下,多速率相位检测器120可以输出第六触发器126的所述输出信号(即,在约225度的相位处采样的输入数据dat)作为恢复的数据rdat。69.并且,为了以与输入数据dat的第二数据速率dr2对应的半速率halfrate驱动多速率相位检测器120,如图4所示,数字块180可以向多速率相位检测器120提供在一个周期ped内以“1000”及“0010”交替的数字码dcode。例如,多速率相位检测器120可以在周期ped的第一半部分接收所述高电平的第一数字信号d1以及所述低电平的第二数字信号d2、第三数字信号d3及第四数字信号d4,在周期ped的第二半部分接收所述高电平的第三数字信号d3以及所述低电平的第一数字信号d1、第二数字信号d2及第四数字信号d4。在这种情况下,多速率相位检测器120可以在输入数据dat在约0度至约45度的相位范围内具有边沿的情况下输出上行信号up,在输入数据dat在约45度至约90度的相位范围内具有边沿的情况下输出下行信号dn,在输入数据dat在约180度至约225度的相位范围内具有边沿的情况下输出上行信号up,在输入数据dat在约225度至约270度的相位范围内具有边沿的情况下输出下行信号dn。据此,如图5的附图标记330所示,多速率相位检测器120可以在以与输入数据dat的约2gbps的第二数据速率dr2对应的半速率halfrate被驱动时,在多相位时钟信号mpck的每半周期执行所述相位检测,即,在多相位时钟信号mpck的每个周期ped执行两次所述相位检测。并且,在一实施例中,当多速率相位检测器120以半速率halfrate被驱动时,例如,在多相位时钟信号mpck的相位被调整为输入数据dat在约45度及约225度的相位处具有边沿的情况下,多速率相位检测器120可以输出第四触发器124的所述输出信号(即,在约135度的相位采样的输入数据dat)以及第八触发器128的所述输出信号(即,在约315度的相位采样的输入数据dat)作为恢复的数据rdat。70.并且,为了以与输入数据dat的第三数据速率dr3对应的四分之一速率quarterrate驱动多速率相位检测器120,如图4所示,数字块180可以向多速率相位检测器120提供在一个周期ped内以“1000”、“0100”、“0010”及“0001”交替的数字码dcode。例如,多速率相位检测器120可以在周期ped的第一1/4处接收所述高电平的第一数字信号d1以及所述低电平的第二数字信号d2、第三数字信号d3及第四数字信号d4,在周期ped的第二1/4处接收所述高电平的第二数字信号d2以及所述低电平的第一数字信号d1、第三数字信号d3及第四数字信号d4,在周期ped的第三1/4处接收所述高电平的第三数字信号d3以及所述低电平的第一数字信号d1、第二数字信号d2及第四数字信号d4,在周期ped的第四1/4处接收所述高电平的第四数字信号d4以及所述低电平的第一数字信号d1、第二数字信号d2及第三数字信号d3。在这种情况下,多速率相位检测器120可以在输入数据dat在约0度至约45度的相位范围内具有边沿的情况下输出上行信号up,在输入数据dat在约45度至约90度的相位范围内具有边沿的情况下输出下行信号dn,在输入数据dat在约90度至约135度的相位范围内具有边沿的情况下输出上行信号up,在输入数据dat在约135度至约180度的相位范围内具有边沿的情况下输出下行信号dn,在输入数据dat在约180度至约225度的相位范围内具有边沿的情况下输出上行信号up,在输入数据dat在约225度至约270度的相位范围内具有边沿的情况下输出下行信号dn,在输入数据dat在约270度至约315度的相位范围内具有边沿的情况下输出上行信号up,在输入数据dat在约315度至约360度的相位范围内具有边沿的情况下输出下行信号dn。据此,如图5的附图标记350所示,多速率相位检测器120可以在以与输入数据dat的约4gbps的第三数据速率dr3对应的四分之一速率quarterrate被驱动时,在多相位时钟信号mpck的每个1/4周期执行所述相位检测,即,在多相位时钟信号mpck的每个周期ped执行四次所述相位检测。并且,在一实施例中,当多速率相位检测器120以四分之一速率quarterrate被驱动时,例如,当多相位时钟信号mpck的相位被调整为输入数据dat在约45度、约135度、约225度及约315度的相位处具有边沿时,多速率相位检测器120可以输出第一触发器121的所述输出信号(即,在约0度的相位采样的输入数据dat)、第三触发器123的所述输出信号(即,在约90度的相位采样的输入数据dat)、第五触发器125的所述输出信号(即,在约180度的相位采样的输入数据dat)及第七触发器127的输出信号(即,在约270度的相位采样的输入数据dat)作为恢复的数据rdat。71.另外,图2示出了锁相环电路110的构成的一示例,但是根据本发明的实施例的锁相环电路110的构成并不局限于图2的示例。并且,图3示出了多速率相位检测器120的构成的一示例,但是根据本发明的实施例的多速率相位检测器120的构成并不局限于图3的示例。72.另外,在时钟数据恢复电路100不包括死区校准电路200的情况下,如图6所示,多相位时钟信号mpck可以在不是一般锁定点nlp的死区dz1、dz2内被锁定。例如,如图6中的附图标记410所示,当多速率相位检测器120以与第一数据速率dr1对应的全速率fullrate被驱动时,在多相位时钟信号mpck(例如,第二时钟信号ck45)比输入数据dat落后约0单位区间(ui:unitinterval)至约0.125ui的情况下,即,在具有比输入数据dat大约0度至约45度的相位的情况下,上行信号up可以具有高于下行信号dn的电平,并且提供正的电荷泵电流icp,并且减小多相位时钟信号mpck的相位。在此,所述ui(unitinterval)可以对应于输入数据dat的各个比特的宽度或时间。并且,在第二时钟信号ck45比输入数据dat领先约0ui至约0.125ui的情况下,即,在具有比输入数据dat小约0度至约45度的相位的情况下,下行信号dn可以具有高于上行信号up的电平,并且提供负的电荷泵电流icp,并且增加多相位时钟信号mpck的相位。据此,在第二时钟信号ck45相对于输入数据dat具有约‑0.125ui至约0.125ui(即,约‑45度至约45度)的相位差(或者约0ui至约0.125ui及约0.875ui至约1ui(即,约0度至约45度及约315度至约360度)的相位差)的情况下,多相位时钟信号mpck可以被调整为第二时钟信号ck45相对于输入数据dat具有约0ui(即,约0度)的相位差,并且在一般锁定点nlp被锁定。然而,在第二时钟信号ck45相对于输入数据dat具有约0.125ui至约0.875ui(即,约45度至约315度)的相位差的情况下,可以不生成电荷泵电流icp,并且多相位时钟信号mpck不会被调整,并且不会在一般锁定点nlp被锁定。据此,当多速率相位检测器120以全速率fullrate被驱动时,可以存在约45度至约315度的第一死区dz1。并且,如图6的附图标记430所示,当多速率相位检测器120以与第二数据速率dr2对应的半速率halfrate被驱动时,在多相位时钟信号mpck(例如,第二时钟信号ck45)相对于输入数据dat具有约0ui至约0.25ui及约0.75ui至约1ui(即,约0度至约90度及约270度至约360度)的相位差的情况下,多相位时钟信号mpck可以在一般锁定点nlp被锁定。然而,当多速率相位检测器120以半速率halfrate被驱动时,可以存在约90度至约270度的第二死区dz2。另外,如图6的附图标记450所示,当多速率相位检测器120以与第三数据速率dr3对应的四分之一速率quarterrate被驱动时,多相位时钟信号mpck可以在一般锁定点nlp被锁定,并且可以不存在死区。73.然而,在根据本发明的实施例的包括死区校准电路200的时钟数据恢复电路100中,为了使多相位时钟信号mpck不在第一死区dz1及第二死区dz2内被锁定,多速率相位检测器120可以在初始区间与输入数据dat的数据速率无关地以预定的初始速率进行操作,在多相位时钟信号mpck被锁定之后,多速率相位检测器120以与输入数据dat的所述数据速率对应的最终速率进行操作,并且死区校准电路200执行变更在第一死区dz1及第二死区dz2内被锁定的多相位时钟信号mpck的相位的死区校准操作。74.例如,如图7所示,多速率相位检测器120可以在所述初始区间与输入数据dat的数据速率dr1、dr2、dr3无关地以全速率fullrate作为所述初始速率进行操作。在一实施例中,所述初始区间可以是从开始传送输入数据dat的时间点到多相位时钟信号mpck被锁定的时间点为止的区间,但是并不局限于此。即,在所述初始区间中,与输入数据dat是以约1gbps的第一数据速率dr1被接收,还是以约2gbps的第二数据速率dr2被接收,还是以约4gbps的第三数据速率dr3被接收无关地,数字块180可以向多速率相位检测器120提供“1000”的数字码dcode。据此,多速率相位检测器120可以如图7的附图标记510所示地利用第一时钟信号ck0、第二时钟信号ck45及第三时钟信号ck90对以约1gbps的第一数据速率dr1接收的输入数据dat执行所述相位检测,如图7的附图标记530所示地利用第一时钟信号ck0、第二时钟信号ck45及第三时钟信号ck90对以约2gbps的第二数据速率dr2接收的输入数据dat执行所述相位检测,如图7的附图标记550所示地利用第一时钟信号ck0、第二时钟信号ck45及第三时钟信号ck90对以约4gbps的第三数据速率dr3接收的输入数据dat执行所述相位检测。据此,与输入数据dat的数据速率dr1、dr2、dr3无关地,多相位时钟信号mpck可以在多相位时钟信号mpck的约0度至约90度的第一相位范围内被锁定。75.再次参照图1,若多相位时钟信号mpck在所述初始区间被锁定,则锁定检测器170可以检测锁相环电路110的锁定状态而生成锁定使能信号lock_en。例如,锁定检测器170可以在提供给压控振荡器160的控制电压vc在预定时间期间具有实质上恒定的电压电平的情况下生成锁定使能信号lock_en。76.死区校准电路200可以响应于锁定使能信号lock_en确定多速率相位检测器120的所述多个速率中与输入数据dat的数据速率dr1、dr2、dr3对应的最终速率。例如,死区校准电路200可以在输入数据dat的所述数据速率为第一数据速率dr1的情况下将所述最终速率确定为全速率fullrate,在输入数据dat的所述数据速率为作为第一数据速率dr1的两倍的第二数据速率dr2的情况下将所述最终速率确定为半速率halfrate,在输入数据dat的数据速率为作为第二数据速率dr2的两倍的第三数据速率dr3的情况下将所述最终速率确定为四分之一速率quarterrate。77.在一实施例中,与多相位时钟信号mpck的一个周期ped对应的多相位时钟信号mpck的约0度至约360度的相位范围被划分为约0度至约90度的第一相位范围、约90度至约180度的第二相位范围、约180度至约270度的第三相位范围及约270度至约360度的第四相位范围,多相位时钟信号mpck可以在约0度至约90度的所述第一相位范围内被在所述初始区间中以所述初始速率(例如,全速率fullrate)进行操作的多速率相位检测器120所锁定。死区校准电路200可以检测输入数据dat在约90度至约180度的所述第二相位范围内的第一边沿以及所述输入数据dat在约180度至约270度的所述第三相位范围内的第二边沿。并且,死区校准电路200可以在未检测到所述第一边沿及所述第二边沿的情况下响应于锁定使能信号lock_en将所述最终速率确定为全速率fullrate,在未检测到所述第一边沿并检测到所述第二边沿的情况下响应于锁定使能信号lock_en将所述最终速率确定为半速率halfrate,在检测到所述第一边沿及所述第二边沿的情况下响应于锁定使能信号lock_en将所述最终速率确定为四分之一速率quarterrate。78.数字块180可以控制多速率相位检测器120以由死区校准电路200确定的所述最终速率进行操作。例如,数字块180可以在所述最终速率被确定为全速率fullrate的情况下向多速率相位检测器120提供“1000”的数字码dcode,在所述最终速率被确定为半速率halfrate的情况下向多速率相位检测器120提供在一个周期ped内以“1000”及“0010”交替的数字码dcode,在所述最终速率被确定为四分之一速率quarterrate的情况下向多速率相位检测器120提供在一个周期ped内以“1000”、“0100”、“0010”及“0001”交替的数字码dcode。数字块180可以生成校准使能信号cal_en。在一实施例中,校准使能信号cal_en可以在多速率相位检测器120的所述最终速率被确定之后继续具有高电平,然而并不局限于此。在另一实施例中,在所述最终速率被确定之后,校准使能信号cal_en可以周期性地或非周期性地具有所述高电平。79.死区校准电路200可以响应于校准使能信号cal_en执行死区校准(deadzonecalibration)操作。在一实施例中,死区校准电路200可以响应校准使能信号cal_en判断多相位时钟信号mpck是否在死区内被锁定,并且在多相位时钟信号mpck在所述死区内被锁定的情况下变更多相位时钟信号mpck的相位。80.在一实施例中,死区校准电路200还可以检测输入数据dat在约270度至约360度的所述第四相位范围内的第三边沿。在所述最终速率被确定为全速率fullrate的情况下,死区校准电路200可以响应于校准使能信号cal_en,当检测到所述第一边沿、所述第二边沿或所述第三边沿时判断多相位时钟信号mpck在所述死区内被锁定,而当未检测到所述第一边沿、所述第二边沿及所述第三边沿时判断多相位时钟信号mpck未在所述死区内未被锁定。并且,在所述最终速率被确定为半速率halfrate的情况下,死区校准电路200可以响应于校准使能信号cal_en,当检测到所述第一边沿或所述第三边沿时判断多相位时钟信号mpck在所述死区内被锁定,当未检测到所述第一边沿及所述第三边沿时判断多相位时钟信号mpck未在所述死区内被锁定。并且,在所述最终速率被确定为四分之一速率quarterrate的情况下,死区校准电路200可以响应于校准使能信号cal_en判断多相位时钟信号mpck未在所述死区内被锁定。死区校准电路200可以在判断多相位时钟信号mpck在所述死区内被锁定的情况下向锁相环电路110中所包括的环路滤波器150提供附加电荷泵电流iacp,以变更多相位时钟信号mpck的所述相位。81.在一实施例中,为了确定所述最终速率并执行所述死区校准操作,如图8所示,死区校准电路200可以包括边沿检测块210、速率确定块230、死区检测块250及死区电荷泵280。82.边沿检测块210可以检测输入数据dat在约90度至约180度的所述第二相位范围内的所述第一边沿、输入数据dat在约180度至约270度的所述第三相位范围内的所述第二边沿以及输入数据dat在约270度至约360度的所述第四相位范围内的所述第三边沿。83.例如,如图8所示,边沿检测块210包括:第一触发器211,响应于具有约90度的相位的第三时钟信号ck90而对输入数据dat进行采样;第二触发器212,响应于具有约180度的相位的第五时钟信号ck180而对输入数据dat进行采样;第三触发器213,响应于具有约270度的相位的第七时钟信号ck270而对输入数据dat进行采样;第四触发器214,响应于具有约0度的相位(即,约360度的相位)的第一时钟信号ck0而对输入数据dat进行采样;第一异或门221,对第一触发器211的输出信号及第二触发器212的输出信号执行异或运算而检测所述第一边沿;第二异或门222,对第二触发器212的所述输出信号及第三触发器213的输出信号执行异或运算而检测所述第二边沿;以及第三异或门223,对第三触发器213的所述输出信号及第四触发器214的输出信号执行异或运算而检测所述第三边沿。在一实施例中,边沿检测块210还可包括用于第一触发器211至第四触发器214的所述输出信号的对齐(align)的第五触发器215至第十触发器220。例如,第五触发器215可以位于第一触发器211与第一异或门221之间,并且响应于具有约135度的相位的第四时钟信号ck135而对第一触发器211的所述输出信号进行采样。第六触发器216可以位于第二触发器212与第一异或门221之间,并且响应于具有约225度的相位的第六时钟信号ck225而对第二触发器212的所述输出信号进行采样。第七触发器217可以位于第二触发器212与第二异或门222之间,并且响应于具有约225度的相位的第六时钟信号ck225而对第二触发器212的所述输出信号进行采样。第八触发器218可以位于第三触发器213与第二异或门222之间,并且响应于具有约225度的相位的第六时钟信号ck225而对第三触发器213的所述输出信号进行采样。第九触发器219可以位于第三触发器213与第三异或门223之间,并且响应于具有约315度的相位的第八时钟信号ck315而对第三触发器213的所述输出信号进行采样。第十触发器220可以位于第四触发器214与第三异或门223之间,并且响应于具有约315度的相位的第八时钟信号ck315而对第四触发器214的所述输出信号进行采样。84.速率确定块230可以基于锁定使能信号lock_en、第一异或门221的所述输出信号(即,所述第一边沿)及第二异或门222的所述输出信号(即,所述第二边沿)而确定所述最终速率。85.例如,如图8所示,速率确定块230可以包括:第一多路复用器231,响应于锁定使能信号lock_en选择性地输出第一异或门221的所述输出信号或低电源电压vss;第二多路复用器232,响应于锁定使能信号lock_en选择性地输出第二异或门222的所述输出信号或低电源电压vss;第十一触发器241,响应于第一多路复用器231的输出信号对高电源电压vdd进行采样而生成第一速率检测信号rds1;以及第十二触发器242,响应于第二多路复用器232的输出信号对高电源电压vdd进行采样而生成第二速率检测信号rds2。86.如图9所示,具有低电平的第一速率检测信号rds1及具有所述低电平的第二速率检测信号rds2可以表示未检测到所述第一边沿及所述第二边沿,即,表示以第一数据速率dr1接收输入数据dat。据此,在第一速率检测信号rds1及第二速率检测信号rds2全部具有所述低电平的情况下,数字块180可以控制多速率相位检测器120以与第一数据速率dr1对应的全速率fullrate作为所述最终速率进行操作。并且,具有所述低电平的第一速率检测信号rds1及具有高电平的第二速率检测信号rds2可以表示未检测到所述第一边沿而检测到所述第二边沿,即,表示以作为第一数据速率dr1的两倍的第二数据速率dr2接收输入数据dat。据此,在第一速率检测信号rds1具有所述低电平且第二速率检测信号rds2具有所述高电平的情况下,数字块180可以控制多速率相位检测器120以与第二数据速率dr2对应的半速率halfrate作为所述最终速率进行操作。并且,具有所述高电平的第一速率检测信号rds1及具有所述高电平的第二速率检测信号rds2可以表示检测到所述第一边沿及所述第二边沿,即,表示以作为第二数据速率dr2的两倍的第三数据速率dr3接收输入数据dat。据此,在第一速率检测信号rds1及第二速率检测信号rds2全部具有所述高电平的情况下,数字块180可以控制多速率相位检测器120以与第三数据速率dr3对应的四分之一速率quarterrate作为所述最终速率进行操作。87.死区检测块250可以基于校准使能信号cal_en、所述最终速率、所述第一边沿、所述第二边沿及所述第三边沿判断多相位时钟信号mpck是否在所述死区内被锁定。88.例如,如图8所示,死区检测块250可以包括:第三多路复用器251,响应于校准使能信号cal_en选择性地输出第一异或门221的所述输出信号或低电源电压vss作为第一校准信号cal1;第四多路复用器252,响应于校准使能信号cal_en选择性地输出第二异或门222的所述输出信号或低电源电压vss作为第二校准信号cal2;第五多路复用器253,响应于校准使能信号cal_en选择性地输出第三异或门223的所述输出信号或低电源电压vss作为第三校准信号cal3;第一或门261,对第一校准信号cal1、第二校准信号cal2及第三校准信号cal3执行或运算而输出全速率校准信号full_cal;第二或门262,对第一校准信号cal1及第三校准信号cal3执行或运算而输出半速率校准信号half_cal;以及第六多路复用器270,响应于与所述最终速率对应的最终速率信号frates选择性地输出全速率校准信号full_cal、半速率校准信号half_cal或低电源电压vss作为死区检测信号dzds。89.具有高电平的第一校准信号cal1可以表示输入数据dat在约90度至约180度的所述第二相位范围内具有所述第一边沿,具有所述高电平的第二校准信号cal2表示输入数据dat在约180度至约270度的所述第三相位范围内具有所述第二边沿,具有所述高电平的第三校准信号cal3指示输入数据dat在约270度至约360度的所述第四相位范围内具有所述第三边沿。并且,第一或门261可以在第一校准信号cal1、第二校准信号cal2及第三校准信号cal3中的任意一个以上具有所述高电平时输出所述高电平的全速率校准信号full_cal,第二或门262在第一校准信号cal1及第三校准信号cal3中的一个以上具有所述高电平时输出所述高电平的半速率校准信号half_cal。并且,第六多路复用器270可以响应于与全速率fullrate对应的最终速率信号frates而输出全速率校准信号full_cal作为死区检测信号dzds,响应于与半速率halfrate对应的最终速率信号frates而输出半速率校准信号half_cal作为死区检测信号dzds,响应于与四分之一速率quarterrate对应的最终速率信号frates输出低电源电压vss作为死区检测信号dzds。90.据此,如图10所示,在最终速率信号frates对应于全速率fullrate的情况下,死区检测块250可以在第一校准信号cal1、第二校准信号cal2及第三校准信号cal3全部具有低电平时输出低电平的死区检测信号dzds,在第一校准信号cal1、第二校准信号cal2及第三校准信号cal3中的一个以上具有高电平时输出高电平的死区检测信号dzds。并且,在最终速率信号frates对应于半速率halfrate的情况下,死区检测块250可以在第一校准信号cal1及第三校准信号cal3全部具有低电平时输出低电平的死区检测信号dzds,而在第一校准信号cal1及第三校准信号cal3中的一个以上具有高电平时输出高电平的死区检测信号dzds。并且,在最终速率信号frates对应于四分之一速率quarterrate的情况下,死区检测块250可以与第一校准信号cal1、第二校准信号cal2及第三校准信号cal3无关地输出低电平的死区检测信号dzds。91.死区电荷泵280可以在多相位时钟信号mpck被判断为在所述死区内被锁定的情况下,向锁相环电路110中所包括的环路滤波器150提供附加电荷泵电流iacp。死区电荷泵280可以在死区检测信号dzds具有所述低电平的情况下不向环路滤波器150提供附加电荷泵电流iacp,在死区检测信号dzds具有所述高电平的情况下向环路滤波器150提供附加电荷泵电流iacp。在一实施例中,附加电荷泵电流iacp可以为负的电流,锁相环电路110基于由死区电荷泵280提供的附加电荷泵电流iacp增加多相位时钟信号mpck的所述相位。92.据此,如图11的附图标记610所示,在多速率相位检测器120以全速率fullrate被驱动的情况下,即使多相位时钟信号mpck在约45度至约315度的第一死区dz1被锁定,多相位时钟信号mpck的相位也可以通过附加电荷泵电流iacp而增加,并且多相位时钟信号mpck也可以在一般锁定点nlp被锁定。并且,如图11的附图标记630所示,在多速率相位检测器120以半速率halfrate被驱动的情况下,即使多相位时钟信号mpck在约90度至约270度的第二死区dz2被锁定,多相位时钟信号mpck的相位也可以通过附加电荷泵电流iacp而增加,并且多相位时钟信号mpck也可以在一般锁定点nlp被锁定。另外,如图11的附图标记650所示,在多速率相位检测器120以四分之一速率quarterrate被驱动的情况下,不存在死区,并且多相位时钟信号mpck可以在一般锁定点nlp被锁定。93.如上所述,在根据本发明的实施例的时钟数据恢复电路100中,多速率相位检测器120在初始区间以全速率fullrate进行操作,死区校准电路200响应于锁定使能信号lock_en而确定与数据速率dr1、dr2、dr3对应的所述最终速率,并且多速率相位检测器120以所述最终速率进行操作,死区校准电路200可以在响应于校准使能信号cal_en而判断多相位时钟信号mpck在所述死区内被锁定的情况下,执行变更多相位时钟信号mpck的相位的所述死区校准操作。据此,可以防止多相位时钟信号mpck在所述死区内被锁定,并且可以防止通过响应于多相位时钟信号mpck对输入数据dat进行采样而生成的恢复的数据rdat的错误。并且,由于时钟数据恢复电路100利用多速率相位检测器120,因此时钟数据恢复电路100可以具有小尺寸及低功耗。94.图12是示出根据本发明的实施例的时钟数据恢复电路的驱动方法的流程图。95.参照图1及图12,在显示装置的数据驱动器中所包括的时钟数据恢复电路100中,能够以多个速率进行操作的多速率相位检测器120在初始区间以作为所述多个速率中的预定的一个速率的初始速率进行操作,同时锁相环电路110可以基于输入数据dat生成多相位时钟信号mpck(s710)。在一实施例中,多速率相位检测器120的所述多个速率包括全速率、半速率及四分之一速率,所述初始速率可以为所述全速率。96.锁定检测器170可以检测锁相环电路110的锁定状态,并且在检测到所述锁定状态时生成锁定使能信号lock_en(s720)。死区校准电路200可以响应于锁定使能信号lock_en确定所述多个速率中与输入数据dat的数据速率对应的最终速率(s730)。97.数字块180可以控制多速率相位检测器120以所述最终速率进行操作(s740)。并且,数字块180可以生成校准使能信号cal_en。死区校准电路200可以响应于校准使能信号cal_en而判断多相位时钟信号mpck是否在死区内被锁定(s750)。死区校准电路200可以在多相位时钟信号mpck在所述死区内被锁定的情况下变更多相位时钟信号mpck的相位(s760)。据此,可以防止多相位时钟信号mpck在所述死区内被锁定,并且可以防止通过响应于多相位时钟信号mpck对输入数据dat进行采样而生成的恢复的数据rdat的错误。并且,由于时钟数据恢复电路100利用多速率相位检测器120,因此时钟数据恢复电路100可以具有小尺寸及低功耗。98.图13是示出根据本发明的实施例的显示装置的框图。99.参照图13,显示装置800可以包括:显示面板810,包括多个像素px;栅极驱动器820,向多个像素px提供栅极信号gs;数据驱动器830,向多个像素px提供数据信号ds;以及控制器850,控制栅极驱动器820及数据驱动器830。100.显示面板810可以包括多条数据线、多条栅极线以及连接于所述多条数据线和所述多条栅极线的多个像素px。在一实施例中,各个像素px可以包括开关晶体管以及连接于所述开关晶体管的液晶电容器,并且显示面板810可以是液晶显示器(lcd:liquidcrystaldisplay)面板。在另一实施例中,各个像素px可以包括至少两个晶体管、至少一个电容器以及有机发光二极管(oled:organiclightemittingdiode),并且显示面板810可以是oled显示面板。然而,显示面板810并不局限于所述lcd面板及所述oled显示面板,可以是任意的显示面板。101.栅极驱动器820可以基于从控制器850接收的栅极控制信号gctrl而生成栅极信号gs,并且通过所述多条栅极线向多个像素px提供栅极信号gs。在一实施例中,栅极控制信号gctrl可以包括栅极开始信号及栅极时钟信号,但并不局限于此。在一实施例中,栅极驱动器820可以被实现为集成在显示面板810的外围部的非晶硅栅极(asg:amorphoussilicongate)驱动器。在另一实施方式中,栅极驱动器820可以被实现为一个以上栅极集成电路(ic:integratedcircuit)。并且,根据实施例,栅极驱动器820可以直接贴装在显示面板810上,或者通过柔性膜以膜上芯片(cof:chiponfilm)形态连接于显示面板810。102.数据驱动器830可以包括从控制器850接收输入数据dat的时钟数据恢复电路840。时钟数据恢复电路840可以基于输入数据dat生成多相位时钟信号,并基于所述多相位时钟信号对输入数据dat进行采样而生成恢复的数据rdat。在一实施例中,时钟数据恢复电路840可以是图1的时钟数据恢复电路100。数据驱动器830可以基于恢复的数据rdat而生成数据信号ds,并通过所述多条数据线向多个像素px提供与恢复的数据rdat对应的数据信号ds。在一实施例中,数据驱动器830可以利用一个以上数据驱动器ic来实现。根据实施例,所述数据驱动器ic可以直接贴装(mounted)在显示面板810上,或者以cof形态连接于显示面板810。在另一实施例中,数据驱动器830可以集成(integrated)在显示面板810的外围部。103.控制器(例如,时序控制器(tcon:timingcontroller))850可以从外部的主机处理器(例如,图形处理单元(gpu:graphicprocessingunit)或图形卡)接收输入图像数据idat及控制信号ctrl。在一实施例中,输入图像数据idat可以是包括红色图像数据、绿色图像数据及蓝色图像数据的rgb图像数据。控制器850可以将输入图像数据idat转换为具有适合于数据驱动器830的形式的输入数据dat。并且,在一实施例中,控制信号ctrl可以包括垂直同步信号、水平同步信号、数据使能信号、主时钟信号等,但并不局限于此。控制器850可以基于输入图像数据idat及控制信号ctrl生成输入数据dat及栅极控制信号gctrl。控制器850可以向栅极驱动器820提供栅极控制信号gctrl而控制栅极驱动器820的操作,并且向数据驱动器830提供输入数据dat而控制数据驱动器830的操作。104.在根据本发明的实施例的显示装置800中,时钟数据恢复电路840的多速率相位检测器可以在初始区间以全速率进行操作,时钟数据恢复电路840的死区校准电路响应于锁定使能信号确定与输入数据dat的数据速率对应的最终速率,所述多速率相位检测器以所述最终速率进行操作,并且所述死区校准电路在响应于校准使能信号而判断所述多相位时钟信号在死区内被锁定的情况下执行变更所述多相位时钟信号的相位的死区校准操作。据此,可以防止所述多相位时钟信号在所述死区内被锁定,并且可以防止通过响应于所述多相位时钟信号对输入数据dat进行采样而生成的恢复的数据rdat的错误。并且,由于时钟数据恢复电路840利用所述多速率相位检测器,因此时钟数据恢复电路840可以具有小尺寸及低功耗。105.图14是示出根据本发明的实施例的包括显示装置的电子设备的框图。106.参照图14,电子设备1100可以包括处理器1110、存储器装置1120、存储装置1130、输入/输出装置1140、电源供应器1150及显示装置1160。电子设备1100还可以包括能够与视频卡、声卡、存储卡、usb装置等进行通信或者与其他系统进行通信的多个端口(port)。107.处理器1110可以执行特定计算或任务(task)。根据实施例,处理器1110可以是微处理器(microprocessor)、中央处理装置(cpu)等。处理器1110可以通过地址总线(addressbus)、控制总线(controlbus)及数据总线(databus)等连接于其他构成要素。根据实施例,处理器1110还可以连接于诸如外围构成要素互连(pci:peripheralcomponentinterconnect)总线的扩展总线。108.存储器装置1120可以存储电子设备1100的操作所需的数据。例如,存储器装置1120可以包括诸如可擦除可编程只读存储器(eprom:erasableprogrammableread‑onlymemory)、电可擦除可编程只读存储器(eeprom:electricallyerasableprogrammableread‑onlymemory)、闪存(flashmemory)、相变随机存取存储器(pram:phasechangerandomaccessmemory)、电阻随机存取存储器(rram:resistancerandomaccessmemory)、纳米浮栅存储器(nfgm:nanofloatinggatememory)、聚合物随机存取存储器(poram:polymerrandomaccessmemory)、磁随机存取存储器(mram:magneticrandomaccessmemory)、铁电随机存取存储器(fram:ferroelectricrandomaccessmemory)等非易失性存储器装置和/或诸如动态随机存取存储器(dram:dynamicrandomaccessmemory)、静态随机存取存储器(sram:staticrandomaccessmemory)、移动dram等易失性存储器装置。109.存储装置1130可以包括固态驱动器(ssd:solidstatedrive)、硬盘驱动器(hdd:harddiskdrive)、紧凑盘只读存储器(cd‑rom)等。输入/输出装置1140可以包括诸如键盘、小键盘、触摸板、触摸屏、鼠标等输入结构以及诸如扬声器、打印机等输出结构。电源供应器1150可以供应电子设备1100的操作所需的电源。显示装置1160可以通过所述总线或其他通信链路连接于其他构成要素。110.在显示装置1160中,数据驱动器中所包括的时钟数据恢复电路的多速率相位检测器可以在初始区间以全速率进行操作,所述时钟数据恢复电路的死区校准电路响应于锁定使能信号确定与输入数据的数据速率对应的最终速率,所述多速率相位检测器以所述最终速率进行操作,并且所述死区校准电路在响应于校准使能信号而判断多相位时钟信号在死区内被锁定的情况下执行变更所述多相位时钟信号的相位的死区校准操作。据此,可以防止所述多相位时钟信号在所述死区内被锁定,并且可以防止通过响应于所述多相位时钟信号对所述输入数据进行采样而生成的恢复的数据的错误。并且,由于所述时钟数据恢复电路利用所述多速率相位检测器,因此所述时钟数据恢复电路可以具有小尺寸及低功耗。111.根据实施例,电子设备1100可以是诸如数字电视(digitaltelevision)、3d电视、个人计算机(pc:personalcomputer)、家用电子设备、笔记本计算机(laptopcomputer)、平板计算机(tabletcomputer)、移动电话(mobilephone)、智能电话(smartphone)、个人数字助理(pda:personaldigitalassistant)、便携式多媒体播放器(pmp:portablemultimediaplayer)、数码相机(digitalcamera)、音乐播放器(musicplayer)、便携式游戏主机(portablegameconsole)、导航仪(navigation)等包括显示装置1160的任意的电子设备。112.产业上的可利用性113.本发明可以应用于数据驱动器执行时钟训练的任意的显示装置及包括该显示装置的电子设备。例如,本发明可以应用于包括显示装置的诸如电视(tv:television)、数字电视、3d电视、移动电话(mobilephone)、智能电话(smartphone)、平板计算机(tabletcomputer)、笔记本计算机(laptopcomputer)、个人计算机(pc:personalcomputer)、家用电子设备、个人数字助理(pda:personaldigitalassistant)、便携式多媒体播放器(pmp:portablemultimediaplayer)、数码相机(digitalcamera)、音乐播放器(musicplayer)、便携式游戏主机(portablegameconsole)、导航仪(navigation)等任意的电子设备。114.以上,虽然参照本发明的实施例进行了说明,但只要是本

技术领域:

:的熟练的技术人员,则应当能够理解在不脱离记载于权利要求书的本发明的思想及构思的范围内可以对本发明进行多种修改以及变更。当前第1页12当前第1页12

背景技术:

::2.显示装置的数据驱动器可以利用时钟数据恢复(cdr:clockdatarecovery)电路基于从所述显示装置的控制器接收的输入数据恢复时钟信号及数据。另外,所述输入数据可以根据显示面板的分辨率及帧频率而以多个数据速率中的一个数据速率进行传送,据此,要求所述cdr电路支持对应于所述多个数据速率的多速率。3.这样的多速率cdr电路可以划分为利用多速率相位检测器的多速率cdr电路以及利用多速率压控振荡器的多速率cdr电路。另外,与所述利用多速率压控振荡器的多速率cdr电路相比,所述利用多速率相位检测器的多速率cdr电路具有尺寸小且功耗低的优点。然而,在所述利用多速率相位检测器的多速率cdr电路中存在时钟信号可能被锁定在死区内的问题。技术实现要素:4.本发明的一目的在于提供一种能够防止时钟信号被锁定在死区内的时钟数据恢复电路。5.本发明的另一目的在于提供一种包括能够防止时钟信号被锁定在死区内的时钟数据恢复电路的显示装置。6.本发明的又一目的在于提供一种能够防止时钟信号被锁定在死区内的时钟数据恢复电路的驱动方法。7.但是,本发明所要解决的技术问题并不限于上述技术问题,本发明可以在不脱离本发明的思想及构思的范围内实现多种扩展。8.为了达成本发明的一目的,根据本发明的实施例的一种显示装置的数据驱动器中所包括的时钟数据恢复电路包括:锁相环电路,输入数据生成多相位时钟信号,并且包括能够以多个速率进行操作并在初始区间以作为所述多个速率中的预定的一个速率的初始速率进行操作的多速率相位检测器;锁定检测器,检测所述锁相环电路的锁定状态而生成锁定使能信号;死区校准电路,响应于所述锁定使能信号而确定所述多个速率中与所述输入数据的数据速率对应的最终速率;以及数字块,控制所述多速率相位检测器以所述最终速率进行操作,并且生成校准使能信号。所述死区校准电路响应于所述校准使能信号而判断所述多相位时钟信号是否在死区内被锁定,并且在所述多相位时钟信号在所述死区内被锁定的情况下,变更所述多相位时钟信号的相位。9.在一实施例中,所述多个速率可以包括所述多速率相位检测器在所述多相位时钟信号的每个周期执行相位检测的全速率、所述多速率相位检测器在所述多相位时钟信号的每半个周期执行所述相位检测的半速率以及所述多速率相位检测器在所述多相位时钟信号的每1/4个周期执行所述相位检测的四分之一速率,所述初始速率为所述全速率。10.在一实施例中,所述输入数据的所述数据速率可以为第一数据速率、作为所述第一数据速率的两倍的第二数据速率以及作为所述第二数据速率的两倍的第三数据速率中的一个数据速率,在所述输入数据的所述数据速率为所述第一数据速率的情况下,所述死区校准电路响应于所述锁定使能信号而将所述最终速率确定为所述全速率,在所述输入数据的所述数据速率为所述第二数据速率的情况下,所述死区校准电路响应于所述锁定使能信号而将所述最终速率确定为所述半速率,在所述输入数据的所述数据速率为所述第三数据速率的情况下,所述死区校准电路响应于所述锁定使能信号而将所述最终速率确定为所述四分之一速率。11.在一实施例中,与所述多相位时钟信号的一个周期对应的所述多相位时钟信号的相位范围可以被划分为第一相位范围、第二相位范围、第三相位范围及第四相位范围,所述多相位时钟信号通过以所述初始速率进行操作的所述多速率相位检测器在所述第一相位范围内被锁定,所述死区校准电路检测所述输入数据在所述第二相位范围内的第一边沿以及所述输入数据在所述第三相位范围内的第二边沿,在未检测到所述第一边沿及所述第二边沿的情况下,所述死区校准电路响应于所述锁定使能信号而将所述最终速率确定为所述全速率,在未检测到所述第一边沿并检测到所述第二边沿的情况下,所述死区校准电路响应于所述锁定使能信号而将所述最终速率确定为所述半速率,在检测到所述第一边沿及所述第二边沿的情况下,所述死区校准电路响应于所述锁定使能信号而将所述最终速率确定为所述四分之一速率。12.在一实施例中,所述死区校准电路还可以检测所述输入数据在所述第四相位范围内的第三边沿,在所述最终速率被确定为所述全速率的情况下,所述死区校准电路响应于所述校准使能信号而在检测到所述第一边沿、所述第二边沿和所述第三边沿中的至少一个边沿时判断所述多相位时钟信号在所述死区内被锁定,在所述最终速率被确定为所述半速率的情况下,所述死区校准电路响应于所述校准使能信号而在检测到所述第一边沿和所述第三边沿中的至少一个边沿时判断所述多相位时钟信号在所述死区内被锁定,在所述最终速率被确定为所述四分之一速率的情况下,所述死区校准电路响应于所述校准使能信号而判断所述多相位时钟信号未在所述死区内被锁定。13.在一实施例中,在所述多相位时钟信号被判断为在所述死区内被锁定的情况下,所述死区校准电路可以向所述锁相环电路中所包括的环路滤波器提供附加电荷泵电流,来变更所述多相位时钟信号的所述相位。14.在一实施例中,与所述多相位时钟信号的一个周期对应的所述多相位时钟信号的相位范围可以被划分为第一相位范围、第二相位范围、第三相位范围及第四相位范围,所述死区校准电路包括:边沿检测块,检测所述输入数据在所述第二相位范围内的第一边沿、所述输入数据在所述第三相位范围内的第二边沿以及所述输入数据在所述第四相位范围内的第三边沿;速率确定块,基于所述锁定使能信号、所述第一边沿、所述第二边沿而确定所述最终速率;死区检测块,基于所述校准使能信号、所述最终速率、所述第一边沿、所述第二边沿及所述第三边沿判断所述多相位时钟信号是否在所述死区内被锁定;以及死区电荷泵,在所述多相位时钟信号被判断为在所述死区内被锁定的情况下,向所述锁相环电路中所包括的环路滤波器提供附加电荷泵电流。15.在一实施例中,所述多相位时钟信号包括具有彼此不同的相位的第一时钟信号、第二时钟信号、第三时钟信号、第四时钟信号、第五时钟信号、第六时钟信号、第七时钟信号、第八时钟信号,所述边沿检测块包括:第一触发器,响应于所述第三时钟信号而对所述输入数据进行采样;第二触发器,响应于所述第五时钟信号而对所述输入数据进行采样;第三触发器,响应于所述第七时钟信号而对所述输入数据进行采样;第四触发器,响应于所述第一时钟信号而对所述输入数据进行采样;第一异或门,对所述第一触发器的输出信号及所述第二触发器的输出信号执行异或运算而检测所述第一边沿;第二异或门,对所述第二触发器的所述输出信号及所述第三触发器的输出信号执行异或运算而检测所述第二边沿;以及第三异或门,对所述第三触发器的所述输出信号及所述第四触发器的输出信号执行异或运算而检测所述第三边沿。16.在一实施例中,所述边沿检测块还可以包括:第五触发器,位于所述第一触发器与所述第一异或门之间,并且响应于所述第四时钟信号而对所述第一触发器的所述输出信号进行采样;第六触发器,位于所述第二触发器与所述第一异或门之间,并且响应于所述第六时钟信号而对所述第二触发器的所述输出信号进行采样;第七触发器,位于所述第二触发器与所述第二异或门之间,并且响应于所述第六时钟信号而对所述第二触发器的所述输出信号进行采样;第八触发器,位于所述第三触发器与所述第二异或门之间,并且响应于所述第六时钟信号而对所述第三触发器的所述输出信号进行采样;第九触发器,位于所述第三触发器与所述第三异或门之间,并且响应于所述第八时钟信号而对所述第三触发器的所述输出信号进行采样;以及第十触发器,位于所述第四触发器与所述第三异或门之间,并且响应于所述第八时钟信号而对所述第四触发器的所述输出信号进行采样。17.在一实施例中,所述速率确定块可以包括:第一多路复用器,响应于所述锁定使能信号而选择性地输出所述第一异或门的输出信号或低电源电压;第二多路复用器,响应于所述锁定使能信号而选择性地输出所述第二异或门的输出信号或所述低电源电压;第十一触发器,响应于所述第一多路复用器的输出信号而对高电源电压进行采样而生成第一速率检测信号;以及第十二触发器,响应于所述第二多路复用器的输出信号而对所述高电源电压进行采样而生成第二速率检测信号。18.在一实施例中,在所述第一速率检测信号及所述第二速率检测信号全部具有低电平的情况下,所述数字块可以控制所述多速率相位检测器以全速率作为所述最终速率进行操作,在所述第一速率检测信号具有所述低电平且所述第二速率检测信号具有高电平的情况下,所述数字块控制所述多速率相位检测器以半速率作为所述最终速率进行操作,在所述第一速率检测信号及所述第二速率检测信号全部具有所述高电平的情况下,所述数字块控制所述多速率相位检测器以四分之一速率作为所述最终速率进行操作。19.在一实施例中,所述死区检测块可以包括:第三多路复用器,响应于所述校准使能信号而选择性地输出所述第一异或门的输出信号或低电源电压作为第一校准信号;第四多路复用器,响应于所述校准使能信号而选择性地输出所述第二异或门的输出信号或所述低电源电压作为第二校准信号;第五多路复用器,响应于所述校准使能信号而选择性地输出所述第三异或门的输出信号或所述低电源电压作为第三校准信号;第一或门,对所述第一校准信号、所述第二校准信号及所述第三校准信号执行或运算而输出全速率校准信号;第二或门,对所述第一校准信号及所述第三校准信号执行或运算而输出半速率校准信号;以及第六多路复用器,响应于与所述最终速率对应的最终速率信号而选择性地输出所述全速率校准信号、所述半速率校准信号或所述低电源电压作为死区检测信号。20.在一实施例中,所述死区电荷泵可以在所述死区检测信号具有低电平的情况下不向所述环路滤波器提供所述附加电荷泵电流,而在所述死区检测信号具有高电平的情况下向所述环路滤波器提供所述附加电荷泵电流。21.在一实施例中,所述附加电荷泵电流可以为负的电流,所述锁相环电路基于由所述死区电荷泵提供的所述附加电荷泵电流而增加所述多相位时钟信号的所述相位。22.在一实施例中,所述多速率相位检测器可以检测所述输入数据与所述多相位时钟信号的相位差,所述锁相环电路还包括:电荷泵,响应于由所述多速率相位检测器检测的所述相位差而生成电荷泵电流;环路滤波器,对所述电荷泵电流进行滤波而生成控制电压;以及压控振荡器,基于所述控制电压生成所述多相位时钟信号。23.在一实施例中,所述多相位时钟信号包括具有彼此不同的相位的第一时钟信号、第二时钟信号、第三时钟信号、第四时钟信号、第五时钟信号、第六时钟信号、第七时钟信号、第八时钟信号,所述多速率相位检测器包括:第一触发器第二触发器、第三触发器、第四触发器、第五触发器、第六触发器、第七触发器、第八触发器,分别响应于所述第一时钟信号至第八时钟信号而对所述输入数据进行采样;第一异或门,包括第一输入端子、第二输入端子以及输出上行信号的第一输出端子;第二异或门,包括第三输入端子、第四输入端子以及输出下行信号的第二输出端子;第一开关块,响应于从所述数字块接收的数字码而向所述第一输入端子提供所述第一触发器的输出信号、所述第三触发器的输出信号、所述第五触发器的输出信号或所述第七触发器的输出信号;第二开关块,响应于所述数字码而向所述第二输入端子及所述第三输入端子提供所述第二触发器的输出信号、所述第四触发器的输出信号、所述第六触发器的输出信号或所述第八触发器的输出信号;以及第三开关块,响应于所述数字码而向所述第四输入端子提供所述第三触发器的所述输出信号、所述第五触发器的所述输出信号、所述第七触发器的所述输出信号或所述第一触发器的所述输出信号。24.在一实施例中,在所述最终速率被确定为全速率的情况下,所述多速率相位检测器可以输出所述第六触发器的所述输出信号作为恢复的数据,在所述最终速率被确定为半速率的情况下,所述多速率相位检测器输出所述第四触发器的所述输出信号及所述第八触发器的所述输出信号作为所述恢复的数据,在所述最终速率被确定为四分之一速率的情况下,所述多速率相位检测器输出所述第一触发器的所述输出信号、所述第三触发器的所述输出信号、所述第五触发器的所述输出信号及所述第七触发器的所述输出信号作为所述恢复的数据。25.为了达成本发明的另一目的,根据本发明的实施例的一种显示装置包括:显示面板,包括多个像素;数据驱动器,包括基于输入数据生成多相位时钟信号及恢复的数据的时钟数据恢复电路,并且向所述多个像素提供与所述恢复的数据对应的数据信号;以及控制器,向所述数据驱动器提供所述输入数据。所述时钟数据恢复电路包括:锁相环电路,基于所述输入数据生成所述多相位时钟信号,并且包括能够以多个速率进行操作并在初始区间以作为所述多个速率中的预定的一个速率的初始速率进行操作的多速率相位检测器;锁定检测器,检测所述锁相环电路的锁定状态而生成锁定使能信号;死区校准电路,响应于所述锁定使能信号而确定所述多个速率中与所述输入数据的数据速率对应的最终速率;以及数字块,控制所述多速率相位检测器以所述最终速率进行操作,并且生成校准使能信号。所述死区校准电路响应于所述校准使能信号而判断所述多相位时钟信号是否在死区内被锁定,并且在所述多相位时钟信号在所述死区内被锁定的情况下,变更所述多相位时钟信号的相位。26.为了达成本发明的又一目的,根据本发明的实施例的一种显示装置的数据驱动器中所包括的时钟数据恢复电路的驱动方法,包括如下步骤:使能够以多个速率进行操作的多速率相位检测器在初始区间以作为所述多个速率中的预定的一个速率的初始速率进行操作,来基于输入数据生成多相位时钟信号;检测包括所述多速率相位检测器的锁相环电路的锁定状态;确定所述多个速率中与所述输入数据的数据速率对应的最终速率;控制所述多速率相位检测器以所述最终速率进行操作;判断所述多相位时钟信号是否在死区内被锁定;以及在所述多相位时钟信号在所述死区内被锁定的情况下,变更所述多相位时钟信号的相位。27.在一实施例中,所述多速率相位检测器的所述多个速率可以包括全速率、半速率及四分之一速率,所述初始速率为所述全速率。28.在根据本发明的实施例的时钟数据恢复电路、显示装置及时钟数据恢复电路的驱动方法中,多速率相位检测器可以在初始区间以全速率进行操作,死区校准电路响应于锁定使能信号而确定与数据速率对应的最终速率,所述多速率相位检测器在所述初始区间后以所述最终速率进行操作,并且所述死区校准电路响应于校准使能信号而在判断多相位时钟信号在死区内被锁定的情况下执行变更所述多相位时钟信号的相位的死区校准操作。据此,可以防止所述多相位时钟信号在所述死区内被锁定,并防止恢复的数据的错误,并且可以减小所述时钟数据恢复电路的尺寸及功耗。29.然而,本发明的效果并不限于上述效果,其可以在不脱离本发明的思想及构思的范围内实现多种扩展。附图说明30.图1是示出根据本发明的实施例的时钟数据恢复电路的框图。31.图2是示出根据本发明的实施例的时钟数据恢复电路中所包括的锁相环电路的一示例的框图。32.图3是示出图2的锁相环电路中所包括的多速率相位检测器的一示例的框图。33.图4是示出根据相位检测速率的数字码的示例的图。34.图5是用于说明以全速率、半速率和四分之一速率进行操作的多速率相位检测器的相位检测的示例的时序图。35.图6是示出不包括死区校准电路的时钟数据恢复电路的多相位时钟信号的锁定点及死区的示例的图。36.图7是用于说明根据本发明的实施例的时钟数据恢复电路中所包括的多速率相位检测器在初始区间的操作的时序图。37.图8是示出根据本发明的实施例的时钟数据恢复电路中所包括的死区校准电路的一示例的框图。38.图9是示出根据第一速率检测信号及第二速率检测信号的最终速率的一示例的图。39.图10是用于说明根据最终速率信号、第一校准信号、第二校准信号及第三校准信号的死区检测信号的一示例的图。40.图11是示出根据本发明的实施例的时钟数据恢复电路的多相位时钟信号的锁定点及死区的示例的图。41.图12是示出根据本发明的实施例的时钟数据恢复电路的驱动方法的流程图。42.图13是示出根据本发明的实施例的显示装置的框图。43.图14是示出根据本发明的实施例的包括显示装置的电子设备的框图。44.附图标记说明45.100:时钟数据恢复电路ꢀꢀꢀꢀꢀꢀꢀꢀ110:锁相环电路46.120:多速率相位检测器ꢀꢀꢀꢀꢀꢀꢀꢀ140:电荷泵47.150:环路滤波器ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ160:压控振荡器48.170:锁定检测器ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ180:数字块49.200:死区校准电路ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ210:边沿检测块50.230:速率确定块ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ250:死区检测块51.280:死区电荷泵ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ800:显示装置52.810:显示面板ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ820:栅极驱动器53.830:数据驱动器ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ840:时钟数据恢复电路54.850:控制器具体实施方式55.以下,参照附图对本发明的优选实施例进行更详细的说明。针对附图上相同的构成要素使用相同的附图标记,并且省略针对相同的构成要素的重复说明。56.图1是示出根据本发明的实施例的时钟数据恢复电路的框图,图2是示出根据本发明的实施例的时钟数据恢复电路中所包括的锁相环电路的一示例的框图,图3是示出图2的锁相环电路中所包括的多速率相位检测器的一示例的框图,图4是示出根据相位检测速率的数字码的示例的图,图5是用于说明以全速率、半速率和四分之一速率进行操作的多速率相位检测器的相位检测的示例的时序图,图6是示出不包括死区校准电路的时钟数据恢复电路的多相位时钟信号的锁定点及死区的示例的图,图7是用于说明根据本发明的实施例的时钟数据恢复电路中所包括的多速率相位检测器在初始区间的操作的时序图,图8是示出根据本发明的实施例的时钟数据恢复电路中所包括的死区校准电路的一示例的框图,图9是示出根据第一速率检测信号及第二速率检测信号的最终速率的一示例的图,图10是用于说明根据最终速率信号、第一校准信号、第二校准信号及第三校准信号的死区检测信号的一示例的图,图11是示出根据本发明的实施例的时钟数据恢复电路的多相位时钟信号的锁定点及死区的示例的图。57.参照图1,根据本发明的实施例的显示装置的数据驱动器中所包括的时钟数据恢复电路100可以包括:锁相环电路110,基于输入数据dat生成多相位时钟信号mpck;锁定检测器170,检测锁相环电路110的锁定状态;数字块180,向锁相环电路110中所包括的多速率相位检测器120提供数字码dcode;以及死区校准电路200,执行针对多相位时钟信号mpck的死区校准(deadzonecalibration)操作。58.锁相环电路110可以从所述显示装置的控制器(例如,时序控制器(timingcontroller;tcon))接收输入数据dat,并基于输入数据dat生成多相位时钟信号mpck,并且响应于多相位时钟信号mpck而对输入数据dat进行采样来生成恢复的数据rdat。多相位时钟信号mpck可以包括具有彼此不同的相位的多个时钟信号。例如,多相位时钟信号mpck可以包括第一时钟信号至第八时钟信号,所述第一时钟信号至第八时钟信号在将一个周期等分为8份的时间点处具有边沿,即,具有将对应于所述一个周期的360度的相位等分为8份的相位。59.在一实施例中,锁相环电路110可以根据由所述数据驱动器驱动的显示面板的分辨率和/或帧频率而以多种数据速率dr1、dr2、dr3中的一个速率接收输入数据dat。例如,锁相环电路110可以在所述显示面板具有4k超高清晰度(uhd:ultrahighdefinition)分辨率并以约60hz的帧频率被驱动的情况下以约1gbps的第一数据速率dr1接收输入数据dat,在所述显示面板具有所述4kuhd分辨率并以约120hz的帧频率被驱动的情况下以作为第一数据速率dr1的两倍的约2gbps的第二数据速率dr2接收输入数据dat,在所述显示面板具有8kuhd分辨率并以约120hz的所述帧频率被驱动的情况下以作为第二数据速率dr2的两倍的约4gbps的第三数据速率dr3接收输入数据dat。为了支持这样的输入数据dat的多种数据速率dr1、dr2、dr3,锁相环电路110可以包括能够以多个速率进行操作的多速率相位检测器120。60.在一实施例中,如图2所示,锁相环电路110可以包括多速率相位检测器120、电荷泵140、环路滤波器150及压控振荡器160。多速率相位检测器120可以检测输入数据dat与多相位时钟信号mpck的相位差,并生成对应于所述相位差的信号(例如,上行信号up和/或下行信号dn)。例如,多速率相位检测器120可以在输入数据dat领先(lead)多相位时钟信号mpck的情况下生成上行信号up,而在多相位时钟信号mpck领先输入数据dat的情况下生成下行信号dn。电荷泵140可以响应于由多速率相位检测器120检测的所述相位差而生成电荷泵电流icp。例如,电荷泵140可以响应于上行信号up而向环路滤波器150提供正的电荷泵电流icp,而响应于下行信号dn而向环路滤波器150提供负的电荷泵电流icp,即,从环路滤波器150吸引(draw)电荷泵电流icp。环路滤波器150可以对电荷泵电流icp进行滤波而生成控制电压vc。例如,环路滤波器150可以响应于正的电荷泵电流icp而增加控制电压vc,而响应于负的电荷泵电流icp而减小控制电压vc。并且,在一实施例中,环路滤波器150可以去除多相位时钟信号mpck的高频噪声成分。压控振荡器160可以基于控制电压vc生成多相位时钟信号mpck。例如,压控振荡器160可以在控制电压vc增加时减小多相位时钟信号mpck的相位,而在控制电压vc减小时增加多相位时钟信号mpck的相位。在一实施例中,压控振荡器160可以是8‑相位(8‑phase)压控振荡器,所述8‑相位(8‑phase)压控振荡器生成具有彼此不同的相位的第一时钟信号ck0、第二时钟信号ck45、第三时钟信号ck90、第四时钟信号ck135、第五时钟信号ck180、第六时钟信号ck225、第七时钟信号ck270、第八时钟信号ck315作为多相位时钟信号mpck。例如,第一时钟信号ck0可以具有约0度的相位,第二时钟信号ck45具有约45度的相位,第三时钟信号ck90具有约90度的相位,第四时钟信号ck135具有约135度的相位,第五时钟信号ck180具有约180度的相位,第六时钟信号ck225具有约225度的相位,第七时钟信号ck270具有约270度的相位,第八时钟信号ck315具有约315度的相位。61.多速率相位检测器120可以以多个速率中的一个速率进行操作。在一实施例中,多速率相位检测器120可以以与输入数据dat的第一数据速率dr1对应的全速率fullrate、与作为第一数据速率dr1的两倍的第二数据速率dr2对应的半速率halfrate以及与作为第二数据速率dr2的两倍的第三数据速率dr3对应的四分之一速率quarterrate进行操作。在一实施例中,为了能够以全速率fullrate、半速率halfrate及四分之一速率quarterrate进行操作,如图3所示,多速率相位检测器120可以包括第一触发器121至第八触发器128、第一开关块131、第二开关块133、第三开关块135以及第一异或门137及第二异或门139。62.第一触发器121至第八触发器128可以分别响应于第一时钟信号ck0、第二时钟信号ck45、第三时钟信号ck90、第四时钟信号ck135、第五时钟信号ck180、第六时钟信号ck225、第七时钟信号ck270、第八时钟信号ck315对输入数据dat进行采样。例如,第一触发器121可以响应于具有约0度的相位的第一时钟信号ck0而对输入数据dat进行采样,第二触发器122响应于具有约45度的相位的第二时钟信号ck45而对输入数据dat进行采样,第三触发器123响应于具有约90度的相位的第三时钟信号ck90而对输入数据dat进行采样,第四触发器124响应于具有约135度的相位的第四时钟信号ck135而对输入数据dat进行采样,第五触发器125响应于具有约180度的相位的第五时钟信号ck180而对输入数据dat进行采样,第六触发器126响应于具有约255度的相位的第六时钟信号ck225而对输入数据dat进行采样,第七触发器127响应于具有约270度的相位的第七时钟信号ck270而对输入数据dat进行采样,第八触发器128响应于具有约315度的相位的第八时钟信号ck315而对输入数据dat进行采样。63.第一开关块131可以响应于从数字块180接收的数字码dcode向第一异或门137的第一输入端子提供第一触发器121的输出信号、第三触发器123的输出信号、第五触发器125的输出信号或第七触发器127的输出信号。例如,数字码dcode可以包括第一数字信号d1至第四数字信号d4,第一开关块131包括第一开关sw1至第四开关sw4。第一开关sw1可以响应于第一数字信号d1向所述第一输入端子传送第一触发器121的所述输出信号,第二开关sw2响应于第二数字信号d2向所述第一输入端子传送第三触发器123的所述输出信号,第三开关sw3响应于第三数字信号d3向所述第一输入端子传送第五触发器125的所述输出信号,第四开关sw4响应于第四数字信号d4向所述第一输入端子传送第七触发器127的所述输出信号。64.第二开关块133可以响应于数字码dcode向第一异或门137的第二输入端子及第二异或门139的第三输入端子提供第二触发器122的输出信号、第四触发器124的输出信号、第六触发器126的输出信号或第八触发器128的输出信号。例如,第二开关块133可以包括第五开关sw5至第八开关sw8。第五开关sw5可以响应于第一数字信号d1向所述第二输入端子及第三输入端子传送第二触发器122的所述输出信号,第六开关sw6响应于第二数字信号d2向所述第二输入端子及第三输入端子传送第四触发器124的所述输出信号,第七开关sw7响应于第三数字信号d3向所述第二输入端子及第三输入端子传送第六触发器126的所述输出信号,第八开关sw8响应于第四数字信号d4向所述第二输入端子及第三输入端子传送第八触发器128的所述输出信号。65.第三开关块135可以响应于数字码dcode向第二异或门139的第四输入端子提供第三触发器123的所述输出信号、第五触发器125的所述输出信号、第七触发器127的所述输出信号或第一触发器121的所述输出信号。例如,第三开关块135可以包括第九开关sw9至第十二开关sw12。第九开关sw9可以响应于第一数字信号d1向所述第四输入端子传送第三触发器123的所述输出信号,第十开关sw10响应于第二数字信号d2向所述第四输入端子传送第五触发器125的所述输出信号,第十一开关sw11响应于第三数字信号d3向所述第四输入端子传送第七触发器127的所述输出信号,第十二开关sw12响应于第四数字信号d4向所述第四输入端子传送第一触发器121的所述输出信号。66.第一异或门137可以在所述第一输入端子接收第一开关块131的输出信号,在所述第二输入端子接收第二开关块133的输出信号,并且对第一开关块131的所述输出信号及第二开关块133的所述输出信号执行异或运算而生成上行信号up,并在第一输出端子输出上行信号up。67.并且,第二异或门139可以在所述第三输入端子接收第二开关块133的所述输出信号,在所述第四输入端子接收第三开关块135的输出信号,并且对第二开关块133的所述输出信号及第三开关块135的所述输出信号执行异或运算而生成下行信号dn,并在第二输出端子处输出下行信号dn。68.为了以与输入数据dat的第一数据速率dr1对应的全速率fullrate驱动多速率相位检测器120,如图4所示,数字块180可以向多速率相位检测器120提供“1000”的数字码dcode。例如,多速率相位检测器120可以接收高电平的第一数字信号d1以及低电平的第二数字信号d2、第三数字信号d3及第四数字信号d4。响应于所述高电平的第一数字信号d1以及所述低电平的第二数字信号d2、第三数字信号d3及第四数字信号d4,第一开关块131可以输出第一触发器121的所述输出信号(即,在约0度的相位采样的输入数据dat),第二开关块133输出第二触发器122的所述输出信号(即,在约45度的相位采样的输入数据dat),第三开关块135输出第三触发器123的所述输出信号(即,在约90度的相位采样的输入数据dat)。第一异或门137可以对第一开关块131的所述输出信号(即,在约0度的相位采样的输入数据dat)以及第二开关块133的所述输出信号(即,在约45度的相位采样的输入数据dat)执行异或运算而生成上行信号up。据此,上行信号up可以在输入数据dat在多相位时钟信号mpck的约0度至约45度的相位范围内具有边沿的情况下具有高电平。另外,具有所述高电平的上行信号up表示输入数据dat领先多相位时钟信号mpck(即,具有约45度的相位的第二时钟信号ck45),并且锁相环电路110可以响应于具有所述高电平的上行信号up而减小多相位时钟信号mpck的相位。并且,第二异或门139可以对第二开关块133的所述输出信号(即,在约45度的相位采样的输入数据dat)以及第三开关块135的所述输出信号(即,在约90度的相位采样的输入数据dat)执行异或运算而生成下行信号dn。据此,下行信号dn可以在输入数据dat在多相位时钟信号mpck的约45度至约90度的相位范围内具有边沿的情况下具有高电平。另外,具有所述高电平的下行信号dn表示多相位时钟信号mpck(即,具有约45度的相位的第二时钟信号ck45)领先输入数据dat,并且锁相环电路110可以响应于具有所述高电平的下行信号dn增加多相位时钟信号mpck的相位。以这种方式,如图5的附图标记310所示,多速率相位检测器120在以与输入数据dat的约1gbps的第一数据速率dr1对应的全速率fullrate被驱动时,可以在多相位时钟信号mpck(例如,第一时钟信号ck0)的每个周期ped执行一次检测输入数据dat和多相位时钟信号mpck的相位差的相位检测。并且,在一实施例中,当多速率相位检测器120以全速率fullrate被驱动时,例如在多相位时钟信号mpck的相位被调整为输入数据dat在约45度的相位处具有边沿的情况下,多速率相位检测器120可以输出第六触发器126的所述输出信号(即,在约225度的相位处采样的输入数据dat)作为恢复的数据rdat。69.并且,为了以与输入数据dat的第二数据速率dr2对应的半速率halfrate驱动多速率相位检测器120,如图4所示,数字块180可以向多速率相位检测器120提供在一个周期ped内以“1000”及“0010”交替的数字码dcode。例如,多速率相位检测器120可以在周期ped的第一半部分接收所述高电平的第一数字信号d1以及所述低电平的第二数字信号d2、第三数字信号d3及第四数字信号d4,在周期ped的第二半部分接收所述高电平的第三数字信号d3以及所述低电平的第一数字信号d1、第二数字信号d2及第四数字信号d4。在这种情况下,多速率相位检测器120可以在输入数据dat在约0度至约45度的相位范围内具有边沿的情况下输出上行信号up,在输入数据dat在约45度至约90度的相位范围内具有边沿的情况下输出下行信号dn,在输入数据dat在约180度至约225度的相位范围内具有边沿的情况下输出上行信号up,在输入数据dat在约225度至约270度的相位范围内具有边沿的情况下输出下行信号dn。据此,如图5的附图标记330所示,多速率相位检测器120可以在以与输入数据dat的约2gbps的第二数据速率dr2对应的半速率halfrate被驱动时,在多相位时钟信号mpck的每半周期执行所述相位检测,即,在多相位时钟信号mpck的每个周期ped执行两次所述相位检测。并且,在一实施例中,当多速率相位检测器120以半速率halfrate被驱动时,例如,在多相位时钟信号mpck的相位被调整为输入数据dat在约45度及约225度的相位处具有边沿的情况下,多速率相位检测器120可以输出第四触发器124的所述输出信号(即,在约135度的相位采样的输入数据dat)以及第八触发器128的所述输出信号(即,在约315度的相位采样的输入数据dat)作为恢复的数据rdat。70.并且,为了以与输入数据dat的第三数据速率dr3对应的四分之一速率quarterrate驱动多速率相位检测器120,如图4所示,数字块180可以向多速率相位检测器120提供在一个周期ped内以“1000”、“0100”、“0010”及“0001”交替的数字码dcode。例如,多速率相位检测器120可以在周期ped的第一1/4处接收所述高电平的第一数字信号d1以及所述低电平的第二数字信号d2、第三数字信号d3及第四数字信号d4,在周期ped的第二1/4处接收所述高电平的第二数字信号d2以及所述低电平的第一数字信号d1、第三数字信号d3及第四数字信号d4,在周期ped的第三1/4处接收所述高电平的第三数字信号d3以及所述低电平的第一数字信号d1、第二数字信号d2及第四数字信号d4,在周期ped的第四1/4处接收所述高电平的第四数字信号d4以及所述低电平的第一数字信号d1、第二数字信号d2及第三数字信号d3。在这种情况下,多速率相位检测器120可以在输入数据dat在约0度至约45度的相位范围内具有边沿的情况下输出上行信号up,在输入数据dat在约45度至约90度的相位范围内具有边沿的情况下输出下行信号dn,在输入数据dat在约90度至约135度的相位范围内具有边沿的情况下输出上行信号up,在输入数据dat在约135度至约180度的相位范围内具有边沿的情况下输出下行信号dn,在输入数据dat在约180度至约225度的相位范围内具有边沿的情况下输出上行信号up,在输入数据dat在约225度至约270度的相位范围内具有边沿的情况下输出下行信号dn,在输入数据dat在约270度至约315度的相位范围内具有边沿的情况下输出上行信号up,在输入数据dat在约315度至约360度的相位范围内具有边沿的情况下输出下行信号dn。据此,如图5的附图标记350所示,多速率相位检测器120可以在以与输入数据dat的约4gbps的第三数据速率dr3对应的四分之一速率quarterrate被驱动时,在多相位时钟信号mpck的每个1/4周期执行所述相位检测,即,在多相位时钟信号mpck的每个周期ped执行四次所述相位检测。并且,在一实施例中,当多速率相位检测器120以四分之一速率quarterrate被驱动时,例如,当多相位时钟信号mpck的相位被调整为输入数据dat在约45度、约135度、约225度及约315度的相位处具有边沿时,多速率相位检测器120可以输出第一触发器121的所述输出信号(即,在约0度的相位采样的输入数据dat)、第三触发器123的所述输出信号(即,在约90度的相位采样的输入数据dat)、第五触发器125的所述输出信号(即,在约180度的相位采样的输入数据dat)及第七触发器127的输出信号(即,在约270度的相位采样的输入数据dat)作为恢复的数据rdat。71.另外,图2示出了锁相环电路110的构成的一示例,但是根据本发明的实施例的锁相环电路110的构成并不局限于图2的示例。并且,图3示出了多速率相位检测器120的构成的一示例,但是根据本发明的实施例的多速率相位检测器120的构成并不局限于图3的示例。72.另外,在时钟数据恢复电路100不包括死区校准电路200的情况下,如图6所示,多相位时钟信号mpck可以在不是一般锁定点nlp的死区dz1、dz2内被锁定。例如,如图6中的附图标记410所示,当多速率相位检测器120以与第一数据速率dr1对应的全速率fullrate被驱动时,在多相位时钟信号mpck(例如,第二时钟信号ck45)比输入数据dat落后约0单位区间(ui:unitinterval)至约0.125ui的情况下,即,在具有比输入数据dat大约0度至约45度的相位的情况下,上行信号up可以具有高于下行信号dn的电平,并且提供正的电荷泵电流icp,并且减小多相位时钟信号mpck的相位。在此,所述ui(unitinterval)可以对应于输入数据dat的各个比特的宽度或时间。并且,在第二时钟信号ck45比输入数据dat领先约0ui至约0.125ui的情况下,即,在具有比输入数据dat小约0度至约45度的相位的情况下,下行信号dn可以具有高于上行信号up的电平,并且提供负的电荷泵电流icp,并且增加多相位时钟信号mpck的相位。据此,在第二时钟信号ck45相对于输入数据dat具有约‑0.125ui至约0.125ui(即,约‑45度至约45度)的相位差(或者约0ui至约0.125ui及约0.875ui至约1ui(即,约0度至约45度及约315度至约360度)的相位差)的情况下,多相位时钟信号mpck可以被调整为第二时钟信号ck45相对于输入数据dat具有约0ui(即,约0度)的相位差,并且在一般锁定点nlp被锁定。然而,在第二时钟信号ck45相对于输入数据dat具有约0.125ui至约0.875ui(即,约45度至约315度)的相位差的情况下,可以不生成电荷泵电流icp,并且多相位时钟信号mpck不会被调整,并且不会在一般锁定点nlp被锁定。据此,当多速率相位检测器120以全速率fullrate被驱动时,可以存在约45度至约315度的第一死区dz1。并且,如图6的附图标记430所示,当多速率相位检测器120以与第二数据速率dr2对应的半速率halfrate被驱动时,在多相位时钟信号mpck(例如,第二时钟信号ck45)相对于输入数据dat具有约0ui至约0.25ui及约0.75ui至约1ui(即,约0度至约90度及约270度至约360度)的相位差的情况下,多相位时钟信号mpck可以在一般锁定点nlp被锁定。然而,当多速率相位检测器120以半速率halfrate被驱动时,可以存在约90度至约270度的第二死区dz2。另外,如图6的附图标记450所示,当多速率相位检测器120以与第三数据速率dr3对应的四分之一速率quarterrate被驱动时,多相位时钟信号mpck可以在一般锁定点nlp被锁定,并且可以不存在死区。73.然而,在根据本发明的实施例的包括死区校准电路200的时钟数据恢复电路100中,为了使多相位时钟信号mpck不在第一死区dz1及第二死区dz2内被锁定,多速率相位检测器120可以在初始区间与输入数据dat的数据速率无关地以预定的初始速率进行操作,在多相位时钟信号mpck被锁定之后,多速率相位检测器120以与输入数据dat的所述数据速率对应的最终速率进行操作,并且死区校准电路200执行变更在第一死区dz1及第二死区dz2内被锁定的多相位时钟信号mpck的相位的死区校准操作。74.例如,如图7所示,多速率相位检测器120可以在所述初始区间与输入数据dat的数据速率dr1、dr2、dr3无关地以全速率fullrate作为所述初始速率进行操作。在一实施例中,所述初始区间可以是从开始传送输入数据dat的时间点到多相位时钟信号mpck被锁定的时间点为止的区间,但是并不局限于此。即,在所述初始区间中,与输入数据dat是以约1gbps的第一数据速率dr1被接收,还是以约2gbps的第二数据速率dr2被接收,还是以约4gbps的第三数据速率dr3被接收无关地,数字块180可以向多速率相位检测器120提供“1000”的数字码dcode。据此,多速率相位检测器120可以如图7的附图标记510所示地利用第一时钟信号ck0、第二时钟信号ck45及第三时钟信号ck90对以约1gbps的第一数据速率dr1接收的输入数据dat执行所述相位检测,如图7的附图标记530所示地利用第一时钟信号ck0、第二时钟信号ck45及第三时钟信号ck90对以约2gbps的第二数据速率dr2接收的输入数据dat执行所述相位检测,如图7的附图标记550所示地利用第一时钟信号ck0、第二时钟信号ck45及第三时钟信号ck90对以约4gbps的第三数据速率dr3接收的输入数据dat执行所述相位检测。据此,与输入数据dat的数据速率dr1、dr2、dr3无关地,多相位时钟信号mpck可以在多相位时钟信号mpck的约0度至约90度的第一相位范围内被锁定。75.再次参照图1,若多相位时钟信号mpck在所述初始区间被锁定,则锁定检测器170可以检测锁相环电路110的锁定状态而生成锁定使能信号lock_en。例如,锁定检测器170可以在提供给压控振荡器160的控制电压vc在预定时间期间具有实质上恒定的电压电平的情况下生成锁定使能信号lock_en。76.死区校准电路200可以响应于锁定使能信号lock_en确定多速率相位检测器120的所述多个速率中与输入数据dat的数据速率dr1、dr2、dr3对应的最终速率。例如,死区校准电路200可以在输入数据dat的所述数据速率为第一数据速率dr1的情况下将所述最终速率确定为全速率fullrate,在输入数据dat的所述数据速率为作为第一数据速率dr1的两倍的第二数据速率dr2的情况下将所述最终速率确定为半速率halfrate,在输入数据dat的数据速率为作为第二数据速率dr2的两倍的第三数据速率dr3的情况下将所述最终速率确定为四分之一速率quarterrate。77.在一实施例中,与多相位时钟信号mpck的一个周期ped对应的多相位时钟信号mpck的约0度至约360度的相位范围被划分为约0度至约90度的第一相位范围、约90度至约180度的第二相位范围、约180度至约270度的第三相位范围及约270度至约360度的第四相位范围,多相位时钟信号mpck可以在约0度至约90度的所述第一相位范围内被在所述初始区间中以所述初始速率(例如,全速率fullrate)进行操作的多速率相位检测器120所锁定。死区校准电路200可以检测输入数据dat在约90度至约180度的所述第二相位范围内的第一边沿以及所述输入数据dat在约180度至约270度的所述第三相位范围内的第二边沿。并且,死区校准电路200可以在未检测到所述第一边沿及所述第二边沿的情况下响应于锁定使能信号lock_en将所述最终速率确定为全速率fullrate,在未检测到所述第一边沿并检测到所述第二边沿的情况下响应于锁定使能信号lock_en将所述最终速率确定为半速率halfrate,在检测到所述第一边沿及所述第二边沿的情况下响应于锁定使能信号lock_en将所述最终速率确定为四分之一速率quarterrate。78.数字块180可以控制多速率相位检测器120以由死区校准电路200确定的所述最终速率进行操作。例如,数字块180可以在所述最终速率被确定为全速率fullrate的情况下向多速率相位检测器120提供“1000”的数字码dcode,在所述最终速率被确定为半速率halfrate的情况下向多速率相位检测器120提供在一个周期ped内以“1000”及“0010”交替的数字码dcode,在所述最终速率被确定为四分之一速率quarterrate的情况下向多速率相位检测器120提供在一个周期ped内以“1000”、“0100”、“0010”及“0001”交替的数字码dcode。数字块180可以生成校准使能信号cal_en。在一实施例中,校准使能信号cal_en可以在多速率相位检测器120的所述最终速率被确定之后继续具有高电平,然而并不局限于此。在另一实施例中,在所述最终速率被确定之后,校准使能信号cal_en可以周期性地或非周期性地具有所述高电平。79.死区校准电路200可以响应于校准使能信号cal_en执行死区校准(deadzonecalibration)操作。在一实施例中,死区校准电路200可以响应校准使能信号cal_en判断多相位时钟信号mpck是否在死区内被锁定,并且在多相位时钟信号mpck在所述死区内被锁定的情况下变更多相位时钟信号mpck的相位。80.在一实施例中,死区校准电路200还可以检测输入数据dat在约270度至约360度的所述第四相位范围内的第三边沿。在所述最终速率被确定为全速率fullrate的情况下,死区校准电路200可以响应于校准使能信号cal_en,当检测到所述第一边沿、所述第二边沿或所述第三边沿时判断多相位时钟信号mpck在所述死区内被锁定,而当未检测到所述第一边沿、所述第二边沿及所述第三边沿时判断多相位时钟信号mpck未在所述死区内未被锁定。并且,在所述最终速率被确定为半速率halfrate的情况下,死区校准电路200可以响应于校准使能信号cal_en,当检测到所述第一边沿或所述第三边沿时判断多相位时钟信号mpck在所述死区内被锁定,当未检测到所述第一边沿及所述第三边沿时判断多相位时钟信号mpck未在所述死区内被锁定。并且,在所述最终速率被确定为四分之一速率quarterrate的情况下,死区校准电路200可以响应于校准使能信号cal_en判断多相位时钟信号mpck未在所述死区内被锁定。死区校准电路200可以在判断多相位时钟信号mpck在所述死区内被锁定的情况下向锁相环电路110中所包括的环路滤波器150提供附加电荷泵电流iacp,以变更多相位时钟信号mpck的所述相位。81.在一实施例中,为了确定所述最终速率并执行所述死区校准操作,如图8所示,死区校准电路200可以包括边沿检测块210、速率确定块230、死区检测块250及死区电荷泵280。82.边沿检测块210可以检测输入数据dat在约90度至约180度的所述第二相位范围内的所述第一边沿、输入数据dat在约180度至约270度的所述第三相位范围内的所述第二边沿以及输入数据dat在约270度至约360度的所述第四相位范围内的所述第三边沿。83.例如,如图8所示,边沿检测块210包括:第一触发器211,响应于具有约90度的相位的第三时钟信号ck90而对输入数据dat进行采样;第二触发器212,响应于具有约180度的相位的第五时钟信号ck180而对输入数据dat进行采样;第三触发器213,响应于具有约270度的相位的第七时钟信号ck270而对输入数据dat进行采样;第四触发器214,响应于具有约0度的相位(即,约360度的相位)的第一时钟信号ck0而对输入数据dat进行采样;第一异或门221,对第一触发器211的输出信号及第二触发器212的输出信号执行异或运算而检测所述第一边沿;第二异或门222,对第二触发器212的所述输出信号及第三触发器213的输出信号执行异或运算而检测所述第二边沿;以及第三异或门223,对第三触发器213的所述输出信号及第四触发器214的输出信号执行异或运算而检测所述第三边沿。在一实施例中,边沿检测块210还可包括用于第一触发器211至第四触发器214的所述输出信号的对齐(align)的第五触发器215至第十触发器220。例如,第五触发器215可以位于第一触发器211与第一异或门221之间,并且响应于具有约135度的相位的第四时钟信号ck135而对第一触发器211的所述输出信号进行采样。第六触发器216可以位于第二触发器212与第一异或门221之间,并且响应于具有约225度的相位的第六时钟信号ck225而对第二触发器212的所述输出信号进行采样。第七触发器217可以位于第二触发器212与第二异或门222之间,并且响应于具有约225度的相位的第六时钟信号ck225而对第二触发器212的所述输出信号进行采样。第八触发器218可以位于第三触发器213与第二异或门222之间,并且响应于具有约225度的相位的第六时钟信号ck225而对第三触发器213的所述输出信号进行采样。第九触发器219可以位于第三触发器213与第三异或门223之间,并且响应于具有约315度的相位的第八时钟信号ck315而对第三触发器213的所述输出信号进行采样。第十触发器220可以位于第四触发器214与第三异或门223之间,并且响应于具有约315度的相位的第八时钟信号ck315而对第四触发器214的所述输出信号进行采样。84.速率确定块230可以基于锁定使能信号lock_en、第一异或门221的所述输出信号(即,所述第一边沿)及第二异或门222的所述输出信号(即,所述第二边沿)而确定所述最终速率。85.例如,如图8所示,速率确定块230可以包括:第一多路复用器231,响应于锁定使能信号lock_en选择性地输出第一异或门221的所述输出信号或低电源电压vss;第二多路复用器232,响应于锁定使能信号lock_en选择性地输出第二异或门222的所述输出信号或低电源电压vss;第十一触发器241,响应于第一多路复用器231的输出信号对高电源电压vdd进行采样而生成第一速率检测信号rds1;以及第十二触发器242,响应于第二多路复用器232的输出信号对高电源电压vdd进行采样而生成第二速率检测信号rds2。86.如图9所示,具有低电平的第一速率检测信号rds1及具有所述低电平的第二速率检测信号rds2可以表示未检测到所述第一边沿及所述第二边沿,即,表示以第一数据速率dr1接收输入数据dat。据此,在第一速率检测信号rds1及第二速率检测信号rds2全部具有所述低电平的情况下,数字块180可以控制多速率相位检测器120以与第一数据速率dr1对应的全速率fullrate作为所述最终速率进行操作。并且,具有所述低电平的第一速率检测信号rds1及具有高电平的第二速率检测信号rds2可以表示未检测到所述第一边沿而检测到所述第二边沿,即,表示以作为第一数据速率dr1的两倍的第二数据速率dr2接收输入数据dat。据此,在第一速率检测信号rds1具有所述低电平且第二速率检测信号rds2具有所述高电平的情况下,数字块180可以控制多速率相位检测器120以与第二数据速率dr2对应的半速率halfrate作为所述最终速率进行操作。并且,具有所述高电平的第一速率检测信号rds1及具有所述高电平的第二速率检测信号rds2可以表示检测到所述第一边沿及所述第二边沿,即,表示以作为第二数据速率dr2的两倍的第三数据速率dr3接收输入数据dat。据此,在第一速率检测信号rds1及第二速率检测信号rds2全部具有所述高电平的情况下,数字块180可以控制多速率相位检测器120以与第三数据速率dr3对应的四分之一速率quarterrate作为所述最终速率进行操作。87.死区检测块250可以基于校准使能信号cal_en、所述最终速率、所述第一边沿、所述第二边沿及所述第三边沿判断多相位时钟信号mpck是否在所述死区内被锁定。88.例如,如图8所示,死区检测块250可以包括:第三多路复用器251,响应于校准使能信号cal_en选择性地输出第一异或门221的所述输出信号或低电源电压vss作为第一校准信号cal1;第四多路复用器252,响应于校准使能信号cal_en选择性地输出第二异或门222的所述输出信号或低电源电压vss作为第二校准信号cal2;第五多路复用器253,响应于校准使能信号cal_en选择性地输出第三异或门223的所述输出信号或低电源电压vss作为第三校准信号cal3;第一或门261,对第一校准信号cal1、第二校准信号cal2及第三校准信号cal3执行或运算而输出全速率校准信号full_cal;第二或门262,对第一校准信号cal1及第三校准信号cal3执行或运算而输出半速率校准信号half_cal;以及第六多路复用器270,响应于与所述最终速率对应的最终速率信号frates选择性地输出全速率校准信号full_cal、半速率校准信号half_cal或低电源电压vss作为死区检测信号dzds。89.具有高电平的第一校准信号cal1可以表示输入数据dat在约90度至约180度的所述第二相位范围内具有所述第一边沿,具有所述高电平的第二校准信号cal2表示输入数据dat在约180度至约270度的所述第三相位范围内具有所述第二边沿,具有所述高电平的第三校准信号cal3指示输入数据dat在约270度至约360度的所述第四相位范围内具有所述第三边沿。并且,第一或门261可以在第一校准信号cal1、第二校准信号cal2及第三校准信号cal3中的任意一个以上具有所述高电平时输出所述高电平的全速率校准信号full_cal,第二或门262在第一校准信号cal1及第三校准信号cal3中的一个以上具有所述高电平时输出所述高电平的半速率校准信号half_cal。并且,第六多路复用器270可以响应于与全速率fullrate对应的最终速率信号frates而输出全速率校准信号full_cal作为死区检测信号dzds,响应于与半速率halfrate对应的最终速率信号frates而输出半速率校准信号half_cal作为死区检测信号dzds,响应于与四分之一速率quarterrate对应的最终速率信号frates输出低电源电压vss作为死区检测信号dzds。90.据此,如图10所示,在最终速率信号frates对应于全速率fullrate的情况下,死区检测块250可以在第一校准信号cal1、第二校准信号cal2及第三校准信号cal3全部具有低电平时输出低电平的死区检测信号dzds,在第一校准信号cal1、第二校准信号cal2及第三校准信号cal3中的一个以上具有高电平时输出高电平的死区检测信号dzds。并且,在最终速率信号frates对应于半速率halfrate的情况下,死区检测块250可以在第一校准信号cal1及第三校准信号cal3全部具有低电平时输出低电平的死区检测信号dzds,而在第一校准信号cal1及第三校准信号cal3中的一个以上具有高电平时输出高电平的死区检测信号dzds。并且,在最终速率信号frates对应于四分之一速率quarterrate的情况下,死区检测块250可以与第一校准信号cal1、第二校准信号cal2及第三校准信号cal3无关地输出低电平的死区检测信号dzds。91.死区电荷泵280可以在多相位时钟信号mpck被判断为在所述死区内被锁定的情况下,向锁相环电路110中所包括的环路滤波器150提供附加电荷泵电流iacp。死区电荷泵280可以在死区检测信号dzds具有所述低电平的情况下不向环路滤波器150提供附加电荷泵电流iacp,在死区检测信号dzds具有所述高电平的情况下向环路滤波器150提供附加电荷泵电流iacp。在一实施例中,附加电荷泵电流iacp可以为负的电流,锁相环电路110基于由死区电荷泵280提供的附加电荷泵电流iacp增加多相位时钟信号mpck的所述相位。92.据此,如图11的附图标记610所示,在多速率相位检测器120以全速率fullrate被驱动的情况下,即使多相位时钟信号mpck在约45度至约315度的第一死区dz1被锁定,多相位时钟信号mpck的相位也可以通过附加电荷泵电流iacp而增加,并且多相位时钟信号mpck也可以在一般锁定点nlp被锁定。并且,如图11的附图标记630所示,在多速率相位检测器120以半速率halfrate被驱动的情况下,即使多相位时钟信号mpck在约90度至约270度的第二死区dz2被锁定,多相位时钟信号mpck的相位也可以通过附加电荷泵电流iacp而增加,并且多相位时钟信号mpck也可以在一般锁定点nlp被锁定。另外,如图11的附图标记650所示,在多速率相位检测器120以四分之一速率quarterrate被驱动的情况下,不存在死区,并且多相位时钟信号mpck可以在一般锁定点nlp被锁定。93.如上所述,在根据本发明的实施例的时钟数据恢复电路100中,多速率相位检测器120在初始区间以全速率fullrate进行操作,死区校准电路200响应于锁定使能信号lock_en而确定与数据速率dr1、dr2、dr3对应的所述最终速率,并且多速率相位检测器120以所述最终速率进行操作,死区校准电路200可以在响应于校准使能信号cal_en而判断多相位时钟信号mpck在所述死区内被锁定的情况下,执行变更多相位时钟信号mpck的相位的所述死区校准操作。据此,可以防止多相位时钟信号mpck在所述死区内被锁定,并且可以防止通过响应于多相位时钟信号mpck对输入数据dat进行采样而生成的恢复的数据rdat的错误。并且,由于时钟数据恢复电路100利用多速率相位检测器120,因此时钟数据恢复电路100可以具有小尺寸及低功耗。94.图12是示出根据本发明的实施例的时钟数据恢复电路的驱动方法的流程图。95.参照图1及图12,在显示装置的数据驱动器中所包括的时钟数据恢复电路100中,能够以多个速率进行操作的多速率相位检测器120在初始区间以作为所述多个速率中的预定的一个速率的初始速率进行操作,同时锁相环电路110可以基于输入数据dat生成多相位时钟信号mpck(s710)。在一实施例中,多速率相位检测器120的所述多个速率包括全速率、半速率及四分之一速率,所述初始速率可以为所述全速率。96.锁定检测器170可以检测锁相环电路110的锁定状态,并且在检测到所述锁定状态时生成锁定使能信号lock_en(s720)。死区校准电路200可以响应于锁定使能信号lock_en确定所述多个速率中与输入数据dat的数据速率对应的最终速率(s730)。97.数字块180可以控制多速率相位检测器120以所述最终速率进行操作(s740)。并且,数字块180可以生成校准使能信号cal_en。死区校准电路200可以响应于校准使能信号cal_en而判断多相位时钟信号mpck是否在死区内被锁定(s750)。死区校准电路200可以在多相位时钟信号mpck在所述死区内被锁定的情况下变更多相位时钟信号mpck的相位(s760)。据此,可以防止多相位时钟信号mpck在所述死区内被锁定,并且可以防止通过响应于多相位时钟信号mpck对输入数据dat进行采样而生成的恢复的数据rdat的错误。并且,由于时钟数据恢复电路100利用多速率相位检测器120,因此时钟数据恢复电路100可以具有小尺寸及低功耗。98.图13是示出根据本发明的实施例的显示装置的框图。99.参照图13,显示装置800可以包括:显示面板810,包括多个像素px;栅极驱动器820,向多个像素px提供栅极信号gs;数据驱动器830,向多个像素px提供数据信号ds;以及控制器850,控制栅极驱动器820及数据驱动器830。100.显示面板810可以包括多条数据线、多条栅极线以及连接于所述多条数据线和所述多条栅极线的多个像素px。在一实施例中,各个像素px可以包括开关晶体管以及连接于所述开关晶体管的液晶电容器,并且显示面板810可以是液晶显示器(lcd:liquidcrystaldisplay)面板。在另一实施例中,各个像素px可以包括至少两个晶体管、至少一个电容器以及有机发光二极管(oled:organiclightemittingdiode),并且显示面板810可以是oled显示面板。然而,显示面板810并不局限于所述lcd面板及所述oled显示面板,可以是任意的显示面板。101.栅极驱动器820可以基于从控制器850接收的栅极控制信号gctrl而生成栅极信号gs,并且通过所述多条栅极线向多个像素px提供栅极信号gs。在一实施例中,栅极控制信号gctrl可以包括栅极开始信号及栅极时钟信号,但并不局限于此。在一实施例中,栅极驱动器820可以被实现为集成在显示面板810的外围部的非晶硅栅极(asg:amorphoussilicongate)驱动器。在另一实施方式中,栅极驱动器820可以被实现为一个以上栅极集成电路(ic:integratedcircuit)。并且,根据实施例,栅极驱动器820可以直接贴装在显示面板810上,或者通过柔性膜以膜上芯片(cof:chiponfilm)形态连接于显示面板810。102.数据驱动器830可以包括从控制器850接收输入数据dat的时钟数据恢复电路840。时钟数据恢复电路840可以基于输入数据dat生成多相位时钟信号,并基于所述多相位时钟信号对输入数据dat进行采样而生成恢复的数据rdat。在一实施例中,时钟数据恢复电路840可以是图1的时钟数据恢复电路100。数据驱动器830可以基于恢复的数据rdat而生成数据信号ds,并通过所述多条数据线向多个像素px提供与恢复的数据rdat对应的数据信号ds。在一实施例中,数据驱动器830可以利用一个以上数据驱动器ic来实现。根据实施例,所述数据驱动器ic可以直接贴装(mounted)在显示面板810上,或者以cof形态连接于显示面板810。在另一实施例中,数据驱动器830可以集成(integrated)在显示面板810的外围部。103.控制器(例如,时序控制器(tcon:timingcontroller))850可以从外部的主机处理器(例如,图形处理单元(gpu:graphicprocessingunit)或图形卡)接收输入图像数据idat及控制信号ctrl。在一实施例中,输入图像数据idat可以是包括红色图像数据、绿色图像数据及蓝色图像数据的rgb图像数据。控制器850可以将输入图像数据idat转换为具有适合于数据驱动器830的形式的输入数据dat。并且,在一实施例中,控制信号ctrl可以包括垂直同步信号、水平同步信号、数据使能信号、主时钟信号等,但并不局限于此。控制器850可以基于输入图像数据idat及控制信号ctrl生成输入数据dat及栅极控制信号gctrl。控制器850可以向栅极驱动器820提供栅极控制信号gctrl而控制栅极驱动器820的操作,并且向数据驱动器830提供输入数据dat而控制数据驱动器830的操作。104.在根据本发明的实施例的显示装置800中,时钟数据恢复电路840的多速率相位检测器可以在初始区间以全速率进行操作,时钟数据恢复电路840的死区校准电路响应于锁定使能信号确定与输入数据dat的数据速率对应的最终速率,所述多速率相位检测器以所述最终速率进行操作,并且所述死区校准电路在响应于校准使能信号而判断所述多相位时钟信号在死区内被锁定的情况下执行变更所述多相位时钟信号的相位的死区校准操作。据此,可以防止所述多相位时钟信号在所述死区内被锁定,并且可以防止通过响应于所述多相位时钟信号对输入数据dat进行采样而生成的恢复的数据rdat的错误。并且,由于时钟数据恢复电路840利用所述多速率相位检测器,因此时钟数据恢复电路840可以具有小尺寸及低功耗。105.图14是示出根据本发明的实施例的包括显示装置的电子设备的框图。106.参照图14,电子设备1100可以包括处理器1110、存储器装置1120、存储装置1130、输入/输出装置1140、电源供应器1150及显示装置1160。电子设备1100还可以包括能够与视频卡、声卡、存储卡、usb装置等进行通信或者与其他系统进行通信的多个端口(port)。107.处理器1110可以执行特定计算或任务(task)。根据实施例,处理器1110可以是微处理器(microprocessor)、中央处理装置(cpu)等。处理器1110可以通过地址总线(addressbus)、控制总线(controlbus)及数据总线(databus)等连接于其他构成要素。根据实施例,处理器1110还可以连接于诸如外围构成要素互连(pci:peripheralcomponentinterconnect)总线的扩展总线。108.存储器装置1120可以存储电子设备1100的操作所需的数据。例如,存储器装置1120可以包括诸如可擦除可编程只读存储器(eprom:erasableprogrammableread‑onlymemory)、电可擦除可编程只读存储器(eeprom:electricallyerasableprogrammableread‑onlymemory)、闪存(flashmemory)、相变随机存取存储器(pram:phasechangerandomaccessmemory)、电阻随机存取存储器(rram:resistancerandomaccessmemory)、纳米浮栅存储器(nfgm:nanofloatinggatememory)、聚合物随机存取存储器(poram:polymerrandomaccessmemory)、磁随机存取存储器(mram:magneticrandomaccessmemory)、铁电随机存取存储器(fram:ferroelectricrandomaccessmemory)等非易失性存储器装置和/或诸如动态随机存取存储器(dram:dynamicrandomaccessmemory)、静态随机存取存储器(sram:staticrandomaccessmemory)、移动dram等易失性存储器装置。109.存储装置1130可以包括固态驱动器(ssd:solidstatedrive)、硬盘驱动器(hdd:harddiskdrive)、紧凑盘只读存储器(cd‑rom)等。输入/输出装置1140可以包括诸如键盘、小键盘、触摸板、触摸屏、鼠标等输入结构以及诸如扬声器、打印机等输出结构。电源供应器1150可以供应电子设备1100的操作所需的电源。显示装置1160可以通过所述总线或其他通信链路连接于其他构成要素。110.在显示装置1160中,数据驱动器中所包括的时钟数据恢复电路的多速率相位检测器可以在初始区间以全速率进行操作,所述时钟数据恢复电路的死区校准电路响应于锁定使能信号确定与输入数据的数据速率对应的最终速率,所述多速率相位检测器以所述最终速率进行操作,并且所述死区校准电路在响应于校准使能信号而判断多相位时钟信号在死区内被锁定的情况下执行变更所述多相位时钟信号的相位的死区校准操作。据此,可以防止所述多相位时钟信号在所述死区内被锁定,并且可以防止通过响应于所述多相位时钟信号对所述输入数据进行采样而生成的恢复的数据的错误。并且,由于所述时钟数据恢复电路利用所述多速率相位检测器,因此所述时钟数据恢复电路可以具有小尺寸及低功耗。111.根据实施例,电子设备1100可以是诸如数字电视(digitaltelevision)、3d电视、个人计算机(pc:personalcomputer)、家用电子设备、笔记本计算机(laptopcomputer)、平板计算机(tabletcomputer)、移动电话(mobilephone)、智能电话(smartphone)、个人数字助理(pda:personaldigitalassistant)、便携式多媒体播放器(pmp:portablemultimediaplayer)、数码相机(digitalcamera)、音乐播放器(musicplayer)、便携式游戏主机(portablegameconsole)、导航仪(navigation)等包括显示装置1160的任意的电子设备。112.产业上的可利用性113.本发明可以应用于数据驱动器执行时钟训练的任意的显示装置及包括该显示装置的电子设备。例如,本发明可以应用于包括显示装置的诸如电视(tv:television)、数字电视、3d电视、移动电话(mobilephone)、智能电话(smartphone)、平板计算机(tabletcomputer)、笔记本计算机(laptopcomputer)、个人计算机(pc:personalcomputer)、家用电子设备、个人数字助理(pda:personaldigitalassistant)、便携式多媒体播放器(pmp:portablemultimediaplayer)、数码相机(digitalcamera)、音乐播放器(musicplayer)、便携式游戏主机(portablegameconsole)、导航仪(navigation)等任意的电子设备。114.以上,虽然参照本发明的实施例进行了说明,但只要是本

技术领域:

:的熟练的技术人员,则应当能够理解在不脱离记载于权利要求书的本发明的思想及构思的范围内可以对本发明进行多种修改以及变更。当前第1页12当前第1页12

再多了解一些

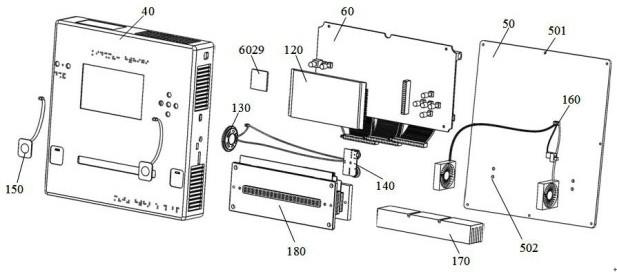

本文用于企业家、创业者技术爱好者查询,结果仅供参考。