技术特征:

1.一种显示装置的数据驱动器中所包括的时钟数据恢复电路,其特征在于,包括:锁相环电路,基于输入数据生成多相位时钟信号,并且包括能够以多个速率进行操作并在初始区间以作为所述多个速率中的预定的一个速率的初始速率进行操作的多速率相位检测器;锁定检测器,检测所述锁相环电路的锁定状态而生成锁定使能信号;死区校准电路,响应于所述锁定使能信号而确定所述多个速率中与所述输入数据的数据速率对应的最终速率;以及数字块,控制所述多速率相位检测器以所述最终速率进行操作,并且生成校准使能信号,其中,所述死区校准电路响应于所述校准使能信号而判断所述多相位时钟信号是否在死区内被锁定,并且在所述多相位时钟信号在所述死区内被锁定的情况下,变更所述多相位时钟信号的相位。2.根据权利要求1所述的时钟数据恢复电路,其特征在于,所述多个速率包括所述多速率相位检测器在所述多相位时钟信号的每个周期执行相位检测的全速率、所述多速率相位检测器在所述多相位时钟信号的每半个周期执行所述相位检测的半速率以及所述多速率相位检测器在所述多相位时钟信号的每1/4个周期执行所述相位检测的四分之一速率,所述初始速率为所述全速率。3.根据权利要求2所述的时钟数据恢复电路,其特征在于,所述输入数据的所述数据速率为第一数据速率、作为所述第一数据速率的两倍的第二数据速率以及作为所述第二数据速率的两倍的第三数据速率中的一个数据速率,在所述输入数据的所述数据速率为所述第一数据速率的情况下,所述死区校准电路响应于所述锁定使能信号而将所述最终速率确定为所述全速率,在所述输入数据的所述数据速率为所述第二数据速率的情况下,所述死区校准电路响应于所述锁定使能信号而将所述最终速率确定为所述半速率,在所述输入数据的所述数据速率为所述第三数据速率的情况下,所述死区校准电路响应于所述锁定使能信号而将所述最终速率确定为所述四分之一速率。4.根据权利要求2所述的时钟数据恢复电路,其特征在于,与所述多相位时钟信号的一个周期对应的所述多相位时钟信号的相位范围被划分为第一相位范围、第二相位范围、第三相位范围及第四相位范围,所述多相位时钟信号通过以所述初始速率进行操作的所述多速率相位检测器在所述第一相位范围内被锁定,所述死区校准电路检测所述输入数据在所述第二相位范围内的第一边沿以及所述输入数据在所述第三相位范围内的第二边沿,在未检测到所述第一边沿及所述第二边沿的情况下,所述死区校准电路响应于所述锁定使能信号而将所述最终速率确定为所述全速率,在未检测到所述第一边沿并检测到所述第二边沿的情况下,所述死区校准电路响应于所述锁定使能信号而将所述最终速率确定为所述半速率,在检测到所述第一边沿及所述第二边沿的情况下,所述死区校准电路响应于所述锁定使能信号而将所述最终速率确定为所述四分之一速率。

5.根据权利要求4所述的时钟数据恢复电路,其特征在于,所述死区校准电路还检测所述输入数据在所述第四相位范围内的第三边沿,在所述最终速率被确定为所述全速率的情况下,所述死区校准电路响应于所述校准使能信号而在检测到所述第一边沿、所述第二边沿和所述第三边沿中的至少一个边沿时,判断所述多相位时钟信号在所述死区内被锁定,在所述最终速率被确定为所述半速率的情况下,所述死区校准电路响应于所述校准使能信号而在检测到所述第一边沿和所述第三边沿中的至少一个边沿时,判断所述多相位时钟信号在所述死区内被锁定,在所述最终速率被确定为所述四分之一速率的情况下,所述死区校准电路响应于所述校准使能信号而判断所述多相位时钟信号未在所述死区内被锁定。6.根据权利要求1所述的时钟数据恢复电路,其特征在于,在所述多相位时钟信号被判断为在所述死区内被锁定的情况下,所述死区校准电路向所述锁相环电路中所包括的环路滤波器提供附加电荷泵电流,来变更所述多相位时钟信号的所述相位。7.根据权利要求1所述的时钟数据恢复电路,其特征在于,与所述多相位时钟信号的一个周期对应的所述多相位时钟信号的相位范围被划分为第一相位范围、第二相位范围、第三相位范围及第四相位范围,所述死区校准电路包括:边沿检测块,检测所述输入数据在所述第二相位范围内的第一边沿、所述输入数据在所述第三相位范围内的第二边沿以及所述输入数据在所述第四相位范围内的第三边沿;速率确定块,基于所述锁定使能信号、所述第一边沿、所述第二边沿而确定所述最终速率;死区检测块,基于所述校准使能信号、所述最终速率、所述第一边沿、所述第二边沿及所述第三边沿判断所述多相位时钟信号是否在所述死区内被锁定;以及死区电荷泵,在所述多相位时钟信号被判断为在所述死区内被锁定的情况下,向所述锁相环电路中所包括的环路滤波器提供附加电荷泵电流。8.根据权利要求7所述的时钟数据恢复电路,其特征在于,所述多相位时钟信号包括具有彼此不同的相位的第一时钟信号、第二时钟信号、第三时钟信号、第四时钟信号、第五时钟信号、第六时钟信号、第七时钟信号、第八时钟信号,所述边沿检测块包括:第一触发器,响应于所述第三时钟信号对所述输入数据进行采样;第二触发器,响应于所述第五时钟信号对所述输入数据进行采样;第三触发器,响应于所述第七时钟信号对所述输入数据进行采样;第四触发器,响应于所述第一时钟信号对所述输入数据进行采样;第一异或门,对所述第一触发器的输出信号及所述第二触发器的输出信号执行异或运算而检测所述第一边沿;第二异或门,对所述第二触发器的所述输出信号及所述第三触发器的输出信号执行异或运算而检测所述第二边沿;以及第三异或门,对所述第三触发器的所述输出信号及所述第四触发器的输出信号执行异

或运算而检测所述第三边沿。9.根据权利要求8所述的时钟数据恢复电路,其特征在于,所述边沿检测块还包括:第五触发器,位于所述第一触发器与所述第一异或门之间,并且响应于所述第四时钟信号而对所述第一触发器的所述输出信号进行采样;第六触发器,位于所述第二触发器与所述第一异或门之间,并且响应于所述第六时钟信号而对所述第二触发器的所述输出信号进行采样;第七触发器,位于所述第二触发器与所述第二异或门之间,并且响应于所述第六时钟信号而对所述第二触发器的所述输出信号进行采样;第八触发器,位于所述第三触发器与所述第二异或门之间,并且响应于所述第六时钟信号而对所述第三触发器的所述输出信号进行采样;第九触发器,位于所述第三触发器与所述第三异或门之间,并且响应于所述第八时钟信号而对所述第三触发器的所述输出信号进行采样;以及第十触发器,位于所述第四触发器与所述第三异或门之间,并且响应于所述第八时钟信号而对所述第四触发器的所述输出信号进行采样。10.根据权利要求8所述的时钟数据恢复电路,其特征在于,所述速率确定块包括:第一多路复用器,响应于所述锁定使能信号而选择性地输出所述第一异或门的输出信号或低电源电压;第二多路复用器,响应于所述锁定使能信号而选择性地输出所述第二异或门的输出信号或所述低电源电压;第十一触发器,响应于所述第一多路复用器的输出信号而对高电源电压进行采样而生成第一速率检测信号;以及第十二触发器,响应于所述第二多路复用器的输出信号而对所述高电源电压进行采样而生成第二速率检测信号。11.根据权利要求10所述的时钟数据恢复电路,其特征在于,在所述第一速率检测信号及所述第二速率检测信号全部具有低电平的情况下,所述数字块控制所述多速率相位检测器以全速率作为所述最终速率进行操作,在所述第一速率检测信号具有所述低电平且所述第二速率检测信号具有高电平的情况下,所述数字块控制所述多速率相位检测器以半速率作为所述最终速率进行操作,在所述第一速率检测信号及所述第二速率检测信号全部具有所述高电平的情况下,所述数字块控制所述多速率相位检测器以四分之一速率作为所述最终速率进行操作。12.根据权利要求8所述的时钟数据恢复电路,其特征在于,所述死区检测块包括:第三多路复用器,响应于所述校准使能信号而选择性地输出所述第一异或门的输出信号或低电源电压作为第一校准信号;第四多路复用器,响应于所述校准使能信号而选择性地输出所述第二异或门的输出信号或所述低电源电压作为第二校准信号;第五多路复用器,响应于所述校准使能信号而选择性地输出所述第三异或门的输出信

号或所述低电源电压作为第三校准信号;第一或门,对所述第一校准信号、所述第二校准信号及所述第三校准信号执行或运算而输出全速率校准信号;第二或门,对所述第一校准信号及所述第三校准信号执行或运算而输出半速率校准信号;以及第六多路复用器,响应于与所述最终速率对应的最终速率信号而选择性地输出所述全速率校准信号、所述半速率校准信号或所述低电源电压作为死区检测信号。13.根据权利要求12所述的时钟数据恢复电路,其特征在于,所述死区电荷泵在所述死区检测信号具有低电平的情况下不向所述环路滤波器提供所述附加电荷泵电流,而在所述死区检测信号具有高电平的情况下向所述环路滤波器提供所述附加电荷泵电流。14.根据权利要求7所述的时钟数据恢复电路,其特征在于,所述附加电荷泵电流为负的电流,所述锁相环电路基于由所述死区电荷泵提供的所述附加电荷泵电流而增加所述多相位时钟信号的所述相位。15.根据权利要求1所述的时钟数据恢复电路,其特征在于,所述多速率相位检测器检测所述输入数据与所述多相位时钟信号的相位差,所述锁相环电路还包括:电荷泵,响应于由所述多速率相位检测器检测的所述相位差而生成电荷泵电流;环路滤波器,对所述电荷泵电流进行滤波而生成控制电压;以及压控振荡器,基于所述控制电压生成所述多相位时钟信号。16.根据权利要求15所述的时钟数据恢复电路,其特征在于,所述多相位时钟信号包括具有彼此不同的相位的第一时钟信号、第二时钟信号、第三时钟信号、第四时钟信号、第五时钟信号、第六时钟信号、第七时钟信号、第八时钟信号,所述多速率相位检测器包括:第一触发器、第二触发器、第三触发器、第四触发器、第五触发器、第六触发器、第七触发器、第八触发器,分别响应于所述第一时钟信号至第八时钟信号而对所述输入数据进行采样;第一异或门,包括第一输入端子、第二输入端子以及输出上行信号的第一输出端子;第二异或门,包括第三输入端子、第四输入端子以及输出下行信号的第二输出端子;第一开关块,响应于从所述数字块接收的数字码而向所述第一输入端子选择性地提供所述第一触发器的输出信号、所述第三触发器的输出信号、所述第五触发器的输出信号或所述第七触发器的输出信号;第二开关块,响应于所述数字码而向所述第二输入端子及所述第三输入端子选择性地提供所述第二触发器的输出信号、所述第四触发器的输出信号、所述第六触发器的输出信号或所述第八触发器的输出信号;以及第三开关块,响应于所述数字码而向所述第四输入端子提供所述第三触发器的所述输出信号、所述第五触发器的所述输出信号、所述第七触发器的所述输出信号或所述第一触发器的所述输出信号。

17.根据权利要求16所述的时钟数据恢复电路,其特征在于,在所述最终速率被确定为全速率的情况下,所述多速率相位检测器输出所述第六触发器的所述输出信号作为恢复的数据,在所述最终速率被确定为半速率的情况下,所述多速率相位检测器输出所述第四触发器的所述输出信号及所述第八触发器的所述输出信号作为所述恢复的数据,在所述最终速率被确定为四分之一速率的情况下,所述多速率相位检测器输出所述第一触发器的所述输出信号、所述第三触发器的所述输出信号、所述第五触发器的所述输出信号及所述第七触发器的所述输出信号作为所述恢复的数据。18.一种显示装置,其特征在于,包括:显示面板,包括多个像素;数据驱动器,包括基于输入数据生成多相位时钟信号及恢复的数据的时钟数据恢复电路,并且向所述多个像素提供与所述恢复的数据对应的数据信号;以及控制器,向所述数据驱动器提供所述输入数据,其中,所述时钟数据恢复电路包括:锁相环电路,基于所述输入数据生成所述多相位时钟信号,并且包括能够以多个速率进行操作并在初始区间以作为所述多个速率中的预定的一个速率的初始速率进行操作的多速率相位检测器;锁定检测器,检测所述锁相环电路的锁定状态而生成锁定使能信号;死区校准电路,响应于所述锁定使能信号而确定所述多个速率中与所述输入数据的数据速率对应的最终速率;以及数字块,控制所述多速率相位检测器以所述最终速率进行操作,并且生成校准使能信号,其中,所述死区校准电路响应于所述校准使能信号而判断所述多相位时钟信号是否在死区内被锁定,并且在所述多相位时钟信号在所述死区内被锁定的情况下,变更所述多相位时钟信号的相位。19.一种时钟数据恢复电路的驱动方法,作为显示装置的数据驱动器中所包括的时钟数据恢复电路的驱动方法,其特征在于,包括如下步骤:使能够以多个速率进行操作的多速率相位检测器在初始区间以作为所述多个速率中的预定的一个速率的初始速率进行操作,来基于输入数据生成多相位时钟信号;检测包括所述多速率相位检测器的锁相环电路的锁定状态;确定所述多个速率中与所述输入数据的数据速率对应的最终速率;控制所述多速率相位检测器以所述最终速率进行操作;判断所述多相位时钟信号是否在死区内被锁定;以及在所述多相位时钟信号在所述死区内被锁定的情况下,变更所述多相位时钟信号的相位。20.根据权利要求19所述的时钟数据恢复电路的驱动方法,其特征在于,所述多速率相位检测器的所述多个速率包括全速率、半速率及四分之一速率,所述初始速率为所述全速率。

技术总结

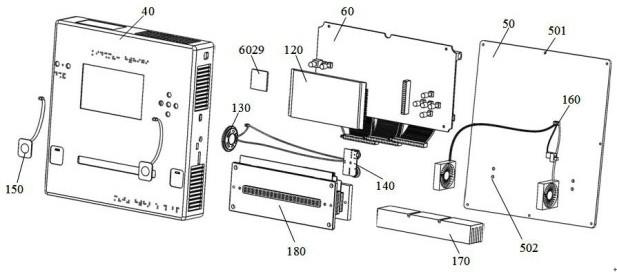

本发明涉及一种时钟数据恢复电路、显示装置及驱动方法。时钟数据恢复电路包括:锁相环电路,基于输入数据生成多相位时钟信号,并且包括能够以多个速率进行操作并在初始区间以作为多个速率中的预定的一个速率的初始速率进行操作的多速率相位检测器;锁定检测器,检测锁相环电路的锁定状态而生成锁定使能信号;死区校准电路,响应于锁定使能信号而确定多个速率中与输入数据的数据速率对应的最终速率;以及数字块,控制多速率相位检测器以最终速率进行操作,生成校准使能信号,死区校准电路响应于校准使能信号而判断多相位时钟信号是否在死区内被锁定,并且在多相位时钟信号在死区内被锁定的情况下,变更多相位时钟信号的相位。位。位。

技术研发人员:片奇铉 朴喜淑

受保护的技术使用者:三星显示有限公司

技术研发日:2021.02.25

技术公布日:2021/11/19

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。