1.本发明涉及半导体领域,特别是涉及一种静电保护电路。

背景技术:

2.随着半导体制备工艺的不断发展,人们对半导体器件的要求也在不断提高,器件的体积不断微缩,相应地半导体器件的沟道越来越短、结深越来越深、氧化层越来越薄,因此对静电防护能力的要求也在不断提高。

3.dram(dynamic random access memory,动态随机存储器)是一种具有数据快速存取功能的半导体器件,以更快的存取速度和更大的数据存储量作为主要的发展方向,但是,现有的静电保护电路无法满足dram等先进制程的低工作电压的高速接口的静电保护需求。

技术实现要素:

4.基于此,有必要针对现有的半导体器件的静电防护能力不足的问题,提供一种静电保护电路。

5.一种静电保护电路,用于保护内部电路,包括:

6.第一电路,连接于电源焊盘和输入焊盘之间,用于泄放第一静电电流,所述第一静电电流从所述输入焊盘流向所述电源焊盘;

7.第二电路,连接于所述输入焊盘和接地焊盘之间,用于泄放第二静电电流,所述第二静电电流从所述输入焊盘流向所述接地焊盘;

8.第三电路,连接于所述电源焊盘和所述输入焊盘之间,用于泄放第三静电电流,所述第三静电电流从所述电源焊盘流向所述输入焊盘;

9.第四电路,连接于所述电源焊盘和所述接地焊盘之间,用于泄放第四静电电流,所述第四静电电流从所述电源焊盘流向所述接地焊盘;

10.第五电路,连接于所述输入焊盘和所述接地焊盘之间,用于泄放第五静电电流,所述第五静电电流从所述接地焊盘流向所述输入焊盘;

11.第六电路,连接于所述接地焊盘和所述电源焊盘之间,用于泄放第六静电电流,所述第六静电电流从所述接地焊盘流向所述电源焊盘。

12.在其中一个实施例中,所述第一电路包括第一npn晶体管和第一pnp晶体管,所述第一npn晶体管的发射极与电源焊盘连接,所述第一npn晶体管的基极与所述第一pnp晶体管的集电极、所述第一npn晶体管的集电极以及所述第一pnp晶体管的基极均连接,所述第一pnp晶体管的发射极与输入焊盘连接,所述第一npn晶体管的基极与发射极之间连接有第一二极管,所述第一pnp晶体管的发射极与基极之间连接有第二二极管;

13.所述第二电路包括第二npn晶体管和第二pnp晶体管,所述第二npn晶体管的发射极与接地焊盘连接,所述第二npn晶体管的基极与所述第二pnp晶体管的集电极、所述第二npn晶体管的集电极以及所述第二pnp晶体管的基极均连接,所述第二pnp晶体管的发射极与所述输入焊盘连接,所述第二npn晶体管的基极与发射极之间连接有第三二极管,所述第

二pnp晶体管的发射极与基极之间连接有第四二极管。

14.在其中一个实施例中,所述第一npn晶体管的基极与集电极之间连接有第一电阻单元,所述第二npn晶体管的基极与集电极之间连接有第二电阻单元。

15.在其中一个实施例中,所述接地焊盘和所述电源焊盘均位于衬底上,所述衬底为p型衬底,所述衬底中设有第一n型深阱,所述第一n型深阱中设有第一p型阱、第一n型阱和第二p型阱,其中:

16.所述第一p型阱中设有第一p型重掺杂区和第一n型重掺杂区,所述第一n型重掺杂区与所述接地焊盘电连接;

17.所述第一n型阱中设有第二p型重掺杂区、第二n型重掺杂区和第三p型重掺杂区,所述第二n型重掺杂区与所述第一p型重掺杂区电连接,所述第二p型重掺杂区和所述第三p型重掺杂区均与所述输入焊盘电连接;

18.所述第二p型阱中设有第三n型重掺杂区和第四p型重掺杂区,所述第三n型重掺杂区与所述电源焊盘电连接,所述第四p型重掺杂区与所述第二n型重掺杂区电连接。

19.在其中一个实施例中,所述第三电路包括第三npn晶体管和第三pnp晶体管,所述第三npn晶体管的发射极与输入焊盘连接,所述第三npn晶体管的基极与所述第三pnp晶体管的集电极、所述第三npn晶体管的集电极以及所述第三pnp晶体管的基极均连接,所述第三pnp晶体管的发射极与电源焊盘连接,所述第三npn晶体管的基极与发射极之间连接有第五二极管,所述第三pnp晶体管的发射极与基极之间连接有第六二极管;

20.所述第四电路包括第四npn晶体管和第四pnp晶体管,所述第四npn晶体管的发射极与接地焊盘连接,所述第四npn晶体管的基极与所述第四pnp晶体管的集电极、所述第四npn晶体管的集电极以及所述第四pnp晶体管的基极均连接,所述第四pnp晶体管的发射极与所述电源焊盘连接,所述第四npn晶体管的基极与发射极之间连接有第七二极管,所述第四pnp晶体管的发射极与基极之间连接有第八二极管。

21.在其中一个实施例中,所述第三npn晶体管的基极与集电极之间连接有第三电阻单元,所述第四npn晶体管的基极与集电极之间连接有第四电阻单元。

22.在其中一个实施例中,所述接地焊盘和所述输入焊盘均位于衬底上,所述衬底为p型衬底,所述衬底中设有第二n型深阱,所述第二n型深阱中设有第三p型阱、第二n型阱和第四p型阱,其中:

23.所述第三p型阱中设有第五p型重掺杂区和第四n型重掺杂区,所述第四n型重掺杂区与所述接地焊盘电连接;

24.所述第二n型阱中设有第六p型重掺杂区、第五n型重掺杂区和第七p型重掺杂区,所述第五n型重掺杂区与所述第五p型重掺杂区电连接,所述第六p型重掺杂区和所述第七p型重掺杂区均与所述电源焊盘电连接;

25.所述第四p型阱中设有第六n型重掺杂区和第八p型重掺杂区,所述第六n型重掺杂区与所述输入焊盘电连接,所述第八p型重掺杂区与所述第五n型重掺杂区电连接。

26.在其中一个实施例中,所述第五电路包括第五npn晶体管和第五pnp晶体管,所述第五npn晶体管的发射极与输入焊盘连接,所述第五npn晶体管的基极与所述第五pnp晶体管的集电极、所述第五npn晶体管的集电极以及所述第五pnp晶体管的基极均连接,所述第五pnp晶体管的发射极与接地焊盘连接,所述第五npn晶体管的基极与发射极之间连接有第

九二极管,所述第五pnp晶体管的发射极与基极之间连接有第十二极管;

27.所述第六电路包括第六npn晶体管和第六pnp晶体管,所述第六npn晶体管的发射极与电源焊盘连接,所述第六npn晶体管的基极与所述第六pnp晶体管的集电极、所述第六npn晶体管的集电极以及所述第六pnp晶体管的基极均连接,所述第六pnp晶体管的发射极与所述接地焊盘连接,所述第六npn晶体管的基极与发射极之间连接有第十一二极管,所述第六pnp晶体管的发射极与基极之间连接有第十二二极管。

28.在其中一个实施例中,所述第五npn晶体管的基极与集电极之间连接有第五电阻单元,所述第六npn晶体管的基极与集电极之间连接有第六电阻单元。

29.在其中一个实施例中,所述电源焊盘和所述输入焊盘均位于衬底上,所述衬底为p型衬底,所述衬底中设有第三n型深阱,所述第三n型深阱中设有第五p型阱、第三n型阱和第六p型阱,其中:

30.所述第五p型阱中设有第九p型重掺杂区和第七n型重掺杂区,所述第七n型重掺杂区与所述电源焊盘电连接;

31.所述第三n型阱中设有第十p型重掺杂区、第八n型重掺杂区和第十一p型重掺杂区,所述第八n型重掺杂区与所述第九p型重掺杂区电连接,所述第十p型重掺杂区和所述第十一p型重掺杂区均与所述接地焊盘电连接;

32.所述第六p型阱中设有第九n型重掺杂区和第十二p型重掺杂区,所述第九n型重掺杂区与所述输入焊盘电连接,所述第十二p型重掺杂区与所述第八n型重掺杂区电连接。

33.上述静电保护电路,用于保护内部电路,包括:第一电路,连接于电源焊盘和输入焊盘之间,用于泄放第一静电电流,所述第一静电电流从所述输入焊盘流向所述电源焊盘;第二电路,连接于所述输入焊盘和接地焊盘之间,用于泄放第二静电电流,所述第二静电电流从所述输入焊盘流向所述接地焊盘;第三电路,连接于所述电源焊盘和所述输入焊盘之间,用于泄放第三静电电流,所述第三静电电流从所述电源焊盘流向所述输入焊盘;第四电路,连接于所述电源焊盘和所述接地焊盘之间,用于泄放第四静电电流,所述第四静电电流从所述电源焊盘流向所述接地焊盘;第五电路,连接于所述输入焊盘和所述接地焊盘之间,用于泄放第五静电电流,所述第五静电电流从所述接地焊盘流向所述输入焊盘;第六电路,连接于所述接地焊盘和所述电源焊盘之间,用于泄放第六静电电流,所述第六静电电流从所述接地焊盘流向所述电源焊盘。在本发明中,第一电路至第六电路分别用于沿设定的电流流向泄放两个焊盘之间的静电电流,并当静电现象属于不同的静电模式时,导通相应不同的静电电流的泄放电路,且在不触发内部电路的前提下,实现了对静电电流进行快速地泄放,从而既不影响内部电路的正常功能,同时又提供了较强的静电保护能力。

附图说明

34.图1为一实施例的静电保护电路的结构示意图;

35.图2为一实施例的针对ps模式和pd模式静电的保护电路的电路图;

36.图3为图2实施例的电路图对应的器件结构示意图;

37.图4为一实施例的针对nd模式静电的保护电路的电路图;

38.图5为图4实施例的电路图对应的器件结构示意图;

39.图6为一实施例的针对ns模式静电的保护电路的电路图;

40.图7为图6实施例的电路图对应的器件结构示意图;

41.图8为一实施例的全模式的静电保护电路的电路图。

42.元件标号说明:

43.第一电路:11;第二电路:12;第三电路:13;第四电路:14;第五电路:15;第六电路:16;第一n型深阱:21;第二n型深阱:22;第三n型深阱:23;第一p型阱:31;第二p型阱:32;第三p型阱:33;第四p型阱:34;第五p型阱:35;第六p型阱:36;第一n型阱:41;第二n型阱:42;第三n型阱:43;第一p型重掺杂区:301;第二p型重掺杂区:302;第三p型重掺杂区:303;第四p型重掺杂区:304;第五p型重掺杂区:305;第六p型重掺杂区:306;第七p型重掺杂区:307;第八p型重掺杂区:308;第九p型重掺杂区:309;第十p型重掺杂区:310;第十一p型重掺杂区:311;第十二p型重掺杂区:312;第一n型重掺杂区:401;第二n型重掺杂区:402;第三n型重掺杂区:403;第四n型重掺杂区:404;第五n型重掺杂区:405;第六n型重掺杂区:406;第七n型重掺杂区:407;第八n型重掺杂区:408;第九n型重掺杂区:409

具体实施方式

44.为了便于理解本技术,下面将参照相关附图对本技术进行更全面的描述。附图中给出了本技术的实施例。但是,本技术可以以许多不同的形式来实现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使本技术的公开内容更加透彻全面。

45.除非另有定义,本文所使用的所有的技术和科学术语与属于本技术的技术领域的技术人员通常理解的含义相同。本文中在本技术的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本技术。

46.空间关系术语例如“在...下”、“在...下面”、“下面的”、“在...之下”、“在...之上”、“上面的”等,在这里可以用于描述图中所示的一个元件或特征与其它元件或特征的关系。应当明白,除了图中所示的取向以外,空间关系术语还包括使用和操作中的器件的不同取向。例如,如果附图中的器件翻转,描述为“在其它元件下面”或“在其之下”或“在其下”元件或特征将取向为在其它元件或特征“上”。因此,示例性术语“在...下面”和“在...下”可包括上和下两个取向。此外,器件也可以包括另外地取向(譬如,旋转90度或其它取向),并且在此使用的空间描述语相应地被解释。

47.在此使用时,单数形式的“一”、“一个”和“/该”也可以包括复数形式,除非上下文清楚指出另外的方式。还应当理解的是,术语“包括/包含”或“具有”等指定所陈述的特征、整体、步骤、操作、组件、部分或它们的组合的存在,但是不排除存在或添加一个或更多个其他特征、整体、步骤、操作、组件、部分或它们的组合的可能性。同时,在本说明书中,术语“和/或”包括相关所列项目的任何及所有组合。

48.这里参考作为本发明的理想实施例(和中间结构)的示意图的横截面图来描述发明的实施例,这样可以预期由于例如制造技术和/或容差导致的所示形状的变化。因此,本发明的实施例不应当局限于在此所示的区的特定形状,而是包括由于例如制造技术导致的形状偏差。例如,显示为矩形的注入区在其边缘通常具有圆的或弯曲特征和/或注入浓度梯度,而不是从注入区到非注入区的二元改变。同样,通过注入形成的埋藏区可导致该埋藏区和注入进行时所经过的表面之间的区中的一些注入。因此,图中显示的区实质上是示意性的,它们的形状并不表示器件的区的实际形状,且并不限定本发明的范围。

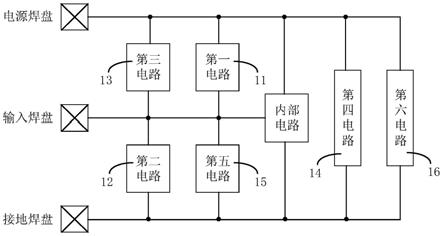

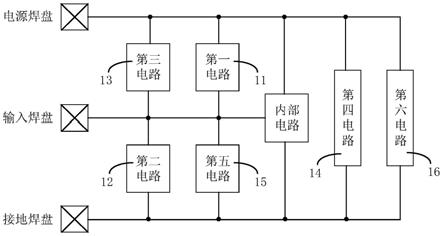

49.图1为一实施例的静电保护电路的结构示意图,静电保护电路用于保护内部电路,如图1所示,在本实施例中,静电保护电路包括第一电路11、第二电路12、第三电路13、第四电路14、第五电路15和第六电路16。

50.第一电路11,连接于电源焊盘和输入焊盘之间,用于泄放第一静电电流,第一静电电流从输入焊盘流向电源焊盘;

51.第二电路12,连接于输入焊盘和接地焊盘之间,用于泄放第二静电电流,第二静电电流从输入焊盘流向接地焊盘;

52.第三电路13,连接于电源焊盘和输入焊盘之间,用于泄放第三静电电流,第三静电电流从电源焊盘流向输入焊盘;

53.第四电路14,连接于电源焊盘和接地焊盘之间,用于泄放第四静电电流,第四静电电流从电源焊盘流向接地焊盘;

54.第五电路15,连接于输入焊盘和接地焊盘之间,用于泄放第五静电电流,第五静电电流从接地焊盘流向输入焊盘;

55.第六电路16,连接于接地焊盘和电源焊盘之间,用于泄放第六静电电流,第六静电电流从接地焊盘流向电源焊盘。

56.在本实施例中,第一电路11至第六电路16分别用于沿设定的电流流向在两个焊盘之间泄放静电电流,并当静电现象属于不同的静电模式时,导通相应不同的静电电流的泄放电路。进一步地,本实施例中设置的第一电路11、第二电路12、第三电路13、第四电路14、第五电路15和第六电路16的触发电压均低于内部电路的触发电压,因此,本实施例的静电保护电路可以在不触发内部电路的前提下,对静电电流进行快速地泄放,从而既不影响内部电路的正常功能,同时又提供了较强的静电保护能力。

57.图2为一实施例的针对ps模式和pd模式静电的保护电路的电路图,如图2所示,在本实施例中,第一电路11和第二电路12用于针对ps模式的静电和pd模式的静电,以对内部电路进行保护,其中,ps模式是指静电电压正向于接地电压的静电放电模式,pd模式是指静电电压正向于电源电压的静电放电模式。

58.第一电路11包括第一npn晶体管q1和第一pnp晶体管q2,第一npn晶体管q1的发射极与电源焊盘连接,第一npn晶体管q1的基极与第一pnp晶体管q2的集电极、第一npn晶体管q1的集电极以及第一pnp晶体管q2的基极均连接,第一pnp晶体管q2的发射极与输入焊盘连接,第一npn晶体管q1的基极与发射极之间连接有第一二极管d1,第一pnp晶体管q2的发射极与基极之间连接有第二二极管d2。其中,第一二极管d1和第二二极管d2共同构成二极管电流路径,第一npn晶体管q1和第一pnp晶体管q2共同构成scr(silicon controlled rectifier,可控硅整流器)电流路径。

59.第二电路12包括第二npn晶体管q3和第二pnp晶体管q4,第二npn晶体管q3的发射极与接地焊盘连接,第二npn晶体管q3的基极与第二pnp晶体管q4的集电极、第二npn晶体管q3的集电极以及第二pnp晶体管q4的基极均连接,第二pnp晶体管q4的发射极与输入焊盘连接,第二npn晶体管q3的基极与发射极之间连接有第三二极管d3,第二pnp晶体管q4的发射极与基极之间连接有第四二极管d4。其中,其中,第三二极管d3和第四二极管d4共同构成二极管电流路径,第二npn晶体管q3和第二pnp晶体管q4共同构成scr电流路径。

60.具体地,当未发生esd(electro-static discharge,静电放电)时,电源焊盘输入

电源电压,接地焊盘连接至地,内部电路正常工作。可以理解的是,由于二极管结构和scr结构的电路特性,二极管电流路径的导通电压小于scr电流路径的导通电压,因此,当发生ps模式和pd模式的esd时,静电电压正向于电源电压或正向于接地电压,本实施例的电路结构会使第一电路11和第二电路12中的二极管电流路径先导通,并通过引流作用再触发相应的scr电流路径导通,而且由于scr电流路径内部的正反馈效应,可以使第一npn晶体管q1、第一pnp晶体管q2、第二npn晶体管q3和第二pnp晶体管q4快速饱和导通,从而实现了比单独的scr结构更低的触发电压和更快的启动速度。

61.进一步地,本实施例的第一电路11和第二电路12的寄生电容较小,因此不会影响内部电路的运行状态,而且本实施例的第一电路11和第二电路12的维持电压可以大于操作电压,从而避免了闩锁效应,即防止了电路功能的混乱或者电路直接无法工作的问题,提高了静电保护电路的可靠性和稳定性。

62.在本实施例中,第一电路11和第二电路12共同用于针对ps模式的静电和pd模式的静电,以对内部电路进行保护,通过第一电路11内部设置的二极管电流路径和scr电流路径,利用二极管电流路径的低触发电压的特性,通过二极管电流路径的引流作用进一步导通scr电流路径,从而提供了一种低触发电压、快启动速度的ps模式和pd模式静电的保护电路。

63.继续参考图2,第一npn晶体管q1的基极与集电极之间连接有第一电阻单元,第二npn晶体管q3的基极与集电极之间连接有第二电阻单元。具体地,第一电阻单元可以包括电阻r1和电阻r2,第二电阻单元可以包括电阻r3和电阻r4,本实施例通过设置第一电阻单元和第二电阻单元可以加快第一npn晶体管q1和第二npn晶体管q3进入饱和状态的速度,从而提高第一电路11的电流泄放速度,同样地,第二电阻单元可以提高第二电路12的电流泄放速度。因此,本实施例的第一电路11和第二电路12进一步提高了对内部电路的esd保护速度。

64.图3为图2实施例的电路图对应的器件结构示意图,在本实施中,电源焊盘、接地焊盘和输入焊盘均位于衬底上(为了更清楚地说明各焊盘与各掺杂区之间的电流流向,图3中未将电源焊盘、接地焊盘和输入焊盘绘制在衬底上),衬底为p型衬底。

65.如图3所示,衬底中设有第一n型深阱21,第一n型深阱21中设有第一p型阱31、第一n型阱41和第二p型阱32,其中:第一p型阱31中设有第一p型重掺杂区301和第一n型重掺杂区401,第一n型重掺杂区401与接地焊盘电连接;第一n型阱41中设有第二p型重掺杂区302、第二n型重掺杂区402和第三p型重掺杂区303,第二n型重掺杂区402与第一p型重掺杂区301电连接,第二p型重掺杂区302和第三p型重掺杂区303均与输入焊盘电连接;第二p型阱32中设有第三n型重掺杂区403和第四p型重掺杂区304,第三n型重掺杂区403与电源焊盘电连接,第四p型重掺杂区304与第二n型重掺杂区402电连接。

66.具体地,第一n型阱41、第二p型阱32和第三n型重掺杂区403共同构成第一npn晶体管q1,第三p型重掺杂区303、第一n型阱41和第二p型阱32共同构成第一pnp晶体管q2,第四p型重掺杂区304和第三n型重掺杂区403共同构成第一二极管d1,第三p型重掺杂区303和第二n型重掺杂区402共同构成第二二极管d2,第一n型阱41和第二p型阱32之间形成第一电阻单元中的电阻r1和电阻r2。第一n型阱41、第一p型阱31和第二n型重掺杂区402共同构成第二npn晶体管q3,第二p型重掺杂区302、第一n型阱41和第一p型阱31共同构成第二pnp晶体

管q4,第一p型重掺杂区301和第一n型重掺杂区401共同构成第三二极管d3,第二p型重掺杂区302和第二n型重掺杂区402共同构成第四二极管d4,第一n型阱41和第一p型阱31之间形成第二电阻单元中的电阻r3和电阻r4。

67.进一步地,图3中的黑色小箭头所示即为二极管电流路径的电流流向,白色大箭头所示即为scr电流路径的电流流向。当施加ps模式或pd模式的静电时,在输入焊盘与电源焊盘之间,二极管电流路径先导通,即电流从输入焊盘沿着第三p型重掺杂区303、第二n型重掺杂区402、第四p型重掺杂区304和第三n型重掺杂区403流向电源焊盘,从而再进一步触发scr电流路径的导通,即经过第一pnp晶体管q2和第一npn晶体管q1对静电电流进行泄放。同样地,在输入焊盘与接地焊盘之间,二极管电流路径先导通,即电流从输入焊盘沿着第二p型重掺杂区302、第二n型重掺杂区402、第一p型重掺杂区301和第一n型重掺杂区401流向电源焊盘,从而再进一步触发scr电流路径的导通,即经过第二pnp晶体管q4和第二npn晶体管q3对静电电流进行泄放。因此,本实施例的静电保护电路可以避免静电电流流经内部电路,从而实现了对内部电路的静电保护。

68.图4为一实施例的针对nd模式静电的保护电路的电路图,如图4所示,在本实施例中,第三电路13和第四电路14用于针对nd模式的静电,以对内部电路进行保护,其中,nd模式是指静电电压负向于电源电压的静电放电模式。

69.第三电路13包括第三npn晶体管q5和第三pnp晶体管q6,第三npn晶体管q5的发射极与输入焊盘连接,第三npn晶体管q5的基极与第三pnp晶体管q6的集电极、第三npn晶体管q5的集电极以及第三pnp晶体管q6的基极均连接,第三pnp晶体管q6的发射极与电源焊盘连接,第三npn晶体管q5的基极与发射极之间连接有第五二极管d5,第三pnp晶体管q6的发射极与基极之间连接有第六二极管d6。其中,第五二极管d5和第六二极管d6共同构成二极管电流路径,第三npn晶体管q5和第三pnp晶体管q6共同构成scr电流路径。

70.第四电路14包括第四npn晶体管q7和第四pnp晶体管q8,第四npn晶体管q7的发射极与接地焊盘连接,第四npn晶体管q7的基极与第四pnp晶体管q8的集电极、第四npn晶体管q7的集电极以及第四pnp晶体管q8的基极均连接,第四pnp晶体管q8的发射极与电源焊盘连接,第四npn晶体管q7的基极与发射极之间连接有第七二极管d7,第四pnp晶体管q8的发射极与基极之间连接有第八二极管d8。其中,其中,第七二极管d7和第八二极管d8共同构成二极管电流路径,第四npn晶体管q7和第四pnp晶体管q8共同构成scr电流路径。

71.具体地,当未发生esd时,输入焊盘输入电源电压,接地焊盘连接至地,内部电路正常工作。可以理解的是,由于二极管结构和scr结构的电路特性,二极管电流路径的导通电压小于scr电流路径的导通电压,因此,当发生nd模式的esd时,静电电压负向于电源电压,本实施例的电路结构会使第三电路13和第四电路14中的二极管电流路径先导通,并通过引流作用再触发相应的scr电流路径导通,而且由于scr电流路径内部的正反馈效应,可以使第三npn晶体管q5、第三pnp晶体管q6、第四npn晶体管q7和第四pnp晶体管q8快速饱和导通,从而实现了比单独的scr结构更低的触发电压和更快的启动速度。

72.进一步地,本实施例的第三电路13和第四电路14的寄生电容较小,因此不会影响内部电路的运行状态,而且本实施例的第三电路13和第四电路14的维持电压可以大于操作电压,从而避免了闩锁效应,即防止了电路功能的混乱或者电路直接无法工作的问题,提高了静电保护电路的可靠性和稳定性。

73.在本实施例中,第三电路13和第四电路14共同用于针对nd模式的静电,以对内部电路进行保护,通过第三电路13内部设置的二极管电流路径和scr电流路径,利用二极管电流路径的低触发电压的特性,通过二极管电流路径的引流作用进一步导通scr电流路径,从而提供了一种低触发电压、快启动速度的nd模式静电的保护电路。

74.继续参考图4,第三npn晶体管q5的基极与集电极之间连接有第三电阻单元,第四npn晶体管q7的基极与集电极之间连接有第四电阻单元。具体地,第三电阻单元可以包括电阻r5和电阻r6,第四电阻单元可以包括电阻r7和电阻r8,本实施例通过设置第三电阻单元和第四电阻单元可以加快第三npn晶体管q5和第四npn晶体管q7进入饱和状态的速度,从而提高第三电路13的电流泄放速度,同样地,第四电阻单元可以提高第四电路14的电流泄放速度。因此,本实施例的第三电路13和第四电路14进一步提高了对内部电路的esd保护速度。

75.图5为图4实施例的电路图对应的器件结构示意图,在本实施中,电源焊盘、接地焊盘和输入焊盘均位于衬底上(为了更清楚地说明各焊盘与各掺杂区之间的电流流向,图5中未将电源焊盘、接地焊盘和输入焊盘绘制在衬底上),衬底为p型衬底。如图5所示,衬底中设有第二n型深阱22,第二n型深阱22中设有第三p型阱33、第二n型阱42和第四p型阱34,其中:第三p型阱33中设有第五p型重掺杂区305和第四n型重掺杂区404,第四n型重掺杂区404与接地焊盘电连接;第二n型阱42中设有第六p型重掺杂区306、第五n型重掺杂区405和第七p型重掺杂区307,第五n型重掺杂区405与第五p型重掺杂区305电连接,第六p型重掺杂区306和第七p型重掺杂区307均与电源焊盘电连接;第四p型阱34中设有第六n型重掺杂区406和第八p型重掺杂区308,第六n型重掺杂区406与输入焊盘电连接,第八p型重掺杂区308与第五n型重掺杂区405电连接。

76.具体地,第二n型阱42、第四p型阱34和第六n型重掺杂区406共同构成第三npn晶体管q5,第七p型重掺杂区307、第二n型阱42和第四p型阱34共同构成第三pnp晶体管q6,第八p型重掺杂区308和第六n型重掺杂区406共同构成第五二极管d5,第七p型重掺杂区307和第五n型重掺杂区405共同构成第六二极管d6,第二n型阱42和第四p型阱34之间形成第三电阻单元中的电阻r5和电阻r6。第二n型阱42、第三p型阱33和第四n型重掺杂区404共同构成第四npn晶体管q7,第六p型重掺杂区306、第二n型阱42和第三p型阱33共同构成第四pnp晶体管q8,第五p型重掺杂区305和第四n型重掺杂区404共同构成第七二极管d7,第六p型重掺杂区306和第五n型重掺杂区405共同构成第八二极管d8,第二n型阱42和第三p型阱33之间形成第四电阻单元中的电阻r7和电阻r8。

77.进一步地,图5中的黑色小箭头所示即为二极管电流路径的电流流向,白色大箭头所示即为scr电流路径的电流流向。当施加nd模式的静电时,在电源焊盘与输入焊盘之间,二极管电流路径先导通,即电流从电源焊盘沿着第七p型重掺杂区307、第五n型重掺杂区405、第八p型重掺杂区308和第六n型重掺杂区406流向输入焊盘,从而再进一步触发scr电流路径的导通,即经过第三pnp晶体管q6和第三npn晶体管q5对静电电流进行泄放。同样地,在电源焊盘与接地焊盘之间,二极管电流路径先导通,即电流从电源焊盘沿着第六p型重掺杂区306、第五n型重掺杂区405、第五p型重掺杂区305和第四n型重掺杂区404流向输入焊盘,从而再进一步触发scr电流路径的导通,即经过第八pnp晶体管和第七npn晶体管对静电电流进行泄放。因此,本实施例的静电保护电路可以避免静电电流流经内部电路,从而实现

了对内部电路的静电保护。

78.图6为一实施例的针对ns模式静电的保护电路的电路图,如图6所示,在本实施例中,第五电路15和第六电路16用于针对ns模式的静电,以对内部电路进行保护,其中,ns模式是指静电电压负向于电源电压的静电放电模式。

79.第五电路15包括第五npn晶体管q9和第五pnp晶体管q10,第五npn晶体管q9的发射极与输入焊盘连接,第五npn晶体管q9的基极与第五pnp晶体管q10的集电极、第五npn晶体管q9的集电极以及第五pnp晶体管q10的基极均连接,第五pnp晶体管q10的发射极与接地焊盘连接,第五npn晶体管q9的基极与发射极之间连接有第九二极管d9,第五pnp晶体管q10的发射极与基极之间连接有第十二极管d10。其中,第九二极管d9和第十二极管d10共同构成二极管电流路径,第五npn晶体管q9和第五pnp晶体管q10共同构成scr电流路径。

80.第六电路16包括第六npn晶体管q11和第六pnp晶体管q12,第六npn晶体管q11的发射极与电源焊盘连接,第六npn晶体管q11的基极与第六pnp晶体管q12的集电极、第六npn晶体管q11的集电极以及第六pnp晶体管q12的基极均连接,第六pnp晶体管q12的发射极与接地焊盘连接,第六npn晶体管q11的基极与发射极之间连接有第十一二极管d11,第六pnp晶体管q12的发射极与基极之间连接有第十二二极管d12。其中,其中,第十一二极管d11和第十二二极管d12共同构成二极管电流路径,第六npn晶体管q11和第六pnp晶体管q12共同构成scr电流路径。

81.具体地,当未发生esd时,输入焊盘输入电源电压,电源焊盘连接至地,内部电路正常工作。可以理解的是,由于二极管结构和scr结构的电路特性,二极管电流路径的导通电压小于scr电流路径的导通电压,因此,当发生ns模式的esd时,静电电压负向于接地电压,本实施例的电路结构会使第五电路15和第六电路16中的二极管电流路径先导通,并通过引流作用再触发相应的scr电流路径导通,而且由于scr电流路径内部的正反馈效应,可以使第五npn晶体管q9、第五pnp晶体管q10、第六npn晶体管q11和第六pnp晶体管q12快速饱和导通,从而实现了比单独的scr结构更低的触发电压和更快的启动速度。

82.进一步地,本实施例的第五电路15和第六电路16的寄生电容较小,因此不会影响内部电路的运行状态,而且本实施例的第五电路15和第六电路16的维持电压可以大于操作电压,从而避免了闩锁效应,即防止了电路功能的混乱或者电路直接无法工作的问题,提高了静电保护电路的可靠性和稳定性。

83.在本实施例中,第五电路15和第六电路16共同用于针对ns模式的静电,以对内部电路进行保护,通过第五电路15内部设置的二极管电流路径和scr电流路径,利用二极管电流路径的低触发电压的特性,通过二极管电流路径的引流作用进一步导通scr电流路径,从而提供了一种低触发电压、快启动速度的ns模式静电的保护电路。

84.继续参考图6,第五npn晶体管q9的基极与集电极之间连接有第五电阻单元,第六npn晶体管q11的基极与集电极之间连接有第六电阻单元。具体地,第五电阻单元可以包括电阻r9和电阻r10,第六电阻单元可以包括电阻r11和电阻r12,本实施例通过设置第五电阻单元和第六电阻单元可以加快第五npn晶体管q9和第六npn晶体管q11进入饱和状态的速度,从而提高第五电路15的电流泄放速度,同样地,第六电阻单元可以提高第六电路16的电流泄放速度。因此,本实施例的第五电路15和第六电路16进一步提高了对内部电路的esd保护速度。

85.图7为图6实施例的电路图对应的器件结构示意图,在本实施中,电源焊盘、接地焊盘和输入焊盘均位于衬底上(为了更清楚地说明各焊盘与各掺杂区之间的电流流向,图7中未将电源焊盘、接地焊盘和输入焊盘绘制在衬底上),衬底为p型衬底。如图7所示,衬底中设有第三n型深阱23,第三n型深阱23中设有第五p型阱35、第三n型阱43和第六p型阱36,其中:第五p型阱35中设有第九p型重掺杂区309和第七n型重掺杂区407,第七n型重掺杂区407与电源焊盘电连接;第三n型阱43中设有第十p型重掺杂区310、第八n型重掺杂区408和第十一p型重掺杂区311,第八n型重掺杂区408与第九p型重掺杂区309电连接,第十p型重掺杂区310和第十一p型重掺杂区311均与接地焊盘电连接;第六p型阱36中设有第九n型重掺杂区409和第十二p型重掺杂区312,第九n型重掺杂区409与输入焊盘电连接,第十二p型重掺杂区312与第八n型重掺杂区408电连接。

86.具体地,第三n型阱43、第六p型阱36和第九n型重掺杂区409共同构成第五npn晶体管q9,第十一p型重掺杂区311、第三n型阱43和第六p型阱36共同构成第五pnp晶体管q10,第十二p型重掺杂区312和第九n型重掺杂区409共同构成第九二极管d9,第十一p型重掺杂区311和第八n型重掺杂区408共同构成第十二极管d10,第三n型阱43和第六p型阱36之间形成第五电阻单元中的电阻r9和电阻r10。第三n型阱43、第五p型阱35和第七n型重掺杂区407共同构成第六npn晶体管q11,第十p型重掺杂区310、第三n型阱43和第五p型阱35共同构成第六pnp晶体管q12,第九p型重掺杂区309和第七n型重掺杂区407共同构成第十一二极管d11,第十p型重掺杂区310和第八n型重掺杂区408共同构成第十二二极管d12,第三n型阱43和第五p型阱35之间形成第六电阻单元中的电阻r11和电阻r12。

87.进一步地,图7中的黑色小箭头所示即为二极管电流路径的电流流向,白色大箭头所示即为scr电流路径的电流流向。当施加ns模式的静电时,在接地焊盘与输入焊盘之间,二极管电流路径先导通,即电流从接地焊盘沿着第十一p型重掺杂区311、第八n型重掺杂区408、第十二p型重掺杂区312和第九n型重掺杂区409流向输入焊盘,从而再进一步触发scr电流路径的导通,即经过第五pnp晶体管q10和第五npn晶体管q9对静电电流进行泄放。同样地,在接地焊盘与电源焊盘之间,二极管电流路径先导通,即电流从接地焊盘沿着第十p型重掺杂区310、第八n型重掺杂区408、第九p型重掺杂区309和第七n型重掺杂区407流向输入焊盘,从而再进一步触发scr电流路径的导通,即经过第六pnp晶体管q12和第六npn晶体管q11对静电电流进行泄放。因此,本实施例的静电保护电路可以避免静电电流流经内部电路,从而实现了对内部电路的静电保护。

88.图8为一实施例的全模式的静电保护电路的电路图,如图8所示,在本实施例中,静电保护电路包括第一电路11、第二电路12、第三电路13、第四电路14、第五电路15和第六电路16,且每个电路都包括前述的二极管电流路径和scr电流路径,第一电路11和第二电路12共同提供针对ps模式和pd模式静电的保护,第三电路13和第四电路14共同提供针对nd模式静电的保护,第五电路15和第六电路16共同提供针对ns模式静电的保护,从而实现了一种低触发电压、快启动速度的全模式、全芯片的静电保护电路。

89.进一步地,前述的ps模式、pd模式、ns模式和nd模式均属于hbm模式(human-body model,人体放电模式)的子模式,即带电人体对器件放电的静电放电模式。除hbm模式以外,本实施的静电保护电路还可用于防护cdm模式(charged device model,帯电设备模式)的静电,cdm模式即带电器件直接对地放电的静电放电模式,本实施例的静电保护电路通过对

cdm模式静电的进行防护,进一步提升了半导体器件的静电防护能力和可靠性。

90.在本说明书的描述中,参考术语“有些实施例”、“其他实施例”、“理想实施例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特征包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性描述不一定指的是相同的实施例或示例。

91.上实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

92.以上实施例仅表达了本技术的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对申请专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本技术构思的前提下,还可以做出若干变形和改进,这些都属于本技术的保护范围。因此,本技术专利的保护范围应以所附权利要求为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。