纹理化的硅半导体处理室组件

相关申请

1.本技术要求于2019年2月6日申请的美国临时申请no.62/801,804、于2019年4月18日申请的美国临时申请no.62/835,907以及于2019年8月13日申请的美国临时申请no.62/866,100的优先权,所有这些申请都通过引用合并于此以用于所有目的。

技术领域

2.本公开涉及用于对半导体晶片进行等离子体处理的等离子体处理室。更具体而言,本公开涉及使用各向异性蚀刻以将半导体处理室内的硅部件进行纹理化的方法。

背景技术:

3.等离子体处理是被用来形成半导体装置。在等离子体处理期间,等离子体处理室的组件可能会被等离子体腐蚀。一些等离子体处理室具有全部硅组件。晶片(其具有高深宽比的特征)的半导体处理需要沉积厚的钝化层。这种处理因此是大量的聚合物沉积与蚀刻处理。于是,由于聚合物的粘附性是随着聚合物厚度的增加而变差,因此聚合物虽然沉积在处理室的组件上,但聚合物无法很好地粘附至室的组件上。这种不良的粘附性会导致聚合物剥落而引起电弧作用及污染。

4.目前已知聚合物的粘附性会因该聚合物试图粘附的表面的粗糙度而有所改善。然而,由于硅是十分易碎的材料,因此无法使用机械方法来使硅组件粗糙化。使用机械方法来使硅粗糙化会导致硅的表面下损伤,从而可能会导致处理室内的剥落与微粒问题。通常,会接着进行酸蚀刻以去除这种表面下的损伤。然而,这种酸蚀刻实际上会洗去或移除或抹平由机械方法所产生的任何粗糙度。因此,期望能使用非机械方法来使硅的表面纹理化,以改善聚合物的粘附性。

技术实现要素:

5.根据一实施方案,提供了半导体处理室的组件。该组件是由包含硅的材料所形成,且该组件具有包括多个丘形结构的纹理化外表面。

6.根据另一实施方案,提供适用于半导体处理室内的组件。该组件包括多结晶硅(multi

‑

crystalline silicon)本体,该多结晶硅本体包括具有表面积的纹理化表面。该纹理化表面包括具有凸部或凹部的区域。

7.根据另一实施方案,提供了用于将半导体处理室的硅组件进行纹理化的方法。提供具有外表面的硅组件。将该外表面纹理化以在外表面上产生丘形结构。

8.根据又一实施方案,提供了一种用于制造在半导体处理室内所使用的多结晶硅组件的方法。提供了具有表面的多结晶硅本体。将该多结晶硅本体的表面纹理化以形成具有表面积的纹理化表面。该纹理化表面包括具有凸部或凹部的区域,且该凸部或凹部具有至少500nm的高度。

附图说明

9.在附图中,本公开是以示例的方式而并非以限制的方式进行说明,其中相同的附图标记指的是相似的组件,且其中:

10.图1是根据一实施方案的等离子体处理室的示意图。

11.图2a显示了位于半导体处理室的硅组件上的丘形锥体结构。

12.图2b是半导体处理室的硅组件上的反向丘形锥体结构的侧视横剖面图。

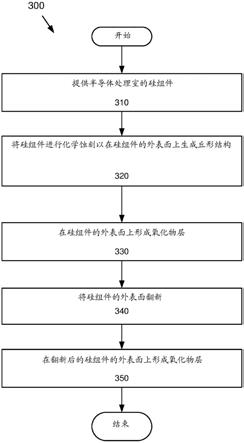

13.图3是用于将半导体处理室的含硅组件进行纹理化的方法的一实施方案的高阶流程图。

14.图4是根据另一实施方案的用于将半导体处理室的含硅组件进行纹理化的方法的高阶流程图。

15.图5是用于将半导体处理室的含硅组件进行纹理化的方法的另一实施方案的高阶流程图。

16.图6是根据又一实施方案的用于将半导体处理室的含硅组件进行纹理化的方法的高阶流程图。

17.图7是根据一实施方案的多结晶硅本体的纹理化表面的放大图像。

18.图8是用于将多结晶硅本体的表面进行纹理化的方法的一实施方案的高阶流程图。

具体实施方式

19.现在将参考附图中所示的几个优选实施方案来详细描述本公开。在下面的描述中,阐述了许多具体细节以便提供对本公开的彻底理解。然而,对于本领域技术人员显而易见的是,本公开可以在没有这些具体细节中的一些或全部的情况下实施。在其他情况下,未详细描述公知的工艺步骤和/或结构,以免不必要地使本公开不清楚。

20.图1为可用于处理半导体晶片的等离子体处理反应器100的实施方案的示意图。在一或多个实施方案中,等离子体处理室100包括由室壁152包围而位于蚀刻室149中的气体分配板106(其提供气体入口)以及静电卡盘(esc)108。在蚀刻室149中,晶片103定位于esc 108上方。esc 108是晶片支撑件。边缘环109围绕esc 108,esc源148可提供偏置到esc 108。气体源110通过气体分配板106而连接到蚀刻室149。在本实施方案中,气体源包括含氧组分源114、含氟组分源116、以及一或多个其他气体源118。esc温度控制器150连接至esc 108。

21.射频(rf)源130提供rf功率至下电极和/或上电极,在本实施方案中,下电极和上电极是esc 108和气体分配板106。在示例性实施方案中,由400千赫(khz)、60兆赫(mhz)、2mhz、13.56mhz和/或27mhz的电源组成rf源130和esc源148。在本实施方案中,上电极接地。在本实施方案中,为每个频率提供一个产生器。在其他实施方案中,产生器可以是单独的rf源,或者单独的rf产生器可以连接到不同的电极。例如,上电极可以具有连接到不同rf源的内电极与外电极。在其他实施方案中可以使用rf源和电极的其他配置。在其他实施方案中,电极可以是感应线圈。

22.控制器135以可控方式连接到rf源130、esc源148、排放泵120以及气体源110。高流量衬垫104是位于蚀刻室149中的衬垫,其限制来自气体源的气体并且具有狭缝102,所述狭缝102允许气体从气体源110至排放泵120的受控流动。

23.如上所述,高深宽比的半导体工艺可能涉及大量的聚合物沉积与蚀刻处理。一些等离子体处理室具有全部硅组件,且这种硅的室组件通常被制造成具有磨平的/研磨的/抛光的表面光洁度,其中进行最终的混合酸蚀刻(mae)处理以将损坏的深度去除。然而,这些使表面平滑的蚀刻实际上是适得其反的,原因在于这些表面光洁度不具有足够高频的粗糙度特性,因此在聚合物大量的沉积处理中会存在关于聚合物在室表面上的不良粘附性的问题,从而导致聚合物剥落以及微粒的产生。如上所述,这种聚合物剥落还导致非期望的电弧现象与污染。使用物理方法对单晶硅表面进行纹理化是具有挑战性的,原因在于由这些物理方法所造成的损伤深度可能需要通过mae处理来去除,而如此将会把粘附性所需的纹理给清洗掉。

24.聚合物在硅室表面上的粘附性随着表面粗糙度的增加而改善,原因在于粘附的表面积增加导致脱层变得更加困难。然而,如上所述,由于硅十分易碎的性质,因此不能将硅机械地粗糙化、或纹理化。因此,使硅表面纹理化的化学方法是更加实用的。

25.根据半导体处理室100的实施方案,气体分配板106(喷头)是由单晶硅(1

‑0‑

0晶体定向)所形成,并且可以使用本文所述的方法进行纹理化以使得在表面上具有丘形结构200(如图2a所显示)。类似地,其他室组件(例如高流量套筒104和边缘环109)也由包含硅的材料形成,且可使用本文所述的方法进行纹理化。在其他实施方案中,由具有1

‑0‑

0晶体定向的硅材料所形成的室组件是使用本文所述的方法进行纹理化。应当理解,理论上具有其他晶体定向(除1

‑1‑

1之外)的硅可使用本文所述的方法进行纹理化。

26.根据一实施方案,单晶硅的各向异性蚀刻可用于产生均匀的锥形、或丘形结构,使半导体处理室100内的组件的硅表面纹理化以增加表面积。这些结构通常是四面结构。由于通过调整纹理化所使用的化学品及其他处理条件可对小丘或锥体的形状、小丘或锥体的高度(峰部到谷部)、以及小丘或锥体的反射率进行选择,因此该纹理化是可调整的。所得到的纹理关联于且取决于化学蚀刻所使用的特定化学品及处理条件、以及暴露于该化学品的时间。

27.应当理解,表面的反射率是以入射光从表面反射的百分比来进行测量的,且通常包括镜面反射率及漫反射率两者的测量。通常是使用耦合至积分球的分光亮度计来进行测量。根据本文所述的实施方案,对于介于400至800nm之间的光,小丘或锥体的平均反射率通常是在约5至30%的范围内。

28.根据一些实施方案,本文所述的纹理化处理是在约50℃至100℃的温度范围内进行。在特定实施方案中,硅的室部件是在约80℃的温度下进行纹理化,该温度接近ipa的沸点。应当注意,在一些实施方案中,于纹理化处理期间需要补充ipa。根据基于ipa的特定化学品,纹理化处理是在约50℃至100℃的温度范围内,利用koh(1至10wt%)及ipa(1至19wt%)进行1至60分钟。替代性地,非基于ipa的化学品也可用于对硅的室部件进行纹理化,其将于以下更详细提及。上方所给出的参数是基于等离子体半导体处理室的硅组件的纹理化处理,所述处理室例如是由lam research corporation(fremont,california)所制造的系列产品。

29.纹理化可用于对室100内的硅部件(例如,边缘环109、气体分配板106、与高流量套筒104)进行选择性图案化或优先性蚀刻。这种选择性图案化或优先性蚀刻可通过使用掩模来实现。举例来说,可对不同区域进行图案化及遮蔽以产生具有不同高度、或不同密度、或

不同表面粗糙度的小丘。在一些实施方案中,纹理化的表面可作为掩模使用以产生进一步的纹理化。

30.在半导体处理室100的一特定实施方案中,上电极(喷头)106是由单晶硅所形成的并且进行选择性纹理化,以在其中心部分具有增加的表面粗糙度,从而局部地改善粘附性。在一些情况下,由于该处理及后续聚合物沉积与蚀刻中的非均匀性,这可能会提供粘附的选择性。在其他实施方案中,硅组件是边缘环或高流量套筒,且所述组件可能会或可能不会进行选择性纹理化。

31.从小丘峰部至谷部的平均高度可介于约500纳米至20微米的范围内。在一些实施方案中,小丘的高度可比小丘的平均高度低于或高于多达20%。根据一些实施方案,丘形或锥形结构的高度实质上与聚合物的厚度类似,以改善沉积后聚合物的粘附性。除了单晶硅之外,多晶硅(polysilicon)、多结晶硅(multi

‑

crystalline silicon)、掺杂硅、以及硅氧化物(sio2)也可以使用本文所述的方法进行纹理化。

32.基于氢氧化钾(koh)及氢氧化钠(naoh)的化学品可用于对硅的室部件进行纹理化,优选是在高温下进行,以形成锥形或丘形结构。锥形或丘形结构导致硅表面的高频粗糙度增加,这有助于改善聚合物的粘附性,从而减少或消除剥落的现象。所得到的纹理化的硅组件外表面可具有介于约0.2至2微米范围内的表面粗糙度。根据一些实施方案,在按照本文所述实施方案进行的纹理化之后,室部件的表面积增加多达1000%。

33.应注意的是,单独使用koh进行硅的蚀刻会造成各向同性蚀刻,并且不会形成所期望的具有丘形结构的纹理。在koh中,存在的添加剂(例如有机醇、或表面活性剂)可用于在硅表面上生成实质均匀的锥体或小丘。根据特定实施方案,该添加剂为异丙醇(ipa)。因此,根据一些实施方案,koh加ipa的溶液可用于生成锥形或丘形结构。然而,ipa可以是挥发性材料。因此,在其他实施方案中,可替代地使用其他添加剂(包括去离子水、表面活性剂、以及其他不含ipa的添加剂)来生成纹理化的表面。

34.参考图3,描述了用于将半导体处理室的硅组件进行纹理化的方法300的实施方案。方法300开始于步骤310:提供半导体处理室的硅组件。该硅组件具有外表面。根据一些实施方案,该硅组件是由单晶硅形成的。在其他实施方案中,该硅组件是多晶硅或掺杂硅。在步骤320中,将硅组件进行化学蚀刻以在硅组件的外表面上生成丘形结构。根据一实施方案,硅组件是使用基于koh的化学品而进行化学蚀刻,以对硅表面进行各向异性蚀刻。在另一实施方案中,硅组件是使用基于naoh的化学品而进行化学蚀刻,以对硅表面进行各向异性蚀刻。

35.如果需要,在步骤330中可在硅组件的外表面上形成氧化物层,以实现更佳的聚合物粘附性。氧化物层的厚度优选为介于约10nm至100微米的范围内。根据一实施方案,可将外层进行原位热氧化以形成氧化物层。根据另一实施方案,是在表面上形成硅氧化物(sio2)层以改善粘附性。还可通过化学气相沉积(cvd)使sio2进行原位沉积。在替代性的实施方案中,可通过cvd或等离子体增强cvd(pecvd)使sicl4 o2或者o2等离子体进行沉积以形成该氧化物层。在又一实施方案中,可沉积其他聚合物以形成外表面上的层,从而进一步促进聚合物的粘附性。

36.在步骤340中,在使用半导体处理室以处理半导体晶片而导致丘形结构腐蚀之后,可将硅组件的外表面翻新。举例来说,如果锥体或小丘的高度变得低于500纳米,则可执行

翻新处理以增加表面积并延长组件的寿命。在一些实施方案中,通过对外表面进行化学性的再蚀刻而使硅组件的外表面翻新。在其他实施方案中,硅组件的外表面是通过模板辅助的方式来进行翻新,或者通过使用现有已腐蚀的丘形纹理硅表面作为蚀刻掩模模板来进行翻新,以对硅组件的表面形态进行调整或使其再生。如果需要,在步骤350中可类似于步骤330在翻新后的硅组件外表面上形成氧化物层,以实现更佳的聚合物粘附性。在一些实施方案中,可省略步骤330与350的氧化物层形成步骤。

37.图4是用于对半导体处理室的硅组件进行选择性纹理化的方法400的另一实施方案的流程图。在步骤410中,提供半导体室的含硅组件。接着在该组件的至少一部分中对该含硅组件的外表面进行选择性纹理化以增加表面积。首先可在步骤420中通过对硅组件的外表面进行图案化及遮蔽而使该外表面选择性纹理化,随后于步骤430中进行化学或机械蚀刻以在该硅组件的外表面上选择性形成丘形结构。

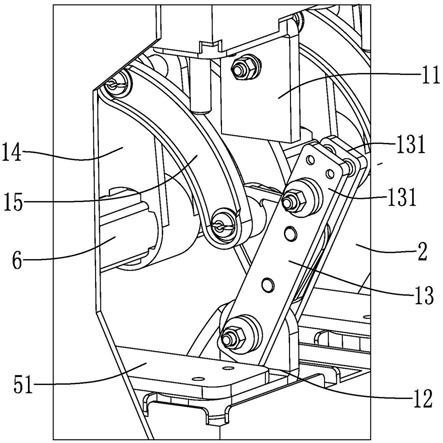

38.根据另一实施方案,代替锥形或丘形结构,可以在半导体处理室100的硅表面上生成反向丘形或反向锥体结构以增加硅表面的表面积,从而改善聚合物的粘附性。如图2b所显示的,这些反向锥体210类似于锥形或丘形结构,不过他们是反向的。根据一些实施方案,反向锥体210可通过使用涉及光刻激光处理等等的技术来生成。

39.在硅表面上纹理化出这种反向锥体的较简易方法涉及在cu(no3)2/hf/h2o2/h2o的混合物中使用结晶硅的无掩模cu纳米粒子(np)辅助各向异性蚀刻,优选是在约50℃下进行约15分钟。根据该实施方案,在纹理化之后可接着使用浓硝酸在超音波浴中将反向锥体清洗至少约20分钟,以去除剩余的cu

‑

np。上方所给出的参数是基于等离子体半导体处理室的硅组件的纹理化处理,所述处理室例如是由lam research corporation(fremont,california)所制造的系列产品。

40.纹理化可用于对半导体处理室100内的硅部件(例如,边缘环109、气体分配板106、与高流量套筒104)进行选择性图案化或优先性蚀刻。这种选择性图案化或优先性蚀刻可通过使用掩模来实现。举例来说,可对不同区域进行图案化及遮蔽以产生具有不同高度、或不同密度、或不同表面粗糙度的反向小丘。在一些实施方案中,自身的纹理化可作为掩模使用以产生进一步的纹理化。

41.在等离子体处理室100的一特定实施方案中,上电极(喷头)106是由单晶硅形成的,并进行选择性纹理化以在其中心部分具有增加的表面粗糙度,从而局部性控制粘附性。在一些情况下,由于该处理及后续聚合物沉积与蚀刻中的非均匀性,这可能会提供粘附的选择性。在其他实施方案中,硅组件是边缘环或高流量套筒,且所述组件可能会或可能不会进行选择性纹理化。

42.由于通过调整纹理化所使用的化学品及其他处理条件可对小丘或锥体的形状、小丘或锥体的高度(峰部到谷部)、以及小丘或锥体的反射率进行选择,因此反向锥体结构的纹理化也是可调整的。反向锥体的表面形态可通过调整蚀刻时间、蚀刻温度、以及cu(no

3)2

/hf/h2o2/h2o的混合物浓度来进行控制。根据一些实施方案,用于生成反向锥体结构的纹理化处理是在约40℃至70℃的范围内进行的。

43.根据一实施方案,在使用cu(no

3)2

/hf/h2o2/h2o的混合物进行纹理化之前,可将具有1

‑0‑

0晶体定向的结晶硅在丙酮中进行清洗,以移除有机污染物且随后使用去离子水进行清洗。

44.参照图5,描述了用于对半导体处理室的硅组件进行纹理化的方法500的一实施方案。该方法500开始于步骤510:提供半导体处理室的硅组件。该硅组件具有外表面。根据一些实施方案,该硅组件是由单晶硅形成的。在其他实施方案中,该硅组件是多晶硅或掺杂硅。在步骤520中,结晶硅组件可以在丙酮中进行清洗以移除有机污染物,随后于步骤530中再以去离子水进行清洗。

45.在步骤540中,对硅组件进行化学蚀刻以在该硅组件的外表面上生成反向的丘形结构。根据一实施方案,该硅组件是使用无掩模的cu纳米粒子(np)进行化学蚀刻,以对硅表面进行各向异性蚀刻。可使用cu(no3)2/hf/h2o2/h2o的混合物将硅表面纹理化,优选是在约50℃的温度下进行约15分钟。

46.如果需要,在步骤550中可在硅组件的外表面上形成氧化物层,以实现更好的聚合物粘附性。氧化物层的厚度优选介于约10nm至100微米的范围内。根据一实施方案,可将外层进行原位热氧化以形成该氧化物层。根据另一实施方案,是在表面上形成硅氧化物(sio2)层以改善粘附性。还可以通过化学气相沉积(cvd)原位沉积sio2。在替代性实施方案中,可通过cvd或等离子体增强cvd(pecvd)沉积sicl4 o2或者o2等离子体以形成该氧化物层。在又一实施方案中,可沉积其他聚合物以形成外表面上的层,以进一步促进聚合物的粘附性。

47.在步骤560中,在使用半导体处理室来处理半导体晶片而导致反向丘形结构腐蚀之后,可将硅组件的外表面翻新。举例来说,如果反向锥体或反向小丘的高度变得低于约500纳米,则可执行翻新处理以增加表面积并延长组件的寿命。在一些实施方案中,通过对外表面进行化学性的再蚀刻而使硅组件的外表面翻新。在其他实施方案中,硅组件的外表面是通过模板辅助的方式来进行翻新,或通过使用现有已腐蚀的反向丘形纹理硅表面作为蚀刻掩模模板来进行翻新,以对硅组件的表面形态进行调整或使其再生。

48.如果需要,在步骤570中,可类似于步骤550在翻新后的硅组件的外表面上形成氧化物层,以实现更佳的聚合物粘附性。在一些实施方案中,可省略步骤570的氧化物形成步骤。

49.图6是用于对半导体处理室的硅组件进行选择性纹理化的方法600的另一实施方案的流程图。在步骤610中,提供半导体室的含硅组件。接着在该组件的至少一部分中对该含硅组件的外表面进行选择性纹理化以增加表面积。该外表面可以通过以下方式选择性纹理化:首先在步骤620中通过对硅组件的外表面进行图案化及遮蔽,随后于步骤630中进行化学或机械蚀刻以在该硅组件的外表面上选择性形成反向的丘形结构。

50.根据另一实施方案,半导体处理室100的气体分配板106以及高流量套筒104是由多结晶硅形成。铸造多结晶硅本体。铸造后的多结晶硅本体具有外表面,该外表面是被纹理化以形成包括凸部的丘形结构。在该实施方案中,凸部具有至少500nm的高度,其中凸部的面积是形成在多结晶硅本体的纹理化表面的整个面积的至少90%上。在多种实施方案中,多结晶硅本体的纹理化表面是该多结晶硅本体的整个表面。

51.在一实施方案中,mae处理使用硝酸、氢氟酸、以及醋酸的混合物,其摩尔比分别为4:1:6。将硅本体的表面暴露于混合酸中以进行蚀刻,并生成纹理化表面。

52.图7是硅本体的纹理化表面704的放大图像。该硅本体的纹理化表面704具有第一晶粒708和第二晶粒712。虚线716所指出的晶粒边界介于第一晶粒708与第二晶粒712之间。

如图7所显示,纹理化使得第一晶粒708的晶粒表面的纹理不同于第二晶粒712的晶粒表面的纹理。不受理论的约束,不同晶粒708、712具有不同的定向(orientation)。取决于晶体的定向,蚀刻是各向异性的。因此,不同晶粒708、712具有不同纹理。然而,本实施方案中的纹理化造成具有丘形结构(包括凸部)的纹理化表面的不同晶粒表面。在本实施方案中,凸部具有至少500nm的高度,其中凸部的面积形成在多结晶硅本体的纹理化表面的面积的至少90%上。因此,尽管不同晶粒表面的纹理是不同的,但该不同晶粒结构的某些特性是一致的,例如使凸部高度和面积百分比介于阈值范围内。

53.根据一些实施方案,本文所述的纹理化处理是在约5℃至80℃的温度范围内进行。在其他实施方案中,该温度范围是约25℃至100℃。纹理化可用于适合用于半导体处理室100中的多结晶硅部件(例如,边缘环109、气体分配板106、上外部电极116、与高流量套筒104)。在一些实施方案中,纹理化可进行60秒至100秒。

54.从小丘峰部至谷部的平均高度可介于约500纳米至20微米的范围内。在一些实施方案中,小丘的高度可比小丘的平均高度低或高达20%。根据一些实施方案,丘形结构的高度可实质上与聚合物的厚度类似,以协助改善沉积后聚合物的粘附性。

55.根据一些实施方案,在根据本文所述的实施方案的纹理化之后,室部件的表面积增加多达1000%。

56.参照图8,描述了用于对半导体处理室100中适用的多结晶硅组件本体进行纹理化的方法的一实施方案。该方法始于提供半导体处理室的多结晶硅组件本体(步骤804)。在本实施方案中,该多结晶硅组件本体是通过铸造而形成的气体分配板106。该多结晶硅组件本体具有外表面。对该多结晶硅组件本体进行化学蚀刻,以在该多结晶硅组件本体的外表面上生成凸部或凹部(步骤808)。这些凸部或凹部可以是丘形结构,其中凹部为反向的丘形结构。根据一实施方案,使用硝酸、氢氟酸、以及醋酸的混合酸(摩尔数相应为4:1:6)来对该多结晶硅组件本体进行化学蚀刻。将该多结晶硅组件本体使用于半导体处理室100中(步骤812)。在半导体处理室100中的使用造成丘形结构腐蚀。举例来说,小丘的高度可能变得少于500纳米。另外,沉积物可能会堆叠在多结晶硅组件本体的外表面的部分上。将使用后的多结晶硅组件本体的外表面进行翻新,以增加表面积并且延长组件的寿命(步骤816)。在本实施方案中,通过对多结晶硅组件本体的表面进行抛光来将硅组件的外表面翻新。抛光将在使用期间沉积在表面上的污染物去除,并使多结晶硅组件本体的表面变得光滑。抛光可将介于0.5mm至2mm之间的多结晶硅组件本体的表面去除。接着,使用上述的蚀刻配方来对多结晶硅组件本体的表面进行化学再蚀刻以生成新的凸部或凹部(例如,丘形结构)(步骤820)。随后,可将多结晶硅组件再次使用于半导体处理室100内。

57.根据另一实施方案,代替形成凸部的丘形结构,该丘形结构形成凹部或草皮状部(divots)。在多种实施方案中,可使用不同比例的mae。代替使用硝酸、氢氟酸、及醋酸的混合酸(摩尔比为4:1:6)的mae处理,其他实施方案可使用硝酸、氢氟酸、及醋酸在其他比例下的混合酸的mae,其中醋酸的体积摩尔浓度(molarity)至少是氢氟酸的体积摩尔浓度的两倍,且醋酸的体积摩尔浓度大于硝酸的体积摩尔浓度。出乎意料地发现,这种蚀刻处理将会提供跨越晶粒边界的均匀纹理,因为凸部与凹部具有特定范围内的高度及面积。对于不同的多结晶晶粒而言,虽然纹理化是不同的,但是在阈值内仍是均匀的。在其他实施方案中,可使用其他各向异性蚀刻处理来提供跨越晶粒边界的均匀纹理,使得该纹理化所提供的凸

部或凹部是在指定的范围内。

58.在多种实施方案中,铸造多结晶硅组件本体。这种铸造可通过将硅熔化、将硅倒入模具中、以及将硅冷却以形成整块的(bulk)多结晶硅本体来执行,而并非将硅形成单晶结构。

59.尽管仅详细描述了本发明的几个实施方案,但应当理解在不背离本发明的精神或范围的情况下,本发明可由许多其他形式来实施。基于前述所有内容,显而易见的是所呈现的实施方案是说明性而非限制性的,且本发明并不限于本文所给出的细节,而是可在随附权利要求的范围和等同方案中进行修改。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。