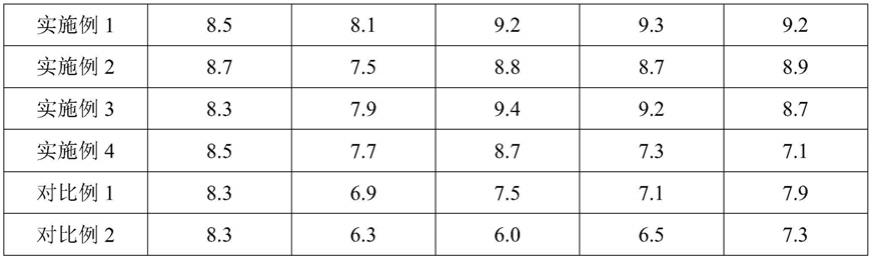

一种小周期z切压电晶片、薄膜、波导及其制备方法

技术领域

1.本技术属于功能性半导体材料领域,特别涉及一种小周期z切压电晶片、薄膜、波导及其制备方法。

背景技术:

2.由于具有较高的非线性频率转换效率,基于准位相匹配的超晶格波导受到国内外研究人员的长期关注和研究。目前,制备超晶格波导的方法主要包括两大类:一是先制备超晶格薄膜,再在超晶格薄膜上制备超晶格波导;二是先制备薄膜波导,再对薄膜波导制备超晶格结构。

3.对于第一种制备方法,超晶格薄膜可通过室温电场极化法制备,图1a至图1f示出室温电场极化法制备超晶格压电晶体薄膜的极化电极以及畴翻转过程示意图,如图1a至图1f所示,室温电场极化法,首先在压电晶体薄膜( z面向上)的上表面间隔设置周期性正电极板,在所述压电晶体薄膜的下表面设置整体负电极,通过向所述压电晶体薄膜施加电场,使所述压电晶体薄膜正负电极相对的区域发生畴反转,从而形成超晶格薄膜。

4.然而,薄膜型超晶格波导所需超晶格周期较小,例如,用薄膜型超晶格波导实现1550nm到775nm波长光转换,需要4μm周期左右的超晶格结构,图2a至图2c示出畴翻转过程中连畴形成的过程,如图2a至图2c所示,由于畴壁处激活能较低,容易成核,因此,在压电晶体薄膜上制备周期较小的光学超晶格易导致畴横向扩展严重,引起连畴现象。例如,即使使用宽度最小的1μm电极,能够得到的最小超晶格周期也为8μm,是目标周期长度的2倍,并且,常规光刻机光刻出小于1μm的线条宽度也具有相当大的难度。

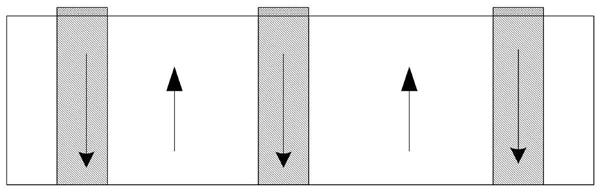

5.图3示出对薄膜波导制备超晶格结构的电极分布示意图,如图3所示,对于第二种制备方法,通常在x切的压电晶体薄膜001的单侧表面直接制备周期性的正负电极002,正负电极002相对设置,通过所述正负电极施加电场加以制备。但是,这种方法对电极的加工制备所要求的工艺条件高,制备过程缓慢,一次只能制备一条光学超晶格波导,效率低下。图4示出采用所述第二种方法制备的超晶格薄膜波导的照片,由图4可知,采用所述第二种制备方法制得的超晶格波导的畴翻转结构的畴壁不垂直,反转区域内部并未完全反转,只能在薄膜表面形成畴反转,而且,所形成的畴并非为规则的矩形,不利于产品的工业生产。

技术实现要素:

6.为解决上述技术问题中的至少一种,例如,超晶格波导制备工艺复杂,所制得超晶格波导中畴结构质量差,超晶格周期长等问题,本技术提供一种小周期z切压电晶体晶片、薄膜、波导及其制备方法,所述小周期z切压电晶体晶片,以及基于所述晶片制备的薄膜和波导均具有超晶格结构,并且,所述超晶格结构的周期可以达到6μm以下,甚至可达2μm,并且,所述超晶格结构均具有较为平整的电畴壁,本技术提供的制备所述小周期z切压电晶体晶片、薄膜、波导方法简便,易于操作,工艺条件易于控制。

7.本技术的目的在于提供以下几个方面:

8.第一方面,本技术提供一种小周期z切压电晶片,所述晶片具有周期分布的超晶格结构,其中,所述超晶格结构的周期长度为2~6μm,优选为4.3μm,所述超晶格结构的电畴壁由晶片的 z面贯穿至晶片的

‑

z面,并且,所述超晶格结构中每个电畴的剖面为楔形。

9.在一种可实现的方式中,所述超晶格结构的电畴壁与 z面的夹角为0

°

~0.2

°

。

10.在一种可实现的方式中,制备所述小周期z切压电晶片的材料包括同成分铌酸锂、同成分钽酸锂、近化学计量比铌酸锂、近化学计量比钽酸锂、掺杂铌酸锂、掺杂钽酸锂和磷酸氧钛钾(ktiopo4,ktp)等。

11.第二方面,本技术还提供一种小周期z切压电薄膜,所述薄膜由第一方面所述小周期z切压电晶片减薄所得。

12.在一种可实现的方式中,所述薄膜的厚度为100nm~50μm,优选为300nm~5μm,例如600nm,以使薄膜波导中的光斑半径减小,能量集中,提高薄膜波导的性能,并且,上述厚度的薄膜便于制造。

13.在一种可实现的方式中,所述薄膜的超晶格结构中,每个电畴区域的最小宽度为1μm,最大宽度为5μm。

14.在一种可实现的方式中,所述减薄的方式包括研磨以及离子注入等。

15.第三方面,本技术还提供一种小周期z切压电基体,所述小周期z切压电基体包括衬底层1和小周期z切压电薄膜层2,所述小周期z切压电薄膜层2为第二方面所述小周期z切压电薄膜。

16.在一种可实现的方式中,制备所述衬底层1的材料为半导体材料,所述半导体材料包括硅、二氧化硅、三氧化二铝、钽酸锂和铌酸锂。

17.可选地,所述衬底层1的厚度为1μm~1000μm,优选为200μm至800μm,使得所述衬底层1具有足够的强度来用作支持小周期z切压电薄膜层2的基体,防止样品在移动过程中碎裂。

18.在一种实现的方式中,所述小周期z切压电薄膜层2的

‑

z面与所述衬底层1贴合,以便于形成周期性畴翻转结构。

19.第四方面,本技术还提供一种小周期z切压电波导,所述波导由第三方面所述小周期z切压电基体制备。

20.第五方面,本技术还提供一种制备第一方面所述小周期z切压电晶片的方法,所述方法包括:

21.在z切压电晶片的上表面和下表面分别制备电极衬底,所述电极衬底为周期性电极衬底,其中,位于上表面的电极衬底与位于下表面的电极衬底具有预设套刻差;

22.在所述电极衬底上制备金属电极;

23.通过所述金属电极向所述z切压电晶片施加电压,电场方向为

‑

z方向;

24.畴反转结束后清洗所述金属电极以及电极衬底。

25.在一种可实现的方式中,所述在z切压电晶片的上表面和下表面分别制备电极衬底可以采用光刻以及套刻的方法。

26.在一种可实现的方式中,所述电极衬底的周期为2~10μm,优选为3~6μm,例如4μm。

27.在一种可实现的方式中,位于上表面的电极衬底与位于下表面的电极衬底的套刻

差为0.1~2.0μm,优选为0.3~1.0μm,例如0.5μm。

28.本技术人发现,

‑

z面表面畴的横向扩展宽度受到套刻差影响,具体地,套刻差越大,所得

‑

z面表面畴的宽度越小。

29.在一种可实现的方式中,所述在所述电极衬底上制备金属电极可以为在所述电极衬底上蒸镀金属电极,优选地,可以利用电子束蒸发技术进行蒸镀,本技术人发现,电子束蒸发效率质量比较好,效率比较高,具体地,采用电子束蒸发所得电极的质量足够工艺所需,并且镀膜速度快。

30.可选地,所述金属电极包括为铬电极、镍电极、铝电极或者钛电极等。

31.在一种可实现的方式中,所述金属电极的厚度为50nm~1000nm,优选为100nm~500nm,例如200nm,如果所述金属电极的厚度过小,则电极不能存储电荷,从而向空气中放电,导致畴翻转时漏电,进而导致畴翻转不能正常进行;如果金属电极的厚度过大,会导致制备效率低下。

32.在一种可实现的方式中,通过所述金属电极向所述z切压电晶片所施加电压的大小为20kv/mm~26kv/mm,例如,24kv/mm。由于晶体矫顽场在24kv/mm附近,在矫顽场附近进行畴翻转,可以降低畴扩展的宽度。

33.第六方面,本技术还提供一种制备第二方面所述小周期z切压电薄膜的方法,所述方法包括:

34.在第二方面所述小周期z切压电晶片上制备无机硅薄膜层;

35.在衬底层上涂覆釉料层;

36.对所述釉料层进行平坦化处理;

37.将所述无机硅薄膜层与所述釉料层进行键合;

38.对键合体中小周期z切压电晶片进行减薄处理;

39.除去除所述小周期z切压电晶片层外的所有材料。

40.第七方面,本技术还提供一种制备第三方面所述小周期z切压电基体的方法,所述方法包括:

41.在第二方面所述小周期z切压电晶片上制备无机硅薄膜层;

42.在衬底层上涂覆釉料层;

43.对所述釉料层进行平坦化处理;

44.将所述无机硅薄膜层与所述釉料层进行键合;

45.对键合体中小周期z切压电晶片进行减薄处理。

46.第八方面,本技术还提供一种制备第四方面所述小周期z切压电波导的方法,所述方法包括:

47.在第三方面所述小周期z切压电基体的小周期z切压电薄膜层2制备光刻胶图形;

48.根据所述光刻胶图形在所述小周期z切压电薄膜层2制备掩膜图形;

49.对所述掩膜图形之外的区域进行刻蚀;

50.清洗所述掩膜图形上的掩膜。

51.与现有技术相比,本技术提供的小周期z切压电晶体晶片具有较小的超晶格周期,并且,所述超晶格结构的畴结构质量高,具的接近平直的电畴壁,上述小周期z切压电晶体晶片本技术通过设置具有特定套刻差的周期性电极制备,制备工艺简单,条件易于控制,基

于所述小周期z切压电晶体晶片制备的小周期z切压电晶体薄膜和波导也相应地具有高质量的超晶格结构,在半导体器件,例如,光波长转换器件中表现出优良的性能。

附图说明

52.图1a示出室温电场极化法制备超晶格压电晶体薄膜的极化电极示意图;

53.图1b示出室温电场极化法制备超晶格压电晶体薄膜畴生长初期示意图;

54.图1c示出室温电场极化法制备超晶格压电晶体薄膜畴生长中期示意图;

55.图1d示出室温电场极化法制备超晶格压电晶体薄膜畴翻转初期示意图;

56.图1e示出室温电场极化法制备超晶格压电晶体薄膜畴翻转中期(畴扩张)示意图;

57.图1f示出室温电场极化法制备超晶格压电晶体薄膜畴翻转完成示意图;

58.图2a示出畴翻转过程中连畴形成初期(畴生长)示意图;

59.图2b示出畴翻转过程中连畴形成中期示意图;

60.图2c示出畴翻转过程中连畴形成畴扩张期示意图;

61.图3示出对薄膜波导制备超晶格结构的电极分布示意图;

62.图4示出另一种现有技术制备的超晶格薄膜波导的照片;

63.图5示出根据本实例优选小周期z切压电晶片的剖面结构示意图;

64.图6示出图5所示晶片的俯视图;

65.图7示出一种制备如图5所示小周期z切压电晶片的流程示意图;

66.图8示出一种小周期z切压电薄膜;

67.图9示出本实例一种制备图7所示小周期z切压电薄膜的流程示意图;

68.图10示出一种小周期z切压电基体;

69.图11示出制备图9所示小周期z切压电基体的流程图;

70.图12示出一种小周期z切压电波导剖面结构示意图;

71.图13示出一种制备图12所示小周期z切压电波导的方法流程图;

72.图14a示出实施例2制备的钽酸锂晶体正z面的畴腐蚀图;

73.图14b示出实施例2制备的钽酸锂晶体负z面的畴腐蚀图;

74.图15示出实施例6制备的光学超晶格薄膜波导的结构示意图。

75.附图标记说明

[0076]1‑

衬底层,2

‑

小周期z切压电薄膜层,3

‑

电畴壁,4

‑

晶片,41

‑

z切压电晶片,42

‑

电极衬底,43

‑

金属电极,44

‑

无机硅薄膜层,45

‑

釉料层,51

‑

正电畴,52

‑

负电畴,001

‑

x切的压电晶体薄膜,002

‑

周期性的正负电极。

具体实施方式

[0077]

这里将详细地对示例性实施例进行说明,其示例表示在附图中。下面的描述涉及附图时,除非另有表示,不同附图中的相同数字表示相同或相似的要素。以下示例性实施例中所描述的实施方式并不代表与本发明相一致的所有实施方式。相反,它们仅是与如所附权利要求书中所详述的、本发明的一些方面相一致方法的例子。

[0078]

以下简要介绍本技术的场景。

[0079]

制备压电材料超晶格结构一般包括两种方法。一种制备超晶格结构的方法为,向

压电晶圆,例如,铌酸锂晶圆的上下表面分别制备电极,其中,一侧电极为片状电极,即,压电晶圆的该侧表面完全覆盖电极,另一侧为周期性电极,即,压电晶圆表面按照预设周期设置条形电极,这种方法能够大面积制备厚度达到500μm的超晶格结构,但是,由于压电晶圆的厚度一般在毫米量级,即,厚度过大,而电畴反转过程中,各电畴的反转速度以及横向扩展速度不均一,受到成核率、晶圆厚度等因素影响,当部分电畴达到设定宽度后,其它部分电畴还未达到设定宽度,这就导致该方法无法制备周期较小的超晶格结构。

[0080]

另一种方法为在x切或y切的压电薄膜上制备小周期光学超晶格结构,一般在薄膜表面设置相对的周期性电极,电极相对的方向为z切向,向电极中通电,使得每组相对设置的两个电极之间产生电压,促使两电极之间的薄膜发生畴反转从而形成较小周期的超晶格结构。由于在薄膜上,相对设置的两个电极之间的间距不能相隔太远,否则难以形成电压,因此,该方法难以在薄膜表面大面积制备小周期超晶格结构。

[0081]

而在晶圆表面制备浅层的大面积小周期超晶格,传统有两种方法:

[0082]

一是在压电晶圆的 z面制备周期性电极,并通过加载高电压、短通电时长来向所述电极上加载少量电量,直接在 z面表面制备超晶格结构,但是这种方法受成核率的限制,制得的超晶格结构均匀性较差,无法大面积制备超晶格结构;

[0083]

二是在压电晶圆的

‑

z面制备周期性电极,通过加载高电压、长通电时长来向所述电极上加载过量电量,利用

‑

z面周期性电极的抑制作用,直接在

‑

z面表面制备超晶格结构,但是这种方法所制得超晶格结构的畴壁不直,质量差。

[0084]

因此,采用现有技术的方法所制备的压电超晶格结构,至少在厚度、面积与周期这三个因素上难以获得同时满足需求的产品。

[0085]

下面通过具体的实施例对本技术提供的小周期z切压电晶片、小周期z切压电薄膜、小周期z切压电基体及它们的制备方法进行详细阐述。

[0086]

由于具有优异的电光、声光、压电、光折变特性以及机械性能等特点,压电晶体材料,例如,铌酸锂或者钽酸锂等,被广泛应用于光电子集成领域。特别地,在光纤通讯领域中,采用压电晶体材料制备的波导调制器具有体积小、性能高以及功耗低等优点,因此,压电晶体材料成为制备波导调制器的主流材料。

[0087]

进一步地,与传统的扩散型波导,薄膜波导一般包括层压的压电薄膜层、隔离层和衬底层,其中,隔离层通常由折射率大于压电薄膜层折射率的材料制备,例如二氧化硅等,使光波或者声波能够更好的被束缚于压电薄膜层中,从而减少声波或者光波的泄露以及损耗,以铌酸锂

‑

二氧化硅为例,压电薄膜层与隔离层的折射率之差可达0.7左右,而传统铌酸锂扩散波导的扩散层与非扩散层折射率差仅为0.01左右,而且,薄膜波导的尺寸小,更便于光电子芯片集成,因此,薄膜波导逐渐成为研究热点。

[0088]

通常,薄膜波导基于单晶压电基体制备而成,所述单晶压电基体一般包括衬底层、隔离层和压电薄膜层,其中,压电薄膜层具有周期极化结构。可以理解的是,单晶压电基体还可以包括其它功能性或者功能性层结构。

[0089]

在本实例中,所述小周期z切压电晶片基于z切压电晶片制备而得,而所述小周期z切压电薄膜以及所述小周期z切压电基体均可以基于所述小周期z切压电晶片制备而得。

[0090]

进一步地,所述小周期z切压电晶片的材料包括同成分铌酸锂、同成分钽酸锂、近化学计量比铌酸锂、近化学计量比钽酸锂、掺杂铌酸锂、掺杂钽酸锂以及ktp等,即,本实例

所述小周期z切压电薄膜以及所述小周期z切压电基体中的压电薄膜层的材料相应地可以包括同成分铌酸锂、同成分钽酸锂、近化学计量比铌酸锂、近化学计量比钽酸锂、掺杂铌酸锂、掺杂钽酸锂以及ktp等。

[0091]

在本实例中,由于只有沿z方向向晶片上施加电压才会使晶片发生畴反转,因此,本实例选择使用z切晶片作为制备小周期z切压电晶体的基础。

[0092]

图5示出根据本实例优选小周期z切压电晶片的剖面结构示意图,图6示出图5所示晶片的俯视图,如图5和图6所示,本实例提供小周期z切压电晶片在宏观外形上与不具有超晶格结构的z切压电晶片相同或者基本相同,但是在微观层面上,本实例提供的小周期z切压电晶片具有超晶格结构,所述超晶格结构可以为由在所述晶片上沿其直径方向周期性交替分布的极化方向相反的电畴所形成。

[0093]

特别地,本实例所述小周期z切压电晶片的极化周期为2~6μm,例如,4.3μm。

[0094]

本领域技术人员可知,在所述超晶格结构中,每个电畴均包括两个电畴壁3,这两个电畴壁3在具有超晶格结构的晶片4中可能相交也可能不相交,两个电畴壁3与晶片4的上下两个面共同围成一块区域,该区域即为一个电畴。其中,极化方向与 z方向相同的称之为正电畴51,极化方向与

‑

z方向相同的,称之为负电畴52。

[0095]

在本实例中,所述超晶格结构的电畴壁由压电晶片的 z面贯穿至压电晶片的

‑

z面,并且,每个所述电畴的剖面均为楔形,具体地,在所述 z面上,负畴的宽度大于正畴的宽度;在所述

‑

z面上,负畴的宽度与正畴的宽度接近,可选地,在所述

‑

z面上,基于负畴的宽度,负畴的宽度与正畴的宽度相差小于20%。

[0096]

在本实例中,同一个正电畴中两个电畴壁之间的夹角α为0~0.5

°

,并且,同一个所述正电畴中,基准电畴壁与 z面之间的夹角β为0~0.2

°

,其中,所述基准电畴壁为同一个正电畴中与 z面更接近垂直的电畴壁。

[0097]

在本技术中,所述小周期z切压电晶片是以压电晶圆为基础制备超晶格结构而获得的产品,即,具有超晶格结构的压电晶圆,所述小周期z切压电晶片可用于制备小周期z切压电薄膜,由所述小周期z切压电晶片可用于制备小周期z切压电薄膜的方法可以采用现有技术中任意一种用压电晶圆制备压电薄膜的方法,例如,研磨抛光法或者离子注入法等。

[0098]

图7示出一种制备如图5所示小周期z切压电晶片的流程示意图,如图7所示,所述方法包括以下步骤s101至步骤s104:

[0099]

步骤s101,在z切压电晶片41的上表面和下表面分别制备电极衬底42,所述电极衬底42为周期性电极衬底,其中,位于上表面的电极衬底42与位于下表面的电极衬底42具有预设套刻差。

[0100]

在本实例中,所述z切压电晶片为切向为z的压电晶片,所述压电晶片可以为同成分铌酸锂、同成分钽酸锂、近化学计量比铌酸锂、近化学计量比钽酸锂、掺杂铌酸锂、掺杂钽酸锂以及ktp等,厚度可以达到500μm。

[0101]

在本实例中,在制备电极衬底前,可以首先对所述z切压电晶片的上下表面分别进行抛光和清洗。本技术对抛光和清洗的具体方法不做特别限定,可以使用现有技术中任意一种对压电晶片进行抛光和清洗的方法。

[0102]

在本实例中,所述在z切压电晶片的上表面和下表面分别制备电极衬底可以采用光刻以及套刻的方法,具体地,可以首先在所述z切压电晶片涂覆光刻胶,即,电极衬底,以

便于在所述z切压电晶片上制备电极。

[0103]

本技术对光刻以及套刻的具体实现方式以及参数不做特别限定,可以采用现有技术中任意一种可用于在z切压电晶片的上表面和下表面分别制备电极衬底的方法,具体参数可根据具体需要而具体设定。

[0104]

在本实例中,所述电极衬底的周期为2~10μm,优选为3~6μm,例如4μm,即,每个电极衬底的宽度为一个周期,并且,相同两个电极衬底的间距也为一个周期。本技术人发现,按照上述周期设置电极衬底,可使上电极与下电极之间形成较小的超晶格周期,并且,上述周期可以使用紫外光刻方法来制备,制备过程简单,更小周期则需要用到电子束曝光方法,难以制备,而更大周期使用常规方法即可制备。

[0105]

在本实例中,位于上表面的电极衬底与位于下表面的电极衬底的套刻差为0.1~2.0μm,优选为0.3~1.0μm,例如0.5μm。本技术人发现,采用上述套刻差可获得目标周期的超晶格结构。具体地,

‑

z面表面畴的横向扩展宽度受到套刻差影响,具体地,翻转的畴随套刻差是增大而减小。

[0106]

步骤s102,在所述电极衬底上制备金属电极。

[0107]

在本实例中,制备金属电极43可以采用现有技术中任意一种在压电晶圆表面制备电极的方法,例如,在所述电极衬底上蒸镀金属电极,优选地,可以利用电子束蒸发技术在所述电极衬底上蒸镀制备电极,本技术人发现,电子束蒸发效率高,所述获得电极质量足够后续工艺所需。

[0108]

在本实例中,金属电极43的材料可以为现有技术中任意一种用于在压电晶圆表面制备电极的材料,具体包括铝、铬、镍、钛或者镍铬合金等,所制备的金属电极包括铝电极、铬电极、镍电极、钛电极或者镍铬合金电极等。

[0109]

可选地,所述金属电极43的厚度可以为50nm~1000nm,优选为100nm~500nm,例如,200nm,所述金属电极的厚度过小会导致畴翻转时漏电,导致畴翻转无法正常进行;如果金属电极的厚度过大,会导致制备效率降低。

[0110]

在本实例中,电子束蒸发制备电极过程所选用的参数可以根据电极材料和电极厚度等参数而具体设定。

[0111]

步骤s103,通过所述金属电极向所述z切压电晶片施加电压,所施加电压的电场方向为

‑

z方向。

[0112]

在本实例中,向所述z切压电晶片施加方向为

‑

z方向的电压,使得所述z切压电晶片在电压所作用的范围内发生畴反转,而未被电压作用的区域则不发生畴反转,从而,在所述z切压电晶片上形成极化方向交替相反的超晶格结构。

[0113]

在本实例中,通过所述金属电极向所述z切压电晶片所施加电压的大小为20kv/mm~26kv/mm,例如,24kv/mm。由于晶体矫顽场在24kv/mm附近,在矫顽场附近进行畴翻转,可以降低畴扩展的宽度。

[0114]

可选地,在 z面接电源正极,在

‑

z面接电源负极,使得所施加电场方向与晶片的极化方向相反,从而使得所述晶片的畴发生反转,形成超晶格结构,施加电场至至畴翻转结束,即,所施加电场的电流变成0a。

[0115]

步骤s104,畴反转结束后清洗所述金属电极以及电极衬底。

[0116]

在实例中,可以采用现有技术中任意一种清洗压电材料表面金属电极以及电极衬

底的方法,例如,化学溶解法等。

[0117]

本技术提供的小周期z切压电晶片采用双面电极的方法制备而得,具体地,将

‑

z面的套刻的电极与 z面的套刻电极形成约0.5μm的套刻差,再向所述电极上加载过量的电量,在 z面上,由于电极周期较小,直接会发生连畴或者接近连畴的现象,而在

‑

z面上,由于电极与设置于 z面的电极不完全相对,而在未相对区域电畴难以生长,因此,在

‑

z面上不会发生连畴现旬,而是直接在

‑

z面的表面上形成超晶格结构。所述小周期z切压电晶片的厚度可达500μm,面积可达4~8英寸,超晶格周期可减小至2~6μm。所述小周期z切压电晶片可用于制备薄膜波导,从而实现高效的频率转换。

[0118]

本技术提供的制备小周期z切超晶格晶片的方法,单次制备所获得的超晶格结构面积大,厚度大,超晶格结构周期小,制备效率高,制备工艺难度和成本低,利于工业化生产。

[0119]

图8示出一种小周期z切压电薄膜,所述小周期z切压电薄膜由图5所示小周期z切压电晶片减薄所得。

[0120]

在本实例中,根据前述方法制备的小周期z切压电薄膜结构主要集中于所述小周期z切压电晶片的

‑

z面附近,因此,所述小周期z切压电薄膜可由所述小周期z切压电晶片的

‑

z面获取,所述薄膜的厚度可以根据需要而具体选择,例如,可以为100nm~50μm,优选为300nm~5μm,例如600nm,本技术人发现,由于薄膜的厚度越小,由其制备的波导中光斑的半径越小,能量也越集中,频率转换效率越高,但是,如果波导尺寸过小,例如,小于光波的波长,则会导致部分光泄露到波导之外,反而导致光频率转换效率降低,并且,薄膜的厚度在上述范围内能够方便地制备超晶格波导,因此,本实例选择所述薄膜的厚度为100nm~50μm。

[0121]

在本实例中,在所述薄膜的超晶格结构中,每个电畴区域的最小宽度为100nm,最大宽度为5μm。本技术人发现,宽度上于100nm的电畴难以制备,而宽度大于5μm的超晶格结构则不能称为小周期超晶格。

[0122]

在本实例中,所述减薄的方式可以包括研磨。

[0123]

图9示出本实例一种制备图7所示小周期z切压电薄膜的流程示意图,如图9所示,所述方法包括以下步骤s201至步骤s206:

[0124]

步骤s201,在所述小周期z切压电晶片上制备无机硅薄膜层44。

[0125]

在本实例中,所述无机硅薄膜层44可以为二氧化硅薄膜层、多晶硅薄膜层或者氮化硅薄膜层中的一种或几种。本技术人发现,所述无机硅薄膜层与釉料的物理化学性质相近,釉料可与所述无机硅薄膜层均匀结合,并且,所述无机硅薄膜层还能够起到低声阻层的作用,从而消除釉料由于在所述小周期z切压电晶片上涂布不均匀而造成的半导体器件性能的下降。

[0126]

本实例对制备所述无机硅薄膜层的方法不做特别限定,可以采用现有技术中任意一种在半导体压电晶片上制备无机硅薄膜层的方法,例如,热沉积法、键合法、粘合法等。

[0127]

在本实例中,所述无机硅薄膜层的厚度为2μm~3μm,优选为2μm,本技术人发现,所述无机硅薄膜层的厚度在上述范围下,能够防止光向下泄漏进基底材料中。

[0128]

可选地,可以对所述无机硅薄膜层进行抛光,使得所述无机硅薄膜层的表面粗糙度小于20nm,以便无机硅薄膜层与釉料结合得更为紧密。

[0129]

步骤s202,在衬底层1上涂覆釉料层45。

[0130]

在本实例中,本步骤具体可以包括以下步骤s221和步骤s222:

[0131]

步骤s221,在压电晶圆表面涂覆釉料。

[0132]

可选地,所述釉料的主要成分为二氧化硅,辅料包括:氧化铝、氧化锌、乙基纤维素,溶剂包括:酯类和醚类、醇类、烃类化合物中的至少两种,一般是脂类的再加上其它类的混合,脂类可以让浆料有良好的润滑性能,也就是可以加热完更平滑,其它的由于沸点低,在升温过程中气化,保证升温后气孔比较少其中,基于所述釉料的总体积,所述釉料中二氧化硅的含量为50g/ml~200g/ml,所述釉料的粘度为50pa

·

s~400pa

·

s,主要成分为高纯二氧化硅,所述釉料的熔点低于压电晶圆的熔点,优选地,所述釉料可以为玻璃浆料,其中,所述玻璃浆料的烧结温度为470℃~550℃,细度小于8μm,粘度为100pa

·

s~200pa

·

s,以便于在制备复合压电基体过程中仅有所述釉料为熔融状态,而压电晶圆为固态,并且,压电晶圆的晶格结构能够保持不变,以便保证所述复合压电基体的压电性能。

[0133]

可选地,在压电晶圆表面涂覆釉料的方法包括刷涂、悬涂和喷涂。

[0134]

进一步地,所述刷涂包括:

[0135]

在压电晶圆上铺设一层丝网,所述丝网的厚度为100μm~500μm,所述丝网的网格可以为正方形,网孔尺寸为1mm~20mm,材料可以为铜或者不锈钢;

[0136]

透过所述丝网向所述压电晶圆表面上均匀刷覆一层釉料,所述釉料的厚度小于或者等于所述丝网的厚度;

[0137]

取下所述丝网。

[0138]

在本技术中,所述悬涂可以为现有技术中任意一种可以晶圆为对象的悬涂方法;所述喷涂可以为现有技术中任意一种可以晶圆为对象的悬涂方法。

[0139]

步骤s222,对所述釉料进行平坦化处理并且定型。

[0140]

在本实例中,本步骤可以包括以下步骤s1221和步骤s1222:

[0141]

步骤s2221,对涂覆有所述釉料的压电晶圆加热至釉料溶剂的挥发温度,并保温。

[0142]

步骤s2222,继续升温至釉料熔点,保温后冷却。

[0143]

在本实例中,在升温至釉料熔点后,使釉料均匀成膜。

[0144]

在本实例中,所述釉料层的厚度为0.1~1000μm,优选为1~100μm,例如,20~60μm,以为压电晶圆提供充足的支撑作用。

[0145]

步骤s203,对所述釉料层进行平坦化处理。

[0146]

所述釉料冷却凝固后可对所述釉料层45进行表面处理,所述表面处理包括研磨和抛光。在本技术中,经过表面处理后,所述釉料层表面的粗糙度为小于10nm,方便基底与上层薄膜熔合后,上下表面平行。

[0147]

步骤s204,将所述无机硅薄膜层44与所述釉料层45进行键合。

[0148]

本步骤可以包括步骤s241至步骤s243:

[0149]

步骤s241,加热所述釉料层至熔融状态。

[0150]

步骤s242,将所述釉料层与所述二氧化硅层贴合。

[0151]

在本实例中,将熔融状态的釉料与所述二氧化硅层贴合后,向所述结合体上施加20g/cm2~20000g/cm2的力,并在该温度下保持压力0.5~10h,使其二者充分结合。

[0152]

步骤s243,冷却所述釉料层。

[0153]

在本实例中,冷却速度可以为1~3℃/h,以使结合体能够缓慢冷却,从而使得各层的微结构完好,避免由于骤冷而导致晶格损伤。

[0154]

步骤s205,对键合体中小周期z切压电晶片进行减薄处理。

[0155]

在本实例中,所述减薄处理可以包括研磨抛光,或者采用离子注入分离的方法。

[0156]

步骤s206,除去除所述小周期z切压电晶片层外的所有材料。

[0157]

在本实例中,除所述小周期z切压电晶片层外的所有材料包括无机硅薄膜层以及釉料层。

[0158]

本实例对除去除所述小周期z切压电晶片层外的所有材料的方法不做特别限定,可以采用现有技术中任意一种可去除附着于压电晶片的上述材料的方法,例如,化学溶解法等。

[0159]

本技术人发现,去除上述材料后可获得小周期z切压电薄膜。由于所获得小周期z切压电薄膜厚度很小,不便于后续使用,因此,仅在有特殊需求的情况下去除上述材料制备小周期z切压电薄膜。

[0160]

图10示出一种小周期z切压电基体,所述小周期z切压电基体包括衬底层1和小周期z切压电薄膜层2,所述小周期z切压电薄膜层2为图7所示小周期z切压电薄膜。

[0161]

在本实例中,制备所述衬底层1的材料为半导体材料,所述半导体材料包括硅、二氧化硅、三氧化二铝、钽酸锂和铌酸锂。

[0162]

可选地,所述衬底层1的厚度为1μm~1000μm。由于衬底层1一般用作支持小周期z切压电薄膜层2的基体,为防止样品在移动过程中碎裂,一般厚度在200μm以上。

[0163]

在本实例中,所述小周期z切压电薄膜层2的

‑

z面与所述衬底层1贴合,以便于形成周期性畴翻转结构。

[0164]

图11示出制备图9所示小周期z切压电基体的流程图,如图10所示,所述方法包括:

[0165]

在图5所示小周期z切压电晶片上制备无机硅薄膜层;

[0166]

在衬底层上涂覆釉料层;

[0167]

对所述釉料层进行平坦化处理;

[0168]

将所述无机硅薄膜层与所述釉料层进行键合;

[0169]

对键合体中小周期z切压电晶片进行减薄处理。

[0170]

图12示出一种小周期z切压电波导剖面结构示意图,所述波导由图10所示小周期z切压电基体制备。

[0171]

图13示出一种制备图12所示小周期z切压电波导的方法流程图,所述方法包括步骤s301至步骤s304:

[0172]

步骤s301,在图10所述小周期z切压电基体的小周期z切压电薄膜层2制备光刻胶图形;

[0173]

步骤s302,根据所述光刻胶图形在所述小周期z切压电薄膜层2制备掩膜图形;

[0174]

步骤s303,对所述掩膜图形之外的区域进行刻蚀;

[0175]

步骤s304,清洗所述掩膜图形上的掩膜。

[0176]

与现有技术相比,本技术提供的小周期z切压电晶体晶片具有较小的超晶格周期,并且,所述超晶格结构的畴结构质量高,具的接近平直的电畴壁,上述小周期z切压电晶体晶片本技术通过设置具有特定套刻差的周期性电极制备,制备工艺简单,条件易于控制,基

于所述小周期z切压电晶体晶片制备的小周期z切压电晶体薄膜和波导也相应地具有高质量的超晶格结构,在半导体器件,例如,光波长转换器件中表现出优良的性能。

[0177]

实施例

[0178]

实施例1光学超晶格晶片的制备

[0179]

(1)利用紫外光刻机和套刻技术在3英寸钽酸锂晶体上下表面制备宽度为1μm的周期性电极结构,上下表面电极不完全对准,套刻差为0.5μm;

[0180]

(2)利用电子束蒸发技术在上下表面蒸镀上一层厚度为200nm的cr金属电极;

[0181]

(3) z面接电源正极,

‑

z面接电源负极,施加约为24kv的电压,至畴翻转结束,即,通过监测电流低于5ma。

[0182]

极化结束后,钽酸锂晶体正负z面的畴腐蚀图如图14a和图14b所示,由图14a和图14b可知, z面已接近连畴,

‑

z面畴扩展较小。在

‑

z面,所得超晶格结构的周期为4.3μm。

[0183]

本实例所得光学超晶格晶片的厚度为500μm,面积为0.5mm

×

20mm。

[0184]

实施例2光学超晶格基体的制备

[0185]

(1)按照实施例1的方法制备3英寸钽酸锂晶片,厚度为0.5mm,晶格周期为4.3μm;将所述3英寸钽酸锂晶片与基质衬底分别抛光,清洗;

[0186]

(2)在所述钽酸锂晶片

‑

z面上沉积厚度为2μm的二氧化硅薄膜层,并对二氧化硅薄膜层进行平坦化加工,使得所述二氧化硅层的表面粗糙度小于20nm;

[0187]

(3)在基质衬底上涂覆一层玻璃釉料,其中,所述玻璃釉料中二氧化硅的含量为50g/ml,所述釉料的粘度为50pa

·

s,烧结温度为470℃,细度小于8μm,粘度为100pa

·

s,涂覆厚度为0.1μm;

[0188]

(4)将基质衬底进行一次升温,升温至可使釉料溶剂挥发温度并保温,直至挥发完全;

[0189]

(5)挥发完全后,将基质衬底进行二次升温,加热至釉料熔点,使釉料均匀成膜;

[0190]

(6)冷却基质衬底并对玻璃釉面进行平坦化加工;

[0191]

(7)将钽酸锂晶体的无机硅材料薄膜表面与基质衬底釉料表面贴合,加热至釉料熔点,加压至2000g/cm2,保持温度和压力0.5h,使其充分结合。

[0192]

实施例3光学超晶格薄膜的制备

[0193]

(1)按照实施例1的方法制备3英寸钽酸锂晶片,厚度为500μm,晶格周期为4.3μm;将所述钽酸锂晶片与基质衬底分别抛光,清洗;

[0194]

(2)在所述钽酸锂晶片

‑

z面上沉积厚度为2μm的多晶硅薄膜层,并对多晶硅薄膜层进行平坦化加工,使得所述多晶硅薄膜层的表面粗糙度小于10nm;

[0195]

(3)在基质衬底上涂覆一层玻璃釉料,其中,所述玻璃釉料中二氧化硅的含量为200g/ml,所述釉料的粘度为400pa

·

s,烧结温度为550℃,细度小于8μm,粘度为200pa

·

s,涂覆厚度为100μm;

[0196]

(4)将基质衬底进行一次升温,升温至可使釉料溶剂挥发温度并保温,直至挥发完全;

[0197]

(5)挥发完全后,将基质衬底进行二次升温,加热至釉料熔点,使釉料均匀成膜;

[0198]

(6)冷却基质衬底并对玻璃釉面进行平坦化加工;

[0199]

(7)将钽酸锂晶体的无机硅材料薄膜表面与基质衬底釉料表面贴合,加热至釉料

熔点,加压至20000g/cm2,保持温度和压力10h,使其充分结合;

[0200]

(8)降至室温后,将上层压电晶体减薄至1μm。

[0201]

实施例4光学超晶格薄膜的制备

[0202]

在实施例1制备的晶片基础上直接研磨抛光至厚度为5μm。

[0203]

实施例5光学超晶格薄膜波导的制备

[0204]

(1)在实施例3制备的钽酸锂薄膜表面利用ma6光刻机光刻出与脊形波导互补的光刻胶图形;

[0205]

(2)通过电子束蒸发在光刻胶图形上覆盖一层金属cr;

[0206]

(3)通过lift off工艺,去除光刻胶以及光刻胶层上的cr,留下cr掩膜图形;

[0207]

(4)利用icp刻蚀设备对样品进行刻蚀,刻蚀掉部分裸露在cr掩膜层之外的钽酸锂层;

[0208]

(5)利用cr清洗剂,清洗掉表面的cr掩膜,并对样品表面做轻微的抛光处理减小损耗。

[0209]

实施例6光学超晶格薄膜波导的制备

[0210]

在实施例4制备的光学超晶格薄膜的制备基础上,用划片机去除波导两边的部分,留下波导结构。划片深度约为50~100μm。制备成的结构如图15所示。

[0211]

本实例所制得超晶格薄膜波导的超晶格周期为4.3μm,面积为3英寸。

[0212]

以上结合具体实施方式和范例性实例对本技术进行了详细说明,不过这些说明并不能理解为对本技术的限制。本领域技术人员理解,在不偏离本技术精神和范围的情况下,可以对本技术技术方案及其实施方式进行多种等价替换、修饰或改进,这些均落入本技术的范围内。本技术的保护范围以所附权利要求为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。