1.本公开大体上涉及半导体存储器和方法,且更确切地说涉及识别所执行代码中的错误。

背景技术:

2.存储器装置通常提供为计算机或其它电子装置中的内部半导体集成电路和/或外部可移除装置。存在许多不同类型的存储器,包含易失性及非易失性存储器。易失性存储器可能需要电力来维持其数据,且可包含随机存取存储器(ram)、动态随机存取存储器(dram)和同步动态随机存取存储器(sdram)等等。非易失性存储器可通过当不被供电时保存所存储的数据来提供永久性数据,并且可包含nand快闪存储器、nor快闪存储器、只读存储器(rom)以及电阻可变存储器,例如相变随机存取存储器(pcram)、电阻性随机存取存储器(rram)和磁性随机存取存储器(mram)等等。

3.存储器装置可组合到一起形成固态驱动器(ssd)、嵌入式多媒体卡(例如mmc)和/或通用快闪存储(ufs)装置。ssd、e.mmc和/或ufs装置可包含非易失性存储器(例如,nand快闪存储器和/或nor快闪存储器),和/或可包含易失性存储器(例如,dram和/或sdram),以及各种其它类型的非易失性和易失性存储器。非易失性存储器可用于广泛范围的电子应用中,例如个人计算机、便携式存储器棒、数码相机、蜂窝式电话、便携式音乐播放器,例如mp3播放器、电影播放器等等。

4.快闪存储器装置可包含将数据存储在例如浮动栅极的电荷存储结构中的存储器单元。快闪存储器装置通常使用允许高存储器密度、高可靠性和低功耗的单晶体管存储器单元。电阻可变存储器装置可包含可基于存储元件(例如,具有可变电阻的电阻性存储器元件)的电阻状态存储数据的电阻性存储器单元。

5.存储器单元可布置成阵列,且阵列架构中的存储器单元可经编程为目标(例如,所要)状态。举例来说,电荷可置于快闪存储器单元的电荷存储结构(例如,浮动栅极)上或从其移除以将所述单元编程到特定数据状态。所述单元的电荷存储结构上的所存储电荷可指示所述单元的阈值电压(vt)。可通过感测快闪存储器单元的电荷存储结构上的所存储电荷(例如,vt)来确定所述单元的状态。

6.引入到代码中的错误和对所存储代码施加的威胁可能影响存储器装置的操作和/或存储在存储器装置的存储器单元中的数据。错误可通过噪声和/或在传输期间引入。威胁可包含例如来自黑客或其它恶意用户的威胁,包含有意的错误引入、中间人(mitm)攻击等等。此类威胁可能造成重大财务损失,和/或可能引起重大安全和/或安保问题。

附图说明

7.图1说明根据本公开的实施例的具有数个物理块的存储器阵列的一部分的图式。

8.图2a说明根据本公开的实施例的用于限定安全存储器阵列的一对寄存器的实例。

9.图2b说明根据本公开的实施例的包含所限定的安全存储器阵列的存储器阵列的

一部分的图式。

10.图3是根据本公开的实施例的包含主机和呈存储器装置形式的设备的计算系统的框图。

11.图4说明根据本公开的实施例的包含主机控制器和设备的实例系统的实例框图。

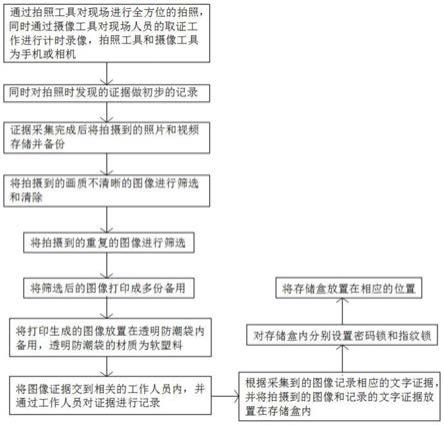

12.图5说明根据本公开的实施例的用于所执行代码中的错误识别的实例流程图。

13.图6是根据本公开的实施例的包含主机和存储器装置的实例系统的框图。

14.图7是根据本公开的实施例的用于确定数个参数的实例过程的框图。

15.图8是根据本公开的实施例的用于确定数个参数的实例过程的框图。

16.图9是根据本公开的实施例的验证证书的实例过程的框图。

17.图10是根据本公开的实施例的验证签名的实例过程的框图。

18.图11是根据本公开的实施例的实例存储器装置的框图。

具体实施方式

19.本公开包含用于所执行代码中的错误识别的设备、方法和系统。可对主机计算系统和/或对存储器装置执行错误校正操作。实施例包含存储器和电路系统,所述电路系统配置成通过将由存储器装置读取的数据与由不同存储器装置读取的错误校正码(ecc)进行比较来识别所执行代码(例如,读取数据)中的错误。将存储器装置的读取数据与不同存储器装置的ecc进行比较以确定读取数据中是否存在错误。

20.存储器装置可用于将数据存储在计算系统中,且可在与计算系统相关联的主机之间传送此数据。存储在存储器装置中的数据可以是对主机的操作重要的例程的代码。举例来说,主机装置可以是车辆,且例程可为动力系或车辆的操作。可使用存储器装置作为用于广泛范围的电子应用的非易失性存储器。

21.主机可以通信方式耦合到多个存储器装置。在一个实例中,存储器装置可包含存储在存储器装置的安全阵列中的数据。存储器装置可包含用于识别具有对应于由存储器装置读取的数据的错误校正码(ecc)的不同存储器装置的电路系统。电路系统可配置成执行完整性检查。完整性检查是指错误校正数据与读取数据的比较。举例来说,电路系统可配置成执行完整性检查以将ecc与存储器装置的读取数据进行比较,且响应于读取数据与ecc的比较而采取动作。当ecc指示校正时,由存储器装置读取的数据可包含类似错误,且可采取校正动作来校正错误。

22.可以多种方式将错误(例如,故障)引入到由存储器装置存储的数据(例如,存储在存储器单元中的数据)中。在传输期间,可无意地通过噪声和/或损害将错误引入到代码中。在一些情况下,错误可无意地引入到存储在存储器中的数据,从而引起存储器的操作的改变。还可通过威胁有意将错误引入到由存储器存储的数据。举例来说,黑客或其它恶意用户可引入错误以试图执行活动(例如,攻击),例如中间人(mitm)攻击,以出于恶意目的对存储器的操作和/或对其中存储的数据进行未经授权的改变。对引入到由存储器存储的数据的错误的威胁和/或后果的另一实例是黑客或其它恶意用户可试图跳过在本文中被称作例程的命令的一部分(例如,可执行代码的一部分),写入为检查和/或安全协议来认证命令。

23.在此攻击和/或错误期间,跳过和/或更改例程,但主机可接收例程已执行的指示。换言之,黑客和/或错误可篡改命令,且致使主机接收到例程已执行的指示。写入为检查命

令的真实性(认证组件、认证软件版本和/或更新、用户身份标识等)的重要例程可设计成在存储器装置的启动(例如引导)期间执行。黑客和/或引入的错误可改变(例如,掩码)外部输入以触发条件,从而可跳过写入为验证命令的真实性的例程。此例程的一个实例可以是写入为在执行软件服务(例如,从自动取款机发布货币和/或传送数据、执行软件等)之前检查支付的真实性的可执行代码的一部分。其它实例可包含用于在执行(计算机系统更新、安装软件等)之前验证软件许可证以认证软件为真的例程,主机装置的重要操作例程(例如,启动操作、动力系操作等)和/或用于检查系统组件的真实性和系统组件的配置(例如,过程工厂控制、汽车组件)的例程。

24.对错误的检测和校正可具有挑战性,因为对检测到的错误的校正可能产生额外(例如,新)错误。这可引起代码的所得架构(例如,例程)中的不可靠性且可影响存储器和存储在存储器中的代码的操作。许多存储器装置采用检测数据中的位错误的错误检查技术,例如ecc。ecc可与例如存储器块、存储器段或存储器扇区等单元群组相关联,并且可通过检测且可能地校正位错误来拯救读取失败。ecc码的实例包含汉明码(hamming code)、里德

‑

所罗门(reed

‑

solomon,rs)码、博斯

‑

乔赫里

‑

霍克文黑姆(bose

‑

chaudhuri

‑

hochquenghem,bch)码、循环冗余检查(crc)码、格雷(golay)码、里德

‑

密勒(reed

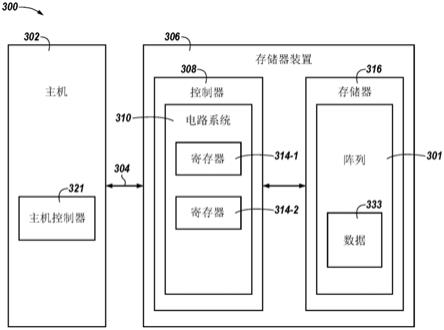

‑

muller)码、戈帕(goppa)码和丹尼斯顿(denniston)码等等。在一些方法中,通过包含耦合到存储器装置的电路系统的控制器对存储器装置执行这些和其它错误检查技术。如所提及,当识别并校正错误时,ecc可能无意地将新错误引入到重要例程(例如,命令)。

25.因而,为了确保识别出由ecc指示的错误,但当校正所识别错误时不引入新错误,可在检测到此类错误时生成警告。主机可与多个存储器装置相关联以检测这些错误。举例来说,主机装置可包含以通信方式耦合到多个存储器装置(例如,ecc存储器装置和无ecc的存储器装置)的主机控制器。多个存储器装置可分别具备数据(例如,命令和/或例程)和/或对应于所述数据的ecc。

26.在一些实例中,ecc和对应例程可在制造阶段期间安全地提供到存储器装置上,和/或使用交换的公钥/私钥安全地验证(本文进一步论述)。包含ecc的ecc存储器装置和包含对应数据(例如,例程)的存储器装置可由相应存储器装置并行地读取。可通过主机装置和/或与主机装置相关联的控制器来比较所执行的ecc和数据。当错误由在具有ecc的存储器装置上运行的ecc识别时,可将由数据存储器装置执行的数据识别为包含潜在错误。换言之,因为存储器装置中的数据对应于另一存储器装置中的ecc,由ecc识别的错误指示存储器装置的数据中的错误。在此情况下,为了避免通过实施自动校正引入的无意错误,可采取动作以警告主机和/或控制器已识别出存储器装置的数据中的错误。此时,可作出关于如何校正错误而不更改重要例程的架构的多个决策。

27.本公开的实施例可通过结合由以通信方式耦合到主机装置的不同存储器装置并行地执行的ecc与数据的比较而在重要例程中利用密码原语解决方案(例如,ecc和或所计算的摘要)来进行错误检测。此类解决方案可识别无意和/或有意引入到代码的错误。这可防止写入为避免财务损失、安全性协议和/或提供对主机装置的操作的安全检查的重要例程的不良操作。此外,当识别错误时,可通过避免自动校正来避免新错误的引入。替代地,可由主机和/或与主机相关联的存储器装置确定动作(例如,例程的警告、告警和/或中止)。

28.如本文中所使用,“一(a/an)”或“数个”可以指某事物中的一或多个,且“多个”可

以指此类事物中的两个或更多个。举例来说,存储器装置可以指一或多个存储器装置,且多个存储器装置可以指两个或更多个存储器装置。另外,如本文中所使用的指定符“m”、“p”、“r”、“b”、“s”和“n”,尤其相对于图式中的附图标记,指示如此指定的数个特定特征可与本公开的数个实施例包含在一起。标示之间的数目可相同或不同。

29.本文中的图遵循编号定则,其中第一一或多个数字对应于图号,且剩余的数字标识图式中的元件或组件。可通过使用类似数字来标识不同图之间的类似元件或组件。举例来说,101可表示图1中的元件“01”,且相似元件可在图2中表示为201。

30.图1说明根据本公开的实施例的具有数个物理块的存储器阵列101的一部分的图式。存储器阵列101可以是例如快闪存储器阵列,例如nand快闪存储器阵列。作为额外实例,存储器阵列101可以是电阻可变存储器阵列,尤其例如pcram、rram、mmram或自旋力矩传送(stt)阵列。然而,本公开的实施例不限于特定类型的存储器阵列。此外,存储器阵列101(例如,阵列101的子集或整个阵列201)可以是安全存储器阵列,如本文中将进一步描述。此外,虽然图1中未展示,但存储器阵列101可与和其操作相关联的各种外围电路系统一起位于特定半导体裸片上。

31.如图1所展示,存储器阵列101具有存储器单元的数个物理块107

‑

0(块0)、107

‑

1(块1)、

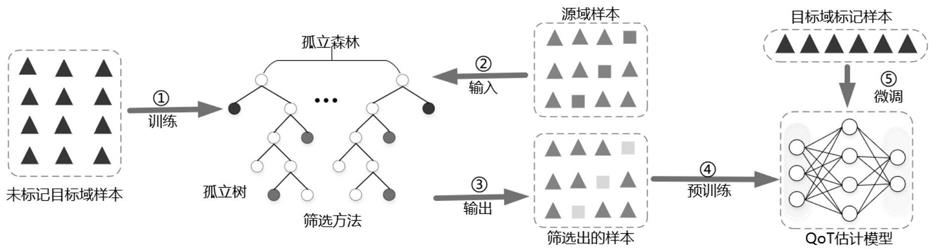

……

、107

‑

b(块b)。存储器单元可以是单层级单元和/或多层级单元,例如二层级单元、三层级单元(tlc)或四层级单元(qlc)。作为实例,存储器阵列101中的物理块的数目可以是128个块、512个块或1,024个块,但实施例不限于存储器阵列101中的二的特定幂或任何特定数目个物理块。

32.存储器单元平面中可包含数个存储器单元物理块(例如,块107

‑

0、107

‑

1、

……

、107

‑

b),且裸片上可包含数个存储器单元平面。举例来说,在图1所展示的实例中,每一物理块107

‑

0、107

‑

1、

……

、107

‑

b可以是单个裸片的部分。也就是说,图1中所说明的存储器阵列101的部分可以是存储器单元的裸片。

33.如图1所展示,每一物理块107

‑

0、107

‑

1、

……

、107

‑

b包含存储器单元的耦合到存取线(例如,字线)的数个物理行(例如,103

‑

0、103

‑

1、

……

、103

‑

r)。每一物理块中的行(例如,字线)的数目可以是32,但实施例不限于每物理块特定数目的行103

‑

0、103

‑

1、

……

、103

‑

r。此外,虽然图1中未展示,但存储器单元可耦合到感测线(例如,数据线和/或数字线)的列。

34.如所属领域的技术人员将了解,每一行103

‑

0、103

‑

1、

……

、103

‑

r可包含数个存储器单元页(例如,物理页)。物理页指代编程和/或感测的单元(例如,作为功能群组一起编程和/或感测的数个存储器单元)。在图1中所展示的实施例中,每一行103

‑

0、103

‑

1、

……

、103

‑

r包括存储器单元的一个物理页。然而,本公开的实施例不限于此。举例来说,在实施例中,每一行可包括存储器单元的多个物理页(例如,耦合到偶数编号的数据线的一或多个偶数存储器单元页,以及耦合到奇数编号的数据线的一或多个奇数存储器单元页)。另外,对于包含多层级单元的实施例,存储器单元的物理页可存储多个数据页(例如,逻辑页)(例如,上部数据页和下部数据页,其中物理页中的每一单元存储朝向上部数据页的一或多个位和朝向下部数据页的一或多个位)。

35.如图1所展示,存储器单元页可包括数个物理扇区105

‑

0、105

‑

1、

……

、105

‑

s(例如,存储器单元子集)。单元的每一物理扇区105

‑

0、105

‑

1、

……

、105

‑

s可存储数据的数个逻

辑扇区。另外,数据的每一逻辑扇区可对应于特定数据页的一部分。作为实例,存储在特定物理扇区中的数据的第一逻辑扇区可对应于与第一数据页对应的逻辑扇区,且存储在特定物理扇区中的数据的第二逻辑扇区可对应于第二数据页。每一物理扇区105

‑

0、105

‑

1、

……

、105

‑

s可存储系统和/或用户数据,和/或可包含开销数据,例如错误校正码(ecc)数据、逻辑块地址(lba)数据和元数据。

36.逻辑块寻址是主机可用以识别数据的逻辑扇区的方案。举例来说,每一逻辑扇区可对应于唯一逻辑块地址(lba)。另外,lba也可对应于(例如,动态地映射到)可指示存储器中的数据的逻辑扇区的物理方位的物理地址,例如物理块地址(pba)。数据的逻辑扇区可以是数据的字节数目(例如256字节、512字节、1,024字节或4,096字节)。然而,实施例不限于这些实例。

37.应注意,用于物理块107

‑

0、107

‑

1、

……

、107

‑

b、行103

‑

0、103

‑

1、

……

、103

‑

r、扇区105

‑

0、105

‑

1、

……

、105

‑

s和页的其它配置是可能的。举例来说,物理块107

‑

0、107

‑

1、

……

、107

‑

b的行103

‑

0、103

‑

1、

……

、103

‑

r可各自存储对应于单个逻辑扇区的数据,所述单个逻辑扇区可包含例如多于或少于512字节的数据。

38.图2a说明根据本公开的实施例的用于限定安全存储器阵列的一对寄存器214

‑

1和214

‑

2的实例,并且图2b说明根据本公开的实施例的包含使用寄存器214

‑

1和214

‑

2限定的安全存储器阵列的存储器阵列201的一部分的图。尽管实施例不限于此,且可使用一或多个寄存器和/或一或多个对寄存器。如图2b中所展示,以类似于结合图1所描述的存储器阵列101的方式,安全存储器阵列201可包含存储器单元的数个物理块207

‑

0、207

‑

1、

……

、207

‑

b,每一物理块包含具有数个存储器单元扇区的数个物理行203

‑

0、203

‑

1、

……

、203

‑

r。

39.如图2a中所展示,寄存器214

‑

1可以限定安全阵列的地址(例如,安全阵列的不同部分的地址),并且寄存器214

‑

2可以限定安全阵列的大小(例如,安全阵列的不同部分的大小)。由寄存器214

‑

1限定的安全阵列的地址可对应于例如安全阵列的起始点(例如,起始lba)(例如,安全阵列的不同部分的起始点),并且由寄存器214

‑

2限定的安全阵列的大小可对应于例如安全阵列的结束点(例如,结束lba)(例如,安全阵列的不同部分的结束点)。

40.举例来说,如图2a中所展示,寄存器214

‑

1和214

‑

2可限定n对值,其中每一相应对包括由寄存器214

‑

1限定的地址值(例如,addr)和由寄存器214

‑

2限定的大小值(例如,size)。举例来说,在图2a中所说明的实例中,pair0包括地址值addr0和大小值size0(例如,pair0=[addr0,size0]),pair1包括地址值addr1和大小值size1(例如,pair1=[addr1,size1])等,其中pair

n

包括地址值addr

n

和大小值size

n

(例如,pair

n

=[addr

n

,size

n

])。一对的地址值可以对应于安全阵列的一部分的起始点(例如,起始lba),并且所述对的地址值和大小值的总和可以对应于安全阵列的所述部分的结束点(例如,结束lba)。因而,整个安全阵列(例如,包括整个安全阵列的部分)可以由以下公式给出:[addr0,addr0 size0]∪[addr1,addr1 size1]∪

…

∪[addr

n

,addr

n

size

n

]。

[0041]

由寄存器214

‑

2限定的大小值是零的第一对可停止安全阵列的限定。举例来说,在图2a中所说明的实例中,如果pair2的大小值是零,那么安全阵列将由以下公式给出:[addr0,addr0 size0]∪[addr1,addr1 size1]。

[0042]

在图2b中说明由寄存器214

‑

1和214

‑

2限定的安全阵列的实例(例如,由寄存器214

‑

2限定的所有大小值均为非零)。举例来说,如图2b中所展示,与存储器阵列201的扇区

205

‑

0相关联的地址(例如lba)为addr0,与存储器阵列201的扇区205

‑

1相关联的地址为addr0 size0,与存储器阵列201的扇区205

‑

2相关联的地址为addr1,与存储器阵列201的扇区205

‑

3相关联的地址为addr1 size1,与存储器阵列201的扇区205

‑

4相关联的地址为addr

n

,并且与存储器阵列201的扇区205

‑

5相关联的地址为addr

n

size

n

。因而,安全阵列包括扇区(例如,存储在扇区中的数据)205

‑

0到205

‑

1、扇区205

‑

2到205

‑

3以及205

‑

4到205

‑

5。然而,存储器阵列201的位于扇区205

‑

0之前的扇区以及存储器阵列201的扇区205

‑

1到205

‑

2不是安全阵列的一部分(例如,安全阵列包括阵列201的子集)。

[0043]

图3是根据本公开的实施例的包含主机302和呈存储器装置306形式的设备的计算系统300的框图。如本文所使用,“设备”可以指但不限于多种结构或结构的组合中的任何一种,例如电路或电路系统、一或多个裸片、一或多个模块、一或多个装置或一或多个系统。此外,在实施例中,计算系统300可包含类似于存储器装置306的数个存储器装置。

[0044]

在图3中所说明的实施例中,存储器装置306可包含具有存储器阵列301的存储器316。存储器阵列301可类似于结合图1所描述的存储器阵列101和结合图2b所描述的存储器阵列201。此外,在实施例中,存储器阵列301(例如,阵列301的子集,或整个阵列301)可以是安全阵列(例如,存储器316的将保持受控制的区域)。

[0045]

图3说明一对寄存器314

‑

1和314

‑

2,但实施例不限于此,且可使用一或多个寄存器和/或一或多对寄存器。寄存器314

‑

1和314

‑

2可以是例如结合图2a所描述的寄存器214

‑

1和214

‑

2,并且安全存储器阵列301可以是例如结合图2b所描述的存储器阵列201。存储在存储器阵列301中的数据(例如,数据333)可包含敏感(例如,非用户)数据,例如待针对敏感应用(例如,例程)执行的装置固件和/或代码。在一些实例中,存储器装置306可包含对应于数据333的ecc,其中ecc和/或由存储器装置306计算的数据的摘要由存储器316以与图3所说明的数据333相同方式(此实施例结合图4论述)存储。

[0046]

在此类实施例中,所述对非易失性寄存器314

‑

1和314

‑

2可用于限定安全阵列以存储数据333(和/或ecc、对应数据和/或摘要)。举例来说,在图3中所说明的实施例中,电路系统310包含可用于限定安全阵列的寄存器314

‑

1和314

‑

2。举例来说,寄存器314

‑

1可限定安全阵列的地址(例如,数据的起始lba),并且寄存器314

‑

2可限定安全阵列的大小(例如,数据的结束lba)。使用此方法,数据333可由存储器装置306存储和保护。

[0047]

如图3中所说明,主机302可经由接口304耦合到存储器装置306。主机302和存储器装置306可在接口304上通信(例如,发送命令和/或数据)。主机302和/或存储器装置306可以是以下各项或为以下各项的部分:计算装置、膝上型计算机、个人计算机、数码相机、数字录制和重放装置、移动电话、pda、存储卡读取器、接口集线器或支持物联网(iot)的装置,例如支持汽车(例如,车辆和/或运输基础设施)iot的装置或支持医疗(例如,可植入和/或健康监测)iot的装置,以及其它主机系统,并且可包含存储器存取装置(例如,处理器)。所属领域的一般技术人员将理解,“处理器”可以是一或多个处理器,例如并行处理系统、数个协处理器等。

[0048]

接口304可呈标准化物理接口的形式。举例来说,当存储器装置306用于计算系统300中的信息存储时,接口304可为串行高级技术附件(sata)物理接口、外围组件互连高速(pcie)物理接口、通用串行总线(usb)物理接口,或小型计算机系统接口(scsi),以及其它物理连接器和/或接口。然而,大体来说,接口304可提供用于在存储器装置306与具有用于

接口304的兼容接收器的主机(例如,主机302)之间传递控制、地址、信息(例如,数据)和其它信号的接口。

[0049]

存储器装置306包含与主机302和存储器316(例如,存储器阵列301)通信的控制器308。举例来说,控制器308可发送对存储器阵列301执行操作的命令,所述操作包含感测(例如,读取)、编程(例如,写入)、移动和/或擦除数据的操作,以及其它操作。

[0050]

控制器308可与存储器316包含在同一物理装置(例如,同一裸片)上。替代地,控制器308可包含在以通信方式耦合到包含存储器316的物理装置的单独物理装置上。在实施例中,控制器308的组件可作为分布式控制器跨越多个物理装置散布(例如,一些组件与存储器在同一裸片上,且一些组件在不同的裸片、模块或板上)。

[0051]

主机302可包含与存储器装置306通信的主机控制器321。主机控制器321可包含在同一物理主机装置302上。替代地,主机控制器321可以是以通信方式耦合到存储器装置306和/或多个存储器装置(结合图4进一步论述)的单独物理装置。主机控制器321可经由接口304向存储器装置306发送命令。主机控制器321可与存储器装置306和/或存储器装置306上的控制器308通信以读取、写入和/或擦除数据,以及进行其它操作。此外,在实施例中,主机302可以是如本文所描述的具有iot通信能力的支持iot的装置。

[0052]

存储器装置306上的控制器308和/或主机302上的主机控制器321可包含控制电路系统和/或逻辑(例如,硬件和固件)。在实施例中,存储器装置306上的控制器308和/或主机控制器321可为耦合到包含物理接口的印刷电路板的专用集成电路(asic)。此外,存储器装置306、主机控制器321和/或主机302可包含易失性和/或非易失性存储器的缓冲器和数个寄存器(例如,寄存器314

‑

1和314

‑

2)。

[0053]

举例来说,如图3中所展示,存储器装置306可包含电路系统310。在图3中所说明的实施例中,电路系统310包含在控制器308中。然而,本公开的实施例不限于此。举例来说,在实施例中,电路系统310可包含在存储器316中(例如,在同一裸片上)(例如,而不是控制器308中)。电路系统310可包括例如硬件、固件和/或软件。

[0054]

计算系统300(例如,主机302和存储器装置306)可利用所执行代码中的错误识别来确定是否已在数据333中识别错误。举例来说,电路系统310可读取存储在存储器316的阵列301中的数据333。电路系统310可识别不同存储器,所述不同存储器可以包含对应于由电路系统310读取的数据333的ecc。如所提及,对引入到数据333的错误的自动校正可引入额外错误。存储器装置306可执行完整性检查以将ecc与由存储器装置306读取的数据333进行比较。存储器装置306可响应于存储器316的读取数据与ecc的比较而采取动作,其中比较指示ecc识别由存储器316读取的数据333中的错误。以此方式,存储器装置306、主机控制器321和/或主机302可确定如何校正由ecc识别的错误。

[0055]

举例来说,电路系统310可配置成确定由ecc识别的错误是否影响与由存储器316读取的数据333相关联的主机装置302的操作。举例来说,数据333可以是用于与呈车辆形式的主机302的动力系操作相关的例程的代码。在制造和/或另一安全个例期间,可将动力系例程作为数据333提供到存储器316,且作为ecc提供到不同存储器。存储器装置306可以是执行动力系例程(例如,数据333)的引导存储器装置。

[0056]

主机控制器321、电路系统310和/或存储器316可响应于存储器316的启动过程和/或执行数据333的其它指示而执行完整性检查。完整性检查可包含由主机控制器321、电路

系统310和/或存储器316将由包含在不同存储器装置上的不同存储器读取的ecc与由存储器316读取的数据333并行地进行比较。完整性检查可包含由电路310和/或主机302确定应用于由ecc识别的错误的校正将额外错误引入到ecc。换言之,由ecc对所识别错误的自动校正可能已经将新的错误引入到ecc,并且对数据333应用类似的校正可能会引入额外错误数据333。其它错误的引入可能导致例程被跳过、更改和/或其它操作问题。基于完整性检查,主机302、主机控制器321和/或电路310可响应于由ecc识别的错误而采取动作以避免校正对应于存储器的读取数据333的错误,和/或可确定替代的校正方法。

[0057]

图4说明根据本公开的实施例的包含主机控制器421和实例存储器装置406

‑

1和406

‑

2的实例系统409的框图。主机(例如,图3的主机302)可包含主机控制器421,其中主机控制器421可以通信方式耦合到至少一个存储器装置(例如,存储器装置406

‑

1)和至少一个其它存储器装置(例如,存储器装置406

‑

2)。举例来说,图4中所说明的系统409包含主机控制器421,其经由接口404

‑

1以通信方式耦合到具有存储器416

‑

1和阵列401

‑

1的存储器装置406

‑

1。主机控制器421说明为经由接口404

‑

2以通信方式耦合到具有存储器416

‑

2和阵列401

‑

2的另一存储器装置406

‑

2。

[0058]

存储器装置406

‑

1可具备数据433

‑

1、433

‑

2和433

‑

n(例如,图3的数据333)。数据433

‑

1、433

‑

2和433

‑

n可以是对应于例程的代码流。可使用与主机控制器421相关联的主机与存储器装置406

‑

1之间的公钥/私钥交换将用于例程的数据433

‑

1、433

‑

2和433

‑

n编码安全地提供到存储器装置406

‑

1上。ecc 432

‑

1、432

‑

2和432

‑

m可对应于数据433

‑

1、433

‑

2和433

‑

n,且使用与主机控制器421相关联的主机与存储器装置406

‑

1之间的公钥/私钥交换安全地提供到存储器装置406

‑

2上。将结合图6到11进一步论述对公钥和私钥的生成和验证。

[0059]

在一些实例中,构成用于例程的代码流的数据433

‑

1、433

‑

2和433

‑

n可以是固定的数据单元(例如,5到8个双字,但实例不限于此)。例程可以是对对应于主机控制器421的主机的操作可能重要的运行时可执行代码。为了检测数据433

‑

1、433

‑

2、433

‑

n中的错误且确定校正错误的动作,主机控制器421可与不同存储器装置406

‑

2相关联,其中不同存储器装置406

‑

2具备例程(例如,用于在数据433

‑

1、433

‑

2和433

‑

n中编码的例程的代码流)和错误校正/检测能力。

[0060]

举例来说,存储器装置406

‑

2可包含对应于例程的ecc 432

‑

1、432

‑

2、432

‑

m和/或对应于例程的摘要435

‑

1、435

‑

2、435

‑

p。ecc 432

‑

1、432

‑

2、432

‑

m可包含对应于存储器装置406

‑

1的数据433

‑

1、433

‑

2和433

‑

n的代码,其中ecc是与其级联的位奇偶校验。举例来说,ecc 432

‑

1可包含与错误校正部分级联的数据433

‑

1的代码,ecc 432

‑

2可包含与错误校正部分级联的数据433

‑

2的代码,且ecc 432

‑

m可包含与错误校正部分级联的数据433

‑

n的代码。

[0061]

摘要435

‑

1、435

‑

2和435

‑

p是由电路系统(例如,图3的电路系统310)应用于用于例程的代码(例如,数据433

‑

1、433

‑

2、433

‑

n)的散列函数的乘积。举例来说,摘要435

‑

1、435

‑

2和435

‑

p可以是由对应数据(例如,数据433

‑

1、433

‑

2、433

‑

n)产生的加密原语(例如,散列),其中对数据的改变可产生不同摘要。换言之,当数据433

‑

1中存在错误时,由数据433

‑

1的电路系统计算的摘要将改变。

[0062]

举例来说,摘要435

‑

1可以是数据433

‑

1的散列,摘要435

‑

2可以是数据433

‑

2的散列,且摘要435

‑

p可以是数据433

‑

n的散列。单独或一起使用的ecc(432

‑

1、432

‑

2、432

‑

m)和

摘要(435

‑

1、435

‑

2、435

‑

p)可由主机(例如,图3的主机302)、主机控制器421和/或电路系统(例如,图3的电路系统310)使用,以确定例程的代码(例如,数据433

‑

1、433

‑

2和433

‑

n)在由存储器装置406

‑

1执行的完整性。

[0063]

数据433

‑

1、433

‑

2、433

‑

n可与ecc 432

‑

1、432

‑

2、432

‑

m和/或摘要435

‑

1、435

‑

2、435

‑

p并行地执行以识别所执行代码(例如,数据433

‑

1、433

‑

2、433

‑

n)中的错误。具体来说,存储器装置406

‑

2可包含电路系统(例如,图3的电路系统310),所述电路系统配置成读取存储在存储器416

‑

2的阵列401

‑

2中的ecc(例如,432

‑

1、432

‑

2和432

‑

m),且识别具有对应于存储器416

‑

2的ecc(例如,432

‑

1、432

‑

2和432m)的读取数据433

‑

1、433

‑

2、433

‑

n的不同存储器装置406

‑

1。存储器装置406

‑

2的电路系统和/或主机控制器421可执行完整性检查以将ecc(例如,432

‑

1、432

‑

2和432

‑

m)与不同存储器装置406

‑

1的读取数据433

‑

1、433

‑

2和433

‑

n进行比较。完整性检查可基于与ecc 432

‑

1、432

‑

2和432

‑

m的比较而确定和/或监测读取数据433

‑

1、433

‑

2和433

‑

n的错误。

[0064]

响应于读取数据433

‑

1、433

‑

2、433

‑

n与ecc 432

‑

1、432

‑

2和432

‑

m的比较,主机控制器421和/或电路系统可采取动作,其中所述比较指示ecc识别存储器装置406

‑

1的读取数据433

‑

1、433

‑

2和/或433

‑

n中的错误。因为对错误的校正可将新错误引入到待执行的数据中,所以主机控制器421和/或与存储器装置406

‑

1相关联的电路系统可采取动作以避免校正由ecc 432

‑

1、432

‑

2和432

‑

m识别的错误。替代地和/或另外,主机控制器421和/或与存储器装置406

‑

1相关联的电路系统可确定错误和/或对错误的校正可如何影响由数据433

‑

1、433

‑

2和433

‑

n编码的例程,且确定校正通过比较ecc 432

‑

1、432

‑

2和432

‑

m与数据433

‑

1、433

‑

2、433

‑

n识别的错误。以此方式,可监测和/或识别由校正动作引入的无意错误。

[0065]

图5说明根据本公开的实施例的用于所执行代码中的错误识别的实例流程图。在522处,主机装置(例如,图3的主机302)可建立至少一个存储器装置以执行用于主机装置的操作的例程。举例来说,在541处,主机装置可限定例程。主机装置可通过交换公钥/私钥而安全地与一或多个存储器装置(例如,图4的存储器装置406

‑

1和406

‑

2)通信以交换加密数据(例如,数据433

‑

1、433

‑

2、433

‑

n)以对例程进行编码。主机装置和/或与存储器装置相关联的电路系统(例如,图3的电路系统310)可为至少一个存储器装置提供ecc(例如,ecc 432

‑

1、432

‑

2、432

‑

m),和/或可基于ecc和/或数据计算摘要(例如,图4的435

‑

1、435

‑

2和435

‑

p)。

[0066]

如所提及,主机装置可以是车辆,且主机控制器可包含在车辆中或车辆外部。主机控制器可与多个存储器装置通信,存储器装置可存储对车辆(例如,主机装置)的重要例程(例如,动力系操作)进行编码的数据串。存储器装置可具备数据和对应ecc,和/或可在安全位置和/或安全时间处计算摘要。举例来说,存储器装置可在主机和/或主机控制器的制造期间具备数据、ecc和摘要。

[0067]

主机装置可包含主机控制器(例如,图4的主机控制器421),其以通信方式耦合到存储器装置以识别所执行代码中的错误。在542处,主机控制器和/或相应存储器装置的电路系统可并行地执行数据流和对应ecc。举例来说,第一存储器装置可以是具有存储器和电路系统且与主机控制器通信的引导存储器装置。第二存储器装置可以是具有存储器和电路系统且还与主机控制器通信的错误校正存储器装置。系统(例如,图4的系统409)可启动,且第一存储器装置可与读取对应于例程的ecc的第二存储器装置并行地读取例程的数据流。

第一存储器装置可经由电路系统(例如,图3的电路系统310)将读取数据传输到主机控制器。第二存储器装置可经由电路系统(例如,图3的电路系统310)将读取ecc传输到主机控制器。

[0068]

在543处,主机控制器可接收从第一存储器装置的电路系统传输的所执行(例如,读取)数据和对应于来自第二存储器装置的电路系统的数据的ecc。在一些实例中,第二存储器装置的电路系统可配置成传输对应于由第一存储器装置传输的数据流的所计算的摘要(例如,所计算的散列)。摘要可由第二存储器装置的电路系统单独地或与ecc数据一起传输,使得主机装置可执行完整性检查。

[0069]

举例来说,在544处,主机控制器可通过将接收到的ecc和/或对应于数据(且由第二存储器装置的电路系统计算)的摘要与来自第一存储器装置的读取数据进行比较来执行完整性检查。如果第二存储器装置的ecc与第一存储器装置的读取数据不匹配(在545处为“否”),那么读取数据中可存在错误。换句话说,ecc可自动校正一或多个错误,由此不再对应于第一存储器装置的数据。在此实例中,在547处,主机控制器和/或与第一存储器装置相关联的电路系统可响应于ecc识别第一存储器装置的读取数据中的错误的比较而采取动作。

[0070]

在一些实例中,将第一存储器装置的读取数据与由第二存储器装置提供的ecc进行比较包含将对应于数据的散列函数与对应于ecc的摘要进行比较。所计算的摘要可能不匹配第一存储器装置的预期读取数据(例如,或预期读取数据的散列)。每一摘要(例如,图4的435

‑

1、435

‑

2、435

‑

p)可基于数据(例如,图4的433

‑

1、433

‑

2、433

‑

n)计算,其中对数据的任何改变可改变摘要的值。当在数据中发生错误时,由第二存储器装置输出的摘要可改变,从而指示错误。在544处,主机控制器和/或第一存储器装置的电路系统可将接收到的摘要与读取数据进行比较。如果摘要和读取数据不匹配(例如,在546处为“否”),那么错误已发生,且主机控制器和/或存储器装置的电路系统可采取547处的动作。

[0071]

举例来说,第一和/或第二存储器装置的电路系统可确定例程中发生错误的位置,且确定错误可对例程具有何种影响。第一和/或第二存储器装置的电路系统可基于ecc和/或摘要对错误的识别而中止(例如,暂停)主机装置的操作。替代地和/或另外,主机控制器可基于由ecc和/或摘要进行的识别来校正读取数据中的错误。在另一实例中,采取的动作可以是指示错误的警告,其中警告由第一存储器装置和/或第二存储器装置的电路系统产生且传送到主机装置。

[0072]

在在544处的完整性检查比较期间期间,主机控制器和/或第一存储器装置和/或第二存储器装置的电路系统可确定从第一存储器装置接收到的读取数据与第二存储器装置的ecc和/或摘要匹配(在548处为“是”)。匹配读取数据与ecc和/或摘要指示来自第一存储器装置的读取数据中不存在错误。在此实例中,在549处,第一和/或第二存储器装置的电路系统可继续进行由数据编码例程的操作。

[0073]

图6是根据本公开的实施例的包含存储器装置606和主机602的实例系统的框图。存储器装置606和主机602可分别为例如结合图3描述的主机302和存储器装置306。

[0074]

计算装置可在使用层分阶段引导,其中每一层认证并加载后续层并且在每一层提供越来越复杂的运行时间服务。一层可被前一层服务并且服务后续层,进而创建构建在下部层上并且服务高阶层的层的互连网络。如图6中所说明,层0(“l

0”)651和层1(“l

1”)653在

存储器装置606内。层0 651可以向层1 653提供固件衍生秘密(fds)密钥652。fds密钥652可以描述层1 653的代码的身份标识和其它安全相关数据。在实例中,特定协议(例如稳固物联网(riot)核心协议)可使用fds 652来验证其加载的层1 653的代码。在实例中,特定协议可包含装置识别组合引擎(dice)和/或riot核心协议。作为实例,fds可包含层1固件图像本身、以密码方式识别经授权层1固件的清单、在安全引导实施方案的上下文中签名的固件的固件版本号,和/或装置的安全关键配置设置。装置秘密658可用于创建fds 652并存储在与存储器装置606相关联的存储器中。

[0075]

如箭头654所说明,存储器装置可以将数据传输到主机602。传输的数据可包含公开的外部识别、证书(例如,外部标识证书)和/或外部公钥。主机602的层2(“l

2”)655可接收所传输数据,且在操作系统(“os”)657的操作中且在第一应用659

‑

1和第二应用659

‑

2上执行所述数据。

[0076]

在实例操作中,存储器装置606可以读取装置秘密658,将层1 653的身份标识散列,并且执行计算,所述计算包含:

[0077]

k

l1

=kdf[fs(s),散列(“不变的信息”)]

[0078]

其中k

l1

是外部公钥,kdf(例如,美国国家标准与技术研究所(nist)特定公开800

‑

108中定义的kdf)是密钥导出函数(例如,hmac

‑

sha256),且fs(s)是装置秘密658。可通过执行以下计算确定fds 652:

[0079]

fds=hmac

‑

sha256[fs(s),sha256(“不变的信息”)]

[0080]

如箭头656所说明,主机602可以将数据传输到存储器装置606。

[0081]

图7是根据本公开的实施例的用于确定数个参数的实例过程的框图。图7是确定包含外部公共识别、外部证书和外部公钥的参数的实例,如箭头754所示,所述参数随后被发送到主机装置(例如,图6中的602)的层2(例如,层2 655)。图7中的层0(“l

0”)751对应于图6中的层0 651,且同样地fds 752对应于fds 652,层1 753对应于层1653,并且箭头754和756分别对应于箭头654和656。

[0082]

将来自层0 751的fds 752发送到层1 753,并由非对称id生成器761使用以生成公共识别(“id

lk public”)765和私有识别767。在缩写的“id

lk public”中,“lk”指示层k(在此实例中为层1),并且“public”指示识别是公开共享的。公共识别765通过向右侧延伸且延伸到存储器装置的层1 753之外的箭头而被说明为共享。生成的私有识别767用作输入到加密器773中的密钥。加密器773可以是用于对数据进行加密的任何处理器、计算装置等。

[0083]

存储器装置的层1 753可包含非对称密钥生成器763。在至少一个实例中,随机数生成器(rnd)736可以可选地将随机数输入到非对称密钥生成器763中。非对称密钥生成器763可生成与存储器装置(例如图6中的存储器装置606)相关联的公钥(“k

lk public”)769(被称为外部公钥)和私钥(“k

lk private”)771(被称为外部私钥)。外部公钥769可为进入加密器773的输入(作为“数据”)。加密器773可使用外部私有识别767和外部公钥769的输入生成结果k'775。外部私钥771和结果k'775可以输入到额外加密器777,从而产生输出k”779。输出k”779是传输到层2(图6的655)的外部证书(“id

l1

证书”)781。外部证书781可提供验证和/或认证从装置发送的数据的来源的能力。作为实例,通过验证证书,从存储器装置发送的数据可与存储器装置的身份标识相关联,如将结合图9进一步描述。此外,外部公钥(“k

l1 public key”)783可传输到层2。因此,存储器装置的公共标识765、证书781和外部公钥

783可传输到主机装置的层2。

[0084]

图8是根据本公开的实施例的用于确定数个参数的实例过程的框图。图8示说明生成装置识别(“id

l2

公共”)866、装置证书(“id

l2

证书”)882和装置公钥(“k

l2 public key”)884的主机(例如,图6中的主机602)的层2 855。

[0085]

如图7所描述,从存储器装置的层1传输到主机的层2 855的外部公钥(“k

l1 public key”)883由主机的非对称id生成器862使用以生成主机的公共识别(“id

lk public”)866和私有识别868。在缩写的“id

lk public”中,“lk”指示层k(在此实例中为层2),并且“public”指示识别是公开共享的。公共识别866通过向右侧延伸且延伸到层2 855之外的箭头而被说明为共享。生成的私有识别868用作输入到加密器874中的密钥。

[0086]

如图8中所展示,证书验证器824使用外部证书881和外部识别865以及外部公钥883。证书验证器824可验证存储器装置(例如,存储器装置606)接收的外部证书881,并响应于外部证书881经过验证或未经验证而确定是接受还是舍弃从存储器装置接收的数据。结合图9描述验证外部证书881的进一步细节。

[0087]

主机的层2 855可包含非对称密钥生成器864。在至少一个实例中,随机数生成器(rnd)838可以可选地将随机数输入到非对称密钥生成器864中。非对称密钥生成器864可生成与主机装置(例如,图6中的主机602)相关联的公钥(“k

lk public”)870(被称为装置公钥)和私钥(“k

lk private”)872(被称为装置私钥)。装置870可为进入加密器874的输入(作为“数据”)。加密器874可使用装置私有识别868和装置公钥870的输入来生成结果k'876。装置私钥872和结果k'876可输入到额外加密器878,从而产生输出k”880。输出k”880是传输回层1(图6的653)的装置证书(“id

l2

证书”)882。装置证书882可提供验证和/或认证从装置发送的数据的来源的能力。作为实例,通过验证证书,从主机发送的数据可与主机的身份标识相关联,如将结合图9进一步描述。此外,装置公钥(“k

l2 public key”)884可以传输到层1。因此,可将主机的公共识别866、证书882和装置公钥884传输到存储器装置的层1。

[0088]

在实例中,响应于存储器装置从主机接收公钥,存储器装置可使用装置公钥对待发送到主机的数据进行加密。反之亦然,主机可使用外部公钥对待发送到存储器装置的数据进行加密。响应于主机接收使用装置公钥加密的数据,主机可使用其自身的装置私钥对数据进行解密。同样地,响应于存储器装置接收使用外部公钥加密的数据,存储器装置可使用其自身的外部私钥对数据进行解密。由于装置私钥不与主机外部的另一装置共享,并且外部私钥不与存储器装置外部的另一装置共享,因此发送到主机和存储器装置的数据保持安全。

[0089]

图9是根据本公开的实施例的验证证书的实例过程的框图。在图9的所说明的实例中,从存储器装置(例如,从图6中的存储器装置606的层1 653)提供公钥983、证书981和公共识别965。证书981和外部公钥983的数据可用作进入解密器985的输入。解密器985可以是用于对数据进行解密的任何处理器、计算装置等。证书981和外部公钥983的解密结果可连同公共识别一起用作进入次级解密器987的输入,从而产生输出。如在989处所说明,外部公钥983和来自解密器987的输出可指示证书是否通过比较而得到验证,从而产生作为输出的是或否991。响应于证书经过验证,可接受、解密和/或处理从已验证装置接收的数据。响应于所述证书未被验证,从已验证装置接收的数据可被舍弃、去除和/或忽略。以此方式,可检测和避免发送不法数据的不法装置。作为实例,可识别发送待处理的数据的黑客且不处理

黑客数据。

[0090]

图10是根据本公开的实施例的验证签名的实例过程的框图。在装置正在发送可被验证以避免后续否认的数据的个例中,可生成签名且与数据一起发送。作为实例,第一装置可作出对第二装置的请求,且一旦第二装置执行所述请求,第一装置就可指示第一装置从未作出此类请求。抗否定方法,例如使用签名,可避免第一装置的否定,且确保第二装置可在无后续困难的情况下执行所请求的任务。

[0091]

存储器装置1006(例如,图3中的存储器装置306)可将数据1090发送到主机(例如,图3中的主机302)。在1094处,存储器装置1006可使用装置私钥1071生成签名1096。签名1096可传输到主机1002。主机1002可在1098处使用先前所接收的数据1092和外部公钥1069来验证签名。以此方式,使用私钥生成签名且使用公钥验证签名。以此方式,用于生成唯一签名的私钥可保持对发送签名的装置私用,同时允许接收装置能够使用发送装置的公钥对签名进行解密以用于验证。这与数据的加密/解密形成对比,所述数据由发送装置使用接收装置的公钥加密且由接收装置使用接收器的私钥解密。在至少一个实例中,装置可通过使用内部密码术过程(例如,椭圆曲线数字签名(ecdsa)或类似过程)来验证数字签名。

[0092]

图11是根据本公开的实施例的实例存储器装置1106的框图。存储器装置1106可以是例如先前结合图3所描述的存储器装置306。

[0093]

如图11中所展示,存储器装置1106可包含数个存储器阵列1101

‑

1到1101

‑

7。存储器阵列1101

‑

1到1101

‑

7可以类似于先前结合图1所描述的存储器阵列101。此外,在图11所说明的实例中,存储器阵列1101

‑

3是安全阵列,存储器阵列1101

‑

6的子集1111包括安全阵列,并且存储器阵列1101

‑

7的子集1113和1115包括安全阵列。子集1111、1113和1115各自可包含例如4千字节的数据。然而,本公开的实施例不限于存储器阵列或安全阵列的特定数目或布置。

[0094]

如图11中所展示,存储器装置1106可包含修复(例如,恢复)块1117。修复块1117可在存储器装置1106的操作期间可能发生的错误(例如,不匹配)的情况下用作数据源。修复块1117可位于可由主机寻址的存储器装置1106的区域之外。

[0095]

如图11中所展示,存储器装置1106可包含串行外围接口(spi)1104和控制器1108。存储器装置1106可使用spi 1104和控制器1108与主机和存储器阵列1101

‑

1到1101

‑

7通信,如本文中先前所描述(例如,结合图3)。

[0096]

如图11中所展示,存储器装置1106可包含用于管理存储器装置1106的安全性的安全寄存器1119。举例来说,安全寄存器1119可配置应用控制器,且与应用控制器进行外部通信。此外,安全寄存器1119可以通过认证命令进行修改。

[0097]

如图11中所展示,存储器装置1106可包含密钥1121。举例来说,存储器装置1106可包含八个不同的槽来存储密钥,例如根密钥、dice

‑

riot密钥和/或其它外部会话密钥。

[0098]

如图11中所展示,存储器装置1106可包含电子可擦除可编程只读存储器(eeprom)1123。eeprom 1123可提供主机可用的安全非易失性区域,其中可擦除和编程各个字节的数据。

[0099]

如图11中所展示,存储器装置1106可包含计数器(例如,单调计数器)1125。计数器1125可用作从主机接收和/或发送到主机的命令(例如,签署命令集或序列)的防重放机制(例如,新鲜度生成器)。举例来说,存储器装置1106可包含六个不同的单调计数器,其中两

个可由存储器装置1106用于认证命令,并且其中四个可由主机使用。

[0100]

如图11中所展示,存储器装置1106可包含sha

‑

256密码散列函数1127和/或hmac

‑

sha256密码散列函数1129。存储器装置1106可使用sha

‑

256和/或hmac

‑

sha256密码散列函数1127和1129来生成密码散列,例如,如本文中先前结合图3所描述的更新220的密码散列,和/或如本文中先前描述的用于验证存储在存储器阵列1101

‑

1到1101

‑

7中的数据的黄金散列。此外,存储器装置1106可以支持dice

‑

riot1131的l0和l1。

[0101]

尽管已在本文中说明并描述了具体实施例,但所属领域的一般技术人员应了解,经计算以实现相同结果的布置可取代所展示的具体实施例。本公开意图涵盖本公开的数个实施例的修改或变化。应理解,以上描述是以说明性方式而非限制性方式进行的。在查阅以上描述后,以上实施例和本文未具体描述的其它实施例的组合对于所属领域的一般技术人员来说将是显而易见的。本公开的数个实施例的范围包含其中使用上述结构和方法的其它应用。因此,本公开的数个实施例的范围应当参考所附权利要求书连同此类权利要求所授权的等效物的完整范围来确定。

[0102]

在前述具体实施方式中,出于简化本公开的目的而将一些特征一起分组在单个实施例中。本公开的这一方法不应被理解为反映本公开的所公开实施例必须使用比每一权利要求中明确陈述的特征更多的特征的意图。实际上,如所附权利要求书所反映,本发明主题在于单个所公开实施例的不到全部的特征。因此,所附权利要求书特此并入于具体实施方式中,其中每一权利要求就其自身而言作为单独实施例。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。