1.本发明涉及一种电子装置,特别涉及一种具有相位延迟元件的电子装置。

背景技术:

2.随着电子产品的蓬勃发展,消费者对电子产品的品质、功能及价格抱有很高的期望,例如朝高解析度的电子产品开发。然而电子装置仍未在各个方面皆符合期待,例如,不同视角下的暗态明显漏光或面板亮度不均。因此,发展出能够进一步改善电子装置品质或效能的结构设计仍为目前业界致力研究的课题之一。

技术实现要素:

3.根据本发明一些实施例,提供一种电子装置,其特征在于,包含第一相位延迟元件、第二相位延迟元件以及液晶层,第二相位延迟元件设置于第一相位延迟元件上,液晶层设置于第一相位延迟元件与第二相位延迟元件之间,且液晶层包含手性剂,手性剂的节距介于7微米至25微米之间。第一相位延迟元件具有第一平面内光延迟值及第一平面外光延迟值,第二相位延迟元件具有第二平面内光延迟值及第二平面外光延迟值,第一平面内光延迟值及第二平面内光延迟值介于20纳米至70纳米之间,且第一平面外光延迟值及第二平面外光延迟值介于170纳米至210纳米之间。

附图说明

4.为让本发明的上述目的、特征和优点能更明显易懂,以下结合附图对本发明的具体实施方式作详细说明,其中:

5.图1显示根据本发明一些实施例中,电子装置的剖面结构示意图;

6.图2显示根据本发明一些实施例中,电子装置的剖面结构示意图;

7.图3显示根据本发明一些实施例中,电子装置的剖面结构示意图;

8.图4显示根据本发明一些实施例中,电子装置的剖面结构示意图;

9.图5显示根据本发明一些实施例中,电子装置的剖面结构示意图;

10.图6显示根据本发明一些实施例中,电子装置的光学分析结果图;

11.图7显示根据本发明一些实施例中,电子装置的剖面结构示意图;

12.图8显示根据本发明一些实施例中,电子装置的子像素区域的上视结构示意图;

13.图9显示根据本发明一些实施例中,电子装置的子像素区域的上视结构示意图;

14.图10显示根据本发明一些实施例中,电子装置的剖面结构示意图。

15.符号说明

16.10、20、30、40、50、60、70 电子装置;

17.100 第一相位延迟元件;

18.101 第一基板;

19.101s 第一基底;

20.101x 电路层;

21.103 相位延迟层;

22.103a 第一相位延迟层;

23.103b 第二相位延迟层;

24.111 第一电极层;

25.111a 主部;

26.111b 分支部;

27.113 第一配向层;

28.200 第二相位延迟元件;

29.201 第二基板;

30.201s 第二基底;

31.201x 彩色滤光层;

32.203 相位延迟层;

33.203a 第三相位延迟层;

34.203b 第四相位延迟层;

35.211 第二电极层;

36.213 第二配向层;

37.300 液晶层;

38.402a 第一偏光层;

39.402b 第二偏光层;

40.a-a

’ꢀ

截线;

41.o

1 第一开口;

42.o

2 第二开口;

43.pn 面板;

44.p1 第一部分;

45.p2 第二部分;

46.p3 第三部分;

47.p4 第四部分;

48.sp 子像素区域;

49.θ 夹角;

50.方位角;

51.θ

1 第一夹角;

52.θ

2 第二夹角;

53.θ

3 第三夹角;

54.θ

4 第三夹角;

55.θ

t 夹角。

具体实施方式

56.以下针对本发明实施例的电子装置作详细说明。应了解的是,以下的叙述提供许

多不同的实施例,用以实施本发明一些实施例的不同样态。以下所述特定的元件及排列方式仅为简单清楚描述本发明一些实施例。当然,这些仅用以举例而非本发明的限定。此外,在不同实施例中可能使用类似和/或对应的标号标示类似和/或对应的元件,以清楚描述本发明。然而,这些类似和/或对应的标号的使用仅为了简单清楚地叙述本发明一些实施例,不代表所讨论的不同实施例和/或结构之间具有任何关联性。

57.透过参考以下的详细描述并同时结合附图可以理解本发明,须注意的是,为了使读者能容易了解及附图的简洁,本发明中的多张附图只绘出电子装置的一部分,且附图中的特定元件并非依照实际比例绘图。此外,图中各元件的数量及尺寸仅作为示意,并非用来限制本发明的范围。

58.应理解的是,附图的元件或装置可以所属技术领域的技术人员所熟知的各种形式存在。此外实施例中可能使用相对性用语,例如「较低」或「底部」或「较高」或「顶部」,以描述附图的一个元件对于另一元件的相对关系。可理解的是,如果将附图的装置翻转使其上下颠倒,则所叙述在「较低」侧的元件将会成为在「较高」侧的元件。本发明实施例可配合附图一并理解,本发明的附图亦被视为发明说明的一部分。再者,当述及一第一材料层位于一第二材料层上或之上时,包括第一材料层与第二材料层直接接触的情形,或者,其间亦可能间隔有一或更多其它材料层的情形,在此情形中,第一材料层与第二材料层之间可能不直接接触。

59.本发明通篇说明书与后附的权利要求中会使用某些词汇来指称特定元件。本领域技术人员应理解,电子设备制造商可能会以不同的名称来指称相同的元件。本文并不意在区分那些功能相同但名称不同的元件。在下文说明书与权利要求书中,「包括」、「含有」、「具有」等词为开放式词语,因此其应被解释为「含有但不限定为

…

」之意。因此,当本发明的描述中使用术语「包括」、「含有」和/或「具有」时,其指定了相应的特征、区域、步骤、操作和/或构件的存在,但不排除一个或多个相应的特征、区域、步骤、操作和/或构件的存在。

60.本文中所提到的方向用语,例如:「上」、「下」、「前」、「后」、「左」、「右」等,仅是参考附图的方向。因此,使用的方向用语是用来说明,而并非用来限制本发明。在附图中,各附图示出的是特定实施例中所使用的方法、结构和/或材料的通常性特征。然而,这些附图不应被解释为界定或限制由这些实施例所涵盖的范围或性质。举例来说,为了清楚起见,各膜层、区域和/或结构的相对尺寸、厚度及位置可能缩小或放大。

61.当相应的构件(例如膜层或区域)被称为「在另一个构件上」时,它可以直接在另一个构件上,或者两者之间可存在有其他构件。另一方面,当构件被称为「直接在另一个构件上」时,则两者之间不存在任何构件。另外,当一构件被称为「在另一个构件上」时,两者在俯视方向上有上下关系,而此构件可在另一个构件的上方或下方,而此上下关系取决于装置的取向(orientation)。

62.此外,应理解的是,虽然在此可使用用语「第一」、「第二」、「第三」等来叙述各种元件、组件、或部分,这些元件、组件或部分不应被这些用语限定。这些用语仅是用来区别不同的元件、组件、区域、层或部分。因此,以下讨论的一第一元件、组件、区域、层或部分可在不偏离本发明的启示的情况下被称为一第二元件、组件、区域、层或部分。

63.于文中,「约」、「实质上」的用语通常表示在一给定值或范围的10%内,或5%内、或3%之内、或2%之内、或1%之内、或0.5%之内。在此给定的数量为大约的数量,亦即在没有

特定说明「约」、「实质上」的情况下,仍可隐含「约」、「实质上」的含义。此外,用语「范围介于第一数值及第二数值之间」表示所述范围包含第一数值、第二数值以及它们之间的其它数值。

64.应理解的是,以下所举实施例可以在不脱离本发明的精神下,可将数个不同实施例中的特征进行替换、重组、混合以完成其他实施例。各实施例间特征只要不违背发明精神或相冲突,均可任意混合搭配使用。

65.于本发明中,厚度、长度与宽度的测量方式可以是采用光学显微镜测量而得,厚度则可以由电子显微镜中的剖面影像测量而得,但不以此为限。另外,任两个用来比较的数值或方向,可存在着一定的误差。若第一值等于第二值,其隐含着第一值与第二值之间可存在着约10%的误差;若第一方向垂直于第二方向,则第一方向与第二方向之间的角度可介于80度至100度之间;若第一方向平行于第二方向,则第一方向与第二方向之间的角度可介于0度至10度之间。

66.除非另外定义,在此使用的全部用语(包含技术及科学用语)具有与本发明所属技术领域的技术人员通常理解的相同涵义。能理解的是,这些用语例如在通常使用的字典中定义用语,应被解读成具有与相关技术及本发明的背景或上下文一致的意思,而不应以一理想化或过度正式的方式解读,除非在本发明实施例有特别定义。

67.根据本发明一些实施例,提供的电子装置包含相位延迟元件,并将相位延迟元件的平面内光延迟值(in-plane retardation;ro)及平面外光延迟值(out-plane retardation;rth)设计在一范围内,可提高电子装置的品质,例如,改善于不同视角下的暗态漏光问题或面板亮度不均等问题。根据本发明一些实施例,电子装置可包含显示装置、发光装置、触控装置、感测装置、拼接装置或上述的组合,但不以此为限。电子装置可包括可弯折或可挠式电子装置。电子装置可例如包含液晶(liquid-crystal)装置,但不限于此。在一些实施例中,电子装置可包含背光模块(backlight module)。背光模块可包含发光二极管,例如包含无机发光二极管(inorganic light emitting diode)、有机发光二极管(organic light emitting diode,oled)、次毫米发光二极管(mini led)、微发光二极管(micro led)、量子点(quantum dot,qd)发光二极管(可例如为qled或qdled)、荧光(fluorescence)、磷光(phosphor)、其它合适的材料或前述的组合,但不以此为限。下文将以显示装置为例阐述电子装置,但本发明不以此为限。

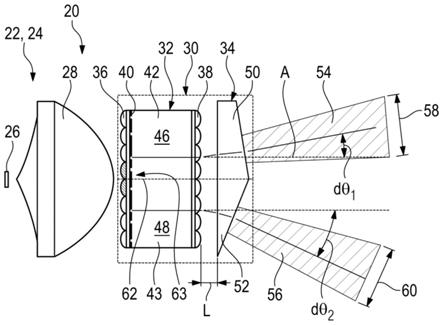

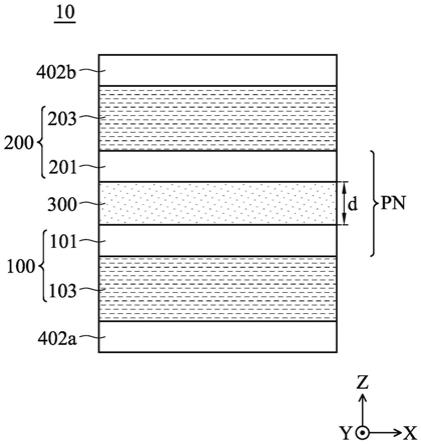

68.请参照图1,图1显示根据本发明一些实施例中,电子装置10的剖面结构示意图。应理解的是,为了清楚说明,图中省略电子装置10的部分元件,仅示意地示出部分元件。根据一些实施例,可添加额外特征于以下所述的电子装置10。在另一些实施例中,以下所述电子装置10的部分特征可以被取代或省略。

69.如图1所示,电子装置10可包含第一相位延迟元件100、第二相位延迟元件200以及液晶层300,第二相位延迟元件200可设置于第一相位延迟元件100上,且液晶层300可设置于第一相位延迟元件100与第二相位延迟元件200之间。

70.在一些实施例中,第一相位延迟元件100以及第二相位延迟元件200可例如用以改变光源的偏极化状态,包括改变光的偏振的长轴的方向和/或光的偏振型态(例如圆偏、椭圆偏或线偏),但不限于此。此外,第一相位延迟元件100具有第一平面内光延迟值(ro-1)及第一平面外光延迟值(rth-1),第二相位延迟元件200具有第二平面内光延迟值(ro-2)及第

二平面外光延迟值(rth-2)。在一些实施例中,第一平面内光延迟值和/或第二平面内光延迟值介于20纳米(nm)至70纳米之间(即20纳米≤ro-1≤70纳米,20纳米≤ro-2≤70纳米)、或介于30纳米至60纳米之间(即30纳米≤ro-1≤60纳米,30纳米≤ro-2≤60纳米),例如,35纳米、40纳米、45纳米、50纳米或55纳米,但不限于此。在一些实施例中,第一平面外光延迟值和/或第二平面外光延迟值介于170纳米至210纳米之间(即170纳米≤rth-1≤210纳米,170纳米≤rth-2≤210纳米)、或介于180纳米至200纳米之间(即180纳米≤rth-1≤200纳米,180纳米≤rth-2≤200纳米),例如,185纳米、190纳米或195纳米,但不限于此。

71.值得注意的是,若第一平面内光延迟值和/或第二平面内光延迟值过小或过大(例如,小于20纳米或大于70纳米),则第一相位延迟元件100或第二相位延迟元件200未可达到适当的光补偿效果,于一些视角下,易产生画面的暗态漏光的问题。相似地,若第一平面外光延迟值和/或第二平面外光延迟值过小或过大(例如,小于170nm或大于210nm),则第一相位延迟元件100或第二相位延迟元件200未可达到适当的光补偿效果,于一些视角下,易产生画面的暗态漏光的问题。

72.在一些实施例中,第一相位延迟元件100的第一平面内光延迟值与第二相位延迟元件200的第二平面内光延迟值可实质上相同,第一相位延迟元件100的第一平面外光延迟值与第二相位延迟元件200的第二平面外光延迟值可实质上相同,但不限于此。

73.根据一些实施例,第一相位延迟元件100可定义为液晶层300与第一偏光层402a之间的所有元件或层别,第二相位延迟元件200可定义为液晶层300与第二偏光层402b之间的所有元件或层别。再者,可借由已知的相位差测量仪器测量第一相位延迟元件100及第二相位延迟元件200的平面内光延迟值及平面外光延迟值,例如,偏光测定仪(axometrics)和/或位相差测定装置kobra系列。

74.请参考图1,在一些实施例中,第一相位延迟元件100可包含第一基板101以及相位延迟层103,第一基板101与相位延迟层103相邻,且第二相位延迟元件200可包含第二基板201以及相位延迟层203,第二基板201与相位延迟层203相邻,但不以此为限。

75.在一些实施例,面板pn可包含第一基板101、第二基板201以及设置于第一基板101及第二基板201之间的元件(包括液晶层300)。在一些实施例中,第一基板101可作为驱动基板,第二基板201可作为彩色滤光层基板,但不以此为限。关于第一基板101及第二基板201的详细配置结构,将于后文中进一步说明。

76.在一些实施例中,相位延迟层103和/或相位延迟层203可包含三醋酸纤维素(triacetyl cellulose,tac)、环烯烃聚合物(cyclic olefin copolymer,cop)、液晶高分子(liquid-crystal polymer,lcp)、聚甲基丙烯酸甲酯(polymethyl methacrylate,pmma)、其它合适的材料或前述的组合,但不限于此。再者,相位延迟层103及相位延迟层203可具有单层结构或多层结构(如图2至5图所示)。

77.在一些实施例中,液晶层300可包含液晶材料、其它合适的调制材料或上述的组合。在一些实施例中,液晶材料可包含向列型(nematic)液晶、层列型(smectic)液晶、胆固醇(cholesteric)液晶、蓝相(blue phase)液晶、其它合适的液晶材料或前述的组合,但不限于此。电子装置10可包含扭转向列(twisted nematic,tn)型液晶装置、超扭转向列(super twisted nematic,stn)型液晶装置、双层超扭转向列(double layer super twisted nematic,dstn)型液晶装置、垂直配向(vertical alignment,va)型液晶装置、水

平电场效应(in-plane switching,ips)型液晶装置、胆固醇型液晶装置、蓝相型液晶装置、边际电场效应(fringe field switching,ffs)型液晶装置、纳米突起垂直排列(nano-protrusion vertical alignment,npva)型液晶装置、其它合适的液晶装置或前述的组合。

78.再者,液晶层300可包含手性剂(chiral dopant),手性剂可调整液晶分子的排列和/或旋转特性,使位于部分区域(例如暗纹区)中的液晶分子可受到电场而转动,提供该部分区域(例如暗纹区)的相位延迟量,提高整体的电子装置的穿透率。暗纹区可定义为在电子装置施加电压而形成电场下,液晶分子转动较少(即提供较少相位延迟量的区域),举例如后续的图8所示,暗纹区可大致对应或重叠于第一电极层111的区域,但不限于此,详细的第一电极层111的设置位置及图案后续会再做叙述。在一些实施例中,手性剂(亦可称之为掌性分子(chiral molecule))的节距p(pitch)介于7微米(μm)至25微米之间(即7μm≤节距p≤25μm)、或介于10μm至20μm之间(即10μm≤节距p≤20μm),但不限于此,例如,11μm、12μm、13μm、14μm、15μm、16μm、17μm、18μm或19μm。当手性剂的节距p设计于上述范围下,可使液晶分子具有适当的旋性,提供较佳的相位延迟量,提高整体的电子装置10的穿透率。在一些实施例中,液晶层300的双折射率(δn,birefringence)与液晶层300的厚度d的乘积值可介于300纳米至550纳米之间(300纳米≦δn.d≦550纳米)、或可介于320纳米至380纳米之间(320纳米≦δn.d≦380纳米)或可介于440纳米至500纳米之间(440纳米≦δn.d≦550纳米),但不限于此。在一些实施例中,厚度d与节距p的比值可介于0.15至0.35之间(0.15≦d/p≦0.35)、0.2至0.3之间(0.2≦d/p≦0.3)或0.23至0.28(0.23≦d/p≦0.28)之间,但不限于此,例如0.24或025。

79.在一些实施例中,节距p(pitch)可透过grandjean-cano楔形槽法所测量,但不限于此。

80.根据一些实施例,前述厚度d指液晶层300于第一基板101的法线方向(例如图中所示出的z方向)上的最大厚度。

81.根据本发明实施例,可使用光学显微镜(optical microscopy,om)、扫描式电子显微镜(scanning electron microscope,sem)、薄膜厚度轮廓测量仪(α-step)、椭圆测厚仪、或其它合适的方式测量各元件的厚度、宽度或元件之间的距离。详细而言,在一些实施例中,可于移除液晶层300之后,使用扫描式电子显微镜取得结构的任一剖面影像,并测量各元件于影像中的高度、厚度或元件之间的距离。

82.如图1所示,根据一些实施例,电子装置10可进一步包含第一偏光层402a以及第二偏光层402b,第一偏光层402a邻近于第一相位延迟元件100,第二偏光层402b邻近于第二相位延迟元件200。在一些实施例中,第一相位延迟元件100、第二相位延迟元件200以及液晶层300设置于第一偏光层402a以及第二偏光层402b之间。

83.在一些实施例中,第一偏光层402a和/或第二偏光层402b可包含聚乙烯醇(polyvinyl alcohol,pva)薄膜、三醋酸纤维素(tri-acetyl cellulose,tac)、压敏胶(pressure sensitive adhesive film)、保护薄膜(protective film)和/或离型膜、其它合适的偏光材料或上述的组合,但不限于此。

84.在一些实施例中,可选择性借由粘着制程将前述各元件粘合,例如,将相位延迟层103与第一基板101粘合、将相位延迟层203与第二基板201粘合、将相位延迟层103与第一偏光层402粘合、或将相位延迟层203与第二偏光层402b粘合。换言之,前述各元件之间可选择

性具有粘着层(未示出)。在另一些实施例中,可借由涂布制程、化学沉积制程、印刷制程、其它合适的制程或前述的组合,依序形成前述各元件的层叠结构。

85.请参照图2,图2显示根据本发明另一些实施例中,电子装置20的剖面结构示意图。应理解的是,后文中与前文相同或相似的组件或元件将以相同或相似的标号表示,其材料、制造方法与功能皆与前文所述相同或相似,故此部分于后文中将不再赘述。

86.如图2所示,在一些实施例,第一相位延迟元件100以及第二相位延迟元件200可为复合层,例如可具有多层相位延迟层。详细而言,在一些实施例中,第一相位延迟元件100可包含第一相位延迟层103a和/或第二相位延迟层103b,第二相位延迟元件200可包含第三相位延迟层203a和/或第四相位延迟层203b,第一相位延迟层103a位于第二相位延迟层103b与第一偏光层402a之间,且第三相位延迟层203a位于第四相位延迟层203b与第二偏光层402b之间。

87.如图2所示,根据一些实施例,上述的相位延迟层可设置于第一基板101和/或第二基板201的外侧,亦即,上述的相位延迟层可设置于面板pn的外侧,为面板外(out-cell)的相位延迟层。在一些实施例中,面板pn包含第一基板101、第二基板201以及设置于两者之间的液晶层300。

88.在一些实施例中,第一相位延迟元件100可设置于第一偏光层402a与液晶层300之间。在一些实施例中,第二相位延迟元件200可设置于第二偏光层402b与液晶层300之间。在一些实施例中,第一相位延迟元件100可包含第一基板101、第一相位延迟层103a和/或第二相位延迟层103b,且第一相位延迟层103a设置于第一基板101与液晶层300之间,第二相位延迟层103b设置于第一相位延迟层103a与液晶层300之间。在一些实施例中,第二相位延迟元件200可包含第二基板201、第三相位延迟层203a和/或第四相位延迟层203b,第三相位延迟层203a设置于第二基板201与液晶层300之间,第四相位延迟层203b设置于第三相位延迟层203a与液晶层300之间。

89.在一些实施例中,第一相位延迟层103a、第二相位延迟层103b、第三相位延迟层203a和/或第四相位延迟层203b的材料可与前述相位延迟层103及相位延迟层203的材料相似,于此不再重复。在一些实施例中,第一相位延迟层103a与第三相位延迟层203a的材料相同,第二相位延迟层103b与第四相位延迟层203b的材料相同,且第一相位延迟层103a与第二相位延迟层103b的材料不同,亦即,电子装置20可具有实质上对称(以液晶层300为基准)的层叠结构,但不限于此。在一些实施例中(未示出),第一相位延迟层103a与第四相位延迟层203b的材料相同,第二相位延迟层103b与第三相位延迟层203a的材料相同,且第一相位延迟层103a与第二相位延迟层103b的材料不同,但不限于此。在一些实施例中,第一相位延迟层103a、第二相位延迟层103b、第三相位延迟层203a及第四相位延迟层203b的材料可部分相同或部分不同,或者全部相同或全部不同。

90.应理解的是,相位延迟层的数目和/或排列方式不限于附图中所示出,根据一些实施例,第一相位延迟元件100及第二相位延迟元件200可具有其它合适数目的相位延迟层(例如,两层、三层、四层,但不限于此),且第一相位延迟元件100及第二相位延迟元件200具有的相位延迟层的数目可相同或不同,只要第一相位延迟元件100及第二相位延迟元件200可具有如上所述的平面内光延迟值及平面外光延迟值即可,例如上述的第一平面内光延迟值和/或第二平面内光延迟值介于20纳米至70纳米之间(20纳米≤ro-1≤70纳米,20纳米≤

ro-2≤70纳米),而第一平面外光延迟值和/或第二平面外光延迟值介于170纳米至210纳米之间(170纳米≤rth-1≤210纳米,170纳米≤rth-2≤210纳米)。

91.请参照图3,图3显示根据本发明另一些实施例中,电子装置30的剖面结构示意图。如图3所示,在一些实施例,第一相位延迟元件100和/或第二相位延迟元件200可包括复合层,例如可具有多层的相位延迟层,且这些相位延迟层可设置于第一基板101及第二基板201的内侧,亦即,可设置于面板pn的内侧,即为面板内(in-cell)的相位延迟层。在图3所示的实施例中,面板pn包含第一基板101、第二基板201及设置于第一基板101与第二基板201之间的第一相位延迟层103a、第二相位延迟层103b、液晶层300、第三相位延迟层203a和/或第四相位延迟层203b,但不限于此。

92.在一些实施例中,第一相位延迟层103a及第二相位延迟层103b可设置于第一基板101与液晶层300之间。在一些实施例中,第三相位延迟层203a及第四相位延迟层203b可设置于第二基板201与液晶层300之间。在一些实施例中,第一相位延迟层103a、第二相位延迟层103b、第三相位延迟层203a和/或第四相位延迟层203b的材料可包含液晶高分子(liquid-crystal polymer,lcp),如上述由液晶高分子所组成的相位延迟层,可设置于液晶层300与第一基板101之间或是液晶层300与第二基板201之间的任一层结构中。在一些实施例中,上述的由液晶高分子所组成的相位延迟层,其对应于不同颜色(例如红色、蓝色和/或绿色,但不限于此)的子像素中可选择性分别具有不同的相位延迟层的厚度,相位延迟层的厚度例如透过扫描式电子显微镜测量该sem影像中的该膜层的最大厚度。

93.请参照图4,图4显示根据本发明另一些实施例中,电子装置40的剖面结构示意图。如图4所示,根据一些实施例,第一相位延迟元件100、第二相位延迟元件200、第一偏光层402a和/或第二偏光层402b可设置于第一基板101及第二基板201的内侧,偏光层亦可设置于面板pn的内侧,为面板内(in-cell)的相位延迟层。在图4所示的实施例中,面板pn包含第一基板101、第二基板201及设置于第一基板101与第二基板201之间的第一偏光层402a、第一相位延迟层103a、第二相位延迟层103b、液晶层300、第二偏光层402b、第三相位延迟层203a和/或第四相位延迟层203b,但不限于此。

94.在一些实施例中,第一相位延迟元件100可设置于液晶层300与第一偏光层402a之间。在一些实施例中,第二相位延迟元件200可设置于液晶层300与第二偏光层402b之间。在一些实施例中,第一偏光层402a可设置于第一相位延迟元件100与第一基板101之间。在一些实施例中,第二偏光层402b可设置于第二相位延迟元件200与第二基板201之间。于图4的实施例的第一偏光层402a和/或第二偏光层402b例如包括金属(纳米)光栅(periodic metal(nano)wire grid plate,wgp),但不限于此。

95.请参照图5,图5显示根据本发明另一些实施例中,电子装置50的剖面结构示意图。如图5所示,在一些实施例,第一相位延迟元件100及第二相位延迟元件200可部分地设置于面板pn内,且可部分地设置于面板pn的外侧。举例来说,第一相位延迟元件100的第二相位延迟层103b及第二相位延迟元件200的第四相位延迟层203b可设置于面板pn的内侧(即第一基板101及第二基板201的内侧)。在一些实施例中,第一相位延迟元件100的第一相位延迟层103a及第二相位延迟元件200的第三相位延迟层203a可设置于面板pn的外侧(即分别设置于第一基板101及第二基板201的外侧)。换言之,第一相位延迟元件100的第一相位延迟层103a及第二相位延迟层103b可分别设置于第一基板101的两侧。在一些实施例中,第二

相位延迟元件200的第三相位延迟层203a以及第四相位延迟层203b可分别设置于第二基板201的两侧。在图5所示的实施例中,面板pn包含第一基板101、第二基板201及设置于第一基板101与第二基板201之间的第二相位延迟层103b、液晶层300和/或第四相位延迟层203b。

96.在一些实施例中(未示出),第一相位延迟元件100可部分设置于面板pn内,且部分设置于面板pn外,而第二相位延迟元件200可完整地设置于面板pn内,但不限于此。换言之,第一相位延迟层103a以及第二相位延迟层103b的其中一者可设置于第一基板101与液晶层300之间,而第三相位延迟层203a及第四相位延迟层203b均设置于第二基板201与液晶层300之间。总而言之,第一相位延迟元件100和/或第二相位延迟元件200可选择性完全地设置于面板pn外、完全地设置于面板pn内或部分地设置于面板pn内且部分地设置于面板pn外。

97.请参照图6,图6显示根据本发明一些实施例中,电子装置的光学分析结果图,此光学分析结果图例如为于电子装置于显示暗态的状况下所测量的结果。此光学分析结果可例如借由锥光(conoscopic)镜头测量或其它合适仪器进行测量或分析,但不限于此。具体而言,在图6中,右侧色阶代表不同的单位面积的亮度(cd/m2),左侧的结果显示对应于不同角度θ及方位角下的单位面积的亮度(cd/m2)的情况。其中,角度θ例如为测量方向与面板pn的法线方向z的夹角,方位角例如为测量方向在平行于面板pn的上表面方向上的角度。在图6中,可得知在角度θ为0度(即包括中心点)至20度的范围,且方位角介于0至360度的情况下,其单位面积的亮度(cd/m2)约大致介于0cd/m2至4e-006cd/m2的范围。在角度θ为20度至40度范围,且方位角介于0至360度的情况下,其单位面积的亮度(cd/m2)约介于4e-006cd/m2至1.2e-004cd/m2的范围。在角度θ为40度至80度的范围,且于大部分的方位角的范围(例如方位角大致介于0度至22.5度、介于67.5度至112.5度、介于172.5度至202.5度和/或介于247.5度至292.5度)下,其单位面积的亮度(cd/m2)约于1.2e-004cd/m2以内。在角度θ为40度至80度的范围,且于其它部分的方位角的范围(上述以外的方位角的范围)下,其单位面积的亮度(cd/m2)约于1.6e-004cd/m2至2.0e-004cd/m2的范围,但不限于此。由此可知,此电子装置于不同视角下的暗态漏光问题并不明显。应理解的是,前述电子装置的单位面积的亮度值(cd/m2)范围仅为示意某一实施例的结果,但不以此为限,此单位面积的亮度值可根据面板pn的设计、液晶层300的材料而有所不同。

98.请参照图7,图7显示根据本发明另一些实施例中,电子装置60的剖面结构示意图。图7示出根据一些实施例中,面板pn的详细结构。应理解的是,图7以面板pn包含第一基板101、第二基板201及液晶层300为例,在面板pn进一步包含其它元件的实施例中,可适当地调整结构排列的配置。

99.如图7,在一些实施例中,第二基板201相对于第一基板101,液晶层300设置于第一基板101与第二基板201之间。承前述,第一基板101可作为驱动基板,第一基板101可包含第一基底101s及电路层101x,电路层101x可设置于第一基底101s上,且电路层101x可位于第一基底101s与液晶层300之间。

100.在一些实施例中,第一基底101s可包含可挠式基板、刚性基板或前述的组合。在一些实施例中,第一基底101s的材料可包含玻璃、石英、蓝宝石(sapphire)、陶瓷、聚酰亚胺(polyimide,pi)、液晶高分子(liquid-crystal polymer,lcp)材料、聚碳酸酯

(polycarbonate,pc)、感光型聚酰亚胺(photo sensitive polyimide,pspi)、聚对苯二甲酸乙二酯(polyethylene terephthalate,pet)、其它合适的材料或前述的组合,但不限于此。

101.在一些实施例中,电路层101x可包含驱动电路,驱动电路可例如包括有源式驱动电路和/或无源式驱动电路。在一些实施例中,驱动电路可包含晶体管(例如,开关晶体管或驱动晶体管等)、数据线、扫描线、导电垫、介电层或其它线路等,但不限于此。

102.在一些实施例中,第一电极层111及第一配向层113可依序设置于电路层101x上,第一电极层111及第一配向层113可位于第一基板101与液晶层300之间,第一电极层111可与电路层101x电性连接。在一些实施例中,第一电极层111可经图案化以具有多个第一开口o1。在一些实施例中,第一配向层113可顺应性地(conformally)形成于第一电极层111上及这些第一开口o1中。

103.在一些实施例中,第一电极层111的材料可包含金属导电材料、透明导电材料、其它合适的材料或前述的组合,但不限于此。金属导电材料可包含铜(cu)、银(ag)、锡(sn)、铝(al)、钼(mo)、钨(w)、金(au)、铬(cr)、镍(ni)、铂(pt)、钛(ti)、上述任一金属合金、其它合适的材料或前述的组合,但不限于此。透明导电材料可包含铟锡氧化物(indium tin oxide,ito)、氧化锡(tin oxide,sno)、氧化锌(zinc oxide,zno)、氧化铟锌(indium zinc oxide,izo)、氧化铟镓锌(indium gallium zinc oxide,igzo)、氧化铟锡锌(indium tin zinc oxide,itzo)、氧化锑锡(antimony tin oxide,ato)、氧化锑锌(antimony zinc oxide,azo)、其它合适的材料或前述的组合,但不限于此。

104.承前述,第二基板201可作为彩色滤光层基板。在一些实施例中,第二基板201可包含第二基底201s及彩色滤光层201x,彩色滤光层201x可设置于第二基底201s上,位于第二基底201s与液晶层300之间。在一些实施例中,第二基板201亦包含遮光层(未示出),遮光层可设置在彩色滤光层201x的彩色滤光单元(未示出)之间。第二基底201s的材料可与前述第一基底101s的材料相似,于此不再重复。第二基底201s的材料可与第一基底101s的材料相同或不同。在一些实施例中,第二电极层211及第二配向层213可依序设置于彩色滤光层201x上,第二电极层211及第二配向层213可位于第二基板201与液晶层300之间。

105.在一些实施例中,第二电极层211可未经图案化,亦即,第二电极层211可不具有开口。再者,第二电极层211的材料可与前述第一电极层111的材料相似,于此不再重复。并且,第二电极层211的材料可与第一电极层111的材料相同或不同。

106.请参照图8,图8显示根据本发明一些实施例中,电子装置60的子像素区域sp的上视结构示意图,图8中的截线a-a’可对应于图7所示的剖面结构。应理解的是,为了清楚说明,图8仅示出第一电极层111,而省略其它元件,电子装置60实际上可具有多个子像素区域sp,图8仅示出了其中一者。

107.如图8所示,第一电极层111对应设置于电子装置60的子像素区域sp中。承前述,第一电极层111可经图案化以具有多个第一开口o1。在一些实施例中,经图案化的第一电极层111可具有主部111a及多个分支部111b,主部111a可将第一电极层111分为第一部分p1、第二部分p2、第三部分p3以及第四部分p4,其中,第一部分p1、第二部分p2、第三部分p3以及第四部分p4可例如以顺时钟方式排列。如图8所示,第二部分p2与第四部分p4相邻于第一部分p1,第三部分p3与第一部分p1大致呈对角方式排列。在一些实施例中,可选择性地有更多或

更少部分。在一些实施例中,主部111a可具有十字形状,但不以此为限。在一些实施例中,多个分支部111b可连接于主部111a,且远离主部111a的方向延伸,但不限于此。

108.在一些实施例中,对应于第一部分p1的分支部111b中的一者与主部111a之间具有第一夹角θ1,对应于第二部分p2中的分支部111b中的一者与主部111a之间具有第二夹角θ2。在一些实施例中,第一夹角θ1与第二夹角θ2大致相等。在一些实施例中,第一夹角θ1和/或第二夹角θ2可介于40度至50度之间(40度≦第一夹角θ1≦50度;40度≦第二夹角θ2≦50度)、或介于于42度至48度之间(42度≦第一夹角θ1≦48度;42度≦第二夹角θ2≦48度),例如,45度。需注意的是,第一夹角θ1及第二夹角θ2指对应该分支部111b(例如其延伸面)与主部111a的长轴(如图中沿y方向延伸的部分)之间所形成的角度。在一些实施例中,对应于第一部分p1的分支部111b中的一者与对应于相邻的第二部分p2的分支部111b中的一者之间具有夹角θ

t

(即大致可视为第一夹角θ1与第二夹角θ2的总合)。在一些实施例中,夹角θ

t

可介于80度至100度之间(80度≦夹角θ

t

≦100度)、或介于于85度至95度之间(85度≦夹角θ

t

≦95度),例如,90度。

109.需注意的是,如图8所示,夹角θ

t

指第一部分p1的延伸面与第二部分p2的分支部111b的延伸面所相交所形成的角度。

110.请参照图8,在一些实施例中,以主部111a的长轴(如图中沿y方向延伸的部分)为基准,第一部分p1的分支部111b与第二部分p2的分支部111b之间为大致对称。在一些实施例中,以主部111a的长轴为基准,第三部分p3的分支部111b与第四部分p4的分支部111b之间为大致对称。在一些实施例中,以主部111a的短轴(如图中沿x方向延伸的部分)为基准,第一部分p1的分支部111b与第四部分p4的分支部111b之间为大致对称。在一些实施例中,以主部111a的短轴为基准,第二部分p2的分支部111b与第三部分p3的分支部111b之间为大致对称。上述「对称」例如包括分支部111b与主部111a之间的夹角大致相同,分支部111b的宽度和/或相邻的分支部111b的间距大致相同,但不限于此。

111.请参照图9,图9显示根据本发明另一些实施例中,电子装置60的子像素区域sp的上视结构示意图。图9所示的实施例与图8所示的实施例相似,两者的差异之一在于,图9中的第一电极层111的分支部111b的延伸方向与图8中的不同。

112.如图9所示,在一些实施例中,对应于第一部分p1的分支部111b中的一者与主部111a之间具有第一夹角θ1,对应于第二部分p2中的分支部111b中的一者与主部111a之间具有第二夹角θ2,对应于第三部分p3中的分支部111b中的一者与主部111a之间具有第三夹角θ3,对应于第四部分p4中的分支部111b中的一者与主部111a之间具有第四夹角θ4。再者,第三夹角θ3及第四夹角θ4的定义与前述第一夹角θ1以及第二夹角θ2的定义相似,与此不再重复。在一些实施例中,第一夹角θ1与第二夹角θ2不相等。在一些实施例中,第三夹角θ3与第四夹角θ4不相等。在一些实施例中,对应于第一部分p1的分支部111b中的一者(例如其延伸面)与对应于相邻的第二部分p2的分支部111b中的一者(例如其延伸面)之间具有夹角θ

t

(即可大致可视为第一夹角θ1与第二夹角θ2的总合)。在一些实施例中,夹角θ

t

可介于80度至100度之间(80度≦夹角θ

t

≦100度)、或介于于85度至95度之间(85度≦夹角θ

t

≦95度),例如,90度。在一些实施例中,对应于第三部分p3的分支部111b中的一者(例如其延伸面)与对应于相邻的第四部分p4的分支部111b中的一者(例如其延伸面)之间具有夹角(未示出,即可大致可视为第三夹角θ3与第四夹角θ4的总合),该夹角的角度范围例如相近于上述夹角θ

t

的角度范围。在一些实施例中,第一夹角θ1可介于45度至75度之间(45度≦第一夹角θ1≦75度),第二夹角θ2介于15度至45度之间(15度≦第一夹角θ1≦45度)之间。

113.如图9所示,在一些实施例中,第三夹角θ3与第一夹角θ1大致相等。在一些实施例中,第二夹角θ2与第四夹角θ4大致相等。在一些实施例中,以主部111a的长轴(如图中沿y方向延伸的部分)为基准,第一部分p1的分支部111b与第二部分p2的分支部111b之间为非对称关系。在一些实施例中,以主部111a的长轴为基准,第三部分p3的分支部111b与第四部分p4的分支部111b之间为非对称关系。在一些实施例中,以主部111a的短轴为基准,第一部分p1的分支部111b与第四部分p4的分支部111b之间为非对称关系。在一些实施例中,以主部111a的短轴(如图中沿x方向延伸的部分)为基准,第二部分p2的分支部111b与第三部分p3的分支部111b之间为非对称关系。

114.相较于图8中所示的第一电极层111,图9的第一电极层111的分支部111b的延伸方向为逆时针的方式调整,即位于不同部分(例如第一部分p1、第二部分p2、第三部分p3及第四部分p4)下的分支部111b的延伸方向皆朝逆时针的方向调整约5度至45度或5度至30度,但不以此为限。在一些实施例中,当手性剂可将液晶分子以顺时针方向旋转的情况下,第一电极层111可例如选用如图9的第一电极层111的分支部111b的延伸方向为逆时针的方式调整的设计,可以达到较佳的穿透率,但不限于此。在另一些实施例(未示出),相较于图8中所示的第一电极层111,第一电极层111的分支部111b的延伸方向可为顺时针的方式调整,即位于不同部分(例如第一部分p1、第二部分p2、第三部分p3及第四部分p4)下的分支部111b的延伸方向皆朝顺时针的方向调整约5度至45度或5度至30度,但不以此为限。在一些实施例中,当手性剂可将液晶分子以顺时针方向旋转的情况下,则第一电极层111的设计可例如的分支部111b的延伸方向可选用逆时针方式调整的设计,可以达到较佳的穿透率,但不限于此。

115.请参照图10,图10显示根据本发明另一些实施例中,电子装置70的剖面结构示意图。图10所示的实施例与图7所示的实施例相似,两者的差异之一在于,在图10中,电子装置70的第二电极层211可经图案化以具有多个第二开口o2。在一些实施例中,第二配向层213可顺应性地(conformally)形成于第二电极层211上及这些第二开口o2中。在一些实施例中,于第一基板101的法线方向(例如图中所示出的z方向)上,第二电极层211可与第一开口o1重叠或第一电极层111可与第二开口o2重叠。在一些实施例中,第二开口o2与第一开口o1的宽度可相同或不同。

116.综上所述,根据本发明一些实施例,提供的电子装置包含第一相位延迟元件及第二相位延迟元件,且第一相位延迟元件及第二相位延迟元件分别的平面内光延迟值(ro)及平面外光延迟值(rth)于本案的设计范围中,可改善电子装置的显示画面品质,例如,降低于不同视角下的暗态漏光问题或面板亮度不均等问题。

117.虽然本发明的实施例及其优点已揭露如上,但应该了解的是,任何本领域技术人员,在不脱离本发明的精神和范围内,当可作改动、替代与润饰。本发明实施例之间的特征只要不违背发明精神或相冲突,均可任意混合搭配使用。此外,本发明的保护范围并未局限于说明书内所述特定实施例中的制程、机器、制造、物质组成、装置、方法及步骤,任何本领域技术人员可从本发明揭示内容中理解现行或未来所发展出的制程、机器、制造、物质组成、装置、方法及步骤,只要可以在此处所述实施例中实施大抵相同功能或获得大抵相同结

果皆可根据本发明使用。因此,本发明的保护范围包括上述制程、机器、制造、物质组成、装置、方法及步骤。本发明的保护范围当视权利要求所界定者为准。本发明的任一实施例或权利要求不须达成本发明所公开的全部目的、优点、特点。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。