地址控制电路和包括其的半导体装置

1.相关申请的交叉引用

2.本技术要求于2021年8月10日提交至韩国知识产权局的韩国申请第10-2021-0105520号的优先权,其整体通过引用并入本文。

技术领域

3.各种实施例大体涉及半导体电路,并且具体地,涉及地址控制电路和包括该地址控制电路的半导体装置。

背景技术:

4.半导体装置(例如,半导体存储装置)具有多种确定其性能的标准,并且其中一个标准是电流消耗。存在各种用于确定半导体存储装置的电流消耗特性的操作标准。因此,设计能够满足上述操作标准的半导体存储装置是非常重要的。特别地,半导体存储装置的存储区的物理布置需要被设计成在操作标准方面具有优势。

技术实现要素:

5.各种实施例涉及一种能够降低操作电流的地址控制电路,以及包括该地址控制电路的半导体装置。

6.在一个实施例中,一种地址控制电路可以包括:地址时序控制电路,其被配置为:锁存从地址时序控制电路外部输入的地址信号,以预定时序顺序地储存锁存的信号,以及将所储存的信号输出作为存储体组地址;以及地址多路复用电路,其被配置为根据存储体组地址来产生存储体组选择信号。地址多路复用电路可以被配置为:当预设的存储器访问模式是第一存储器访问模式时,根据具有第一值的存储体组地址来产生具有第二值的存储体组选择信号,以及当预设的存储器访问模式是第二存储器访问模式时,根据具有与第一值不同的第三值的存储体组地址来产生具有第二值的存储体组选择信号。

7.地址多路复用电路可以包括:地址多路复用器,其被配置为:当预设的存储器访问模式是第一存储器访问模式时,根据存储体组地址的第一地址比特位来产生预解码信号的一部分,且根据存储体组地址的第二地址比特位来产生预解码信号的其余部分,以及当预设的存储器访问模式是第二存储器访问模式时,根据存储体组地址的第二地址比特位来产生预解码信号的一部分,且根据存储体组地址的第一地址比特位来产生预解码信号的其余部分;以及解码电路,其被配置为将通过对预解码信号进行解码而获得的信号输出作为存储体组选择信号。

8.在一个实施例中,一种半导体装置可以包括:存储区,其包括被划分为多个存储体组的多个存储体;以及地址控制电路,其被配置为根据存储体组地址来产生存储体组选择信号。地址控制电路可以被配置为:当预设的存储器访问模式是第一存储器访问模式时,根据具有第一值的存储体组地址来产生具有第二值的存储体组选择信号,且当预设的存储器访问模式是第二存储器访问模式时,根据具有与第一值不同的第三值的存储体组地址来产

生具有第二值的存储体组选择信号,以及当预设的存储器访问模式是第一存储器访问模式时选择性地操作多个存储体组,且当预设的存储器访问模式是第二存储器访问模式时,对多个存储体进行配对并选择性地操作配对的存储体。

9.地址控制电路可以包括:地址多路复用器,其被配置为:当预设的存储器访问模式是第一存储器访问模式时,根据存储体组地址的第一地址比特位来产生预解码信号的一部分,且根据存储体组地址的第二地址比特位来产生预解码信号的其余部分,以及当预设的存储器访问模式是第二存储器访问模式时,根据存储体组地址的第二地址比特位来产生预解码信号的一部分,且根据存储体组地址的第一地址比特位来产生预解码信号的其余部分;以及解码电路,其被配置为将通过对预解码信号进行解码而获得的信号输出作为存储体组选择信号。

10.在一个实施例中,半导体装置可以包括:存储区,其包括被划分为多个存储体组的多个存储体;以及地址控制电路,其被配置为根据存储体组地址来产生用于在多个存储体组之中选择任何一个存储体组的存储体组选择信号。地址控制电路可以被配置为:在对多个存储体之中的两个不同的存储体的连续读取操作期间改变存储体组选择信号的值,以使在第一存储器访问模式中选择的两个存储体组与在第二存储器访问模式中选择的两个存储体组相匹配。

附图说明

11.图1是示出根据实施例的半导体装置的配置的图。

12.图2a和图2b是示出根据实施例的存储体组模式操作的示例的图。

13.图3a和图3b是示出根据实施例的8存储体模式操作的示例的图。

14.图4是示出根据实施例的地址控制电路的配置的图。

15.图5是示出根据实施例的地址多路复用电路的配置的图。

具体实施方式

16.在下文中,将参考附图更详细地描述一些实施例。

17.图1是示出根据实施例的半导体装置100的配置的图。

18.参考图1,半导体装置100可以包括存储区101、地址解码器102、引脚阵列103、数据输入/输出电路104和控制电路105。

19.存储区101可以包括多个存储单元,并且多个存储单元可以包括易失性存储器和非易失性存储器中的一种或两种。易失性存储器的示例包括sram(静态ram)、dram(动态ram)和sdram(同步dram);且非易失性存储器的示例包括rom(只读存储器)、prom(可编程rom)、eeprom(电可擦除可编程rom)、eprom(电可编程rom)、闪速存储器、pram(相变ram)、mram(磁性ram)、rram(电阻式ram)和fram(铁电ram)。在半导体装置100的读取操作期间,可以输出储存在存储区101中的数据。在半导体装置100的写入操作期间,可以将从半导体装置100外部输入的数据储存在存储区101中。存储区101的存储单元可以被划分为多个单元存储区,例如多个存储体。多个存储体可以被划分为存储体组并且被控制为适合于半导体装置100的读取操作和写入操作。

20.地址解码器102可以耦接到控制电路105和存储区101。地址解码器102可以对控制

电路105所提供的地址信号进行解码,并根据解码结果访问存储区101。控制电路105所提供的地址信号可以包括行地址信号和列地址信号。行地址信号可以包括用于选择性地使能多个存储体组的地址和用于选择性地使能多个存储体的地址。用于选择性地使能多个存储体组的地址可以被称为存储体组地址,并且用于选择性地使能多个存储体的地址可以被称为存储体地址。

21.引脚阵列103可以包括命令和地址集成引脚(ca)103-1。通过该命令和地址集成引脚103-1,可以以预定时序顺序地输入命令cmd和外部地址信号add。

22.数据输入/输出电路104可以耦接到存储区101。数据输入/输出电路104可以与半导体装置100的外部或内部交换数据。数据输入/输出电路104可以包括数据输入缓冲器、数据输出缓冲器、数据输入/输出焊盘等。

23.控制电路105可以耦接到存储区101、地址解码器102和数据输入/输出电路104。控制电路105可以执行与半导体装置的读取操作、写入操作和地址处理操作有关的控制操作。控制电路105可以通过命令和地址集成引脚ca从半导体装置100外部接收命令和外部地址信号。控制电路105可以包括地址控制电路。地址控制电路可以控制地址信号,使得地址信号适合于针对半导体装置100的每个操作模式的读取操作和写入操作。地址控制电路可以以预设时序锁存地址信号,使得地址信号适合于针对半导体装置100的每个操作模式的读取操作和写入操作。地址控制电路可以改变地址信号的值,使得地址信号适合于半导体装置100的操作模式。

24.图2a和图2b是示出根据实施例的存储体组模式操作的示例的图。

25.当设计半导体装置100时,可以将其设计为具有降低电流消耗的结构。存在各种用于确定半导体存储装置的电流消耗特性的操作模式idd0、idd2p、idd3p、idd2n、idd3n、idd4r、idd4w、idd5和idd6。半导体装置100被设计成支持多个存储器访问模式。多个存储器访问模式可以包括第一至第三存储器访问模式。第一存储器访问模式可以被称为存储体组模式,第二存储器访问模式可以被称为8存储体模式,且第三存储器访问模式可以被称为16存储体模式。存储体组模式是将多个存储体划分为单元组并进行操作的操作模式。8存储体模式是多个存储体(例如,16个存储体)以配对方式进行划分使得16个存储体像8个存储体那样进行操作的操作模式。16存储体模式是多个存储体(例如,16个存储体)中的每一个都被选择并被操作的操作模式。

26.例如,可以设置多个存储体的物理布置以最小化根据半导体装置100的存储体组模式的电流消耗,并且将参考图2a和图2b来描述该物理布置。

27.图2a示出了存储体的物理布置被设置为当半导体装置100根据基于存储体组模式的idd4r/idd4w模式进行操作时最小化电流消耗的示例。该idd4r/idd4w模式可以指示对两个存储体的连续读取/写入操作。

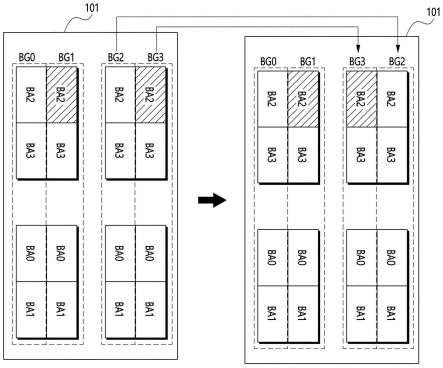

28.参考图2a,存储区101的多个存储体(例如,16个存储体)可以在图的第一方向(例如,水平方向)上被划分为多个存储体组bg0、bg1、bg2和bg3(在下文中,被称为bg0至bg3),然后被控制。仅为便于描述,将第一方向设置为图的水平方向,但不限于此。在下文中,bg0表示第一存储体组,bg1表示第二存储体组,bg2表示第三存储体组,且bg3表示第四存储体组。多个存储体组bg0至bg3例如可以从图的左侧到右侧按照第一存储体组bg0、第二存储体组bg1、第三存储体组bg2和第四存储体组bg3的顺序来布置。

29.多个存储体组bg0至bg3中的每一个可以包括在图的第二方向(例如,垂直方向)上布置的多个存储体ba0、ba1、ba2和ba3(在下文中,被称为ba0至ba3)。仅为了便于描述,将第二方向设置为图的垂直方向,但不限于此。在下文中,ba0表示第一存储体,ba1表示第二存储体,ba2表示第三存储体,且ba3表示第四存储体。例如,多个存储体ba0至ba3可以按照第三存储体ba2、第四存储体ba3、第一存储体ba0和第二存储体ba1的顺序来布置。

30.当半导体装置100根据基于存储体组模式的idd4r/idd4w模式来操作时,可以根据半导体装置的操作标准来对第二存储体组bgl的第三存储体ba2和第三存储体组bg2的第三存储体ba2执行连续的读取/写入操作,如图2a中用阴影指示的。也就是说,为了减少根据idd4r/idd4w模式的电流消耗,对物理上彼此最接近并且在顺序上具有相同编号的存储体执行连续的读取/写入操作是有利的。因此,多个存储体的物理布置被设置为图2a所示的形状。

31.图2b示出了存储体的物理布置被设置为当半导体装置100根据基于存储体组模式的idd4r/idd4w模式来操作时最小化电流消耗的另一示例。

32.参考图2b,存储区101的多个存储体(例如,16个存储体)可以在图的第二方向(例如垂直方向)上被划分为多个存储体组bg0至bg3,然后被控制。仅为便于描述,将第二方向设置为图的垂直方向,但不限于此。多个存储体组bg0至bg3例如可以从图的顶部到底部按照第二存储体组bg1、第三存储体组bg2、第四存储体组bg3和第一存储体组bg0的顺序来布置。

33.多个存储体组bg0至bg3中的每一个可以包括在图的第一方向和第二方向(即水平方向和垂直方向)上布置的多个存储体ba0至ba3。根据多个存储体ba0至ba3的布置,第一存储体ba0和第二存储体ba1可以布置在水平方向上,且第三存储体ba2和第四存储体ba3可以分别布置在第一存储体ba0和第二存储体ba1下方。

34.当半导体装置100根据基于存储体组模式的idd4r/idd4w模式来操作时,可以根据半导体装置的操作标准对第二存储体组bgl的第三存储体ba2和第三存储体组bg2的第三存储体ba2执行连续的读取/写入操作,如图2b中用阴影指示的。也就是说,为了减少根据idd4r/idd4w模式的电流消耗,对物理上彼此最接近并且在顺序上具有相同编号的存储体执行连续的读取/写入操作是有利的。因此,多个存储体的物理布置被设置为图2b所示的形状。

35.图3a和图3b是示出根据实施例的8存储体组模式操作的示例的图。

36.参考图3a的左侧,当根据基于8存储体模式的idd4r/idd4w模式来操作包括具有图2a所示的物理布置的存储区101的半导体装置100时,根据半导体装置的操作标准选择的存储体不同于在上述存储体组模式中选择的存储体。在8存储体模式操作期间,第二存储体组bg1的第三存储体ba2和第四存储体组bg3的第三存储体ba2可以像一个存储体那样操作。在基于存储体组模式的idd4r/idd4w模式的情况下,对第二存储体组bg1的第三存储体ba2和第三存储体组bg2的第三存储体ba2执行连续的读取/写入操作。然而,当半导体装置100根据基于8存储体模式的idd4r/idd4w模式来操作时,对第二存储体组bg1的第三存储体ba2和第四存储体组bg3的第三存储体ba2执行连续的读取/写入操作。结果,在8存储体模式中,所选存储体之间的物理距离增加,大于在存储体组模式中。因此,在信号线负载增加的同时,电流消耗增加。

37.因此,在本实施例中,如图3a的右侧所示,不改变存储区101的存储体的物理布置,并且即便在8存储体模式中,也可以以与存储体组模式相同的方式通过地址控制来选择彼此最接近且在顺序上具有相同编号的存储体。也就是说,可以通过地址控制将第三存储体组bg2和第四存储体组bg3分别识别为第三存储体组bg2和第四存储体组bg3。在下文中,通过地址控制允许存储体组被不同地识别的操作将被称为地址映射改变操作。

38.参考图3b的左侧,当根据基于8存储体模式的idd4r/idd4w模式来操作包括具有图2b所示的物理布置的存储区101的半导体装置100时,根据半导体装置的操作标准选择的存储体不同于在上述存储体组模式中选择的存储体。在基于存储体组模式的idd4r/idd4w模式的情况下,对第二存储体组bg1的第三存储体ba2和第三存储体组bg2的第三存储体ba2执行连续的读取/写入操作。然而,当半导体装置100根据基于8存储体模式的idd4r/idd4w模式来操作时,对第二存储体组bg1的第三存储体ba2和第四存储体组bg3的第三存储体ba2执行连续的读取/写入操作。结果,在8存储体模式中,所选存储体之间的物理距离增加,大于在存储体组模式中。因此,在信号线负载增加的同时,电流消耗增加。

39.因此,在本实施例中,如图3b的右侧所示,不改变存储区101的存储体的物理布置,并且即便在8存储体模式中,也可以以与存储体组模式相同的方式通过地址控制来选择彼此最接近且在顺序上具有相同编号的存储体。也就是说,可以通过地址控制将第三存储体组bg2和第四存储体组bg3分别识别为第三存储体组bg2和第四存储体组bg3。

40.结果,根据本实施例的半导体装置可以保持存储体的物理位置,这些存储体的物理位置被布置为减少存储体组模式中的电流消耗。同时,即便在8存储体模式中,也可以以与存储体组模式相同的方式通过地址控制来选择彼此最接近且在顺序上具有相同编号的存储体,从而降低电流消耗。

41.在下文中,将参考图4和图5描述根据本实施例的地址映射改变操作的电路配置。

42.图4是示出根据实施例的地址控制电路105-1的配置的图。

43.参考图4,地址控制电路105-1可以包括模式设置电路110、地址时序控制电路200和地址多路复用电路400。

44.模式设置电路110可以基于预设的存储器访问模式来产生访问模式信号,例如第一访问模式信号和第二访问模式信号。第一访问模式信号可以被称为存储体组模式信号bgmd,且第二访问模式信号可以被称为8存储体模式信号8bkmd。当半导体装置100的存储器访问模式被设置为8存储体模式时,8存储体模式信号8bkmd可以被产生为高电平,并且当存储器访问模式没有被设置为8存储体模式时,8存储体模式信号8bkmd可以被产生为低电平。当半导体装置100的存储器访问模式被设置为存储体组模式时,存储体组模式信号bgmd可以被产生为高电平,并且当存储器访问模式没有被设置为存储体组模式时,存储体组模式信号bgmd可以被产生为低电平。

45.模式设置电路110可以根据控制信号ctrl来产生8存储体模式信号8bkmd和存储体组模式信号bgmd。模式设置电路110可以包括模式寄存器组和熔丝组中的至少一个。当模式设置电路110被配置为模式寄存器组时,可以使用模式寄存器写入命令作为控制信号ctrl。当模式设置电路110被配置为熔丝组时,可以使用用于熔丝组编程的信号(例如,测试模式信号)作为控制信号ctrl。

46.地址时序控制电路200可以锁存从半导体装置100的外部输入的地址信号add,以

预定时序顺序地储存锁存的信号,并且将所储存的信号输出作为存储体组地址bg《0:1》和存储体地址ba《0:1》。地址时序控制电路200可以包括地址锁存器210和管道寄存器220。

47.地址锁存器210可以锁存从半导体装置100的外部输入的地址信号add并且输出锁存的信号。通过参考图1描述的命令和地址集成引脚ca,可以顺序地输入命令和地址信号add。地址信号add可以包括用于存储体组选择、存储体选择和列访问的地址信号。

48.管道寄存器220可以以预定时序顺序地储存从地址锁存器210输出的信号,并将所储存的信号输出作为存储体组地址bg《0:1》和存储体地址ba《0:1》。尽管未示出,但管道寄存器220还可以储存和输出与半导体装置100的列访问有关的地址。

49.地址多路复用电路400可以根据访问模式信号8bkmd和bgmd来执行改变存储体组地址bg《0:1》的值的地址映射改变操作。地址多路复用电路400可以通过以根据8存储体模式信号8bkmd和存储体组模式信号bgmd的不同方式控制存储体组地址bg《0:1》来产生存储体组选择信号addlatp_bg《0:3》。尽管存储体组地址bg《0:1》的值随着半导体装置100的存储器访问模式的改变而改变,但是地址多路复用电路400可以产生具有相同值的存储体组选择信号addlatp_bg《0:3》。当假设在半导体装置100的存储器访问模式被设置为存储体组模式时输入的存储体组地址bg《0:1》具有值

‘

01’时,在8存储体模式中,存储体组地址bg《0:1》可以被输入为值

‘

10’,这与在存储体组模式中的不同。

50.当存储体组模式信号bgmd具有高电平或者半导体装置100的存储器访问模式被设置为存储体组模式时,地址多路复用电路400可以根据具有第一值(例如

‘

x’)的存储体组地址bg《0:1》来产生具有第二值(例如

‘

z’)的存储体组选择信号addlatp_bg《0:3》。当8存储体模式信号8bkmd具有高电平或半导体装置100的存储器访问模式被设置为8存储体模式时,即使具有不同于第一值(例如

‘

x’)的第三值(例如

‘

y’)的存储体组地址bg《0:1》被输入,地址多路复用电路400也可以产生具有第二值(例如

‘

z’)的存储体组选择信号addlatp_bg《0:3》。地址多路复用电路400可以根据存储体地址ba《0:1》来产生存储体选择信号cbank《0:3》。

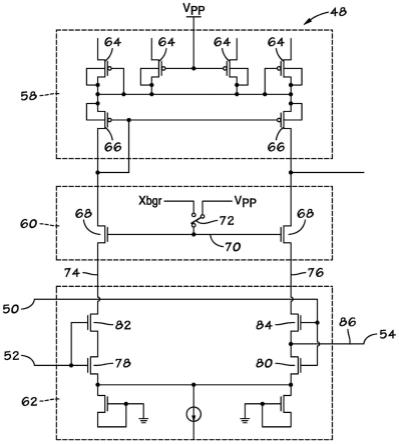

51.图5是示出根据实施例的地址多路复用电路400的配置的图。

52.参考图5,地址多路复用电路400可以包括存储体组地址多路复用电路500和存储体地址多路复用电路600。

53.存储体组地址多路复用电路500可以根据存储体组地址bg《0:1》、8存储体模式信号8bkmd和存储体组模式信号bgmd来产生存储体组选择信号addlatp_bg《0:3》。

54.存储体组地址多路复用电路500可以包括地址多路复用器501和解码电路502。地址多路复用器501可以通过根据8存储体模式信号8bkmd和存储体组模式信号bgmd选择性地组合存储体组地址bg《0:1》的地址比特位来产生预解码信号bgb《1》、bgd《1》、bgb《0》和bgd《0》。地址多路复用器501可以包括多个逻辑门511至513和521至523。第一逻辑门511可以根据8存储体模式信号8bkmd和存储体组模式信号bgmd来将通过对存储体组地址bg《0》反相而获得的信号输出作为第一预解码信号bgb《1》。当半导体装置100的存储器访问模式是8存储体模式时,8存储体模式信号8bkmd可以被设置为高电平,并且存储体组模式信号bgmd可以被设置为低电平。当半导体装置100的存储器访问模式是存储体组模式时,8存储体模式信号8bkmd可以被设置为低电平,并且存储体组模式信号bgmd可以被设置为高电平。当半导体装置100的存储器访问模式是8存储体模式时,第一逻辑门511可以将通过对存储体组地址

bg《0》反相而获得的信号输出作为第一预解码信号bgb《1》。当半导体装置100的存储器访问模式是存储体组模式时,无论存储体组地址bg《0》的电平如何,第一逻辑门511可以将其输出端子的电平保持为初始电平。

55.第二逻辑门512可以根据8存储体模式信号8bkmd和存储体组模式信号bgmd来将通过对存储体组地址bg《1》反相获得的信号输出作为第一预解码信号bgb《1》。当半导体装置100的存储器访问模式是存储体组模式时,第二逻辑门512可以将通过对存储体组地址bg《1》反相而获得的信号输出作为第一预解码信号bgb《1》。当半导体装置100的存储器访问模式是8存储体模式时,无论存储体组地址bg《1》的电平如何,第二逻辑门512可以将其输出端子的电平保持为初始电平。第三逻辑门513可以将通过对第一预解码信号bgb《1》反相而获得的信号输出作为第二预解码信号bgd《1》。

56.当半导体装置100的存储器访问模式是8存储体模式时,第四逻辑门521可以将通过对存储体组地址bg《1》反相而获得的信号输出作为第三预解码信号bgb《0》。当半导体装置100的存储器访问模式是存储体组模式时,无论存储体组地址bg《1》的电平如何,第四逻辑门521可以将其输出端子的电平保持为初始电平。

57.当半导体装置100的存储器访问模式是存储体组模式时,第五逻辑门522可以将通过对存储体组地址bg《0》反相而获得的信号输出作为第三预解码信号bgb《0》。当半导体装置100的存储器访问模式是8存储体模式时,无论存储体组地址bg《0》的电平如何,第五逻辑门522可以将其输出端子的电平保持为初始电平。第六逻辑门523可以将通过对第三预解码信号bgb《0》反相而获得的信号输出作为第四预解码信号bgd《0》。

58.解码电路502可以将通过对第一预解码信号bgb《1》、第二预解码信号bgd《1》、第三预解码信号bgb《0》和第四预解码信号bgd《0》进行解码而获得的信号输出作为存储体组选择信号addlatp_bg《0:3》。解码电路502可以包括多个逻辑门531至534。

59.第一逻辑门531可以将通过对第三预解码信号bgb《0》和第一预解码信号bgb《1》执行与非运算而获得的信号输出作为第一存储体组选择信号addlatp_bg《0》。根据第一存储体组选择信号addlatp_bg《0》,可以在多个存储体组bg0至bg3之中选择第一存储体组bg0。

60.第二逻辑门532可以将通过对第四预解码信号bgd《0》和第一预解码信号bgb《1》执行与非运算而获得的信号输出作为第二存储体组选择信号addlatp_bg《1》。根据第二存储体组选择信号addlatp_bg《1》,可以在多个存储体组bg0至bg3之中选择第二存储体组bg1。

61.第三逻辑门533可以将通过对第三预解码信号bgb《0》和第二预解码信号bgd《1》执行与非运算而获得的信号输出作为第三存储体组选择信号addlatp_bg《2》。根据第三存储体组选择信号addlatp_bg《2》,可以在多个存储体组bg0至bg3之中选择第三存储体组bg2。

62.第四逻辑门534可以将通过对第四预解码信号bgd《0》和第二预解码信号bgd《1》执行与非运算而获得的信号输出作为第四存储体组选择信号addlatp_bg《3》。根据第四存储体组选择信号addlatp_bg《3》,可以在多个存储体组bg0至bg3之中选择第四存储体组bg3。

63.如上所述,存储体组地址多路复用电路500可以在存储体组模式和8存储体模式中通过改变存储体组地址bg《0:1》的顺序来对存储体组地址bg《0:1》进行组合和解码。因此,虽然在存储体组模式中输入的存储体组地址bg《0:1》的值与在8存储体模式中输入的存储体组地址bg《0:1》的值不同,但是可以产生具有相同值的存储体组选择信号addlatp_bg《0:3》。

64.存储体地址多路复用电路600可以将通过对存储体地址ba《0:1》进行解码而获得的信号输出作为存储体选择信号cbank《0:3》。根据存储体选择信号cbank《0:3》,可以在多个存储体组bg0至bg3中的每一个的多个存储体ba0至ba3之中选择一个存储体。

65.虽然已经在上面描述了各种实施例,但是本领域技术人员将理解这些实施例仅代表示例。因此,本文所描述的地址控制电路和半导体装置不应该基于所描述的实施例来限制。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。