1.本发明涉及半导体光刻工艺技术领域,特别是涉及一种掩膜版图形修正方法、掩膜版制备方法及掩膜版。

背景技术:

2.随着超大规模集成电路(ulsi,ultra large scale integration)的飞速发展,集成电路制造工艺变得越来越复杂和精细。在0.18μm及以下技术节点的关键层次中,如to(有源区层次)、gt(栅氧层次)以及an(金属连线层次)等关键层次的cd(关键尺寸)越来越小,某些关键层次的cd已经接近甚至小于光刻工艺中所使用的光波的波长248nm,因此在光刻的曝光过程中,由于光的干涉和衍射现象,实际产品在晶片上得到的光刻图形与原始图形存在一定的变形和偏差,光刻中的这种误差直接影响电路性能和生产成品率。

3.为了消除上述误差,通常使用opc(光学邻近效应矫正)方法对设计图形进行一定的修正。但是opc修正后的图形制备到掩膜版上时,会经过掩膜厂的曝光机,掩膜版经过该曝光机的曝光会产生差异。而当前的opc修正过程中是以客户给出的设计图形为目标来进行opc修正,没有将掩膜版在制版的曝光机曝光过程中的上述差异补偿进去,所以制备出来的图形与opc修正后的图形同样存在差异。尤其在corner rounding(掩膜版上图形转角处允许的最大内径尺寸)问题上,由于目前opc修正通常采用的做法是确保1d(1d在opc修正中通常指设计图形中的关键部位形貌,该关键部位形貌包括但不限于非转角处的线条形貌)做到位,牺牲转角(corner)部分,没有考虑到制版厂在出版时对转角(corner)部分也有要求。此外,制版厂针对不同等级的版子的corner rounding值不一样,这将导致掩膜厂在有些高等级版子上因为此值达不到要求,从而不能制版。

技术实现要素:

4.鉴于以上所述现有技术的缺点,本发明的目的在于提供一种掩膜版图形修正方法、掩膜版制备方法及掩膜版,用于解决现有技术中opc修正过程中没有考虑掩膜版制版时,曝光机曝光造成的差异,导致掩膜版转角尺寸偏差较大而需要重新制版或者不能制版等的问题。

5.为实现上述目的及其他相关目的,本发明提供一种掩膜版图形修正方法,所述修正方法包括:

6.建立opc模型;

7.提供设计图形,获取设计图形数据;

8.根据制版厂反馈的设计图形中的转角图形的角圆误差值及晶圆的线上工艺参数对所述转角图形进行数据预设涨缩,获得预处理的设计图形数据;

9.根据所述opc模型,对所述预处理的设计图形数据进行opc修正。

10.可选地,所述提供设计图形,获取所述设计图形数据还包括,对获取的所述设计图形数据进行逻辑运算处理的步骤。

11.可选地,所述转角图形包括凸转角图形及凹转角图形。

12.可选地,所述opc为基于模型的opc或基于经验的opc。

13.可选地,所述根据所述opc模型,对所述预处理的设计图形数据进行opc修正,还包括:

14.验证所述opc修正后的设计图形的尺寸与目标尺寸的差值是否处于预设范围内;

15.如果是,则结束opc修正;

16.如果否,则对所述转角图形的所述数据预设涨缩进行调整,获得调整后的预处理的设计图形数据,并对调整后的所述预处理的设计图形数据进行opc修正,直至调整后获得的所述opc修正后的图形的尺寸与目标尺寸的差值处于所述预设范围内,则结束opc修正。

17.进一步地,将调整后获得的所述opc修正后的图形的尺寸与目标尺寸的差值处于所述预设范围内的所述转角图形的所述数据预设涨缩写进opc程序中。

18.可选地,所述修正方法用于0.18μm以下的工艺节点。

19.本发明还提供一种掩膜版的制备方法,包括如上所述的掩膜版图形修正方法。

20.可选地,所述掩膜版的制备方法还包括按照所述opc修正后的设计图形数据制作掩膜版的步骤。

21.本发明还提供一种掩膜版,所述掩膜版由以上所述的掩膜版的制备方法制备得到。

22.如上所述,本发明的掩膜版图形修正方法、掩膜版的制备方法及掩膜版,充分考虑了制版厂对转角部分需要做到的cd的要求,并结合晶圆的线上工艺参数要求,对转角图形进行预处理,即对转角图形进行数据预设涨缩,后续以此预处理后的设计图形数据为目标进行opc修正,以达到在不影响线上工艺的情况下,可以对制备掩膜版过程中曝光机在corner rounding部分的差异进行opc调整,从而使得corner rounding差异减小达到制版厂的制版要求,使制版厂可以正常制版。也即,既能消除opc修正后的图形与制版厂制备得到的掩膜版上的图形差异,满足制版厂要求,又确保了在半导体器件制作的光刻过程中基于该掩膜版能获得准确的曝光图形。

附图说明

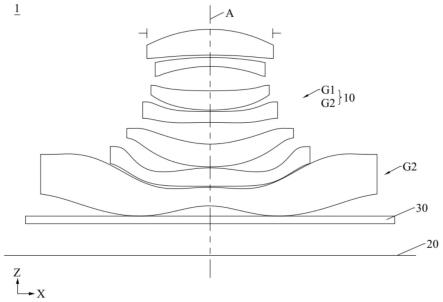

23.图1显示为一实施例中to层次的设计图形。

24.图2显示为一实施例中以to层次的设计图形为目标进行opc修正后制作的掩膜版图形。

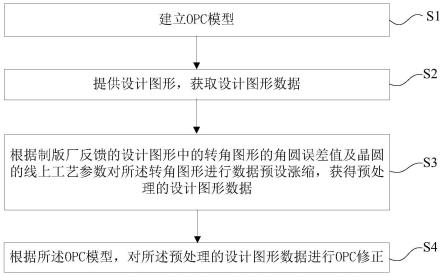

25.图3显示为本发明实施例一的掩膜版图形修正方法的流程示意图。

26.图4显示为采用本发明实施例一掩膜版图形修正方法对图1的to层次的设计图形中的转角图形进行数据预设涨缩后得到的预处理的设计图形数据。

27.图5显示为对图4中的预处理的设计图形数据根据opc模型进行opc修正后制作的掩膜版图形。

28.图6显示为用图2及图5中的掩膜版上的图形进行晶圆工艺仿真得到的图形与to层次的设计图形的对比图。

29.元件标号说明

30.10

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

to层次的设计图形

31.11

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

to层次预处理的设计图形

32.12

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

to层次的掩膜版图形

33.s1~s4

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

步骤

具体实施方式

34.以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。

35.请参阅图1至图6。需要说明的是,本实施例中所提供的图示仅以示意方式说明本发明的基本构想,遂图示中仅显示与本发明中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的型态、数量及比例可根据实际需要进行改变,且其组件布局型态也可能更为复杂。

36.实施例一

37.正如背景技术部分所述,由于光学效应的存在,目前的opc修正通常采用的做法是确保1d做到位,牺牲转角(corner)部分,从而会使转角部分圆角化,在此基础上,传统的opc修正过程中是以客户给出的设计图形为目标来进行opc修正,而opc修正后的图形在制备到掩膜版上时,还需要经过掩膜厂的曝光机曝光,这一曝光过程会对opc修正后的图形产生影响,引起差异,尤其是采用确保1d做到位,牺牲转角(corner)部分的做法会使转角部分圆角化的更厉害,从而达不到出版要求,需要重新制版或者不能制版。

38.如图1、图2及图6所示,以to层次为例,首先如图1所示,提供to层次的设计图形,该to层次的设计图形中包括四个转角a、b、c、d;然后采用现有的以客户给出的设计图形为目标并采用确保1d做到位,牺牲转角(corner)部分的做法进行opc修正并制版,得到如图2所示的掩膜版图形;最后用如图2所示的掩膜版图形进行晶圆工艺仿真,得到晶圆(wafer)上曝光后的仿真图形,如图6中的线条1。从图6中的线条1中可以看出为了确保1d做到位,转角部分的圆角化非常厉害,这样的结果可能会导致达不到出版要求,降低制版厂的出版成功率。

39.发明人基于对以上问题进行分析,充分考虑了掩膜版制版时经曝光机曝光造成的差异,提出了一种掩膜版图形修正方法,该修正方法包括以下步骤:

40.如图3所示,首先进行步骤s1,建立opc模型。

41.作为示例,建立opc模型的过程包括:

42.首先,根据工艺规格,确定光刻工艺参数,由于生产不同的半导体器件,所使用到的光刻工艺具有很大差别,即使在同一半导体器件在制作过程中,也需要进行多道光刻工艺,比如to(有源区层次),gt(栅氧层次),an(金属连线层次)等。在这些不同层次上进行的光刻工艺,所使用到的工艺规格都不相同,因此先要根据所需要实现的器件功能确定半导体器件的工艺规格,并根据工艺要求,确定图形的特征尺寸。在得到工艺规格之后,还需要确定光刻工艺的具体参数,所述光刻工艺具体参数包括曝光光路的光学参数、光刻胶的材料参数以及刻蚀工艺的化学参数。所述曝光光路的光学参数主要指光路的数值孔径、缩放倍率以及曝光光源等具体参数。所述光刻胶的材料参数主要是指光刻胶材料的分辨率、曝

光速率、光敏度等具体参数。所述刻蚀工艺的化学参数主要是指刻蚀剂的酸碱性以及化学性质等具体参数。由于制作不同等级特征尺寸所采用到的光刻工艺不同,因此需要对光刻工艺参数有个明确的定位。这样做的必要之处在于,在接下来确定光学临近效应的临界点时,由于不同的光刻工艺参数所涉及的临界点是不一样的,比如在0.13μm工艺和0.18μm工艺中,临界点就存在几十至几百纳米的差别,因此需要针对不同的光刻工艺,确定不同的临界点。

43.然后,根据所述光刻工艺参数确定opc模型,建立光学临近修正的运算程序。作为示例,光学临近修正的运算程序为opc菜单(opc recipe)中的opc程序,在确定完光刻工艺参数后,可以进行opc建模。建模的基本流程如下:首先是在标片上放置预先设计的测试图案,收集到一组真实光刻晶片的数据。然后使用同样的测试图案,利用opc建模工具进行模拟,如果模拟得到的图案尺寸与相对应的真实晶片数据能够很好的符合,那么就可以认为在这样一个有限的样品空间(sampling space)中,模拟得到的模型能够很好的描述整个曝光系统和化学效应,因此就能用来定量在预知情况下的ope效应,从而可以用来进行opc处理。在工厂端,由于厂家在多数情况下会对自家生产的产品工艺建有相应的数据库,因此建模过程也可简化为调取数据的过程,只需输入相对应的数据模型,就能调取到所需的opc模型。在建完opc模型后,还需要编写opc程序,将适用的掩膜图形进行opc处理。作为示例,在opc菜单(opc recipe)中,opc程序调取和采用所需opc模型进行opc运算。

44.作为示例,所述opc为基于模型的opc或基于经验的opc。

45.如图3所示,然后进行步骤s2,提供设计图形,获取设计图形数据,得到设计图形中的转角图形。

46.作为示例,所述提供设计图形,获取所述设计图形数据,还包括,对获取的所述设计图形数据进行逻辑运算处理的步骤。则后续的数据处理,是基于该逻辑运算处理后的数据进行的。

47.如图3所示,接着进行步骤s3,根据制版厂反馈的设计图形中的转角图形的角圆误差值及晶圆的线上工艺参数对所述转角图形进行数据预设涨缩,获得预处理的设计图形数据。所述转角图形可以为所述设计图形中的垂直拐角。例如,当所述转角图形为凸转角图形(即相对于设计图形来说向外凸出的转角图形)时,将所述凸转角图形的数据向外涨设定值;当所述转角图形为凹转角图形(即相对于设计图形来说向内凹陷的转角图形)时,将所述凹转角图形的数据向内缩设定值。

48.本步骤充分考虑了制版厂对转角部分需要做到的cd的要求,并结合晶圆的线上工艺参数要求,对转角图形进行预处理,即对转角图形进行数据预设涨缩,后续以此预处理后的设计图形数据为目标进行opc修正,以达到在不影响线上工艺的情况下,可以对制版厂曝光机在corner rounding部分的差异进行opc调整,从而使得corner rounding差异减小达到工厂的制版要求,使制版厂可以正常制版。

49.如图3所示,最后进行步骤s4,根据所述opc模型,对所述预处理的设计图形数据进行opc修正。

50.具体地,在对转角图形进行数据预设涨缩后,开始对整个设计图形进行opc修正,此时设计图形中的转角图形是进行了数据预设涨缩后的转角图形,即充分考虑了制版厂的制版工艺及晶圆厂的晶圆制造工艺,实现了两者之间的折中,使在不影响晶圆制造的线上

工艺的情况下,corner rounding差异减小达到制版厂的制版要求,从而制版厂可以正常制版。也即,既能消除opc修正后的图形与制版厂制备得到的掩膜版上的图形差异,满足制版厂要求,又确保了在半导体器件制作的光刻过程中基于该掩膜版能获得准确的曝光图形。

51.作为示例,所述根据所述opc模型,对所述预处理的设计图形数据进行opc修正还包括:

52.验证所述opc修正后的设计图形的尺寸与目标尺寸的差值是否处于预设范围内,这里该预设范围可根据实际情况进行设定;如果是,则结束opc修正;如果否,则对所述转角图形的所述数据预设涨缩进行调整,获得调整后的预处理的设计图形数据,并对调整后的所述预处理的设计图形数据进行opc修正,直至调整后获得的所述opc修正后的图形的尺寸与目标尺寸的差值处于所述预设范围内,得到最终的opc修正后的数据,结束opc修正。较佳地,还可将调整后获得的所述opc修正后的图形的尺寸与目标尺寸的差值处于所述预设范围内的所述转角图形的所述数据预设涨缩写进opc程序中。这尤其适用于在研发初期,可以用opc程式得出多个不同的转角图形数据预设涨缩(即corner cd)的数据,制备到相应等级的掩膜版上,然后进行掩膜版的corner rounding验证,记录下验证通过的条件,后续制备相同等级的掩膜版时就可以将这个条件写进opc的程序里面,这对于与之长期合作的fab和制版厂来说,可以一次性的解决多个等级的corner rounding问题。

53.作为示例,本实施例的掩膜版图形修正方法特别适用于较小的工艺尺寸,例如0.18μm工艺、0.13μm工艺、0.06μm工艺等等。

54.实施例二

55.本实施例提供一种掩膜版的制备方法,该掩膜版的制备方法是基于上述实施例一所述的掩膜版图形修正方法实现的,所以该掩膜版的制备方法所能达到的有益效果可请参见实施例一,以下不再赘述。

56.作为示例,所述制备方法包括将设计图形依照实施例一所述的掩膜版图形修正方法进行opc修正,然后按照所述opc修正后的数据制作掩膜版。较佳地,在制备所述掩膜版的过程中还要进行相应规则的检测,检测没问题即可出版至fab(半导体器件制造厂)。

57.基于该掩膜版的制备方法,本实施例还提供一种掩膜版,通过该实施例的掩膜版的制备方法制备得到。

58.下面以to层次为例对本实施例的掩膜版的制备方法进行举例说明,如图1所示,提供to层次的设计图形,获取该设计图形数据,其中设计图形数据中space》0.3μm,即s1,s2都满足,对width分别为w1,w2,w3进行凸转角和凹转角的补偿。

59.用opc程式选出转角图形及线条端,在图1中转角图形为a、c、d的凸转角图形及b的凹转角图形,根据制版厂反馈的转角图形的角圆误差值及晶圆的线上工艺参数对转角图形进行数据预设涨缩,获得图4的预处理的设计图形数据,其中,转角图形数据预设涨缩为,当space》0.3μm,width>0.42μm时,凸转角图形a、c、d往外张aμm,a>0,width>0.46μm时,凹转角图形b往里缩bμm,b>0。

60.根据opc模型,对图4的预处理的设计图形数据进行opc修正,然后按照opc修正后的数据制作掩膜版得到如图5所示的掩膜版图形。对比图2及图5可看出,凸转角图形a、c、d及凹转角图形b在掩膜版上的尺寸都发生了变化。图2中凸转角图形a在掩膜版上的尺寸为0.032μm、0.036μm,图5中凸转角图形a在掩膜版上的尺寸为(0.032 x)μm,x》a、(0.036 y)μ

m,y》b;图2中凸转角图形c在掩膜版上的尺寸为0.044μm、0.022μm,图5中凸转角图形c在掩膜版上的尺寸为(0.044 x)μm,x》a,(0.022 y)μm,y》b;图2中凸转角图形d在掩膜版上的尺寸为0.039μm、0.022μm,图5中凸转角图形d在掩膜版上的尺寸为(0.039 x)μm,x》a,(0.022 y)μm,y》b;图2中凹转角图形b在掩膜版上的尺寸为0.031μm、0.022μm,图5中凹转角图形b在掩膜版上的尺寸为(0.031 x)μm,x》a、(0.022 y)μm,y》b。在半导体器件制作的光刻过程中,采用该掩膜版进行图形曝光,获得的实际的曝光图形与原始的设计图形间的差异较小,图形曝光的准确性高。

61.接下来对图2及图5中的掩膜版上的图形进行晶圆工艺仿真得到如图6所示的仿真刻蚀图,其中线条1为对图2中的掩膜版上的图形进行晶圆工艺仿真得到的仿真曲线,线条2为对图5中的掩膜版上的图形进行晶圆工艺仿真得到的仿真曲线,可以看出线条1的仿真曲线中转角图形的圆角化非常厉害,但是确保了1d做到位,线条2的仿真曲线中转角图形的圆角化得到缓解,1d的效果被稍微削弱,另外,根据需求也可以调整相应参数,得到图6中的仿真曲线3,仿真曲线3位于仿真曲线1和2之间,也就是说采用本实施例的掩膜版制备方法可以根据不同的晶圆制造工艺及制版厂机台的能力结合起来对设计图形进行预处理调整,从而达到工艺及制版同时满足,使两者折中的效果。

62.这里需要说明的是本实施例中仅以to层次为例对掩膜版的制备方法以及效果进行说明,但并不以此为限,其他opc层次均可以使用本实施例的掩膜版制备方法,例如gt(栅氧层次)以、an(金属连线层次)等均可。

63.综上所述,本发明提供一种掩膜版图形修正方法、掩膜版的制备方法及掩膜版,充分考虑了制版厂对转角部分需要做到的cd的要求,并结合晶圆的线上工艺参数要求,对转角图形进行预处理,即对转角图形进行数据预设涨缩,后续以此预处理后的设计图形数据为目标进行opc修正,以达到在不影响线上工艺的情况下,可以对制备掩膜版过程中曝光机在corner rounding部分的差异进行opc调整,从而使得corner rounding差异减小达到工厂的制版要求,使制版厂可以正常制版。也即,既能消除opc修正后的图形与制版厂制备得到的掩膜版上的图形差异,满足制版厂要求,又确保了在半导体器件制作的光刻过程中基于该掩膜版能获得准确的曝光图形。所以,本发明有效克服了现有技术中的种种缺点而具高度产业利用价值。

64.上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,举凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。