1.本公开涉及集成电路设计技术领域,具体地,涉及一种电流镜电路和供电系统。

背景技术:

2.电流镜电路是模拟集成电路设计领域中最常见的基本单元之一,其噪声影响该电流镜电路所在的芯片的整体噪声,尤其影响电流舵模数转换器的电流镜阵列或者压控振荡器的噪声性能。相关技术中,一般采用电流镜电路中插入rc滤波电路,滤除电流源中的噪声、以及电源或地中的噪声。为了最大程度地滤除噪声,通常rc取值都很大,如此,会导致rc充电时间较长,由于需要对rc充满电之后才能对噪声进行抑制,如此,会导致噪声抑制的效率较低。

技术实现要素:

3.本公开的目的是提供一种电流镜电路和供电系统,以缩短滤波电路的充电时长。

4.为了实现上述目的,本公开第一方面提供一种电流镜电路,所述电路包括:电流源、电流输入模块、镜像电流输出模块、滤波模块和充电控制模块,其中,所述滤波模块位于所述电流输入模块和所述镜像电流输出模块之间;

5.所述电流输入模块与所述电流源相连,用于输入电流;

6.所述滤波模块,用于对流经所述滤波模块的电流进行滤波处理,得到滤波后的电流;

7.所述充电控制模块与所述滤波模块相连,用于根据所述滤波模块的充电状态确定是否对所述滤波模块进行充电,以缩短所述滤波模块的充电时长;

8.所述镜像电流输出模块,用于按照预设倍数对滤波后的电流进行镜像处理,并输出镜像电流。

9.可选地,所述滤波模块包括滤波电阻和滤波电容,所述滤波电阻的第一端与所述电流输入模块相连,所述滤波电阻的第二端分别与所述滤波电容的第一端和镜像电流输出模块相连,所述滤波电容的第二端接地。

10.可选地,所述充电控制模块包括压差检测单元和开关管,所述压差检测单元与所述开关管相连;

11.所述压差检测单元分别与所述滤波电阻的两端相连,用于检测所述滤波电阻两端的电压,并在所述滤波电阻的第一端的电压大于所述滤波电阻第二端的电压时,控制所述开关管导通,以及,在所述滤波电阻的第一端的电压小于或等于所述滤波电阻第二端的电压时,控制所述开关管断开。

12.可选地,所述电流输入模块包括第一晶体管,所述镜像电流输出模块包括第二晶体管;

13.所述第一晶体管的第一端与所述电流源的第一端相连,所述第一晶体管的第二端与所述滤波电阻的第一端相连,所述第一晶体管的第三端用于与第一目标端相连,且所述

第一晶体管的第一端与第二端相连;

14.所述电流源的第二端用于与第二目标端相连;

15.所述第二晶体管的第一端用于与目标电路相连,用于向所述目标电路输出镜像电流,所述第二晶体管的第二端与所述滤波电容的第一端相连,所述第二晶体管的第三端用于与所述第一目标端相连。

16.可选地,在所述第一晶体管为第一nmos管,第二晶体管为第二nmos管时,所述第一目标端为地端,所述第二目标端为电源端;在所述第一晶体管为第一pmos管,第二晶体管为第二pmos管时,所述第一目标端为电源端,所述第二目标端为地端。

17.可选地,所述压差检测单元为运算放大器,所述开关管为第三晶体管;

18.所述运算放大器的输入负端与所述滤波电阻的第一端相连,所述运算放大器的输入正端与所述滤波电阻的第二端相连,所述运算放大器的输出端与所述第三晶体管的第二端相连;

19.所述第三晶体管的第一端与所述滤波电容的第一端相连,所述第三晶体管的第三端与第三目标端相连;

20.其中,若第三晶体管为nmos管则所述第三目标端为地端,若第三晶体管为pmos管则所述第三目标端为电源端。

21.可选地,所述压差检测单元为运算放大器,所述开关管为第四晶体管;

22.所述运算放大器的输入正端与所述滤波电阻的第一端相连,所述运算放大器的输入负端与所述滤波电阻的第二端相连,所述运算放大器的输出端与所述第四晶体管的第二端相连;

23.所述第四晶体管的第三端与所述滤波电容的第一端相连,所述第四晶体管的第一端与第四目标端接地;

24.其中,若第四晶体管为nmos管则第四目标端为电源端,若第四晶体管为pmos则第四目标端为地端。

25.可选地,所述电流源、所述电流输入模块、所述镜像电流输出模块、所述滤波电阻和所述充电控制模块集成设置,所述滤波电容为分立元件。

26.可选地,所述滤波电容为微法级电容。

27.本公开第二方面提供一种供电系统,包括芯片和如本公开第一方面提供的所述的电流镜电路,其中,所述电流镜电路中的所述电流源、所述电流输入模块、所述镜像电流输出模块、所述滤波电阻和所述充电控制模块集成设置在芯片上,所述滤波电容设置在所述芯片之外。

28.采用上述电流镜电路,充电控制模块与滤波模块相连,充电控制模块能够根据滤波模块的充电状态确定是否对滤波模块进行充电,如此,可以增大滤波模块的充电电流,缩短滤波模块的充电时长,从而缩短了噪声抑制的等待时间,有效提升了抑制噪声的效率。

29.本公开的其他特征和优点将在随后的具体实施方式部分予以详细说明。

附图说明

30.附图是用来提供对本公开的进一步理解,并且构成说明书的一部分,与下面的具体实施方式一起用于解释本公开,但并不构成对本公开的限制。在附图中:

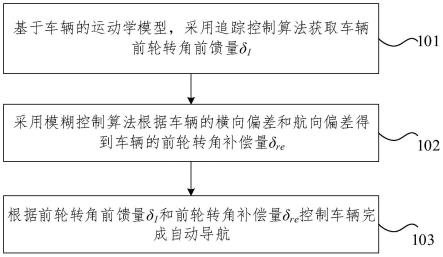

31.图1是根据一示例性实施例示出的一种电流镜电路的框图。

32.图2是根据一示例性实施例示出的一种电流镜电路的电路图。

33.图3是根据一示例性实施例示出的另一种电流镜电路的电路图。

具体实施方式

34.以下结合附图对本公开的具体实施方式进行详细说明。应当理解的是,此处所描述的具体实施方式仅用于说明和解释本公开,并不用于限制本公开。

35.图1是根据一示例性实施例示出的一种电流镜电路的框图。如图1所示,该电流镜电路包括电流源101、电流输入模块102、镜像电流输出模块103、滤波模块104和充电控制模块105。其中,滤波模块104位于电流输入模块102和镜像电流输出模块103之间。

36.如图1所示,电流输入模块102与电流源101相连用于输入电流。滤波模块104用于对流经滤波模块104的电流进行滤波处理,得到滤波后的电流。充电控制模块105与滤波模块104相连,用于根据滤波模块104的充电状态确定是否对滤波模块104进行充电,以缩短滤波模块104的充电时长。镜像电流输出模块103用于按照预设倍数对滤波后的电流进行镜像处理,并输出镜像电流。

37.示例地,在滤波模块104的充电状态为正在充电状态时,充电控制模块105对滤波模块104进行充电,也即是说,除了利用电流源101进行充电之外,还利用充电控制模块105对滤波模块104进行充电,增大滤波模块104的充电电流,进而缩短了滤波模块104的充电时间。

38.此外,在滤波模块104充电末期或充电结束时,即,滤波模块104的充电状态为充电末期状态或充电结束状态时,充电控制模块105不对滤波模块104进行充电。

39.采用上述电流镜电路,充电控制模块与滤波模块相连,充电控制模块能够根据滤波模块的充电状态确定是否对滤波模块进行充电,如此,可以增大滤波模块的充电电流,缩短滤波模块的充电时长,从而缩短了噪声抑制的等待时间,有效提升了抑制噪声的效率。

40.可选地,滤波模块可以包括滤波电阻和滤波电容,其中,滤波电阻的第一端与电流输入模块相连,滤波电阻的第二端分别与滤波电容的第一端和镜像电流输出模块相连,滤波电容的第二端接地。

41.应当理解的是,为了获得更好的滤波效果,滤波电阻的阻值和滤波电容的电容值通常较大,如此,滤波电容充电的时长通常会超过1ms,甚至更长。例如,充电初期,利用电流源对滤波电容进行充电,由于滤波电阻的阻值较大,因此,充电电流较小,滤波电容的电压上升时间就较长,从而导致电容充电的时长较大。在本公开中,在充电过程中,除了利用电流源101对滤波模块104进行充电之外,还可以利用充电控制模块105对滤波模块104进行充电,增大滤波模块104的充电电流,进而实现缩短滤波模块104的充电时长的目的。

42.可选地,电流输入模块102包括第一晶体管,镜像电流输出模块103包括第二晶体管。其中,第一晶体管的第一端与电流源的第一端相连,第一晶体管的第二端与滤波电阻的第一端相连,第一晶体管的第三端用于与第一目标端相连,且第一晶体管的第一端与第二端相连;电流源101的第二端用于与第二目标端相连;第二晶体管的第一端用于与目标电路相连,用于向目标电路输出镜像电流,第二晶体管的第二端与滤波电容的第一端相连,第二晶体管的第三端用于与第一目标端相连。

43.其中,晶体管可以为n型mos管,即nmos管,也可以为p型mos管,即pmos管。在第一晶体管为第一nmos管,第二晶体管为第二nmos管时,第一目标端为地端,第二目标端为电源端。即,第一nmos管的第三端与地端相连,电流源的第二端与电源端相连,第二nmos管的第三端与地端相连。

44.在第一晶体管为第一pmos管,第二晶体管为第二pmos管时,第一目标端为电源端,第二目标端为地端。第一pmos管的第三端与电源端相连,电流源的第二端与地端相连,第二pmos管的第三端与电源端相连。

45.示例地,如图2所示,第一晶体管为第一nmos管nm1,第二晶体管为第二nmos管nm2,nm1的漏极与电流源iin的下端相连,nm1的源极接地,nm1的栅极与滤波电阻r的第一端相连。滤波电阻r的第二端与滤波电容c的上端相连,滤波电容c的下端与地端相连。nm2的栅极与滤波电容c的上端相连,nm2的源极接地,nm2的漏极输出镜像电流。并且,nm1的漏极与栅极相连。其中,nm2输出的镜像电流作为目标电路的输入电流。

46.应当理解的是,在图2中,电流源iin的上端与电源端vdd相连。此外,在图2中并未示出目标电路,在实际应用中,可以根据实际需求将nm2的漏极与相应的目标电路相连。

47.又示例地,如图3所示,第一晶体管为第一pmos管pm1,第二晶体管为第二pmos管pm2,pm1的漏极与电流源iin的上端相连,pm1的源极与电源端vdd相连,pm1的栅极与滤波电阻r的第一端相连。滤波电阻r的第二端与滤波电容c的下端相连,滤波电容c的上端与电源端相连。pm2的栅极与滤波电容c的下端相连,pm2的源极与电源端vdd相连,pm2的漏极输出镜像电流。并且,pm1的漏极与栅极相连。其中,pm2输出的镜像电流作为目标电路的输入电流。

48.应当理解的是,在图3中,电流源iin的下端与地端相连。此外,在图3中并未示出目标电路,在实际应用中,可以根据实际需求将pm2的漏极与相应的目标电路相连。

49.通常情况下,在滤波电容处于充电过程中,滤波电阻两端存在压差,当滤波电容充电结束时,滤波电阻两端的压差接近为0。因此,在一种实施例中,充电控制模块105可以包括压差检测单元和开关管。其中,压差检测单元分别与滤波电阻的两端相连,用于检测滤波电阻两端的电压,并在滤波电阻第一端的电压大于滤波电阻第二端的电压时,控制开关管导通,以增大滤波电容的充电电流,以及,在滤波电阻第一端的电压小于或等于滤波电阻第二端的电压时,控制开关管断开,以减小滤波电容的充电电流。

50.在该实施例的一种实施方式中,压差检测单元为运算放大器,开关管为第三晶体管。其中,运算放大器的输入负端与滤波电阻的第一端相连,运算放大器的输入正端与滤波电阻的第二端相连,运算放大器的输出端与第三晶体管的第二端相连。第三晶体管的第一端与滤波电容的第一端相连,第三晶体管的第三端与第三目标端相连。其中,若第三晶体管为nmos管则第三目标端为地端,若第三晶体管为pmos管则第三目标端为电源端。

51.示例地,如图2所示,假设第三晶体管为pmos,即,第三晶体管为pm3。运算放大器a1的输入负端与滤波电阻r的第一端相连,运算放大器a1的输入正端与滤波电阻r的第二端相连,即,运算放大器a1的输入负端输入的电压为vg,运算放大器a1的输入正端输入的电压为vg_rc。pm3的栅极与运算放大器a1的输出端相连,pm3的源极与电源端相连,pm3的漏极与滤波电容c的上端相连。应当理解的是,运算放大器a1中的电源引脚会与电源端相连,接地引脚会与地端相连。

52.图2所示的电流镜电路的工作原理如下:

53.在上电初始,利用电流源iin为滤波电容c充电,由于滤波电阻r的阻抗较大,滤波电阻r第一端的电压vg大于第二端的电压vg_rc,即,运算放大器a1输出端为低电平,控制pm3导通,从而pm3产生大电流对滤波电容c进行充电。也即是,在pm3导通的情况下,可以通过pm3产生的大电流和电流源iin同时为滤波电容c进行充电,增大了滤波电容c的充电电流,缩短了滤波电容c的充电时间。在充电末期或充电结束时,滤波电阻r两端的电压接近相等,即,vg=vg_rc。此时,运算放大器a1输出端为高电平,pm3不导通,即,pm3的电流为0。如此,使得nm1和nm2能够组成电流镜电路。

54.应当理解的是,在图2中仅示出了第一晶体管和第二晶体管均为nmos第三晶体管为pmos时的电流镜电路,第一晶体管和第二晶体管均为nmos第三晶体管为nmos的电流镜电路与图2所示电路类似,且工作原理与图2所示电路的工作原理相似,本公开对此不作赘述。

55.又示例地,如图3所示,第一晶体管和第二晶体管为pmos管,且第三晶体管为nmos管,即,第一晶体管为pm1第二晶体管为pm2第三晶体管为nm3。如图3所示,运算放大器a1的输入负端与滤波电阻r的第一端相连,运算放大器a1的输入正端与滤波电阻r的第二端相连,即,运算放大器a1的输入负端输入的电压为vg,运算放大器a1的输入正端输入的电压为vg_rc。nm3的栅极与运算放大器a1的输出端相连,nm3的源极与地端相连,nm3的漏极与滤波电容c的下端相连。应当理解的是,运算放大器a1中的电源引脚会与电源端相连,接地引脚会与地端相连。

56.图3所示的电流镜电路的工作原理如下:

57.在上电初始,电容c未开始充电时,vg_rc为vdd,运算放大器a1的输出端为高电平,从而导致nm3导通,可以通过nm3产生的大电流和电流源iin同时为滤波电容c进行充电,从而使得流经滤波电容c的电流增大,缩短滤波电容c的充电时长。在充电末期或充电结束时,滤波电阻r两端的电压几乎相等,运算放大器a1的输出端为低电平,nm3不导通,即,nm3的电流为0。如此,使得pm1和pm2能够组成电流镜电路。

58.应当理解的是,在图3中仅示出了第一晶体管和第二晶体管均为pmos第三晶体管为nmos时的电流镜电路,第一晶体管和第二晶体管均为pmos第三晶体管为pmos的电流镜电路与图3所示电路类似,并工作原理与图3所示电路的工作原理相似,本公开对此不作赘述。

59.采用上述电流镜电路,在滤波电阻的阻值和滤波电容的电容值设置为很大,以实现较好的噪声抑制效果的同时,还可以缩短滤波电容的充电时长,缩短抑制噪声的等待时长,有效提升了抑制噪声的效率。

60.此外,考虑到电流镜电路通常是集成在芯片上,芯片的体积较小,电流镜电路的体积不易过大,而滤波电容的电容值越大其体积就越大,因此,在一种实施例中,将电流源、电流输入模块、镜像电流输出模块、滤波电阻和充电控制模块集成设置,滤波电容为分立元件。这样,电流源、电流输入模块、镜像电流输出模块、滤波电阻和充电控制模块可以集成设置在芯片上,滤波电容设置在芯片之外。如此,在实际应用中,可以根据需求采用电容值较大的滤波电容,以实现更好的噪声抑制效果,进一步提升了抑制噪声的效率。

61.示例地,为了实现更好的噪声抑制效果,通常滤波电容为微法级电容,即,滤波电容的电容值为微法级。

62.基于同一构思,本公开还提供一种供电系统,该供电系统包括芯片和本公开提供

的电流镜电路,其中,电流镜电路中的电流源、电流输入模块、镜像电流输出模块、滤波电阻和所述充电控制模块集成设置在芯片上,滤波电容设置在所述芯片之外。

63.示例地,该供电系统中的镜像电流输出模块与目标电路相连,用于向目标电路输入镜像电流。

64.以上结合附图详细描述了本公开的优选实施方式,但是,本公开并不限于上述实施方式中的具体细节,在本公开的技术构思范围内,可以对本公开的技术方案进行多种简单变型,这些简单变型均属于本公开的保护范围。

65.另外需要说明的是,在上述具体实施方式中所描述的各个具体技术特征,在不矛盾的情况下,可以通过任何合适的方式进行组合。为了避免不必要的重复,本公开对各种可能的组合方式不再另行说明。

66.此外,本公开的各种不同的实施方式之间也可以进行任意组合,只要其不违背本公开的思想,其同样应当视为本公开所公开的内容。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。