技术特征:

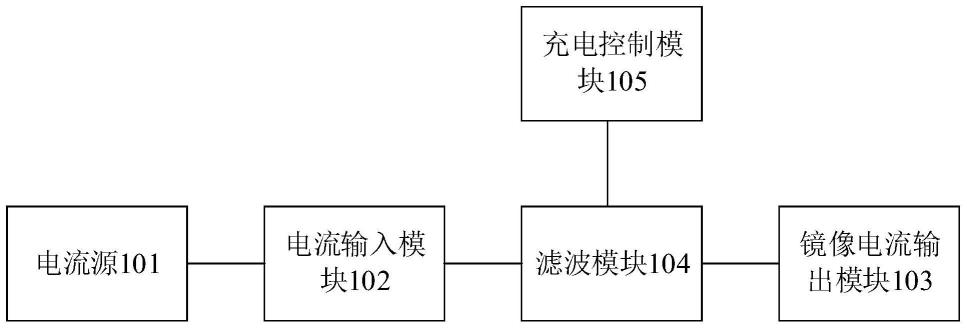

1.一种电流镜电路,其特征在于,所述电路包括:电流源、电流输入模块、镜像电流输出模块、滤波模块和充电控制模块,其中,所述滤波模块位于所述电流输入模块和所述镜像电流输出模块之间;所述电流输入模块与所述电流源相连,用于输入电流;所述滤波模块,用于对流经所述滤波模块的电流进行滤波处理,得到滤波后的电流;所述充电控制模块与所述滤波模块相连,用于根据所述滤波模块的充电状态确定是否对所述滤波模块进行充电,以缩短所述滤波模块的充电时长;所述镜像电流输出模块,用于按照预设倍数对滤波后的电流进行镜像处理,并输出镜像电流。2.根据权利要求1所述的电流镜电路,其特征在于,所述滤波模块包括滤波电阻和滤波电容,所述滤波电阻的第一端与所述电流输入模块相连,所述滤波电阻的第二端分别与所述滤波电容的第一端和镜像电流输出模块相连,所述滤波电容的第二端接地。3.根据权利要求2所述的电流镜电路,其特征在于,所述充电控制模块包括压差检测单元和开关管,所述压差检测单元与所述开关管相连;所述压差检测单元分别与所述滤波电阻的两端相连,用于检测所述滤波电阻两端的电压,并在所述滤波电阻的第一端的电压大于所述滤波电阻的第二端的电压时,控制所述开关管导通,以及,在所述滤波电阻的第一端的电压小于或等于所述滤波电阻第二端的电压时,控制所述开关管断开。4.根据权利要求3所述的电流镜电路,其特征在于,所述电流输入模块包括第一晶体管,所述镜像电流输出模块包括第二晶体管;所述第一晶体管的第一端与所述电流源的第一端相连,所述第一晶体管的第二端与所述滤波电阻的第一端相连,所述第一晶体管的第三端用于与第一目标端相连,且所述第一晶体管的第一端与第二端相连;所述电流源的第二端用于与第二目标端相连;所述第二晶体管的第一端用于与目标电路相连,用于向所述目标电路输出镜像电流,所述第二晶体管的第二端与所述滤波电容的第一端相连,所述第二晶体管的第三端用于与所述第一目标端相连。5.根据权利要求4所述的电流镜电路,其特征在于,在所述第一晶体管为第一nmos管,第二晶体管为第二nmos管时,所述第一目标端为地端,所述第二目标端为电源端;在所述第一晶体管为第一pmos管,第二晶体管为第二pmos管时,所述第一目标端为电源端,所述第二目标端为地端。6.根据权利要求5所述的电流镜电路,其特征在于,所述压差检测单元为运算放大器,所述开关管为第三晶体管;所述运算放大器的输入负端与所述滤波电阻的第一端相连,所述运算放大器的输入正端与所述滤波电阻的第二端相连,所述运算放大器的输出端与所述第三晶体管的第二端相连;所述第三晶体管的第一端与所述滤波电容的第一端相连,所述第三晶体管的第三端与第三目标端相连;其中,若第三晶体管为nmos管则所述第三目标端为地端,若第三晶体管为pmos管则所

述第三目标端为电源端。7.根据权利要求5所述的电流镜电路,其特征在于,所述压差检测单元为运算放大器,所述开关管为第四晶体管;所述运算放大器的输入正端与所述滤波电阻的第一端相连,所述运算放大器的输入负端与所述滤波电阻的第二端相连,所述运算放大器的输出端与所述第四晶体管的第二端相连;所述第四晶体管的第三端与所述滤波电容的第一端相连,所述第四晶体管的第一端与第四目标端接地;其中,若第四晶体管为nmos管则第四目标端为电源端,若第四晶体管为pmos则第四目标端为地端。8.根据权利要求2所述的电流镜电路,其特征在于,所述电流源、所述电流输入模块、所述镜像电流输出模块、所述滤波电阻和所述充电控制模块集成设置,所述滤波电容为分立元件。9.根据权利要求1-8中任一项所述的电流镜电路,其特征在于,所述滤波电容为微法级电容。10.一种供电系统,其特征在于,包括芯片和如权利要求2-9中任一项所述的电流镜电路,其中,所述电流镜电路中的所述电流源、所述电流输入模块、所述镜像电流输出模块、所述滤波电阻和所述充电控制模块集成设置在芯片上,所述滤波电容设置在所述芯片之外。

技术总结

本公开涉及一种电流镜电路和供电系统。电流镜电路包括:电流源、电流输入模块、镜像电流输出模块、滤波模块和充电控制模块,滤波模块位于电流输入模块和镜像电流输出模块之间;电流输入模块与电流源相连用于输入电流;滤波模块用于对流经滤波模块的电流进行滤波处理,得到滤波后的电流;充电控制模块与滤波模块相连用于根据滤波模块的充电状态确定是否对滤波模块进行充电,以缩短滤波模块的充电时长;镜像电流输出模块用于按照预设倍数对滤波后的电流进行镜像处理,并输出镜像电流。如此,可以增大滤波模块的充电电流,缩短滤波模块的充电时长,从而缩短了噪声抑制的等待时间,有效提升了抑制噪声的效率。升了抑制噪声的效率。升了抑制噪声的效率。

技术研发人员:王本川 黄强 王彦浩

受保护的技术使用者:北京思凌科半导体技术有限公司

技术研发日:2022.08.30

技术公布日:2022/12/16

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。