1.本发明总体上涉及用于锁相环(pll)的系统和方法,并且在特定实施方式中,涉及用于具有并联相位检测电路的pll的系统和方法。

背景技术:

2.由于诸如硅锗(sige)的低成本半导体技术和精细几何互补金属氧化物半导体(cmos)工艺的快速发展,在毫米波频率领域中的应用在过去几年中已经引起了极大的关注。高速双极和金属氧化物半导体(mos)晶体管的可用性已经导致了对用于以60ghz、77ghz和80ghz以及超过100ghz的毫米波应用的集成电路的需求不断增长。这样的应用包括例如机动车辆雷达系统和多千兆比特通信系统。

3.毫米波系统中的关键部件之一是用于调谐射频(rf)振荡器的pll。本质上,pll是反馈回路,其接收相对较低频率的时钟信号,并将rf振荡器调谐到具有该时钟信号频率的预定倍数的频率。pll通常包括提供高频周期信号的rf振荡器、将高频周期分成低频信号的分频器电路、将低频信号的相位与参考时钟的相位进行比较的相位检测器、以及对相位检测器的输出进行滤波以提供用于调谐rf振荡器的信号的环路滤波器。

4.在工作期间,pll环路为参考路径中存在的相位噪声(例如,由于参考时钟和相位检测器引起的噪声)提供低通特性,并且为振荡器生成的相位噪声提供高通特性。因此,在低于pll带宽的频率下,pll会衰减振荡器相位噪声并通过参考路径噪声,而在高于pll带宽的频率下,pll会衰减参考路径噪声并通过振荡器相位噪声。因此,在低相位噪声振荡器可用的系统中配置具有低带宽的pll是很常见的。以这种方式,可以在很宽的频率范围内抑制相对大量的参考路径噪声,以换取相对安静的振荡器的噪声占主导地位。

5.然而,具有低相位噪声特性的rf振荡器难以在毫米波频率下设计,因为在这些高频下电容器品质因数下降并且寄生效应增加。毫米波频率下相位噪声性能的提高通常以增加的功耗和增加的芯片面积为代价。减少由rf振荡器生成的pll相位的量的一种方法是使用具有高带宽的pll来控制振荡器的频率。然而,pll的带宽的增加以参考路径噪声的相应的增加为代价。

技术实现要素:

6.根据实施方式,一种操作锁相环(pll)的方法,该方法包括:使用多个并联匹配的相位检测电路将参考信号的相位与时钟信号的相位进行比较,以提供多个相位检测信号,其中,多个并联匹配的相位检测电路中的每一个被配置成与输出特性具有相同的相位差;对多个相位检测信号之和进行滤波,以形成经滤波的相位检测信号;以及使用经滤波的相位检测信号来控制振荡器的频率,其中,该振荡器被配置成提供时钟信号。

7.根据另一实施方式,一种锁相环(pll)包括:多个并联匹配的相位检测电路,多个并联匹配的相位检测电路中的每一个包括耦接至参考信号节点的第一输入端、耦接至时钟信号节点的第二输入端、以及被配置成提供相应的相位检测信号的输出端,其中,多个并联

匹配的相位检测电路中的每一个被配置成与输出特性具有相同的相位差;环路滤波器,其耦接至多个并联匹配的相位检测电路的输出端;以及振荡器,其具有耦接至环路滤波器的输出端的频率控制输入端,其中,该振荡器被配置成提供时钟信号。

8.根据另一实施方式,一种锁相环(pll)包括:多个并联耦接的相位检测信号路径,每个相位检测信号路径包括数字时间转换器和时间数字转换器,时间数字转换器的输入端耦接至数字时间转换器的输出端,其中,多个相位检测信号路径中的每一个被配置成将相同的相位检测特性应用于参考信号与分频时钟信号之间的相位差;求和电路,其耦接至多个相位检测信号路径中的每一个的输出端;数字环路滤波器,其耦接至求和电路的输出端;数控振荡器(dco),其耦接至数字环路滤波器的输出端;分频器,其耦接在dco的输出端与多个相位检测信号路径之间,该分频器被配置成提供分频时钟信号;δ-σ调制器,其输出端耦接至分频器的模控输入端;以及减法电路,其输入端耦接至δ-σ调制器的输入端和δ-σ调制器的输出端并且其输出端耦接至多个相位检测信号路径的每个数字时间转换器的延迟控制输入端。

附图说明

9.为了更完整地理解本发明及其优点,现在参照结合附图给出的以下描述,在附图中:

10.图1a示出了根据实施方式的pll的框图;图1b示出了比较实施方式pll和常规pll的相位噪声性能的曲线图;以及图1c示出了根据另一实施方式的pll的框图;

11.图2a示出了根据实施方式的pll的框图;以及图2b示出了实施方式相位检测信号路径的示意图;

12.图3a示出了根据实施方式的全数字pll;图3b示出了时间数字转换器电路;图3c、图3d和图3e示出了根据另一实施方式的全数字pll;以及图3f示出了在反馈路径中包括可编程整数分频器的adpll的实施方式;

13.图4a和图4b示出了实施方式校准电路连同实施方式相位检测信号路径的框图;

14.图5a和图5b示出了结合了根据实施方式的pll的rf系统的框图;

15.图6示出了根据实施方式的方法的框图。

具体实施方式

16.下面详细讨论本优选实施方式的形成和使用。然而,应该理解,本发明提供了许多可应用的发明构思,这些发明构思可以在各种特定的上下文中实施。所讨论的特定实施方式仅说明制造和使用本发明的特定方式,并且不限制本发明的范围。

17.在一个实施方式中,pll包括两个或更多个并联匹配相位检测电路。通过使用并联匹配相位检测电路,与使用单个相位检测电路相比,由pll的相位检测功能生成的输入参考噪声的量可以减少。

18.图1a示出了根据本发明的实施方式的pll 100。如图所示,pll 100包括m个并联耦接的相位检测电路102、环路滤波器104、振荡器106和时钟分频器108。在工作期间,每个相位检测电路102将参考信号f

ref

的相位与分频时钟f

div

的相位进行比较,以形成多个相位比较信号,这些相位比较信号由求和器103组合并进一步由环路滤波器104滤波。在一些实施

方式中,参考信号f

ref

可以被称为“参考时钟f

ref”,相位检测电路102的参考时钟输入可以被称为“参考信号节点”,并且相位检测电路102的分频时钟信号输入可以被称为“时钟信号节点”,以及相位比较信号可以被称为“相位检测信号”。在各种实施方式中,m个相位检测电路102彼此匹配并且被配置成与输出特性具有相同的相位差。例如,m个相位检测电路102中的每一个可以与输出特性具有相同的输入,例如与输出变量特性具有相同的输入相位差。输出变量可以包括但不限于电压、电流或数字代码。因此,相位检测电路102的输出可以使用由求和器103表示的电压求和器或数字加法器进行组合。相位检测电路102可以被标称地设计为相同的。

19.由环路滤波器104产生的频率控制信号f

osc

用于控制产生输出信号f

pll

的振荡器106的频率。在一些实施方式中,pll 100可以实现为模拟pll,其中相位检测电路102使用相位频率检测器(pfd)和电荷泵来实现,环路滤波器104使用模拟滤波器诸如rc滤波器来实现,振荡器106使用具有模拟频率控制输入的振荡器例如下面关于图2a所讨论的压控振荡器(vco)来实现。在其他实施方式中,pll 100可以实现为全数字pll(adpll),其中相位检测器102使用时间数字转换器(tdc)来实现,环路滤波器104使用数字滤波器来实现,振荡器106使用如以下关于图3a和图3c至图3f所讨论的数控振荡器(dco)来实现。时钟分频器108将f

pll

的频率除以因子n

div

。因此,pll 100的输出频率f

pll

可以表示为:

20.f

pll

=n

div

·fref

,

21.其中,f

ref

是参考时钟f

ref

的频率。在各种实施方式中,时钟分频器108可以实现为整数分频器、分数分频器、计数器或如下面关于图3a和图3c所讨论的与分数分频器串联耦接的预分频器。在一些实施方式中,时钟分频器108可以被省略和/或pll 100的输出频率f

pll

可以使用如下面的实施方式中关于图3d所讨论的本领域已知的无分频器分数n pll电路和方法来调整。

22.在各种实施方式中,使用并联相位检测器电路减少了由pll的相位检测功能生成的噪声。通常,与具有单个相位检测电路102相比,具有m个并联耦接的相位检测器电路102导致由pll的相位检测功能贡献的噪声功率的降低。每个相位检测电路102可以相对于相位特性具有基本相同的阈值和/或相同的输出。在一些实施方式中,可以校准每个相位之间的相对延迟以确保通过每个相位检测器的延迟路径匹配。

23.图1b示出了表示图1a所示的pll 100的相位检测电路102的相位噪声贡献的模拟相位噪声相对于频率的曲线图。轨迹122表示具有单相位检测电路102(例如,m=1)的pll 100的相位检测功能的相位噪声贡献,并且轨迹124表示具有两个相位检测电路102(例如,m=2)的pll 100的相位检测功能的相位噪声贡献。从图1b的曲线图可以看出,对于pll带宽(例如,3mhz)内的频率,表示具有两个相位检测电路102的pll的轨迹124具有比表示具有单个相位检测电路的pll的轨迹122低约3db的相位噪声。

24.实施方式pll也可以实现为“无分频器”pll 150,如图1c所示。pll 150类似于图1a中所示的pll 100,除了不使用分频器108。相比之下,pll 150根据本领域已知的无分频器pll的工作原理进行工作,并且可以结合以下关于图3d讨论的工作原理。

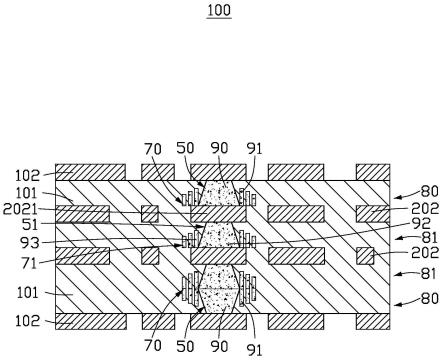

25.图2a示出了可用于实现图1a中所示的pll 100的模拟pll 200的示意图。如图所示,图1a中所示的m个相位检测电路102中的每一个都是使用相位频率检测器(pfd)202以及其后的电荷泵204来实现的。图1a中所示的求和器103通过简单地将每个相应的电荷泵204

的输出连接在一起来实现,以使它们的输出电流在工作期间加在一起。环路滤波器104使用模拟环路滤波器206实现,并且振荡器106使用压控振荡器(vco)210实现。在工作期间,模拟环路滤波器206对电荷泵204的总输出进行滤波以产生调谐电压v

tune

。

26.图2b示出了pfd 202、电荷泵204和模拟环路滤波器206的可能实现的示意图。如图所示,pfd 202包括两个d型触发器222和224以及与门226。在工作期间,当参考时钟信号f

ref

具有在分频时钟信号f

div

的上升时钟沿之前的上升时钟沿时,触发器222响应于参考时钟信号f

ref

的上升沿而生成信号up。在分频时钟信号f

div

的上升沿,触发器224瞬时生成信号down。一旦信号up和down同时有效,与门226复位触发器222和224。类似地,当分频时钟信号f

div

具有在参考时钟信号f

ref

的上升时钟沿之前的上升时钟沿时,触发器224响应于分频时钟信号f

div

的上升沿而生成信号down。在参考时钟信号f

ref

的上升沿,触发器222瞬时生成信号up。一旦信号up和down同时有效,与门226复位触发器222和224。应该理解,图2b中所示的pfd 202的实现只是可以用于实现pfd 202的许多可能的pfd电路的一个示例。也可以使用逻辑和功能等效物以及本领域已知的其他pfd电路。

27.电荷泵204由电流源228和230以及开关232和234表示。当信号up有效时,电流源228生成的电流i

cp1

经由开关232流向模拟环路滤波器206。类似地,当信号down有效时,电流i

cn1

由电流源230生成,经由开关234流向模拟环路滤波器206。如图所示,其余m-1个电荷泵的电荷泵电流i

cp2

到i

cpm

和i

cn2

到i

cnm

与电流i

cp1

和i

cn1

一起被提供给环路滤波器206。图2b中所示的电荷泵204的实现仅是可用于实现电荷泵204的许多可能电荷泵电路中的一个。也可以使用本领域已知的其他电荷泵电路。

28.模拟环路滤波器206包括串联耦接的电容器c1和电阻器r,以及分流电容器c2。在替选实施方式中也可以使用其他模拟环路滤波器拓扑。

29.图3a示出了可用于实现图1a中所示的pll 100的实施方式全数字pll(adpll)300的示意图。在一个实施方式中,图1a中所示的每个相位检测电路102的功能是使用与用于校准并均衡每个相位检测路径的延迟的数字时间转换器(dtc)302串联耦接的时间数字转换器(tdc)304来实现的。在一些实施方式中,tdc 304可以被配置成提供多位输出。图1a中所示的求和器103、环路滤波器104和振荡器106可以分别使用数字求和器306(也称为“求和电路”)、数字环路滤波器308和数控振荡器(dco)310来实现。图1a中所示的时钟分频器108是使用预分频器312来实现的,该预分频器312后跟多模分频器(mmd)314。

30.tdc 304可以使用本领域已知的时间数字转换器电路和方法例如使用游标内插器或抽头延迟线来实现;数字环路滤波器308可以使用本领域已知的数字滤波器例如一阶iir数字滤波器来实现,并且dco 310可以使用本领域已知的dco结构例如具有数字可选择的lc谐振电容的有源lc振荡器(例如负电阻振荡器或考毕兹振荡器)来实现。应该理解,tdc 304、数字环路滤波器308和dco 310的这些实现只是这些电路的许多可能实现示例中的几个。

31.在各种实施方式中,使用量化器316控制mmd 314的分频比。如图所示,期望的分数分频比n

frac_in

(也称为“分数分频值”或“分数分频输入”)被提供给量化器316,该量化器316在模控输入处向mmd 314提供过采样调制输出n

mmd

。在各种实施方式中,量化器316可以使用过采样调制器例如数字δ-σ调制器来实现。通过使用δ-σ调制器,由于δ-σ调制器的噪声整形特性,由mms的改变分频比生成的杂散能量可以分布在多个频率上并推到更高的频

302提供更少的延迟。

36.实施方式概念可以针对所示出的无分频器分数n pll,例如,图3d中示出了根据另一实施方式的无分频器分数n pll 360。如图所示,无分频器分数n pll360与图3a中所示的adpll 300的不同之处在于dco 310的输出f

pll

被提供给tdc 304而不被分频。替代地,使用被配置成应用本领域已知的无分频器频率控制方法的无分频器频率控制块362来调整输出频率。例如,无分频器频率控制块362可以被配置成通过下述方式来调整dco的频率或相位:通过切换dco的调谐电容器组、通过从环形振荡器选择相位、向dco 310的输出施加可调节延迟、从耦接在dco 310与tdc 304之间的可编程延迟线中选择抽头、或本领域已知的其他无分频器频率调整技术。在无分频器频率控制块362被配置成通过量化值来应用对f

pll

的频率的调整的实施方式中,可以通过使用量化器316并使用相位误差信号p

error

来调整dtc 302的延迟来实现进一步的分辨率,如以上实施方式中所述。尽管无分频器分数n pll 360被示为具有被配置成延迟参考时钟f

ref

的dtc 302,但在替选实施方式中,dtc可以被配置成如图3c所示替代地延迟输出时钟f

pll

。

37.在其他实施方式中,也可以如图3e所示实现无分频器整数n pll,图3e示出了根据实施方式的无分频器整数n pll 365。无分频器整数npll 365类似于图3d所示的无分频器分数n pll,除了省略了支持分数n操作的量化器316、求和器318和累加器321。

38.图3f示出了在反馈路径中包括可编程整数分频器372的adpll 370的实施方式。在实施方式中,整数分频器372被配置成将输出时钟f

pll

除以由分频器控制信号fcw设置的整数。尽管adpll 370被示为具有被配置成延迟参考时钟f

ref

的dtc 302,但在替选实施方式中,dtc可以被配置成如图3c所示替代地延迟输出时钟f

pll

。

39.应当理解,为了说明的简单性,已经从图3a至图3f中省略了一些细节。例如,在一些实施方式中,tdc 304的输出可以耦接至校准电路320。这样的耦接在下面关于图4a和图4b概念性地描述,图4a和图4b示出了耦接至lms校准块402的tdc 403的输出。

40.在实施方式中,每个相位检测信号路径的dtc 302可以被单独校准,以便均衡每个相位检测信号路径之间的相对延迟,并且针对每个相位检测信号路径均衡相位误差信号p

error

对dtc提供的延迟的影响。图4a示出了实施方式pll的两个相位检测信号路径的详细视图400,其表示图3a、图3c、图3d、图3e和图3f中描绘的和上面讨论的adpll 300和350的相位检测信号路径。如图所示,每个相位检测信号路径包括dtc 302和tdc 304。每个相位检测信号路径的输入时钟通常表示为ck1和ck2,因为参考时钟f

ref

可以耦接至dtc 302(如图3a、图3d、图3e和图3f所示),或者分频时钟r

div

可以耦接至dtc 302(如图3c所示)。除了dtc 302和tdc 304之外,每个相位检测信号路径还包括耦接至dtc 302的最小均方(lms)校准块402。lms校准块402可以共同实现图3a和图3c中所示的校准电路320的功能。在一个实施方式中,每个lms校准块402被配置成将相位误差信号p

error

映射到应用于时钟信号ck2的对应的校准延迟。

41.图4b图示了示出lms块402的一种可能实现的框图,lms块402被配置成提供对应用于相位误差信号p

error

的增益和偏移的背景校准,以便为dtc 302生成控制信号dtc

ctl

。如图所示,lms块402包括累加器404和406、乘法器412和414以及求和器410。在一个实施方式中,累加器404累加tdc 304的输出ei(k)以产生偏移校正信号w

off,i

,偏移校正信号w

off,i

经由求和器410与相位误差信号p

error

相加。增益校正信号g

lms,i

是通过使用乘法器414将tdc 304的

输出ei(k)乘以相位误差信号p

error

并使用累加器406对相乘信号进行累加来产生的。乘法器412将相位误差信号p

error

乘以增益校正信号g

lms,i

以校正dtc 302相对于相位误差信号p

error

的增益。如图所示,累加器404具有校准增益因子γ并且累加器406具有校准增益因子g,其可以使用lms算法在背景更新。在不使用量化器316的实施方式中,例如在图3f的包括固定分频器的实施方式中,可以省略乘法器412和414、累加器406和求和器410。在这样的实施方式中,累加器404的输出可以连接至dtc 302的控制输入dtc

ctl

。

42.在本发明的实施方式中,lms算法确定描述每个相位检测信号路径的每个tdc 304的输出ei(k)的差或方差的误差度量。误差度量可以是各种输出ei(k)之间的方差、均方差或任何其他合适的误差度量。在pll的工作期间,误差度量被监测并且变量γ和g被更新以使用本领域已知的lms方法来减少和/或最小化误差度量。通过更新这些值,相位误差信号p

error

的增益和偏移以每个相位检测信号路径的相对延迟在相位误差信号p

error

的可用范围内基本匹配的方式校准。由于帮助生成相位误差信号p

error

的量化器316的输出是频繁变化的信号,因此将ei(k)乘以相位误差信号p

error

可以被配置成提供足够的信号活动性以确保在后台校准期间实践增益校准路径。在这方面,相位误差信号p

error

相对于后台校准算法充当训练序列或抖动信号。

43.lms块402可以使用本领域已知的数字电路来实现。例如,求和器410可以使用数字加法器来实现,乘法器412和414可以使用数字乘法器来实现,并且累加器404和406可以使用本领域已知的累加器电路(例如耦接至寄存器的加法器)来实现。在一些实施方式中,使用数字乘法器和/或移位寄存器将校准因子γ和g应用于累加器404和406的输入或输出。在替选实施方式中,lms块402可以使用可编程处理器诸如微控制器或微处理器或数字信号处理器(dsp)来实现。lms块402可以使用本领域已知的控制器(未示出)实现的数字电路和/或可编程处理器来控制。

44.应当理解,图4b中描绘的lms块402的实现表示可以实现dtc块302的相对延迟的许多方式之一。在替选实施方式中,其他校准方法例如其他随机梯度方法、最速下降方法、递归最小二乘法(rls)、或旨在找到一方面消除图4a中的dtc 302与tdc 304之间的延迟失配另一方面也可以使用量化噪声p

error

的dtc

ctl

序列的任何前台校准。

45.图5a示出了实施方式雷达收发器502,其利用如根据上述各种实施方式所描述的实施方式pll。如图所示,雷达收发器包括生成rf信号s

lo

(t)的实施方式pll 504,rf信号s

lo

(t)可以使用本领域已知的频率调制技术进行频率调制。例如,在调频连续波(fmcw)雷达系统中,rf信号s

lo

(t)可以被调频以具有增加频率和/或减少频率的频率斜坡。可替选地,rf信号s

lo

(t)可以根据其他形状和图案例如矩形和正弦进行频率调制。在雷达应用中,lo信号可能处于超高频(shf)或极高频(ehf)频带(例如,机动车辆应用中在76ghz与81ghz之间)。

46.在发射信号路径以及接收信号路径中处理lo信号s

lo

(t)。由tx天线512辐射的发射信号s

rf

(t)是通过例如使用rf功率放大器520放大lo信号s

lo

(t)而生成的。放大器520的输出耦合至tx天线512。由rx天线514提供的接收信号y

rf

(t)被提供给混频器524。在本示例中,接收信号y

rf

(t)(即,天线信号)由rf放大器523(增益g)预放大,使得混频器在其rf输入处接收经放大的信号g y

rf

(t)。混频器524还在其参考输入处接收lo信号s

lo

(t)并且被配置成将经放大的信号g yrf(t)下变频到基带中。在混频器输出处的所得到的基带信号表示为y

bb

(t)。基带信号y

bb

(t)由模拟基带信号处理链530进一步处理,模拟基带信号处理链530基本

上包括一个或更多个滤波器(例如,带通滤波器531)以去除不期望的边带和镜像频率,以及一个或更多个放大器例如放大器532。可以提供给模数转换器的模拟输出信号表示为y(t)。

47.在本示例中,混频器524将rf信号g y

rf

(t)(经放大的天线信号)下变频到基带。相应的基带信号(混频器输出信号)由y

bb

(t)表示。下变频可以在单个阶段(即,从rf频带到基带)或经由一个或更多个中间阶段(从rf频带到if频带并随后到基带)来完成。应当理解,雷达收发器502只是可以利用根据本发明的实施方式的pll的许多可能系统之一。

48.图5b示出了实施方式rf收发器552,其利用如根据以上各种实施方式描述的实施方式pll。rf收发器502可以用在例如rf通信系统中。如图所示,rf收发器552包括耦接至发射信号路径和接收信号路径的基带处理器554。发射信号路径包括数模转换器(dac)556、上变频器558、功率放大器560、可以耦接至发射天线564的发射滤波器562。接收信号路径包括模数转换器(adc)574、下变频器572、低噪声放大器(lna)570和可以耦接至接收天线566的接收滤波器568。可以使用根据本文描述的任何实施方式的pll电路来实现的pll 670被配置成将发射本地振荡器信号txlo提供给发射信号路径的上变频器558,并且将接收本地振荡器信号rxlo提供给接收信号路径的下变频器572。在所示的实施方式中,示出了从参考信号f

ref

得到信号txlo和rxlo的单个pll 670,其可以适用于半双工发射和接收。在替选实施方式中,例如,可以使用两个单独的实施方式pll来实现全双工rf收发器。

49.在工作期间,基带处理器554在数字域中生成基带信号,使用数模转换器(dac)556将该基带信号转换到模拟域以形成模拟基带信号。可以使用本领域已知的dac电路来实现dac 556。使用上变频器558将模拟基带信号上变频到rf频率,上变频器558可以例如使用一个或更多个rf混频电路来实现。使用实施方式功率放大器560放大上变频器的输出,并且使用发射滤波器562对得到的经放大的rf信号进行滤波并将其提供给发射天线564。发射滤波器562可以使用本领域已知的rf滤波器电路和系统来实现,包括但不限于无源lc滤波器、表面声波(saw)滤波器。

50.接收信号路径包括模数转换器(adc)574、下变频器572、低噪声放大器(lna)570和可以耦接至接收天线566的接收滤波器568。在工作期间,接收滤波器568对由接收天线566接收的rf信号进行滤波,经滤波的接收信号由lna 570放大,其输出由下变频器572下变频。经下变频的模拟信号由adc 574数字化,并且经数字化的输出由基带处理器554处理。接收滤波器568可以实现为本领域已知的rf滤波器电路和系统,包括但不限于无源lc滤波器、表面声波(saw)滤波器;下变频器572可以使用本领域已知的下变频器电路和系统来实现,例如一个或更多个rf混频器电路,并且adc 574可以使用本领域已知的adc电路来实现。

51.在一些实施方式中,rf收发器552的所有电路可以在单个单片半导体集成电路上实现。可替选地,rf收发器552的部件可以使用多个部件来划分。应当理解,rf收发器552只是可以利用根据本发明的实施方式的功率放大器的许多系统之一。

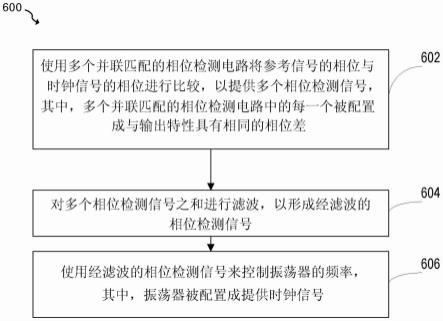

52.图6示出了根据本发明的实施方式的方法600的框图。方法600可以由以上实施方式中描述的任何pll系统来执行。在步骤602中,使用多个并联匹配的相位检测电路将参考信号的相位与时钟信号的相位进行比较,以提供多个相位检测信号。多个并联匹配的相位检测电路中的每一个被配置成与输出特性具有相同的相位差。在模拟实施方式诸如图1a和图1c的实施方式中,可以使用pfd来实现多个相位检测器。在数字实施方式诸如图3a至图3f的实施方式中,可以使用时间数字转换器来实现多个相位检测器。

53.在步骤604中,对多个相位检测信号的和进行滤波,以形成经滤波的相位检测信号。根据特定系统的配置,可以使用模拟滤波器或数字滤波器来执行该滤波。

54.在步骤606中,使用经滤波的相位检测信号来控制振荡器的频率。在各种实施方式中,振荡器被配置成提供时钟信号。在一些实施方式中,可以使用如图1a、图2a、图3a、图3c和图3f的实施方式中所示的分频器对该时钟信号进行分频。可替选的,如图3d的实施方式所示,时钟信号可以不被分频。

55.此处总结了本发明的实施方式。根据本文提交的整个说明书和权利要求书,也可以理解其他实施方式。

56.示例1.一种操作锁相环(pll)的方法,所述方法包括:使用多个并联匹配的相位检测电路将参考信号的相位与时钟信号的相位进行比较,以提供多个相位检测信号,其中,多个并联匹配的相位检测电路中的每一个被配置成与输出特性具有相同的相位差;对多个相位检测信号之和进行滤波,以形成经滤波的相位检测信号;以及使用经滤波的相位检测信号来控制振荡器的频率,其中,振荡器被配置成提供所述时钟信号。

57.示例2.根据示例1的方法,其中:多个并联匹配的相位检测电路中的每一个包括相位频率检测器(pfd)和耦接至所述pfd的输出端的电荷泵;以及对多个相位检测信号之和进行滤波包括使用模拟环路滤波器。

58.示例3.根据示例1或2之一的方法,其中:并联匹配的相位检测电路中的每一个包括时间数字转换器;以及对多个相位检测信号之和进行滤波包括使用数字环路滤波器。

59.示例4.根据示例1至3之一的方法,还包括:对振荡器的频率进行分频以形成分频时钟信号,其中,对振荡器的频率进行分频包括使用耦接至振荡器的输出端的分频器。

60.示例5.根据示例1至4之一的方法,还包括:将分数分频值应用于量化器的输入;以及利用量化器的输出控制分频器的分频比。

61.示例6.根据示例4或5的方法,还包括:确定量化器的量化误差;以及在比较参考信号的相位与时钟信号的相位之前基于所确定的量化误差将参考信号或分频时钟信号延迟一个延迟时间。

62.示例7.根据示例6的方法,其中,将参考信号或分频时钟信号延迟包括使用耦接至多个并联匹配的相位检测电路的相应输入端的多个并联的数字时间转换器。

63.示例8.一种锁相环(pll),包括:多个并联匹配的相位检测电路,多个并联匹配的相位检测电路中的每一个包括耦接至参考信号节点的第一输入端、耦接至时钟信号节点的第二输入端、以及被配置成提供相应的相位检测信号的输出端,其中,多个并联匹配的相位检测电路中的每一个被配置成与输出特性具有相同的相位差;环路滤波器,其耦接至多个并联匹配的相位检测电路的输出端;以及振荡器,其具有耦接至环路滤波器的输出端的频率控制输入端,其中,振荡器被配置成提供时钟信号。

64.示例9.根据示例8的pll,其中:多个并联匹配的相位检测电路中的每一个包括相位频率检测器(pfd)和耦接至pfd的输出的电荷泵;以及环路滤波器包括模拟滤波器。

65.示例10.根据示例8或9之一的方法,其中:并联匹配的相位检测电路中的每一个包括时间数字转换器;以及环路滤波器包括数字滤波器。

66.示例11.根据示例10的pll,其中,时间数字转换器被配置成提供多位输出。

67.示例12.根据示例8至11之一的pll,还包括时钟分频器,其被配置成接收时钟信号

并将分频时钟信号提供给时钟信号节点。

68.示例13.根据示例12的pll,还包括量化器,其耦接在分数分频输入与时钟分频器的模控输入之间。

69.示例14.根据示例13的pll,还包括:量化误差确定电路,其耦接至量化器,量化误差确定电路被配置成提供量化器的确定的量化误差值;以及数字时间转换器,其耦接在参考信号节点与多个并联匹配的相位检测电路中的每一个的第一输入端之间,或者耦接在时钟分频器的输出端与多个并联匹配的相位检测电路的每个的第二输入端之间,数字时间转换器被配置成基于所确定的量化误差值向参考信号节点处的参考信号或向时钟分频器的输出端处的分频时钟信号提供第一延迟。

70.示例15.根据示例14的pll,其中,数字时间转换器包括耦接至多个并联匹配的相位检测电路的相应的第一输入端或第二输入端的多个并联的数字时间转换器。

71.示例16.根据示例15的pll,还包括校准电路,其被配置成针对多个并联的数字时间转换器中的每一个单独地校准第一延迟与所确定的量化误差值之间的关系。

72.示例17.一种锁相环(pll),包括:多个并联耦接的相位检测信号路径,每个相位检测信号路径包括数字时间转换器和时间数字转换器,时间数字转换器的输入端耦接至数字时间转换器的输出端,其中,多个相位检测信号路径中的每一个被配置成将相同的相位检测特性应用于参考信号与分频时钟信号之间的相位差;求和电路,其耦接至多个相位检测信号路径中的每一个的输出端;数字环路滤波器,其耦接至求和电路的输出端;数控振荡器(dco),其耦接至数字环路滤波器的输出端;分频器,其耦接在dco的输出端与多个相位检测信号路径之间,分频器被配置成提供分频时钟信号;δ-σ调制器,其输出端耦接至分频器的模控输入端;以及减法电路,其输入端耦接至δ-σ调制器的输入端和δ-σ调制器的输出端,并且其输出端耦接至多个相位检测信号路径的每个数字时间转换器的延迟控制输入端。

73.示例18.根据示例17的pll,还包括校准电路,其被配置成单独地校准提供给多个相位检测信号路径的每个数字时间转换器的延迟控制输入端的值与由多个相位检测信号路径的每个数字时间转换器所提供的延迟之间的关系。

74.示例19.根据示例17或18之一的pll,其中,多个相位检测信号路径中的每一个的数字时间转换器包括被配置成接收参考信号的输入端。

75.示例20.根据示例17至19之一的pll,其中,多个相位检测信号路径中的每一个的数字时间转换器包括被配置成接收分频时钟信号的输入端。

76.虽然已经参考说明性实施方式描述了本发明,但是该描述不旨在以限制意义进行解释。通过参考描述,示例性实施方式的各种修改及组合以及本发明的其他实施方式对本领域技术人员而言将是明显的。因此,所附权利要求旨在涵盖任何这样的修改或实施方式。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。