1.本技术涉及半导体制造技术领域,具体而言,涉及一种半导体器件结构的制造方法及半导体器件结构。

背景技术:

2.在半导体器件结构(如芯片封装结构)的制造过程中,涂胶工艺不可避免。例如,在器件结构的制作过程中,经常需要在电子器件表面(如芯片的表面)进行涂胶作业(如进行pi胶或pr胶的涂布)。然而,发明人经研究发现,这种传统的涂胶方式,难以使得胶层表面具有较高的平整性,影响整个半导体器件的制作效果和器件质量。

技术实现要素:

3.基于上述内容,为解决上述问题,本技术提供一种半导体器件结构的制造方法及半导体器件结构,可以。

4.首先,第一方面,本技术实施例提供一种半导体器件结构的制造方法,所述方法包括:

5.提供一待涂胶对象,并在所述待涂胶对象上形成涂胶挡墙结构,使所述涂胶挡墙结构围绕所述待涂胶对象上的待涂胶区域设置并形成用于对所述待涂胶区域进行涂胶作业的涂胶挡槽;

6.在待涂布的胶材中添加胶材稀释剂,对所述待涂布的胶材进行稀释处理;

7.通过所述涂胶挡槽在所述待涂胶对象上涂布经过稀释处理后的胶材,形成涂胶层。

8.基于本技术第一方面的一种可能的实现方式,提供所述待涂胶对象,包括:

9.基于一基底制作形成芯片,并对所述芯片通过塑封层进行封装,形成芯片封装结构,由所述芯片封装结构作为所述待涂胶对象。

10.基于本技术第一方面的一种可能的实现方式,所述方法还包括:

11.对所述涂胶层进行图案化,得到用于形成重布线结构的图案化窗口;

12.通过所述图案化窗口制作形成重布线层,使所述重布线层穿过所述涂胶层与所述芯片封装结构中的芯片的芯片引脚连接。

13.基于本技术第一方面的一种可能的实现方式,所述待涂胶对为一基板,所述方法还包括:

14.基于所述涂胶层制作形成重布线层;

15.在所述重布线层上制作芯片封装结构,其中,所述重布线层穿过所述涂胶层与所述芯片封装结构中的芯片引脚连接。

16.基于本技术第一方面的一种可能的实现方式,所述方法还包括,在所述芯片封装结构制作完成后,去除所述基板。

17.基于本技术第一方面的一种可能的实现方式,所述涂胶层的厚度小于所述涂胶挡

墙结构的高度。

18.基于本技术第一方面的一种可能的实现方式,所述方法还包括:

19.对所述涂胶挡墙结构进行研磨,以去除所述涂胶挡墙结构的多余部分。

20.第二方面,本技术实施例还提供一种半导体器件结构,包括待涂胶对象、涂胶挡墙结构、以及涂胶层;

21.其中,所述涂胶挡墙结构位于所述待涂胶对象上、所述涂胶挡墙结构围绕所述待涂胶对象上的待涂胶区域设置形成用于对所述待涂胶区域进行涂胶作业的涂胶挡槽,所述涂胶层位于所述涂胶挡槽内。

22.基于本技术第二方面的一种可能的实现方式,所述待涂胶对象包括基底、芯片、以及塑封层,所述半导体器件结构还包括基于所述涂胶层制作形成的重布线层,所述重布线层穿过所述涂胶层与所述芯片的芯片引脚连接。

23.基于本技术第二方面的一种可能的实现方式,所述涂胶层的厚度小于所述涂胶挡墙结构的高度。

24.相较于现有技术,本技术实施例提供的半导体器件结构的制造方法及半导体器件结构,通过在待涂胶对象上制作形成涂胶挡墙结构,然后对胶材进行稀释处理后通过涂胶挡槽进行涂胶作业形成涂胶层。通过这种方式,相较于现有的半导体器件结构的制程工艺中的涂胶方法,由于胶材经过稀释处理后,流动性较好,在涂胶挡槽内可以通过自流平的方式形成表面更为平整的涂胶层。此外,虽然胶材经过稀释处理,由于涂胶挡墙结构的存在,也可以容易的形成特定厚度的涂胶层。相较于现有的未设置涂胶挡墙结构的方法,不会因为胶材被稀释而难以形成所需厚度的涂胶层。

25.此外,本实施例由于先形成了较高的涂胶挡墙结构,稀释后的胶材具有高流动性,不仅非常容易流平(平坦化),而且还可以避免粘度高容易产生气泡和针孔的风险。同时,黏度低的胶不易形成较厚膜的缺点被较高的涂胶挡墙结构所弥补,在干燥以及稀释剂挥发后,可以形成平坦的且具有一定膜厚的涂胶层。

附图说明

26.为了更清楚地说明本技术实施例的技术方案,下面将对实施例中所需要使用的附图作简单地介绍。应当理解,以下附图仅示出了本技术的某些实施例,因此不应被看作是对范围的限定。对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他相关的附图。

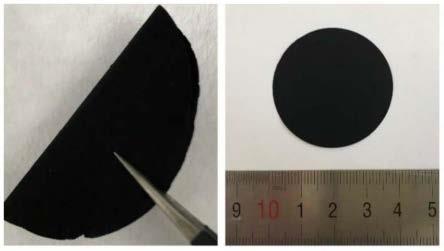

27.图1是本技术实施例提供的一种常见的半导体器件结构制程工艺中的涂胶结果示意图之一。

28.图2是本技术实施例提供的一种常见的半导体器件结构制程工艺中的涂胶结果示意图之二。

29.图3是本技术实施例提供的半导体器件结构的制造方法的流程示意图。

30.图4是本技术实施例提供的半导体器件结构的制造方法中形成涂胶挡墙结构的局部截面示意图。

31.图5是本技术实施例提供的半导体器件结构的制造方法形成涂胶挡墙结构的局部平面示意图。

32.图6是本技术一实施例提供的一种制作待涂胶对象的过程示意图。

33.图7是本技术实施例提供的用于在芯片封装结构作为待涂胶对象时形成涂胶挡墙结构的示意图。

34.图8是图7的基础上形成涂胶层的结构示意图。

35.图9是在图7的结构基础上形成重布线结构的示意图。

36.图10是本技术另一实施例中直接在以一基板作为待涂胶对象制作涂胶层以及重布线结构的示意图。

37.图11是在图10的基础上进一步制作与重布线结构连接的芯片封装结构的示意图。

具体实施方式

38.为使本技术实施例的目的、技术方案和优点更加清楚,下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例是本技术一部分实施例,而不是全部的实施例。通常在此处附图中描述和示出的本技术实施例的组件可以以各种不同的配置来布置和设计。

39.因此,以下对在附图中提供的本技术的实施例的详细描述并非旨在限制要求保护的本技术的范围,而是仅仅表示本技术的选定实施例。基于本技术中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

40.应注意到:相似的标号和字母在下面的附图中表示类似项,因此,一旦某一项在一个附图中被定义,则在随后的附图中不需要对其进行进一步定义和解释。

41.在本技术的描述中,需要理解的是,术语“上”、“下”、“内”、“外”、“左”、“右”等指示的方位或位置关系为基于附图所示的方位或位置关系,或者是该申请产品使用时惯常摆放的方位或位置关系,或者是本领域技术人员惯常理解的方位或位置关系,仅是为了便于描述本技术和简化描述,而不是指示或暗示所指的设备或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本技术的限制。

42.此外,术语“第一”、“第二”等仅用于区分描述,而不能理解为指示或暗示相对重要性。

43.在本技术的描述中,还需要说明的是,除非另有明确的规定和限定,“设置”、“连接”等术语应做广义理解,例如,“连接”可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接连接,也可以通过中间媒介间接连接,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本技术中的具体含义。

44.下面结合附图,对本技术的具体实施方式进行详细说明。

45.诚如前述背景技术所描述的技术问题,本技术发明人对传统的较为常用的一些涂胶作业全流程进行了研究分析。一般而言,较为常用的涂胶方式包括采用旋转式涂胶机(spin coater)和狭缝式涂胶机(slit coater)进行涂胶两种方式。无论采用哪种涂胶方式,因为胶有一定黏度,流动性一般,因此在不平的表面也会形成不平整的胶膜,例如图1所示,在因为突出的器件结构01的存在,会导致形成的胶膜02会存在不平整的表面。此外,如果选用黏度小的胶材,虽然可以具有较好的流动性,却又难以形成需要的膜厚。又或者,即

便在平整的表面进行涂胶作业,也可能会因为涂胶材料的表面张力因素在胶层的边缘(如图2所示)产生异形结构,都不利于胶层的平整性,而影响整体器件结构的工艺质量。为解决上述问题,传统以及现有的一些方法对于不平整表面的介质平坦化常采用化学机械研磨方法(cmp)或无应力抛光技术(sfp)等实现表面的平整化,然而这些方法所需使用到的设备价格昂贵、成本高、材料消耗大,提升了半导体器件结构的制作成本,同时,这种方法也存在均匀性差的问题。

46.为了解决前述问题,本技术实施例创新性地提供了一种半导体器件结构的制造方法,如图3所示,是该制造方法的流程示意图,下面将结合附图对该制造方法进行示例性的说明。

47.步骤s100,如图4所示,提供一待涂胶对象100,并在所述待涂胶对象100上形成涂胶挡墙结构200。所述涂胶挡墙结构围绕所述待涂胶对象100上的待涂胶区域设置形成用于对所述待涂胶区域进行涂胶作业的涂胶挡槽210。

48.在本实施例中,可通过pi涂覆、曝光、显影或者点胶或者印刷来实现所述涂胶挡墙结构200的制作。例如,作为一种示例,可以首先在所述待涂胶对象100上涂布形成一阻挡材料层,然后,通过光刻掩膜对所述阻挡材料层进行光刻图案化,去除与待涂胶区域对应的阻挡材料层,即可形成如图4所述的涂胶挡墙结构200。在其他实施例中,也可以通过精准点胶或者喷墨印刷等工艺形成所述涂胶挡墙结构200,本实施例对形成所述涂胶挡墙结构200的具体实现方式不进行具体限定。

49.步骤s200,在待涂布的胶材中添加胶材稀释剂,对所述待涂布的胶材进行稀释处理。本实施例中,所述胶材可以是pi胶(polyimide,聚酰亚胺)或pr胶(photo resist,光刻胶)。其中,通过对所述胶材进行稀释处理之后,可以使得所述胶材具有较好的流动性。其中,所述稀释剂可以是干燥后可挥发的稀释剂。

50.步骤s300,如图5所示,通过所述涂胶挡槽210在所述待涂胶对象100上涂布经过稀释处理后的胶材,形成涂胶层300。本实施例中,所述涂胶挡墙结构200的高度大于需要涂布的胶层的厚度。如此,形成的涂胶层300的厚度,小于所述涂胶挡墙结构200的高度。

51.本技术实施例中,通过上述方法首先在待涂胶对象100上制作形成涂胶挡墙结构200,然后对胶材进行稀释处理后通过涂胶挡槽210进行涂胶作业形成涂胶层300。通过这种方式,相较于现有的半导体器件结构的制程工艺中的涂胶方法,由于胶材经过稀释处理后,流动性较好,在涂胶挡槽210内可以通过自流平的方式形成表面更为平整的涂胶层300。此外,虽然胶材经过稀释处理,由于涂胶挡墙结构200的存在,也可以容易的形成特定厚度的涂胶层300。相较于现有的未设置涂胶挡墙结构200的方法,不会因为胶材被稀释而难以形成所需厚度的涂胶层。

52.此外,本实施例由于先形成了较高的涂胶挡墙结构200,稀释后的胶材具有高流动性,不仅非常容易流平(平坦化),而且还可以避免粘度高容易产生气泡和针孔的风险。同时,黏度低的胶不易形成较厚膜的缺点被较高的涂胶挡墙结构200所弥补,在干燥以及稀释剂挥发后,可以形成平坦的且具有一定膜厚的涂胶层300。

53.进一步地,为了直观的体现上述方法在半导体器件结构的涂胶工艺中的具体应用及效果,本实施例以上述方法在芯片封装结构中的制程工艺中的应用为例进行示例性的说明。

54.在一种可能的实施方式中,所述待涂胶对象100可以是已经制作形成有芯片的封装结构。基于此,所述步骤s100中,提供所述待涂胶对象100的步骤可以包括以下内容。

55.首先,如图6所示,基于一基底110制作形成芯片120。

56.然后,对所述芯片120通过塑封层130进行封装,形成芯片封装结构。对所述芯片120进行封装可以采用emc材料(epoxy molding compound,环氧树脂模塑料)实现,在封装之后,还可以执行研磨(grind)等其他工艺流程,使得形成的芯片封装结构具有较平整的表面。关于芯片封装有关的其它工艺流程,本实施例不再一一赘述。

57.其中,包括所述基底110、芯片120、以及塑封层130的所述芯片封装结构即作为本技术实施例中的待涂胶对象100。如此,在所述芯片封装结构(待涂胶对象)上形成涂胶挡墙结构200的结构示意图如图7所示,经过涂胶挡槽210形成涂胶层300的示例性结构示意图如图8所示。

58.在上述内容的基础上,以对所述芯片封装结构的后续重布线(rdl)工艺为例,形成所述涂胶层300之后,本技术实施例提供的半导体器件结构的制造方法还可以包括重布线结构的制作过程。例如,如图9所示,对所述涂胶层300进行图案化,得到用于形成重布线结构的图案化窗口,然后通过所述图案化窗口制作形成与所述芯片封装结构中的芯片120的芯片引脚连接的重布线层400(rdl层)。此外,对所述涂胶层300进行图案化的过程中,可以包括对所述涂胶层300进行的soft bake(软烘烤)、exposure(曝光)、peb(硬烘烤)、develop(显影)、post bake(后烘烤)等步骤,但不仅限于此。

59.作为一种示例,本实施例中,所述重布线结构可以包括多层重布线层400。例如,本实施例以所述重布线结构包括两层重布线层400为例,可以先在所述涂胶挡槽210内先形成第一涂胶层,并基于第一涂胶层形成第一重布线层;然后,再在第一重布线层上方形成第二涂胶层,并基于第二涂胶层形成第二重布线层。也就是说,可以基于所述涂胶挡槽210分别多次进行涂胶层的制作,每次制作涂胶层可以用于进行一层重布线层的制作工艺,具体的重布线结构的重布线层的数量,本实施例不具体进行限定。

60.在另一种可能的实施方式中,所述待涂胶对象100可以是一个用于制作重布线结构的基板,例如图10所示,可以直接基于一基板形成所述涂胶挡墙结构200,然后在在所述基板上通过涂胶挡槽210形成涂胶层300,接着再基于所述涂胶层300制作形成所述重布线层400。如此,与上一个可能的实施方式不同的在于,此处可以先制作重布线层400,然后再制作与重布线层400连接的芯片封装结构,其中,所述重布线层穿过所述涂胶层与所述芯片封装结构中的芯片引脚连接。在制作好芯片封装结构之后,可以去除(debond)所述基板得到制作完成的半导体器件结构(芯片封装结构),例如图11所示,如此,可以将芯片引脚的信号通过重布线层400引出,并与其它需要的电子器件连接。本实施例中,所述基板可以包括一基底以及设置在基底上的临时键合胶层,以利于基于该基板的其它组成结构的制作。

61.其中,除上述内容之外,上述制造方法中,在完成所述涂胶层300的制作后,还可以根据所述涂胶挡墙结构300的高度,对所述涂胶挡墙结构300进行研磨,以去除所述涂胶挡墙结构300的多余部分,例如,高出所述涂胶层300的部分。

62.在上述内容的基础上,本技术实施例还提供一种基于上述制造方法而制造得到的半导体器件结构。

63.例如,在本实施例中的一种可能的实现方式中,如图9所示,所述半导体器件结构

包括待涂胶对象100、涂胶挡墙结构200、以及涂胶层300。其中,所述涂胶挡墙结构200位于所述待涂胶对象100上、所述涂胶挡墙结构200围绕所述待涂胶对象100上的待涂胶区域设置形成用于对所述待涂胶区域进行涂胶作业的涂胶挡槽210,所述涂胶层位于所述涂胶挡槽210内。

64.针对芯片封装结构的具体实施例,所述待涂胶对象100包括基底110、芯片120、以及塑封层130,所述半导体器件结构还包括基于所述涂胶层300制作形成的重布线层400,所述重布线层400穿过所述涂胶层300与所述芯片120的芯片引脚连接。

65.综上所述,本技术实施例提供的半导体器件结构的制造方法及半导体器件结构,通过在待涂胶对象100上制作形成涂胶挡墙结构200,然后对胶材进行稀释处理后通过涂胶挡槽210进行涂胶作业形成涂胶层300。通过这种方式,相较于现有的半导体器件结构的制程工艺中的涂胶方法,由于胶材经过稀释处理后,流动性较好,在涂胶挡槽210内可以通过自流平的方式形成表面更为平整的涂胶层300。此外,虽然胶材经过稀释处理,由于涂胶挡墙结构200的存在,也可以容易的形成特定厚度的涂胶层300。相较于现有的未设置涂胶挡墙结构200的方法,不会因为胶材被稀释而难以形成所需厚度的涂胶层。

66.此外,本实施例由于先形成了较高的涂胶挡墙结构200,稀释后的胶材具有高流动性,不仅非常容易流平(平坦化),而且还可以避免粘度高容易产生气泡和针孔的风险。同时,黏度低的胶不易形成较厚膜的缺点被较高的涂胶挡墙结构200所弥补,在干燥以及稀释剂挥发后,可以形成平坦的且具有一定膜厚的涂胶层300。同时,本技术无需采用化学机械研磨方法(cmp)或无应力抛光技术(sfp)等即可实现涂胶层表面的平整化,进而降低了半导体器件结构的制作成本。

67.出于说明目的,前面的描述是参考具体实施例而进行的。但是,上述说明性论述并不打算穷举或将本技术局限于所公开的精确形式。根据上述教导,众多修改和变化都是可行的。选择并描述这些实施例是为了最佳地说明本技术的原理及其实际应用,从而使本领域技术人员最佳地利用本技术,并利用具有不同修改的各种实施例以适于预期的特定应用。出于说明目的,前面的描述是参考具体实施例而进行的。但是,上述说明性论述并不打算穷举或将本技术局限于所公开的精确形式。根据上述教导,众多修改和变化都是可行的。选择并描述这些实施例是为了最佳地说明本技术的原理及其实际应用,从而使本领域技术人员最佳地利用本技术,并利用具有不同修改的各种实施例以适于预期的特定应用。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。