1.本发明属于集成电路制造技术领域,具体涉及一种外延层的制备方法以及含外延层的半导体。

背景技术:

2.外延就是在单晶衬底上淀积一层薄的单晶层,新淀积的这层称为外延层。外延为优化器件性能方面提供了很大的灵活性,例如在某些情况下,需要硅片有非常纯的与衬底有相同晶体结构(单晶)的硅表面,还要保持对杂质类型和浓度的控制,这要通过在硅表面淀积一个外延层来达到。

3.随着硅外延片在半导体制造领域应用的不断扩展,外延工艺的重要性越来越高,比如外延在cmos集成电路中,它可以将闩锁效应降到最低;比如在功率器件中,它可以解决高频功率器件的击穿电压与集电极串联电阻对集电区电阻率的要求之间的矛盾。目前对用于制作器件的外延片的要求也越来越高,外延层的电阻率及其均匀性是最重要的参数之一,其中外延层的电阻率与均匀性是由掺杂物质的浓度以及均匀性来决定的,而外延层的杂质浓度会受到自掺杂效应的影响,特别是对于高电阻率即低掺杂的产品影响更为明显。因此降低自掺杂效应对外延层杂质浓度的控制就有重要意义。

技术实现要素:

4.本发明的目的在于提供一种外延层的制备方法以及含外延层的半导体,降低自掺杂效应和提高掺杂均匀性。

5.本发明提供一种外延层的制备方法,包括:提供一衬底;在外延腔室的内壁形成硅膜层,所述硅膜层不掺杂;在所述外延腔室内生长位于所述衬底上的第一外延层,所述第一外延层不掺杂或者低掺杂;在所述外延腔室内生长位于所述第一外延层上的第二外延层,所述第二外延层掺杂。

6.进一步的,提供一所述衬底之后,形成所述硅膜层之前还包括:依次采用sc1溶液和sc2溶液清洗所述衬底,所述sc1溶液包含氢氧化铵、过氧化氢和去离子水;所述sc2溶液包含盐酸、过氧化氢和去离子水。

7.进一步的,所述衬底为n型重掺杂硅衬底,所述衬底的电阻率范围为0.001欧姆厘米~0.003欧姆厘米。

8.进一步的,所述第一外延层和所述第二外延层的材质均为单晶硅,所述第一外延层和所述第二外延层的掺杂元素均包括磷或砷。

9.进一步的,所述硅膜层采用化学气相沉积工艺形成,所述硅膜层的厚度为0.1μm~100μm。

10.进一步的,所述第一外延层的厚度为:0.1μm~10μm,所述第二外延层的厚度为:1μm~100μm。

11.进一步的,所述衬底为p型重掺杂硅衬底,所述第二外延层为p型掺杂。

12.进一步的,所述第一外延层和所述第二外延层均采用化学气相沉积工艺形成。

13.进一步的,形成所述第二外延层的化学气相沉积工艺具体包括:温度900℃~1200℃,压力0.1torr~760torr,以h2为载气,通入硅源气体反应生成所述第二外延层;同时通入掺杂剂,对所述第二外延层进行低掺杂。

14.本发明还提供一种含外延层的半导体,包括:衬底;位于所述衬底上的第一外延层,所述第一外延层不掺杂或者低掺杂;位于所述第一外延层上的第二外延层,所述第二外延层掺杂。

15.与现有技术相比,本发明具有如下有益效果:本发明提供一种外延层的制备方法以及含外延层的半导体,制备方法包括:提供一衬底;在外延腔室的内壁形成硅膜层,所述硅膜层不掺杂;在所述外延腔室内生长位于所述衬底上的第一外延层,所述第一外延层不掺杂或者低掺杂;在所述外延腔室内生长位于所述第一外延层上的第二外延层,所述第二外延层掺杂。在外延腔室的内壁形成硅膜层,避免外延腔室的杂质扩散掺杂到后续形成的第一外延层和第二外延层,降低了自掺杂效应;衬底与第二外延层之间间隔第一外延层,第一外延层不掺杂或者低掺杂,通过第一外延层的过渡或间隔,避免了衬底中的杂质向第二外延层的扩散,第二外延层为产品真正起作用的外延层,降低了自掺杂效应,提高了掺杂均匀性。

附图说明

16.图1为一种含外延层的半导体其外延层的杂质浓度受自掺杂效应的影响示意图。

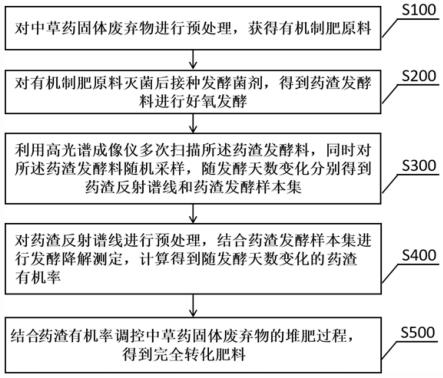

17.图2为本发明实施例的外延层的制备方法流程示意图。

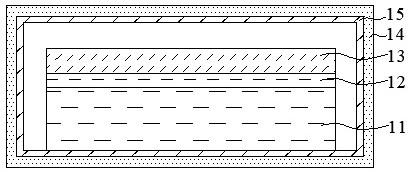

18.图3为本发明实施例的含外延层的半导体结构示意图。

19.图4为改进之前的掺杂均匀性图。

20.图5为改进之后的掺杂均匀性图。

21.其中,附图标记如下:01-衬底;02-外延层;11-衬底;12-第一外延层;13-第二外延层;14-外延腔室的内壁;15-硅膜层15。

具体实施方式

22.如背景技术所述,外延层的杂质浓度会受到自掺杂效应的影响。

23.研究发现,如图1所示,在重掺杂的衬底01上生长有轻掺杂的外延层02。自掺杂效应主要包括,一是高温外延,重掺杂的衬底01中的杂质(例如沿路径a)反扩散进入气相边界层,又从气相边界层扩散掺入外延层02;二是衬底01的杂质(例如沿路径b)直接扩散到外延层02;三是反应系统(例如外延腔室)的杂质(例如沿路径c)扩散掺杂到外延层02。

24.基于上述研究,本发明实施例提供了一种外延层的制备方法。以下结合附图和具体实施例对本发明进一步详细说明。根据下面说明,本发明的优点和特征将更清楚。需要说

明的是,附图均采用非常简化的形式且使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

25.为了便于描述,本技术一些实施例可以使用诸如“在

…

上方”、“在

…

之下”、“顶部”、“下方”等空间相对术语,以描述如实施例各附图所示的一个元件或部件与另一个(或另一些)元件或部件之间的关系。应当理解的是,除了附图中描述的方位之外,空间相对术语还旨在包括装置在使用或操作中的不同方位。例如若附图中的装置被翻转,则被描述为在其它元件或部件“下方”或“之下”的元件或部件,随后将被定位为在其它元件或部件“上方”或“之上”。下文中的术语“第一”、“第二”、等用于在类似要素之间进行区分,且未必是用于描述特定次序或时间顺序。要理解,在适当情况下,如此使用的这些术语可替换。

26.本发明实施例提供了一种外延层的制备方法,如图2所示,包括:步骤s1、提供一衬底;步骤s2、在外延腔室的内壁形成硅膜层,所述硅膜层不掺杂;步骤s3、在所述外延腔室内生长位于所述衬底上的第一外延层,所述第一外延层不掺杂或者低掺杂;步骤s4、在所述外延腔室内生长位于所述第一外延层上的第二外延层,所述第二外延层掺杂。

27.具体的,如图3所示,衬底11的类型可包括硅、锗、碳化硅、氮化镓或砷化镓中至少一种。所述衬底11例如为n型重掺杂硅衬底,其电阻率范围为0.001欧姆厘米~0.003欧姆厘米。

28.接着,执行一清洁步骤,清洗所述衬底11。具体包括使用湿法清洗工艺机台清洗所述衬底,清洗工艺可以是rca(由于其由radio corporation of america提出)标准清洗,且其包括:使用sc1溶液(标准清洁1)的第一清洁步骤, sc1溶液含有氢氧化铵(nh4oh)、过氧化氢(h2o2)和去离子水(h2o)。使用sc2溶液(标准清洁2)的第二清洁步骤,sc2 溶液含有盐酸(hcl)、过氧化氢(h2o2)和去离子水。通常用于50℃至80℃范围内的所述第一溶液sc1,主要是用来移除析出于所述衬底表面上的颗粒和隐埋于靠近所述衬底的颗粒,以及用来使表面亲水。通常用于70℃至90℃范围内的所述第二溶液sc2,主要特别经由形成氯化物用来移除已沉积于所述衬底上的金属污染物。

29.接着,在外延腔室的内壁14形成不掺杂的硅膜层15,硅膜层15的厚度可为0.1μm~100μm,具体可采用化学气相沉积形成硅膜层15。在外延腔室的内壁14形成不掺杂的硅膜层15,如此一来避免外延腔室(反应腔室)的杂质扩散掺杂到后续形成的第一外延层12和第二外延层13,降低了自掺杂效应,提高了掺杂均匀性。

30.接着,在所述外延腔室内生长位于所述衬底11上的第一外延层12,其中,所述第一外延层12不掺杂或者低掺杂。第一外延层的厚度可为:0.1μm~10μm。第一外延层12的材质例如为单晶硅。在本实施例中,第一外延层12可采用化学气相沉积工艺形成,但不限于此方式,化学气相沉积在高温的环境下进行,温度为900℃~1200℃,压力0.1 torr~760torr,以h2为载气,通入硅源气体反应形成第一外延层12。反应物包括:硅烷、二氯二氢硅和三氯氢硅中的至少一种。外延生长步骤中,四氯硅烷(sicl4)被经常用作硅原子的来源,而在反应气体中添加氯化氢可以增加生长过程中的沉积的能力。可通过调控一些参数来控制外延层的沉积状况,可影响外延状况的参数包括了衬底的表面情况、氯化氢的浓度、硅气体源种

类或成长压力和温度等。在一示例中,在形成第一外延层12时,向外延腔室(例如化学气相沉积腔室)通入掺杂剂,掺杂元素均包括磷或砷,对第一外延层12进行低掺杂。在另一示例中,在形成第一外延层12时不需要通入掺杂剂,第一外延层12为无掺杂的外延层。

31.接着,在所述外延腔室内生长位于所述第一外延层12上的第二外延层13,所述第二外延层13掺杂。第二外延层13的厚度可为:1μm~100μm。电阻率与外延层的杂质浓度相关,杂质浓度越低,外延层的电阻率越高;杂质浓度越高,电阻率越低。

32.示例性的,第二外延层13的材质为单晶硅,所述第二外延层13的掺杂元素包括磷或砷。以上示例示出了半导体包括的衬底为n型掺杂,外延层也为n型(例如磷或砷)掺杂的情形,该类型的半导体可用于nmos器件。其他示例中,半导体包括的衬底可为p型掺杂,外延层为p型(例如硼)掺杂,该类型的半导体可用于pmos器件。

33.第一外延层12和第二外延层13较佳的为相同材料。所述第二外延层13的掺杂元素的浓度可大于第一外延层12内掺杂元素的浓度。与衬底相比,外延层可以更好的控制掺杂浓度,也可以做到更低的c、o含量。

34.在本实施例中,第二外延层13也可采用化学气相沉积工艺形成,外延生长条件为:温度为900℃~1200℃,压力0.1 torr~760torr,以h2为载气,通入硅源气体反应生成第二外延层13。反应物包括:硅烷、二氯二氢硅和三氯氢硅中的至少一种。外延生长步骤中,四氯硅烷(sicl4)被经常用作硅原子的来源,而在反应气体中添加氯化氢可以增加生长过程中的沉积的能力。可通过调控一些参数来控制外延层的沉积状况,可影响外延状况的参数包括了衬底的表面情况、氯化氢的浓度、硅气体源种类或成长压力和温度等。在形成第二外延层13时,向外延腔室(例如化学气相沉积腔室)通入掺杂剂,掺杂元素均包括磷或砷,对第二外延层13进行低掺杂。

35.本发明实施例在外延腔室的内壁14形成硅膜层15,避免外延腔室的杂质扩散掺杂到后续形成的第一外延层12和第二外延层13,降低了自掺杂效应;衬底11与第二外延层13之间间隔第一外延层12,第一外延层12不掺杂或者低掺杂,通过第一外延层12的过渡或间隔,避免了衬底11中的杂质向第二外延层13的扩散,第二外延层13为产品真正起作用的外延层,降低了自掺杂效应,提高了掺杂均匀性。

36.图4为改进之前的掺杂均匀性图;图5为改进之后的掺杂均匀性图;结合图4和图5所示,改进之前的掺杂均匀性为7.55%,改进之后的掺杂均匀性为4.98%,数值越小代表均匀性越高,本发明简单有效地降低了自掺杂效应以及提高了掺杂的均匀性,其掺杂的均匀性由7.55%提高到4.98%,掺杂的均匀性提升了34%。

37.本发明还提供一种含外延层的半导体,如图3所示,包括:衬底11;位于所述衬底11上的第一外延层12,所述第一外延层12不掺杂或者低掺杂;位于所述第一外延层11上的第二外延层12,所述第二外延层12掺杂。

38.具体的,衬底11的类型可包括硅、锗、碳化硅、氮化镓或砷化镓中至少一种。所述衬底11例如为n型重掺杂硅衬底,其电阻率范围为0.001欧姆厘米~0.003欧姆厘米。所述第一外延层12和所述第二外延层13的材质可均为单晶硅,所述第一外延层12和所述第二外延层13的掺杂元素均包括磷或砷。所述硅膜层的厚度为0.1μm~100μm,所述第一外延层的厚度为:0.1μm~10μm,所述第二外延层的厚度为:1μm~100μm。

39.其他示例中,半导体包括的衬底可为p型掺杂,第二外延层为p型(例如硼)掺杂,该类型的半导体可用于pmos器件。

40.综上所述,本发明提供一种外延层的制备方法,包括:提供一衬底;在外延腔室的内壁形成硅膜层,所述硅膜层不掺杂;在所述外延腔室内生长位于所述衬底上的第一外延层,所述第一外延层不掺杂或者低掺杂;在所述外延腔室内生长位于所述第一外延层上的第二外延层,所述第二外延层掺杂。在外延腔室的内壁形成硅膜层,避免外延腔室的杂质扩散掺杂到后续形成的第一外延层和第二外延层,降低了自掺杂效应;衬底与第二外延层之间间隔第一外延层,第一外延层不掺杂或者低掺杂,通过第一外延层的过渡或间隔,避免了衬底中的杂质向第二外延层的扩散,第二外延层为产品真正起作用的外延层,降低了自掺杂效应,提高了掺杂均匀性。

41.本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分互相参见即可。对于实施例公开的方法而言,由于与实施例公开的器件相对应,所以描述的比较简单,相关之处参见方法部分说明即可。

42.上述描述仅是对本发明较佳实施例的描述,并非对本发明权利范围的任何限定,任何本领域技术人员在不脱离本发明的精神和范围内,都可以利用上述揭示的方法和技术内容对本发明技术方案做出可能的变动和修改,因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化及修饰,均属于本发明技术方案的保护范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。