1.本公开涉及摄像元件和该摄像元件的制造方法。更具体地,本公开涉及通过将多个半导体芯片粘合在一起而构造出来的摄像元件以及该摄像元件的制造方法。

背景技术:

2.近年来,已使用了其中将多个半导体芯片粘合在一起以实现小型化的半导体元件。作为这种半导体元件的制造方法,使用了一种通过将晶圆(wafer)粘合在一起来制造出半导体的方法。这被称为wow(wafer on wafer:晶圆上叠加晶圆),其是这样一种制造方法:其中,在被分离成各个单片(piece)之前在其上各自形成有集成电路的半导体晶圆被粘合在一起,粘合起来的半导体芯片彼此电连接,并且然后把由此产生的晶圆单片化为单独的集成电路。这是具有优异生产率的制造方法,这是因为是在晶圆的状态下统一进行粘合。然而,存在的一个问题是该wow具有降低的产量。在被分离成各个单片之前在晶圆上形成的半导体芯片中会以一定的比例出现诸如不能正常工作的芯片等有缺陷的芯片。作为将包含这种有缺陷的芯片的晶圆粘合在一起的结果,当至少一个晶圆上的半导体芯片有缺陷时,那么已经被分离成各个单片的所有半导体元件都会被判定为有缺陷的产品。因此,已经经历了粘合步骤的半导体元件的产量低于单个晶圆的产量。

3.与这种wow对照地,还使用了一种其中单片化的半导体芯片被粘合到晶圆上的制造方法。这种半导体元件的制造方法被称为cow(chip on wafer:晶圆上叠加芯片)。通过在粘合之前测试半导体芯片和它们在晶圆上的各个半导体芯片区域以便选择出无缺陷的芯片,就可以防止产量降低。作为这种半导体元件,例如,使用的是具有如下构造的摄像元件:该构造中,将其中设置有响应于入射光而生成图像信号的像素的半导体芯片和其中设置有用于处理图像信号的处理电路的半导体芯片粘合。通过将多个半导体芯片粘合在一起,可以使摄像元件小型化。已经提出了一种摄像元件,其中通过在粘合之前对半导体芯片进行电测试来筛选半导体芯片,并且把被判定为无缺陷产品的半导体芯片用来粘合(例如,参见专利文献1)。

4.[引文列表]

[0005]

[专利文献]

[0006]

[专利文献1]:国际申请公布wo 2019/087764

技术实现要素:

[0007]

[技术问题]

[0008]

上述传统技术具有当将测试之后的半导体芯片进行粘合时摄像元件会被损坏的问题。各半导体芯片的测试包括通过形成在半导体芯片的表面上的测试焊盘来检测电信号。电信号的检测可以借助于测试探针来检测。各测试探针都设置有金属针头,该金属针头的尖端与任何测试焊盘接触,从而使测试探针电连接到测试焊盘。此时,测试探针的针头以相对较高的针压与测试焊盘接触。这会穿透测试焊盘的正面上的氧化膜,从而会降低与测

试焊盘之间的电阻。测试探针的针头的这种接触使测试焊盘的正面变得凹凸不平。当半导体芯片被粘合在一起时,这种凹凸不平的尖端可能会损坏与之相对的半导体芯片,从而导致摄像元件发生损坏。

[0009]

本公开是鉴于上述问题而做出的,本公开的目的在于防止包括被粘合在一起的多个半导体芯片的摄像元件被损坏。

[0010]

[问题的解决方案]

[0011]

本公开是为了解决上述问题而做出的,本公开的第一方面是一种摄像元件,其包括多个半导体芯片,所述多个半导体芯片各者都包括半导体基板和配线区域,所述多个半导体芯片粘合在一起。所述多个半导体芯片之中的一个半导体芯片设置有对入射光进行光电转换的光电转换部。所述多个半导体芯片之中的两个半导体芯片各者都包括第一焊盘,所述两个半导体芯片的所述配线区域的表面粘合在一起,所述第一焊盘设置于所述配线区域的所述表面上,并且当所述两个半导体芯片的所述配线区域的所述表面被粘合时所述第一焊盘是彼此接合的,所述两个半导体芯片之中的至少一个半导体芯片还包括第二焊盘和绝缘膜,所述第二焊盘设置于所述配线区域中,所述绝缘膜设置于所述第二焊盘和用于粘合的所述表面之间,所述第二焊盘形成有朝着用于粘合的所述表面的凸部。

[0012]

此外,在该第一方面中,所述绝缘膜可以被形成为具有覆盖所述第二焊盘的厚度。

[0013]

此外,在该第一方面中,所述绝缘膜可以被形成为具有650nm以上的厚度。

[0014]

此外,在该第一方面中,所述绝缘膜可以由绝缘材料形成。

[0015]

此外,在该第一方面中,所述绝缘膜可以包含由硅化合物制成的所述绝缘材料。

[0016]

此外,在该第一方面中,所述摄像元件还可以包括:保护金属膜,其被设置于所述第二焊盘的表面上。

[0017]

此外,在该第一方面中,所述多个半导体芯片之中的至少一个半导体芯片还可以包括用于连接到外部电路的第三焊盘。

[0018]

此外,在该第一方面中,所述第三焊盘可以与所述第二焊盘被设置于同一层中。

[0019]

此外,在该第一方面中,所述第二焊盘可以被形成为具有与所述第一焊盘不同的尺寸。

[0020]

此外,在该第一方面中,所述第二焊盘可以被形成为具有比所述第一焊盘更大的尺寸。

[0021]

此外,在该第一方面中,所述第二焊盘可以由铝制成。

[0022]

此外,在该第一方面中,所述第二焊盘可以具有通过触针式测试而形成的所述凸部。

[0023]

此外,在该第一方面中,所述第二焊盘可以具有在如下凹部中形成的所述凸部:所述凹部被设置于所述第二焊盘的朝着用于粘合的所述表面的一侧上。

[0024]

此外,在该第一方面中,所述多个半导体芯片之中的所述两个半导体芯片均可以包括被设置成与另一者中的所述第二焊盘相对着的所述第二焊盘。

[0025]

此外,在该第一方面中,所述第一焊盘可以由铜制成。

[0026]

此外,在该第一方面中,所述多个半导体芯片之中的至少一个半导体芯片可以设置有用于处理基于所述光电转换而生成的图像信号的处理电路。

[0027]

此外,在该第一方面中,所述多个半导体芯片之中的所述两个半导体芯片均可以

设置有所述处理电路并且可以被粘合在一起。

[0028]

此外,在该第一方面中,所述光电转换部可以对照射到所述半导体芯片的与设置有所述配线区域的所述表面不同的表面上的所述入射光进行光电转换。

[0029]

此外,本公开的第二方面是摄像元件的制造方法,所述方法包括:光电转换部设置步骤,在该步骤中,在一个半导体基板上设置对入射光进行光电转换的光电转换部;第二焊盘设置步骤,在该步骤中,在分别设置于两个半导体基板上的配线区域中设置第二焊盘,所述第二焊盘形成有凸部,所述凸部朝着当所述配线区域被粘合在一起时用于粘合的表面;绝缘膜形成步骤,在该步骤中,在所述第二焊盘的表面上形成绝缘膜;第一焊盘设置步骤,在该步骤中,在所述配线区域的设置有所述第二焊盘的表面上设置第一焊盘,当所述配线区域被粘合在一起时所述第一焊盘是彼此接合的;以及粘合步骤,在该步骤中,使所述两个半导体基板的分别设置有所述第一焊盘的所述配线区域粘合在一起,并且使相应的所述第一焊盘彼此接合。

[0030]

此外,在该第二方面中,所述方法还可以包括通过所设置的所述第二焊盘进行测试的测试步骤。此外,所述绝缘膜形成步骤可以包括:在设置有已经进行了所述测试的所述第二焊盘的所述配线区域中形成所述绝缘膜。

[0031]

本公开的该方面提供了将绝缘膜设置于测试焊盘的正面上的效果。本发明预期能够在测试之后对测试焊盘进行保护。

附图说明

[0032]

图1是示出根据本公开实施方案的摄像元件的构造例的图。

[0033]

图2是示出根据本公开实施方案的摄像元件的构造例的框图。

[0034]

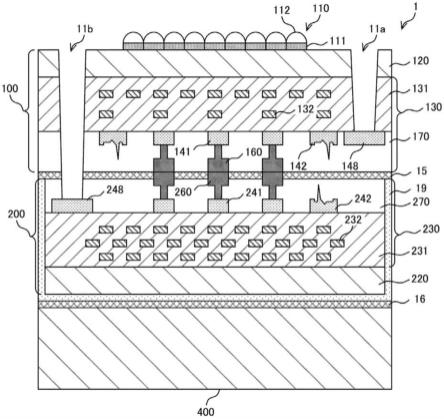

图3是示出根据本公开第一实施方案的摄像元件的构造例的图。

[0035]

图4是示出根据本公开第一实施方案的焊盘的构造例的图。

[0036]

图5是示出根据本公开实施方案的测试例的图。

[0037]

图6是示出根据本公开第一实施方案的绝缘膜的构造例的图。

[0038]

图7是示出根据本公开第一实施方案的绝缘膜的另一构造例的图。

[0039]

图8是示出根据本公开第一实施方案的摄像芯片的制造方法的示例的图。

[0040]

图9是示出根据本公开第一实施方案的摄像芯片的制造方法的示例的图。

[0041]

图10是示出根据本公开第一实施方案的摄像芯片的制造方法的示例的图。

[0042]

图11是示出根据本公开第一实施方案的摄像芯片的制造方法的示例的图。

[0043]

图12是示出根据本公开第一实施方案的摄像元件的制造方法的示例的图。

[0044]

图13是示出根据本公开第一实施方案的摄像元件的制造方法的示例的图。

[0045]

图14是示出根据本公开第一实施方案的摄像元件的制造方法的示例的图。

[0046]

图15是示出根据本公开第一实施方案的摄像元件的制造方法的示例的图。

[0047]

图16是示出根据本公开第一实施方案的摄像元件的另一构造例的图。

[0048]

图17是示出根据本公开第二实施方案的测试焊盘的构造例的图。

[0049]

图18是示出根据本公开第三实施方案的摄像元件的构造例的图。

[0050]

图19是示出根据本公开第四实施方案的摄像元件的构造例的图。

[0051]

图20是示出根据本公开第四实施方案的摄像元件的另一构造例的图。

[0052]

图21是示出相机的示意性构造例的框图,该相机是可以应用本技术的摄像装置的示例。

具体实施方式

[0053]

接下来,将参照附图来说明用于实施本公开的方案(在下文中,称为实施方案)。在以下附图中,相同或相似的部分由相同或相似的附图标记和符号来表示。另外,将按以下顺序说明实施方案。

[0054]

1.第一实施方案

[0055]

2.第二实施方案

[0056]

3.第三实施方案

[0057]

4.第四实施方案

[0058]

5.相机的应用例

[0059]

《1.第一实施方案》

[0060]

[摄像元件的外观]

[0061]

图1是示出根据本公开实施方案的摄像元件的构造例的图。图1是示出摄像元件1的外观的图。图1所示的摄像元件1由半导体芯片来构造而成,并且作为裸片被安装在基板20上。基板20相当于构成半导体封装的基板等,并且用于传送摄像元件1的信号的焊盘21被设置在该基板上。摄像元件1粘合到基板20,并通过引线接合方式连接到焊盘21。具体地,设置于摄像元件1上的焊盘和基板20上的焊盘21借助于接合线30彼此电连接。摄像元件1的引线接合用焊盘被设置在构成摄像元件1的半导体芯片的内层,并且接合线经由在摄像元件1的上表面上形成的开口部11连接进去。另外,稍后说明的像素阵列部50被设置在摄像元件1的上表面上。

[0062]

[摄像元件的构造]

[0063]

图2是示出根据本公开实施方案的摄像元件的构造例的框图。摄像元件1包括像素阵列部50、垂直驱动部60、列信号处理部70和控制部80。

[0064]

像素阵列部50被构造成具有以二维格子形式排列着的像素110。这里,像素110生成对应于照射光的图像信号。每个像素110包括产生对应于照射光的电荷的光电转换部。另外,每个像素110还包括像素电路。像素电路基于由光电转换部产生的电荷来生成图像信号。图像信号的生成通过由垂直驱动部60生成的控制信号来控制,这将在后面进行说明。信号线51和52以xy矩阵形式设置于像素阵列部50中。信号线51是用于传送像素110中的像素电路的控制信号的信号线,其对应于像素阵列部50的每行而配置着,并且是针对设置于各行中的像素110共用地布线而成的。信号线52是用于传送由像素110的像素电路生成的图像信号的信号线,其对应于像素阵列部50的每列而设置着,并且是针对设置于各列中的像素110共用地布线而成的。光电转换部和像素电路被形成在半导体基板上。

[0065]

垂直驱动部60生成像素110的像素电路的控制信号。该垂直驱动部60将所生成的控制信号通过图2中的信号线51传送到像素110。列信号处理部70处理从像素110经由图2中的信号线52传送过来的图像信号。列信号处理部70中的处理相当于例如将像素110中生成的模拟图像信号转换为数字图像信号的模数转换。由列信号处理部70处理过的图像信号作为摄像元件1的图像信号而被输出。控制部80整体上控制摄像元件1。控制部80生成并输出

用于控制垂直驱动部60和列信号处理部70的控制信号,从而控制摄像元件1。由控制部80生成的控制信号通过信号线81和82被传送到垂直驱动部60和列信号处理部70。

[0066]

[摄像元件的截面构造]

[0067]

图3是示出根据本公开第一实施方案的摄像元件的构造例的图。图3是示出摄像元件1的构造例的示意性截面图。摄像元件1通过将多个半导体芯片粘合在一起来构造而成。具体地,图3中所示的摄像元件1包括粘合在一起的摄像芯片100和逻辑芯片200。此外,摄像元件1还包括氧化膜19、氧化膜接合层15和16以及支撑基板400。

[0068]

摄像芯片100是其中设置有上述的包括像素110的像素阵列部50的半导体芯片,并且也是生成图像信号的半导体芯片。摄像芯片100包括半导体基板120和配线区域130。

[0069]

半导体基板120是其上形成有像素110的诸如光电转换部和像素电路等元件的半导体基板。半导体基板120可以由例如硅(si)形成。从半导体基板120的背面侧用入射光照射光电转换部。在半导体基板120的背面侧,对应于每个各像素110都设置有颜色滤光片111和片上透镜112。具有这种构造的摄像元件1被称为背面照射型摄像元件。

[0070]

配线区域130是其中形成有配线的区域,这些配线用于将信号传送到设置于半导体基板120上的元件。该配线区域130被设置于半导体基板120的正面侧。配线区域130包括绝缘层131和配线层132。配线层132是用于将信号传送到设置于半导体基板120上的元件的配线。参照图2说明的信号线51等由配线层132形成。例如,配线层132可以由诸如铜(cu)等金属形成。绝缘层131将配线层132绝缘。该绝缘层131可以由例如氧化硅(sio2)等绝缘材料形成。注意,配线层132和绝缘层131均可以形成为多层。处于不同层中的配线层132可以通过将在稍后进行说明的通孔插塞133彼此连接。

[0071]

此外,焊盘被设置在配线区域130中。各焊盘是由诸如铝(al)等金属形成的电极状端子。这种焊盘包括排列着的焊盘141、测试焊盘142和接合焊盘148。

[0072]

焊盘141是连接到配线层132并且被用来传送信号的焊盘。该焊盘141也是会连接到将在稍后进行说明的表面焊盘160的焊盘。

[0073]

测试焊盘142是用于对摄像芯片100进行测试的焊盘。与焊盘141一样,该测试焊盘142连接到配线层132,通过该测试焊盘来传送信号。通过该测试焊盘142传送的信号包括用于测试摄像芯片100的控制信号和在测试期间由摄像芯片100生成的信号。另外,测试焊盘142形成有凸部(将在稍后进行说明的凸部144),这些凸部朝着当摄像芯片100和逻辑芯片200粘合在一起时它们的用于粘合的表面。

[0074]

摄像芯片100的测试可以通过例如半导体测试设备来执行。半导体测试设备可以将用于测试的控制信号输入到摄像芯片100并且可以检测来自摄像芯片100的诸如图像信号等输出信号,从而判定摄像芯片100是否为无缺陷产品。通过将已经判定为无缺陷产品的摄像芯片100应用于摄像元件1中就可以提高摄像元件1的产量。可以使用测试探针来执行控制信号的输入和输出信号的检测。该测试探针设置有金属针头。通过使测试探针的该针头与测试焊盘142发生触针式接触,测试探针的针头和测试焊盘142彼此电连接,从而可以传送用于测试的信号。在该触针式接触时,针头的尖端与测试焊盘142接触。在测试焊盘142的正面上形成有诸如氧化物等膜。为了穿透该膜从而与测试焊盘142的金属部分接触,测试探针的针头利用相对高的压力与测试焊盘142接触。结果,在测试之后,针头痕迹残留在测试焊盘142的正面上。具体地,在测试之后,在测试焊盘142的正面上形成了图3中所示的凹

凸不平。

[0075]

接合焊盘148是连接到参照图1所说明的接合线30的焊盘。在接合焊盘148的背面上,设置有从摄像芯片100的背面侧贯通半导体基板120和配线区域130的开口部11a。通过该开口部11a来实施引线接合。

[0076]

绝缘膜170是将测试焊盘142绝缘的膜。此外,绝缘膜170被设置在测试焊盘142与用于粘合的表面之间以保护测试焊盘142。该绝缘膜170可以由绝缘材料形成。具体地,绝缘膜170可以由诸如sio2等氧化物形成。此外,绝缘膜170可以形成得包含诸如氮化硅(sin)等氮化物。如上所述,在测试之后,在测试焊盘142的正面上形成了凹凸不平。如果这样的凸部与对面的逻辑芯片200的焊盘等发生干涉,则半导体芯片可能会被损坏或者可能由于信号泄漏而发生误操作。因此,将测试焊盘142设置在距摄像芯片100的正面较深的位置处,并且用绝缘膜170覆盖着。这就可以防止出现诸如逻辑芯片200受到损坏等问题。

[0077]

绝缘膜170被形成为具有能够覆盖上述凸部的厚度。如果该绝缘膜170的厚度不足,则在处于凸部的尖端附近的绝缘膜170中会形成空隙。当将摄像芯片100和逻辑芯片200粘合在一起时该空隙会成为障碍。此外,作为稍后所述的表面焊盘160的材料的cu可能会从该空隙扩散到配线区域130。此外,如果形成有该空隙,那么作为凸部的材料的al可能会在形成表面焊盘160时发生扩散,并由此污染了制造设备。为了防止这种障碍,绝缘膜170需要被形成为具有预定的膜厚度。稍后将会说明绝缘膜170的细节。

[0078]

表面焊盘160是被设置在配线区域130的正面上并且被用来传送信号的焊盘。图3中所示的表面焊盘160是隔着焊盘141被设置在配线区域130的正面上并且信号能够经由其予以传送的示例。此外,当摄像芯片100和逻辑芯片200被粘合在一起时,表面焊盘160连接到逻辑芯片200的表面焊盘(稍后所述的表面焊盘260)。信号可以经由彼此连接起来的表面焊盘160和表面焊盘260在摄像芯片100和逻辑芯片200之间传送。表面焊盘160可以由cu制成。如将在稍后说明的,表面焊盘160可以被形成为具有与测试焊盘142不同的尺寸。

[0079]

注意,焊盘141、测试焊盘142、接合焊盘148和表面焊盘160也可以被认为是设置于配线区域130中的配线的一部分。此外,绝缘膜170可以被认为是设置于配线区域130中的绝缘层的一部分。表面焊盘是权利要求中记载的第一焊盘的示例。测试焊盘142是权利要求中记载的第二焊盘的示例。接合焊盘148是权利要求中记载的第三焊盘的示例。

[0080]

逻辑芯片200是其中设置有用于处理由摄像芯片100生成的图像信号的处理电路的半导体芯片。此外,用于生成摄像芯片100的控制信号的控制电路可以被设置在逻辑芯片200中。参照图2而被说明的垂直驱动部60、列信号处理部70和控制部80可以被设置在逻辑芯片200中。逻辑芯片200包括半导体基板220和配线区域230。

[0081]

半导体基板220可以是与半导体基板120一样的半导体基板,在该半导体基板220上可以形成有诸如垂直驱动部60和列信号处理部70等元件。

[0082]

配线区域230可以与配线区域130一样是其中形成有配线的区域,该配线用于将信号传送到设置于半导体基板220中的元件,并且配线区域230包括绝缘层231和配线层232。

[0083]

此外,焊盘241、测试焊盘242和接合焊盘248被设置在配线区域230中。与焊盘141一样,焊盘241是用来传送信号的焊盘。与测试焊盘142一样,测试焊盘242是用来传送用于测试逻辑芯片200的信号的焊盘。与接合焊盘148一样,接合焊盘248是连接到接合线30的焊盘。与接合焊盘148不同的是,在接合焊盘248的表面上形成有开口部11b。该开口部11b是贯

通摄像芯片100和将在稍后进行说明的绝缘膜270的开口部。通过开口部11b来实施设置于逻辑芯片200上的接合焊盘248的引线接合。焊盘241、测试焊盘242和接合焊盘248可以由al制成。

[0084]

与绝缘膜170一样,绝缘膜270是将测试焊盘242绝缘且用于保护测试焊盘242的膜。该绝缘膜270可以由诸如sio2等氧化物或诸如sin等氮化物形成。

[0085]

表面焊盘260与表面焊盘160一样是被设置在配线区域230的表面上并且用于传送信号的焊盘,并且也是连接到表面焊盘160的焊盘。表面焊盘260可以由铜制成。

[0086]

注意,焊盘241、测试焊盘242、接合焊盘248和表面焊盘260也可以被认为是设置于配线区域230中的配线的一部分。此外,绝缘膜270可以被认为是设置于配线区域230中的绝缘层的一部分。此外,表面焊盘260是权利要求中记载的第一焊盘的示例。测试焊盘242是权利要求中记载的第二焊盘的示例。接合焊盘248是权利要求中记载的第三焊盘的示例。

[0087]

氧化膜接合层15被设置于摄像芯片100和逻辑芯片200之间以便将摄像芯片100与逻辑芯片200接合。该氧化膜接合层15由诸如sio2等氧化物形成,以便通过氧化膜接合法来接合摄像芯片100和逻辑芯片200。在该氧化膜接合法中,通过等离子体处理等使诸如sio2等氧化物的表面活性化,并且由此活性化的氧化膜通过加热压接来粘合到一起。在图3中所示的摄像元件1中,在设置于逻辑芯片200的配线区域230的表面上的氧化膜接合层15与摄像芯片100的配线区域130之间进行氧化膜接合。在摄像芯片100的绝缘膜170的表面和逻辑芯片200的绝缘膜270的表面由氧化物形成的情况下,可以省去氧化膜接合层15,因而在绝缘膜170和270之间进行氧化膜接合。

[0088]

氧化膜19是包围逻辑芯片200的氧化膜。氧化膜19用于保护逻辑芯片200。氧化膜19可以由sio2制成。

[0089]

支撑基板400是用于支撑摄像芯片100和逻辑芯片200的基板。对于该支撑基板400,可以使用si基板。支撑基板400通过氧化膜接合层16粘合到逻辑芯片200。

[0090]

如上所述,经由氧化膜接合层15把摄像芯片100的绝缘膜170和逻辑芯片200的绝缘膜270接合起来。此时,面对着的表面焊盘160和260在位置上相互对准并且通过加热压接而相互接合。这就可以将摄像芯片100和逻辑芯片200粘合在一起。在摄像芯片100和逻辑芯片200之间,把配线区域130和配线区域230隔着氧化膜接合层15以及绝缘膜170和270粘合到一起。

[0091]

通过将测试焊盘142和242设置于距摄像芯片100和逻辑芯片200的接合面较深的位置处并且通过在测试焊盘142和242上设置绝缘膜170和270,可以防止这些测试焊盘与面对着它们的半导体芯片接触。这就可以将测试焊盘142和242设置于粘合在一起的摄像芯片100和逻辑芯片200中的相对位置处。图3中右侧所示的测试焊盘142和242示出了这种相对状态。注意,与图3中左侧所示的测试焊盘142一样,可能未布置有相对的测试焊盘242。

[0092]

[焊盘的构造]

[0093]

图4是示出根据本公开第一实施方案的焊盘的构造例的图。图4是示出测试焊盘142等的构造例的示意性截面图。如图4所示,焊盘141、测试焊盘142和接合焊盘148可以被设置于配线区域130的同一层中。此外,焊盘141、测试焊盘142和接合焊盘148均连接到配线层132。焊盘141等与配线层132是通过通孔插塞133彼此连接的。通孔插塞133由柱状金属形成,用于把作为不同层的配线层132彼此连接起来,并且还用于把配线层132与焊盘141等彼

此连接起来。

[0094]

此外,保护金属膜可以被设置于焊盘141、测试焊盘142和接合焊盘148的表面上。该保护金属膜是用于保护焊盘141等的金属膜,并且可以由层叠起来的钛(ti)膜和氮化钛(tin)膜形成。可替代地,可以使用层叠起来的钽(ta)膜和氮化钽(tan)膜。保护金属膜151被设置于焊盘141的表面上,保护金属膜152被设置于测试焊盘142的表面上,并且保护金属膜158被设置于接合焊盘148的表面上。

[0095]

表面焊盘160被设置于焊盘141的表面上。该表面焊盘160由焊盘161和通孔插塞162组成。焊盘161是埋入绝缘膜170中的焊盘,并且也是与配线区域130的表面邻接的焊盘。通孔插塞162把焊盘141和焊盘161彼此连接起来。图4中示出了其中一个通孔插塞162被设置于焊盘141和161之间的示例。在焊盘141和161之间可以设置有多个通孔插塞162。

[0096]

焊盘161和通孔插塞162可以由cu制成,并且也可以同时形成。例如,焊盘161和通孔插塞162可以通过镀铜来形成。具体地,可以通过以下过程来形成。首先,在绝缘膜170中形成具有焊盘161和通孔插塞162的形状的开口部。接下来,在该开口部中形成用于防止cu扩散的保护层(未示出)。接下来,与绝缘膜邻接地设置籽晶层(未示出),然后进行电镀,从而在具有开口部的绝缘膜170的表面上设置了cu膜。之后,对绝缘膜170的表面上的cu膜进行研磨,以去除开口部以外的cu,从而可以形成表面焊盘160。对cu的研磨可以通过化学机械研磨(cmp:chemical mechanical polishing)来进行。注意,当形成开口部时,部分地去除了保护金属膜151。

[0097]

如上所述,测试焊盘142是与测试用测试探针的针头接触的焊盘。测试探针的针头的接触使得在测试焊盘142上形成凸部144。通过将测试焊盘142设置于距表面焊盘160的表面较深的位置处,可以防止凸部144与将要粘合的逻辑芯片200发生接触。此外,通过设置有绝缘膜170,可以保护形成有凸部144的测试焊盘142。此外,绝缘膜170可以保护逻辑芯片200使其免于受到测试焊盘142的凸部144的影响。

[0098]

注意,图4中所示的测试焊盘142是其中在与测试探针的针头接触的区域中形成有凹部143的示例。通过设置有凹部143,测试之后的凸部144的尖端可以位于距表面焊盘160的表面较深的位置处,从而可以确保裕量。

[0099]

如上所述,接合焊盘148是连接到接合线30的焊盘。开口部11形成在接合焊盘148的背面。当形成开口部11时,接合焊盘148的一部分被去除从而形成凹部。

[0100]

参见图4,还设置有模仿焊盘(imitation pad)149。该模仿焊盘149是不用于传送任何信号的焊盘,并且不与配线层132连接。该模仿焊盘149是所谓的虚设焊盘,并且也是设置于未设置有任何焊盘141等的区域中、且用来使绝缘膜170等的厚度均一的焊盘。保护金属膜159被设置于模仿焊盘149的表面上。

[0101]

模仿焊盘149、焊盘141、表面焊盘160、测试焊盘142和接合焊盘148可以被形成为具有不同的尺寸。为了允许测试用探针的针头接触,测试焊盘142可以被形成为在平面图中具有相对较大的尺寸。另一方面,表面焊盘160被形成为具有相对较小的尺寸。这是为了减少将会在稍后进行说明的制造过程中实施cmp时出现的凹陷。其上设置有该表面焊盘160的焊盘141也被形成为具有相对较小的尺寸。因此,测试焊盘142可以被形成为具有大于表面焊盘160的尺寸。此外,接合焊盘148被形成为具有相对较大的尺寸以用于引线接合。此外,模仿焊盘149可以被形成为具有例如约3μm的宽度。此外,例如,焊盘141和表面焊盘160可以

分别被形成为具有约5μm的宽度。此外,例如,测试焊盘142可以被形成为具有50μm以下的宽度。此外,例如,接合焊盘148可以被形成为具有50μm至100μm的宽度。这样,各焊盘可以被形成为具有适用于该焊盘预期用途的尺寸。

[0102]

[使用测试焊盘的测试]

[0103]

图5是示出根据本公开实施方案的测试的示例的图。图5是示出使用测试焊盘142的测试状态的图。同时,图5中未示出保护金属膜152。

[0104]

图5中的a示出了测试之前的测试焊盘142。在测试焊盘142的正面上形成有凹部143。薄的绝缘膜170a被设置于测试焊盘142的正面和侧面上的除凹部143以外的区域中。

[0105]

图5中的b示出了正在测试的测试焊盘142。在测试开始时,测试探针的针头3与测试焊盘142的凹部143接触。此时,针头3的尖端刺入测试焊盘142的正面。结果,作为测试焊盘142的材料的al翘起从而形成凸部144。

[0106]

图5中的c示出了测试之后的测试焊盘142。测试探针的针头3被撤去,并且在测试焊盘142的正面上形成了作为针头痕迹的凹部145。通过这样进行测试,在测试焊盘142上形成了凸部144。

[0107]

[绝缘膜的构造]

[0108]

图6是示出根据本公开第一实施方案的绝缘膜的构造例的图。图6是示出绝缘膜170的结构例的图。图6中的a示出了绝缘膜170的一个示例。在图6中的a中,绝缘膜170被设置于测试焊盘142的正面和配线区域130的表面之间。因此,绝缘膜170的处于测试焊盘142的正面上方的厚度是与从测试焊盘142的正面到配线区域130的表面的高度相当的厚度。为了将绝缘膜170形成得具有能够覆盖测试焊盘142的正面上的凸部144的形状,需要将绝缘膜170的厚度t1设计为大于凸部144的高度、且还包括依据制造过程而定的裕量的值。例如,该绝缘膜170的厚度t1可以被设定为650nm以上。在这种情况下,表面焊盘160的距焊盘141正面的高度h与作为绝缘膜170的厚度的厚度t1大致相同。

[0109]

图6中的b示出了其中绝缘膜170的厚度不足的示例。如上所述,在制造表面焊盘160时,通过cmp来研磨绝缘膜170和构成表面焊盘160的cu膜。在cmp中,使用含有研磨剂的化学液体(研磨液)。如果绝缘膜170的厚度不足,则会在处于凸部144附近的绝缘膜170中形成空隙(空隙651)。该空隙651会导致摄像芯片100和逻辑芯片200粘合在一起的强度降低。此外,如果作为表面焊盘160的材料的cu埋入到空隙651中并相应地扩散到配线区域130中,则会导致绝缘层131的绝缘电阻的降低等。图6中的b示出了其中测试焊盘142的凸部144被cmp中所使用的化学液体溶出并且由此形成了空隙651的示例。图6中的b中的虚线表示凸部144被溶出。发生溶出的作为测试焊盘142的材料的al可能会污染cmp研磨设备和半导体芯片。为了防止这种问题的发生,需要将上述值应用于绝缘膜170的厚度t1。

[0110]

图6中的c示出了其中在测试焊盘142的正面上形成有凹部143的示例。当形成有凹部143时,绝缘膜170的厚度t1相当于从凹部143的底面到配线区域130的表面的高度。

[0111]

[绝缘膜的另一构造]

[0112]

图7是示出根据本公开第一实施方案的绝缘膜的另一构造例的图。图7中所示的绝缘膜170由多个绝缘材料层形成,这是与图6所示的绝缘膜170的不同之处。图7中所示的绝缘膜170由绝缘材料膜171~173组成。绝缘材料膜171和173均可以由sio2膜形成。绝缘材料膜172可以由sin膜形成。换句话说,图7中所示的绝缘膜170由两层sio2膜和插入在这两层

sio2膜之间的sin膜组成。跟绝缘材料膜171和173一样,由sin制成的绝缘材料膜172是用于保护测试焊盘142的膜。此外,绝缘材料膜172还可以被用作在制造表面焊盘160时的cmp研磨过程中的蚀刻停止膜。此外,通过设置有绝缘材料膜172,可以减小半导体基板120的翘曲。

[0113]

[摄像芯片的制造方法]

[0114]

图8至图11是示出根据本公开第一实施方案的摄像芯片的制造方法的示例的图。图8至图11也是示出了摄像芯片100的制造过程的示例的图。以摄像芯片100为例,将说明根据本公开实施方案的半导体芯片的制造过程。

[0115]

首先,在呈晶圆状的半导体基板120上形成诸如光电转换部等元件,并且形成配线区域130的绝缘层131和配线层132(未示出)(图8的a)。该步骤是权利要求中记载的光电转换部设置步骤的示例。

[0116]

接下来,在绝缘层131的表面上形成焊盘141等的材料膜601。例如,这可以通过使用溅射法等形成al膜来实现。接下来,形成保护金属膜151等的材料膜602。例如,这可以通过使用溅射法等将ti膜和tin膜彼此层叠来实现(图8中的b)。

[0117]

接下来,形成焊盘141和测试焊盘142。这可以通过如下方式来实现:在材料膜602的表面上的将要设置有焊盘141等的区域中涂敷抗蚀剂,并且使用该抗蚀剂作为掩模以蚀刻掉除将要设置有焊盘141的区域以外的材料膜601和602(图8中的c)。该步骤是权利要求中记载的第二焊盘设置步骤的示例。

[0118]

接下来,将薄的绝缘膜170a设置于包括焊盘141等在内的配线区域130的表面上。例如,这可以通过使用化学气相沉积(cvd:chemical vapor deposition)法形成作为绝缘膜170a的材料的sio2膜来实现(图8中的d)。

[0119]

接下来,去除位于测试焊盘142的表面的中心区域处的绝缘膜170a和保护金属膜152。这可以通过干法蚀刻来实现。通过该蚀刻,可以形成凹部143(图9中的e)。

[0120]

接下来,逐个地测试呈晶圆状的摄像芯片100。测试探针的针头3与测试焊盘142接触以便针对测试焊盘142执行测试信号的输入和输出(图9中的f)。该步骤是权利要求中记载的测试步骤的示例。

[0121]

获取测试之后的呈晶圆状的摄像芯片100之中的无缺陷芯片的位置。结果,筛选出了无缺陷的摄像芯片100(图9中的g)。

[0122]

接下来,在绝缘层131的表面上设置绝缘膜170(绝缘膜170b)。该绝缘膜170b是具有能够覆盖焊盘141和测试焊盘142的厚度的绝缘膜(图10中的h)。该步骤是权利要求中记载的绝缘膜形成步骤的示例。

[0123]

接下来,在与焊盘141相邻的绝缘膜170中形成开口部603和604。开口部603和604分别是对应于通孔插塞162和焊盘161的开口部。例如,这可以通过使用干法蚀刻去除开口部603和604所在区域中的绝缘膜170来实现(图10中的i)。

[0124]

接下来,在绝缘膜170的表面上设置用于表面焊盘160的材料膜605。此时,材料膜605也被设置到开口部603和604中。这可以通过镀cu膜来实现(图11中的j)。接下来,去除设置于绝缘膜170的除开口部603和604所在区域以外的表面上的材料膜605。这可以通过cmp来实现。因此,可以形成通孔插塞162和焊盘161,从而完成了表面焊盘160(图11中的k)。该步骤是权利要求中记载的第一焊盘设置步骤的示例。

[0125]

通过上述这些步骤,可以制造出呈晶圆状的摄像芯片100。通过类似的步骤,可以形成呈晶圆状的逻辑芯片200。之后,通过对其上布置有逻辑芯片200的晶圆进行切割,就可以将逻辑芯片200分离成各个单片。注意,可以在逻辑芯片200粘合到摄像芯片100之后将摄像芯片100分离成各个单片。

[0126]

[摄像元件的制造方法]

[0127]

图12至图15是示出根据本公开第一实施方案的摄像元件的制造方法的示例的图。图12至图15也是示出了摄像元件1的制造过程的示例的图。

[0128]

首先,将作为测试结果而被判定为无缺陷产品的逻辑芯片200排列到重排基板606上。此时,排列了多个逻辑芯片200,以与呈晶圆状的摄像芯片100对准。各逻辑芯片200可以通过设置于重排基板606上的粘合剂607来予以固定(图12中的a)。

[0129]

接下来,将其上设置有氧化膜接合层15的支撑基板608设置到逻辑芯片200的绝缘膜270的表面上并进行接合。这可以通过氧化膜接合法来实现(图12中的b)。

[0130]

接下来,将其上设置有逻辑芯片200的支撑基板608倒置,然后去除重排基板606和粘合剂607(图12中的c)。

[0131]

接下来,研磨半导体基板220的背面侧,以进行减薄。例如,这可以通过cmp来实现(图12中的d)。

[0132]

接下来,在逻辑芯片200的周围设置氧化膜609。例如,这可以通过通过使用cvd法形成sio2膜来实现。接下来,研磨氧化膜609的表面并进行平坦化(图13中的e)。

[0133]

接下来,将其上设置有氧化膜接合层16的支撑基板400粘合到氧化膜609的表面。这可以通过氧化膜接合法来实现(图13中的f)。

[0134]

接下来,将支撑基板400倒置,然后去除支撑基板608。例如,这可以通过对支撑基板608进行蚀刻来实现(图13中的g)。

[0135]

接下来,将表面焊盘260设置于逻辑芯片200上。这可以通过图10中的i所示的步骤至图11中的k所示的步骤来实现(图13中的h)。

[0136]

接下来,将摄像芯片100粘合到逻辑芯片200。这可以通过将参照图11中的k所说明的呈晶圆状的摄像芯片100粘合到设置于支撑基板400上的逻辑芯片200来实现。这种粘合是通过氧化膜接合法来实现的(图14中的i)。该步骤是权利要求中记载的粘合步骤的示例。

[0137]

接下来,研磨摄像芯片100的半导体基板120的背面侧,以进行减薄(图14中的j)。

[0138]

接下来,在摄像芯片100的半导体基板120上对应于每个像素110而设置颜色滤光片111和片上透镜112(图15中的k)。另外,形成开口部11(未示出)。

[0139]

接下来,将粘合在一起的摄像芯片100和逻辑芯片200分离成各个单片(图15中的l)。因此,可以制造出摄像元件1。

[0140]

《摄像元件的另一构造》

[0141]

图16是示出根据本公开第一实施方案的摄像元件的另一构造例的图。图16是类似于图3而示出了摄像元件1的构造例的示意性截面图。图16与图3的摄像元件1的不同之处在于,摄像芯片100的尺寸和逻辑芯片200的尺寸彼此不同。

[0142]

图16中示出了其中逻辑芯片200被形成为具有小于摄像芯片100的尺寸的示例。测试焊盘242被设置于逻辑芯片200中,并且绝缘膜270被设置于测试焊盘242和逻辑芯片200的背面之间。

[0143]

在图16中所示的摄像芯片100中,测试焊盘142可以被设置于不与逻辑芯片200相对着的位置处。在这种情况下,可以省去测试焊盘142周围的绝缘膜170。

[0144]

如上所述,在根据本公开第一实施方案的摄像元件1中,测试探针的针头3与分别设置于摄像芯片100和逻辑芯片200上的测试焊盘142和242接触,以测试这些芯片。已经经过测试的摄像芯片100和逻辑芯片200粘合在一起以形成摄像元件1。在该粘合之前,绝缘膜170和270分别被设置于测试焊盘142和242上。这可以防止摄像元件1因为被形成在测试焊盘142和242的表面上的凸部而受到损坏。

[0145]

《2.第二实施方案》

[0146]

在根据上述第一实施方案的摄像元件1中,测试探针的针头3与测试焊盘142的正面接触。相比之下,根据本公开第二实施方案的摄像元件1与上述第一实施方案的不同之处在于,保护金属膜被设置于测试焊盘142的正面上,并且测试探针的针头3与保护金属膜接触。

[0147]

[焊盘的构造]

[0148]

图17是示出根据本公开第二实施方案的测试焊盘的构造例的图。图17是类似于图4而示出了测试焊盘142的构造例的示意性截面图。图17与参照图4所说明的测试焊盘142的不同之处在于,保护金属膜152也被设置于凹部143的表面上。

[0149]

图17中所示的保护金属膜152可以通过在参照图9中的e所说明的蚀刻步骤中留下保护金属膜152来形成。因此,在测试焊盘142的表面上设置有保护金属膜152,从而使得测试探针的针头3与保护金属膜152的表面接触。由于保护金属膜152具有比作为测试焊盘142的材料的al更高的硬度,因此可以减小凸部144的高度。这可以使凸部144的尖端与摄像芯片100的正面分隔开。藉此,可以提高凸部144的尖端和摄像芯片100的正面之间的距离的裕量。此外,可以减小绝缘膜170的厚度,从而可以使摄像元件1更薄。在图17中,绝缘膜170的厚度可以被设定为从保护金属膜152的表面到配线区域130的表面的厚度(图中所示的t2)。

[0150]

摄像元件1的除上述构造以外的其他构造与本公开第一实施方案中所说明的摄像元件1的构造相同,因此将省略对它们的说明。

[0151]

如上所述,在根据本公开第二实施方案的摄像元件1中,保护金属膜152也被设置于测试焊盘142的表面上的与测试探针的针头3接触的区域上。这就可以将测试焊盘142的凸部144的高度设计得较小,从而提高制造摄像元件1时的产量。

[0152]

《3.第三实施方案》

[0153]

根据上述第一实施方案的摄像元件1由粘合在一起的摄像芯片100和逻辑芯片200这两个半导体芯片组成。相比之下,根据本公开第三实施方案的摄像元件1与上述第一实施方案的不同之处在于,将三个以上的半导体芯片粘合在一起。

[0154]

[摄像元件的构造]

[0155]

图18是示出根据本公开第三实施方案的摄像元件的构造例的图。图18是类似于图3而示出了摄像元件1的构造例的示意性截面图。图18与图3所示的摄像元件1的不同点在于,除了设置有摄像芯片100和逻辑芯片200之外,还设置有半导体芯片300。

[0156]

半导体芯片300是也粘合到摄像芯片100的半导体芯片。该半导体芯片300包括半导体基板320和配线区域330。测试焊盘342、表面焊盘360和绝缘膜370被设置于配线区域330中。使用测试焊盘342来进行测试,并且在接粘合时将表面焊盘360接合到摄像芯片100

的表面焊盘160。在半导体芯片300中,例如,可以设置有参照图2所说明的垂直驱动部60。在这种情况下,列信号处理部70和控制部80可以被设置于逻辑芯片200中。此外,其他处理电路等可以被设置于半导体芯片300中。例如,在半导体芯片300中可以设置有用于执行图像信号的存储处理的存储器电路或用于执行ai(artificial intelligent:人工智能)处理的电路。

[0157]

注意,表面焊盘360是权利要求中记载的第一焊盘的示例。测试焊盘342是权利要求中记载的第二焊盘的示例。

[0158]

摄像元件1的除上述构造以外的其他构造与本公开第一实施方案中所述的摄像元件1的构造相同,因此将省略对它们的说明。

[0159]

如上所述,根据本公开第三实施方案的摄像元件1由粘合在一起的三个以上半导体芯片组成。因此,可以让摄像元件1小型化。

[0160]

《4.第四实施方案》

[0161]

在根据上述第三实施方案的摄像元件1中,逻辑芯片200和半导体芯片300都粘合到摄像芯片100。相比之下,根据本公开第四实施方案的摄像元件1与上述第三实施方案的不同之处在于,摄像芯片100、逻辑芯片200和半导体芯片300依次层叠着。

[0162]

[摄像元件的构造]

[0163]

图19是示出根据本公开第四实施方案的摄像元件的构造例的图。图19是类似于图18而示出了摄像元件1的构造例的示意性截面图。图19与图18所示的摄像元件1的不同之处在于,摄像芯片100、逻辑芯片200和半导体芯片300依次层叠着。

[0164]

在图19中所示的摄像元件1中,逻辑芯片200的表面焊盘260和半导体芯片300的表面焊盘360彼此接合且粘合到一起。摄像芯片100粘合到逻辑芯片200的背面。摄像芯片100和逻辑芯片200之间的信号传送可以通过由两个通孔插塞连接起来而构成的双接触部12来进行。双接触部12的一个通孔插塞连接到摄像芯片100的焊盘141,并且另一个通孔插塞连接到逻辑芯片200的焊盘241。此外,这两个通孔插塞通过摄像芯片100背面上的导体来彼此连接。这就可以在摄像芯片100的焊盘141和逻辑芯片200的焊盘241之间传送信号。

[0165]

《摄像元件的另一构造》

[0166]

图20是示出根据本公开第四实施方案的摄像元件的另一构造例的图。图20是类似于图19而示出了摄像元件1的构造例的示意性截面图。图20与图19所示的摄像元件1的不同之处在于,摄像芯片100的表面焊盘和逻辑芯片200的表面焊盘接合在一起,并且半导体芯片300粘合到逻辑芯片200的背面。在图20中所示的摄像元件1中,可以将半导体芯片300设置成代替参照图3所说明的摄像元件1的支撑基板400。摄像芯片100的焊盘141和半导体芯片300的焊盘341通过双接触部12彼此连接。

[0167]

摄像元件1的除上述构造以外的其他构造与本公开第三实施方案中所述的摄像元件1的构造相同,因此将省略对它们的说明。

[0168]

如上所述,根据本公开第四实施方案的摄像元件1由依次层叠的三个以上半导体芯片组成。即使在摄像元件1中设置有具有大致相同尺寸的这些半导体芯片时,它们也可以粘合在一起。

[0169]

《5.相机的应用例》

[0170]

根据本公开的技术(本技术)可以应用于各种产品。例如,本技术可以被实现为安

装在诸如相机等摄像装置上的摄像元件。

[0171]

图21是示出相机的示意性构造例的框图,该相机是本技术可适用的摄像装置的示例。图21中的相机1000包括透镜1001、摄像元件1002、摄像控制部1003、透镜驱动部1004、图像处理部1005、操作输入部1006、帧存储器1007、显示部1008和记录部1009。

[0172]

透镜1001是相机1000的摄影透镜。透镜1001会聚来自被摄体的光,使光入射到将在稍后进行说明的摄像元件1002,由此形成被摄体的图像。

[0173]

摄像元件1002是对来自被摄体的由透镜1001会聚的光进行摄像的半导体元件。摄像元件1002生成与照射光相对应的模拟图像信号,将该模拟图像信号转换为数字图像信号,并且输出该数字图像信号。

[0174]

摄像控制部1003用于控制摄像元件1002中的摄像。摄像控制部1003通过生成控制信号并将控制信号输出到摄像元件1002来控制摄像元件1002。另外,基于从摄像元件1002输出过来的图像信号,摄像控制部1003可以在相机1000中进行自动对焦。这里,自动对焦是指能够检测出透镜1001的焦点位置并自动调整焦点位置的体系。作为自动对焦,可以使用依据设置于摄像元件1002中的相位差像素来检测出像面相位差从而检测出焦点位置的方法(像面相位差自动对焦)。另外,还可以采用将图像的对比度最大的位置检测为焦点位置的方法(对比度自动对焦)。基于所检测出的焦点位置,摄像控制部1003通过透镜驱动部1004来调整透镜1001的位置,由此进行自动对焦。同时,例如,摄像控制部1003可以被构造为搭载有固件(firmware)的数字信号处理器(dsp:digital signal processor)。

[0175]

透镜驱动部1004基于摄像控制部1003的控制来驱动透镜1001。透镜驱动部1004可以通过使用内置马达来改变透镜1001的位置从而驱动透镜1001。

[0176]

图像处理部1005用于处理由摄像元件1002生成的图像信号。例如,该处理相当于:用于生成与每个像素的红色、绿色和蓝色对应的图像信号之中的颜色不足的图像信号的去马赛克处理、用于去除图像信号中的噪声的降噪处理、用于对图像信号进行编码的处理等。例如,图像处理部1005可以由搭载有固件的微型计算机来构造而成。

[0177]

操作输入部1006用于接收来自相机1000的用户的操作输入。例如,按键或触摸面板可以被用作操作输入部1006。由操作输入部1006接收到的操作输入可以被传送到摄像控制部1003和图像处理部1005。之后,就可以开始与操作输入相对应的处理,例如,诸如被摄体的摄像等处理。

[0178]

帧存储器1007是用于存储作为与一个画面相对应的图像信号的帧的存储器。帧存储器1007由图像处理部1005来控制,并且保持着图像处理期间中的帧。

[0179]

显示部1008显示由图像处理部1005处理后的图像。例如,液晶面板可以被用作显示部1008。

[0180]

记录部1009记录由图像处理部1005处理后的图像。例如,存储卡或硬盘可以被用作记录部1009。

[0181]

上面已经说明了可以应用本公开的相机。本技术可以应用于上述组件之中的摄像元件1002。具体地,图1所示的摄像元件1可以应用于摄像元件1002。

[0182]

第二实施方案的测试焊盘142的构造可以与其他实施方案组合。具体地,图17所示的保护金属膜152可以应用于图18至图20的测试焊盘142等。

[0183]

最后,上述各个实施方案的说明仅仅是本公开的示例,并且本公开不限于上述各

个实施方案。因此,不言而喻的是,在不脱离本公开的技术构思的保护范围内,可以根据设计等进行除上述实施方案以外的各种改变。

[0184]

此外,本说明书中所记载的效果仅仅是示例而不是限制性的。同样,也可以获得其他效果。

[0185]

另外,上述各个实施方案中的附图为示意图,并且各个部分的尺寸比等不一定与实际情况一致。另外,附图当然包括因图面不同而导致尺寸关系和比例不同的部分。

[0186]

本技术也可以是如下技术方案。

[0187]

(1)摄像元件,包括:

[0188]

多个半导体芯片,所述多个半导体芯片各者都包括半导体基板和配线区域,所述多个半导体芯片粘合在一起,

[0189]

所述多个半导体芯片之中的一个半导体芯片设置有对入射光进行光电转换的光电转换部,

[0190]

所述多个半导体芯片之中的两个半导体芯片各者都包括第一焊盘,所述两个半导体芯片的所述配线区域的表面粘合在一起,所述第一焊盘设置于所述配线区域的所述表面上,并且当所述两个半导体芯片的所述配线区域的所述表面被粘合时所述第一焊盘是彼此接合的,所述两个半导体芯片之中的至少一个半导体芯片还包括第二焊盘和绝缘膜,所述第二焊盘设置于所述配线区域中,所述绝缘膜设置于所述第二焊盘和用于粘合的所述表面之间,所述第二焊盘形成有朝着用于粘合的所述表面的凸部。

[0191]

(2)根据(1)所述的摄像元件,其中,所述绝缘膜被形成为具有覆盖所述第二焊盘的厚度。

[0192]

(3)根据(2)所述的摄像元件,其中,所述绝缘膜被形成为具有650nm以上的厚度。

[0193]

(4)根据(1)至(3)中任一项所述的摄像元件,其中,所述绝缘膜由绝缘材料形成。

[0194]

(5)根据(4)所述的摄像元件,其中,所述绝缘膜包含由硅化合物制成的所述绝缘材料。

[0195]

(6)根据(1)至(5)中任一项所述的摄像元件,还包括:保护金属膜,其被设置于所述第二焊盘的表面上。

[0196]

(7)根据(1)至(6)中任一项所述的摄像元件,其中,所述多个半导体芯片之中的至少一个半导体芯片还包括用于连接到外部电路的第三焊盘。

[0197]

(8)根据(7)所述的摄像元件,其中,所述第三焊盘与所述第二焊盘设置于同一层中。

[0198]

(9)根据(1)至(8)中任一项所述的摄像元件,其中,所述第二焊盘被形成为具有与所述第一焊盘不同的尺寸。

[0199]

(10)根据(9)所述的摄像元件,其中,所述第二焊盘被形成为具有比所述第一焊盘大的尺寸。

[0200]

(11)根据(1)至(10)中任一项所述的摄像元件,其中,所述第二焊盘由铝制成。

[0201]

(12)根据(1)至(11)中任一项所述的摄像元件,其中,所述第二焊盘具有通过触针式测试而形成的所述凸部。

[0202]

(13)根据(1)至(12)中任一项所述的摄像元件,其中,所述第二焊盘具有在凹部中形成的所述凸部,所述凹部被设置于所述第二焊盘的朝着用于粘合的所述表面的一侧上。

[0203]

(14)根据(1)至(13)中任一项所述的摄像元件,其中,所述多个半导体芯片之中的所述两个半导体芯片各者都包括被设置成与另一者中的所述第二焊盘相对着的所述第二焊盘。

[0204]

(15)根据(1)至(14)中任一项所述的摄像元件,其中,所述第一焊盘由铜制成。

[0205]

(16)根据(1)至(15)中任一项所述的摄像元件,其中,所述多个半导体芯片之中的至少一个半导体芯片设置有处理电路,所述处理电路用于处理基于所述光电转换而生成的图像信号。

[0206]

(17)根据(16)所述的摄像元件,其中,所述多个半导体芯片之中的所述两个半导体芯片各者都设置有所述处理电路并且被粘合在一起。

[0207]

(18)根据(1)所述的摄像元件,其中,所述光电转换部对照射到所述半导体芯片的与设置有所述配线区域的表面不同的表面上的所述入射光进行光电转换。

[0208]

(19)摄像元件的制造方法,所述方法包括:

[0209]

光电转换部设置步骤,在该步骤中,在一个半导体基板上设置对入射光进行光电转换的光电转换部;

[0210]

第二焊盘设置步骤,在该步骤中,在分别设置于两个半导体基板上的配线区域中设置第二焊盘,所述第二焊盘形成有凸部,所述凸部朝着当所述配线区域被粘合在一起时用于粘合的表面;

[0211]

绝缘膜形成步骤,在该步骤中,在所述第二焊盘的表面上形成绝缘膜;

[0212]

第一焊盘设置步骤,在该步骤中,在所述配线区域的设置有所述第二焊盘的表面上设置第一焊盘,当所述配线区域被粘合在一起时所述第一焊盘是彼此接合的;以及

[0213]

粘合步骤,在该步骤中,使所述两个半导体基板的分别设置有所述第一焊盘的所述配线区域粘合在一起,并且使相应的所述第一焊盘彼此接合。

[0214]

(20)根据(19)所述的摄像元件的制造方法,还包括:

[0215]

通过所设置的所述第二焊盘进行测试的测试步骤,

[0216]

其中,所述绝缘膜形成步骤包括:在设置有已经进行了所述测试的所述第二焊盘的所述配线区域中形成所述绝缘膜。

[0217]

[附图标记列表]

[0218]

1、1002:摄像元件

[0219]

15、16:氧化膜接合层

[0220]

19:氧化膜

[0221]

50:像素阵列部

[0222]

60:垂直驱动部

[0223]

70:列信号处理部

[0224]

80:控制部

[0225]

100:摄像芯片

[0226]

110:像素

[0227]

120、220、320:半导体基板

[0228]

130、230、330:配线区域

[0229]

141、161、241、341:焊盘

[0230]

142、242、342:测试焊盘

[0231]

143:凹部

[0232]

148、248:接合焊盘

[0233]

149:模仿焊盘

[0234]

151、152、158、159:保护金属膜

[0235]

160、260、360:表面焊盘

[0236]

162:通孔插塞

[0237]

170、170a、170b、270:绝缘膜

[0238]

171~173:绝缘材料膜

[0239]

200:逻辑芯片

[0240]

300:半导体芯片

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。