一种高性能的混合抖动型dpwm电路结构

技术领域

1.本发明涉及混合信号集成电路领域,特别涉及数字开关电源,实现对输出电压的精确控制,具体涉及一种高性能的混合抖动型dpwm电路结构。

背景技术:

2.近年来,随着人们对消费类电子产品性能的要求日益提高,电源管理芯片逐渐成为研究的热点。作为电子产品的能量中枢,电源的输出要求高效且稳定,在负载发生突变时,能够在很短的时间内重新恢复到正常工作所需的电压和电流,并保持稳定的输出。

3.如今,dc-dc开关电源根据反馈控制的实现方式可以分为两类,即模拟控制方式(模拟电源)和数字控制方式(数字电源)。模拟开关电源通过误差放大器将采样的信号进行求差和放大,经过模拟电路的反馈回路生成控制信号送给脉宽调制器(pulse width modulation,pwm),调制出特定占空比信号,用于控制功率管的开启和关断时间,从而达到调节输出电压的目的。数字开关电源通过模数转换器(analog-to-digital converter,adc)对输出电压或电流进行实时采样量化,通过一系列控制算法反馈出控制信号,利用数字脉宽调制器(digital pulse width modulation,dpwm)生成特定占空比信号,以控制功率管的开启和关断时间。

4.相较于模拟开关电源,数字开关电源具有稳定性好、抗干扰能力强、设计方式灵活、移植性强、功耗低、系统效率高等优点,因此得到了广泛的关注。高分辨率的dpwm模块是实现全数字高精度高开关频率数字开关电源的重要组成部分,它的分辨率直接关系到输出电压的稳态精度。高精度的dpwm已成为目前的研究热点,也是数字控制开关电源中亟待解决的一个问题。

技术实现要素:

5.为克服现有技术的不足,实现高频率、高线性度、高分辨率、高精度的数字脉宽调制(dpwm),本发明旨在提出一种高性能的混合抖动型dpwm电路结构,主要应用于数字开关电源等领域。

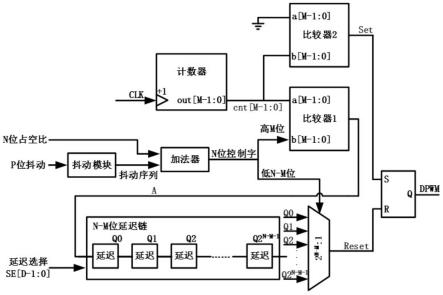

6.为实现本发明的目的,本发明提供的一种高性能的混合抖动型dpwm电路结构,包括抖动模块、加法器、延迟可控的延迟链、计数器1、计数器2、比较器、rs触发器,所述延迟可控的延迟链包括多路选择器和多个延迟单元,

7.所述抖动模块用于根据外部输入的p位抖动位产生相应的抖动序列;

8.所述加法器用于将抖动序列与外部输入的n位占空比相加,得到n位控制字,同时,将n位控制字拆分为高m位和低n-m位;

9.所述计数器用于对外部输入时钟clk进行计数,输出计数值cnt[m-1:0];

[0010]

所述比较器1用于将计数值cnt[m-1:0]与高m位进行比较,当两者相等时输出高电平信号a;

[0011]

所述比较器2用于将计数值cnt[m-1:0]与m’b0进行比较,当cnt[m-1:0]为全0时,

输出置位信号set;

[0012]

所述rs触发器根据所述置位信号set进行置位,将dpwm信号置为高电平;

[0013]

所述a信号进入延迟可控的延迟链产生延迟信号作为多路选择器的输入端,所述低n-m位作为多路选择器的选择端,输出相对应的延迟信号作为复位信号reset,所述reset触发rs触发器进行复位,将dpwm信号复为低电平。

[0014]

其中,所述延迟可控的延迟链内有n-m个延迟单元,每个延迟单元的延迟时间可控,可通过外部d位延迟选择se[d-1:0]进行控制。

[0015]

其中,所述a信号进入延迟可控的延迟链产生延迟信号,具体为:

[0016]

所述a信号进入n-m位延迟链,依次产生2n-m个延迟信号q0、q1、q2

……

q2n-m-1,作为2n-m:1选择器的输入端。

[0017]

其中,所述抖动模块的数字“抖动”通过在多个开关周期取平均值的方法。

[0018]

与现有技术相比,本发明的有益效果为,

[0019]

本发明提出的一种高性能的混合型dpwm电路结构,其可实现高频率、高线性度、高分辨率、高精度的dpwm。

[0020]

本发明提出的结构克服了传统的计数型dpwm和延迟型dpwm的缺点。当计数型dpwm精度较高时,其工作频率将成指数形式上升,同时带来较大的面积与功耗损失。延迟型dpwm由于温度或工艺偏差的存在,会导致延迟链的延迟时间不相等,同时延迟型dpwm占用面积很大。然而本发明提出的混合抖动型dpwm结合了二者的结构特点,将计数型dpwm线性度高、精度高的优势,以及延迟型dpwm可在高频时钟工作的优势结合起来,同时结合数字“抖动”的原理提高dpwm的分辨率。

[0021]

另外,本发明还提出了一种延迟可控的延迟链结构。

[0022]

另外,本发明提出的混合抖动型dpwm结构,能够在高精度与高频率的矛盾之间进行折中,同时利用数字“抖动”原理提高了dpwm的分辨率。

附图说明

[0023]

图1本技术实施例中混合抖动型dpwm的整体结构图

[0024]

图2本技术实施例中2位数字“抖动”的原理图;

[0025]

图3本技术实施例中8路选择延迟模块的结构图;

[0026]

图4本技术实施例中4位占空比 2位抖动位的混合抖动型dpwm结构图;

[0027]

图5本技术实施例中工作时序图。

具体实施方式

[0028]

需要说明的是,在不冲突的情况下,本技术中的实施例及实施例中的特征可以相互组合。

[0029]

以下结合附图和具体实施例对本发明作进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

[0030]

对于本领域技术人员而言,可根据具体情况理解上述术语在本技术中的具体含义。

[0031]

本发明提出一种高性能的混合抖动型dpwm电路结构,由抖动模块、加法器、延迟可

控的延迟链、多路选择器、计数器、比较器、rs触发器等模块构成,其结构如图1所示。

[0032]

其中,外部输入n位占空比,同时输入p位抖动位。抖动模块根据p位抖动位产生相应的抖动序列,数字“抖动”通过在多个开关周期取平均值的方法,实现低精度到高精度的转化,具体原理将在下面进行详细说明。

[0033]

加法器将抖动序列与n位占空比相加,得到n位控制字。将n位控制字拆分为高m位和低n-m位,对高位和低位分别进行处理,高m位进行粗调,低n-m位进行细调,从而提高了分辨率。

[0034]

外部输入时钟clk触发m位计数器进行计数,输出计数值cnt[m-1:0]。比较器1将计数值cnt[m-1:0]与高m位进行比较,当两者相等时输出高电平信号a。比较器2将计数值cnt[m-1:0]与m’b0进行比较,当cnt[m-1:0]为全0时,输出置位信号set。set触发rs触发器进行置位,将dpwm信号置为高电平。

[0035]

延时可控的延迟链内有n-m个延迟单元,每个延迟单元的延迟时间可控,可通过外部d位延迟选择se[d-1:0]进行控制,其具体原理将在下面进行详细说明。a信号进入n-m位延迟链,依次产生2

n-m

个延迟信号q0、q1、q2

……

q2

n-m-1

,作为2

n-m

:1选择器的输入端。低n-m位作为多路选择器的选择端,输出相对应的延迟信号作为复位信号reset。reset触发rs触发器进行复位,将dpwm信号复位为低电平。由此产生了与n位控制字对应占空比的dpwm信号。

[0036]

首先说明数字“抖动”的原理。以2位抖动位为例进行说明,即p=2。dpwm控制主电路功率管的通断,进而影响输出电压的大小。数字“抖动”是基于输出电压平均值的原理,假设每4个输出dpwm波形中有一个脉冲增加了1个lsb所对应的宽度,则输出电压的平均值将增加1/4个lsb所对应的输出电压值,相应的dpwm的分辨率也将提高1/4个lsb,即同理,可实现1/2个lsb和3/4个lsb,如图2所示。2位数字抖动查找表见表1,其根据2位抖动位进行选择,产生相应的抖动序列,依次在每4个开关周期内,将n位占空比与抖动序列相加,得到新的n位控制字。下面以2位抖动位2’b01,4位占空比4’b0110为例进行说明,根据查找表可知,生成抖动序列0 0 0 1,依次在4个开关周期内加在4位占空比上,得到4’b0110、4’b0110、4’b0110、4’b0111。输出的dpwm占空比依次为则利用平均化原理进行处理后的dpwm占空比为由此可见,利用2位数字抖动在4位dpwm的基础上实现了等效为6位的dpwm,提高了2位分辨率。同理,利用3位数字抖动,每8个开关周期产生一组抖动序列,其数字抖动查找表见

[0037]

表2,最终将提高3位分辨率。

[0038]

2位抖动位数字抖动序列000 0 0 0010 0 0 1100 1 0 1110 1 1 1

[0039]

表1

[0040]

3位抖动位数字抖动序列0000 0 0 0 0 0 0 00010 0 0 0 0 0 0 10100 0 0 1 0 0 0 10110 0 1 0 0 1 0 11000 1 0 1 0 1 0 11010 1 0 1 1 0 1 11100 1 1 1 0 1 1 11110 1 1 1 1 1 1 1

[0041]

表2

[0042]

然后说明延迟可控的延迟链的原理,延迟可控的延迟链由多路选择器和多个延迟单元组成。

[0043]

下面以8路选择延迟模块为例进行说明,其由28个延迟单元和8选1选择器构成,如图3所示。每个矩形模块都是一个标准工艺库中的标准延迟单元,se[2:0]代表3位选择码,采用的是8条延迟路径和一个8选1选择器的结构。从in到out存在8条延时不同的路径,每条路径包括图中所示数目的延迟单元,se[2:0]控制选通的路径,达到调整延迟单元总延时的目的。该模块通过8选1选择器在由标准单元块组成的8条延时路径中选择出对应的传输路径,从而得到对应的延时。若每个延迟单元的延时均为t0,多路选择器的延时为td,则8条延时路径可以产生td、td t0、td 2t0、td 3t0、td 4t0、td 5t0、td 6t0、td 7t0共8个不同的延时,通过se[2:0]选择所需要的延时路径,从而实现了延迟可控的延迟链。

[0044]

下面以4位占空比、高2位、低2位、2位抖动位、8路延时可控为例进行说明,即n=4,m=2,p=2,d=3,其结构图如图4所示。假设外部输入4位占空比4’b1010,2位数字“抖动”2’b01。抖动模块根据2位抖动位2’b01产生相应的抖动序列0 0 0 1,每4个开关周期为一次循环,将2位占空比与抖动序列依次相加。第一个开关周期将4位占空比与抖动序列0相加,第二个开关周期将4位占空比与抖动序列0相加,第三个开关周期将4位占空比与抖动序列0相加,第四个开关周期将4位占空比与抖动序列1相加,从而得到4位新的占空比控制字duty[3:0],即4’b1010、4’b1010、4’b1010、4’b1011。2位数字“抖动”通过在4个开关周期取平均值的方法,实现低精度到高精度的转化,提高了2位分辨率。

[0045]

当控制字duty[3:0]=4’b1010时,将4位控制字拆分为高2位2’b10和低2位2’b10,对高位和低位分别进行处理,高2位进行粗调,低2位进行细调。外部时钟clk触发计数器进行计数,输出计数值cnt[1:0]。比较器2将计数值cnt[1:0]与全0进行比较,当cnt[1:0]=2’b00时,输出置位信号set。set触发rs触发器进行置位,将dpwm信号置为高电平。比较器1将计数值cnt[1:0]与高两位2’b10进行比较,当cnt[1:0]=2’b10时,输出高电平信号a。信号a作为延迟链的输入信号,在内部通过3个延迟单元进行延时,分别产生延迟信号q0、q1、q2、q3,作为四选一选择器的输入端。低2位2’b10作为选择器的选择端,输出相对应的延迟信号q2,作为复位信号reset。reset触发rs触发器进行复位,将dpwm信号复位为低电平。由此产生了与4位控制字对应占空比的dpwm信号,其工作的时序图如图5所示。

[0046]

延迟链中每个延迟单元的延时为

△

t,时钟clk的周期需要刚好为

△

t的4倍,即tclk=4

△

t。为满足该关系,可利用上述延时可控的延迟单元进行延时控制,通过3位延时

控制位se[2:0],选择合适的延时路径,进而得到合适的延迟时间。从时序图中可以看出,由于输入4位占空比4’b1010,2位抖动位2’b01对应的抖动序列为0 0 0 1,因此在4个开关周期内依次产生新的占空比控制字duty1[3:0]=4’b1010、duty2[3:0]=4’b1010、duty3[3:0]=4’b1010、duty4[3:0]=4’b1011,最终输出与之对应的10

△

t(粗调8

△

t 细调2

△

t)、10

△

t(粗调8

△

t 细调2

△

t)、10

△

t(粗调8

△

t 细调2

△

t)、11

△

t(粗调8

△

t 细调3

△

t)。同时,利用数字“抖动”平均化的原理,dpwm提高了1/4个lsb,等效于提高了2位分辨率,最终将达到6位的分辨率,实现了高精度、高分辨率的dpwm输出。

[0047]

以上所述仅是本发明的优选实施方式,应当指出的是,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。