1.本公开大体上涉及一种半导体封装结构和半导体结构。

背景技术:

2.在具有高裸片堆叠的多芯片封装(multiple chip package,mcp)结构中,高低导线之间由于空间有限而间隙狭窄,因此存在导线短路的风险。并且,当导线接触裸片边缘时,可能会发生电流泄漏。

3.此外,mcp结构中的堆叠结构复杂,例如,mcp结构可以包括包含多个动态随机存取存储器(dram)裸片的dram堆叠、包含多个nand裸片的nand堆叠以及控制器等。mcp结构中的多个dram裸片因存在短路风险不能并排设置,使得dram堆叠在垂直方向上具有较高的高度。mcp结构在垂直方向上具有较高的高度,大约为1 mm。并且,mcp结构至少需要2个间隔件来实现堆叠下控制器(cus),制备工艺复杂且成本较高。

4.鉴于此,本领域迫切需要提供改进方案以解决上述问题。

技术实现要素:

5.鉴于此,本公开提供了一种半导体封装结构,所述半导体封装结构包括非导电缓冲构件,从而可以避免导线短路和电流泄漏的风险。进一步地,所述半导体封装结构中的裸片可以并排设置,因此半导体封装结构在垂直方向上的高度较低并且可以不包括间隔件。

6.一方面,根据本公开的一实施例,一种半导体封装结构包括基板、第一裸片体和第一非导电缓冲构件。基板具有第一表面。第一裸片体设置在所述第一表面上。所述第一裸片体限定由多个周围表面围绕的顶表面。第一非导电缓冲构件包括覆盖所述第一裸片体的所述周围表面的第一部分以及覆盖所述第一裸片体的所述顶表面的一部分的第二部分。

7.根据本公开的一些实施例,所述第一非导电缓冲构件沿所述第一裸片体的所述周围表面的整个长度延伸。

8.根据本公开的一些实施例,所述第一非导电缓冲构件延伸越过所述第一裸片体的拐角。

9.根据本公开的一些实施例,所述第一非导电缓冲构件围绕所述第一裸片体的所述顶表面。

10.根据本公开的一些实施例,所述第一裸片体包括靠近所述第一裸片体的所述周围表面布置的至少一个第一接合焊盘。所述第一非导电缓冲构件的所述第二部分布置在所述第一接合焊盘的外侧且靠近所述周围表面。所述第一非导电缓冲构件的所述第二部分避开且暴露所述第一接合焊盘。

11.根据本公开的一些实施例,所述第一裸片体经由连接到所述第一接合焊盘的第一导线电连接所述基板。

12.根据本公开的一些实施例,所述第一导线接触所述第一非导电缓冲构件。

13.根据本公开的一些实施例,所述第一导线部分地嵌入所述第一非导电缓冲构件

中。

14.根据本公开的一些实施例,所述第一非导电缓冲构件由环氧树脂制成。

15.根据本公开的一些实施例,所述半导体封装结构进一步包括第二裸片体和第二非导电缓冲构件。所述第二裸片体堆叠在所述第一裸片体上并且与所述第一裸片体形成阶梯构造,所述第二裸片体限定由多个周围表面围绕的顶表面。所述第二非导电缓冲构件包括覆盖所述第二裸片体的所述周围表面的第一部分以及覆盖所述第二裸片体的所述顶表面的一部分的第二部分。

16.根据本公开的一些实施例,所述第二裸片体包括靠近所述第二裸片体的所述周围表面布置的至少一个第二接合焊盘。所述第二非导电缓冲构件的所述第二部分布置在所述第二接合焊盘的外侧且靠近所述第二裸片体的所述周围表面。所述第二非导电缓冲构件的所述第二部分避开且暴露所述第二接合焊盘。其中所述第二接合焊盘相对于所述第一接合焊盘垂直偏移。

17.根据本公开的一些实施例,所述第二导线接触所述第二非导电缓冲构件。

18.根据本公开的一些实施例,所述第二导线部分地嵌入所述第二非导电缓冲构件中。

19.根据本公开的一些实施例,所述第一裸片体是dram裸片,且所述第二裸片体是 nand裸片。

20.根据本公开的一些实施例,所述第一非导电缓冲构件的硬度比所述第一裸片体的硬度低。

21.另一方面,根据本公开的一实施例,一种半导体结构包括多个裸片和缓冲结构。所述多个裸片在载体的表面上布置成二维阵列,其中所述多个裸片中的相邻裸片彼此分隔开一分隔。所述缓冲结构填充在所述多个裸片中的相邻裸片之间的所述分隔中,同时暴露所述多个裸片的顶表面。

22.根据本公开的一些实施例,所述多个裸片的所述二维阵列包括多个行和多个列,其中列分隔的宽度不同于行分隔的宽度。

23.根据本公开的一些实施例,所述多个裸片包括已知的良好裸片。

24.根据本公开的一些实施例,所述多个裸片的每个包括靠近其边缘区域布置的凸块焊盘。所述缓冲结构与所述凸块焊盘以一间隙保持距离。

25.根据本公开的一些实施例,所述缓冲结构的硬度比所述裸片的硬度低。

26.本实用新型的额外层面及优点将部分地在后续说明中描述、显示、或是经由本实用新型实施例的实施而阐释。

附图说明

27.图1示出了示例性的半导体封装结构的剖视图。

28.图2示出了根据本公开一实施例的半导体封装结构的剖视图。

29.图3示出了根据本公开一实施例的半导体封装结构的剖视图。

30.图4示出了现有技术中具有间隔件的半导体封装结构的剖视图。

31.图5a示出了根据本公开一实施例的导体封装结构的剖视图。

32.图5b示出了图5a中的导体封装结构的部分俯视图。

33.图6a至图6f示出了制备根据本公开一实施例的半导体封装结构中的裸片的方法,其中图6c是图6b中所示的步骤的剖视图。

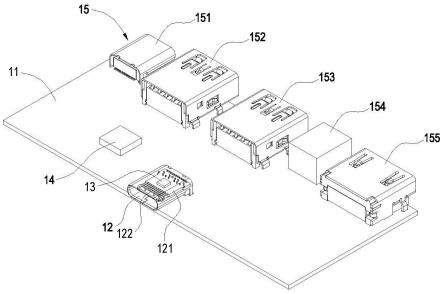

34.图7示出了根据本公开一实施例的半导体结构的俯视图。

35.根据惯例,图示中所说明的各种特征可能并非按比例绘制。因此,为了清晰起见,可任意扩大或减小各种特征的尺寸。图示中所说明的各部件的形状仅为示例性形状,并非限定部件的实际形状。另外,为了清楚起见,可简化图示中所说明的实施方案。因此,图示可能并未说明给定设备或装置的全部组件。最后,可贯穿说明书和图示使用相同参考标号来表示相同特征。

具体实施方式

36.为更好的理解本实用新型的精神,以下结合本实用新型的部分实施例对其作进一步说明。

37.以下揭示内容提供了多种实施方式或例示,其能用以实现本揭示内容的不同特征。下文所述之组件与配置的具体例子系用以简化本揭示内容。当可想见,这些叙述仅为例示,其本意并非用于限制本揭示内容。举例来说,在下文的描述中,将一第一特征形成于一第二特征上或之上,可能包括某些实施例其中所述的第一与第二特征彼此直接接触;且也可能包括某些实施例其中还有额外的组件形成于上述第一与第二特征之间,而使得第一与第二特征可能没有直接接触。此外,本揭示内容可能会在多个实施例中重复使用组件符号和/或标号。此种重复使用乃是基于简洁与清楚的目的,且其本身不代表所讨论的不同实施例和/或组态之间的关系。

38.在本说明书中,除非经特别指定或限定之外,相对性的用词例如:“中央的”、“纵向的”、“侧向的”、“前方的”、“后方的”、“右方的”、“左方的”、“内部的”、“外部的”、“较低的”、“较高的”、“水平的”、“垂直的”、“高于”、“低于”、“上方的”、“下方的”、“顶部的”、“底部的”以及其衍生性的用词(例如“水平地”、“向下地”、“向上地”等等)应该解释成引用在讨论中所描述或在附图中所描示的方向。这些相对性的用词仅用于描述上的方便,且并不要求将本实用新型以特定的方向建构或操作。

39.以下详细地讨论本实用新型的各种实施方式。尽管讨论了具体的实施,但是应当理解,这些实施方式仅用于示出的目的。相关领域中的技术人员将认识到,在不偏离本实用新型的精神和保护范围的情况下,可以使用其他部件和配置。本实用新型的实施可不必包含说明书所描述的实施例中的所有部件或步骤,也可根据实际应用而调整各步骤的执行顺序。

40.图1示出了示例性的半导体封装结构的剖视图。如图1所示,半导体封装结构10 包括基板100、第一裸片体110和第二裸片体120。基板100的第一表面100a的边缘处设置有至少一个接合焊盘1001。第一裸片体110堆叠在基板100的第一表面100a上。第一裸片体110靠近接合焊盘1001并与接合焊盘1001保持一定间隔。第一裸片体110 包括顶表面110a和多个周围表面110b。第一裸片体110包括靠近第一裸片体110的周围表面110b布置于顶表面110a上的至少一个第一接合焊盘1101。第一接合焊盘1101 经由第一导线111连接到接合焊盘1001,以实现第一裸片体110与基板100的电连接。第一导线111不接触第一裸片体110的边缘并且与第一裸片体110的边缘保持第一距离 h1。第二裸片体210堆叠于第一裸片体110的

顶表面110a上。第二裸片体120包括顶表面120a和多个周围表面120b。第二裸片体120包括靠近第二裸片体120的周围表面120b 布置于顶表面120a上的至少一个第二接合焊盘1201。第二裸片体120的第二接合焊盘 1201分别经由第二导线121和第三导线122连接到第一接合焊盘1101和接合焊盘1001,以实现第二裸片体120与第一裸片体110和基板100的电连接。第二导线122不接触第二裸片体120的边缘并且与第二裸片体120的边缘保持第二距离h2。第三导线122与第一导线111和第二导线122之间分别具有第一间隙w1和第二间隙w2。然而,受空间限制,第一间隙w1和第二间隙w2狭窄,存在导线短路风险。另外,第一导线111和第二导线122也容易接触第一裸片体110或第二裸片体120的边缘,从而发生电流泄漏。

41.为克服上述的技术问题,本公开提供了一种包括非导电缓冲构件的半导体封装结构,所述半导体封装结构可以避免导线短路和电流泄漏的风险。

42.图2示出了根据本公开一实施例的半导体封装结构的剖视图。如图2所示,半导体封装结构20包括基板200、第一裸片体210和第一非导电缓冲构件230。

43.基板200具有第一表面200a。基板200的第一表面200a的边缘处设置有至少一个接合焊盘2001。

44.第一裸片体210设置在第一表面200a上。第一裸片体210靠近基板200的接合焊盘2001并与接合焊盘2001保持一定间隔。第一裸片体210限定多个周围表面210b以及由多个周围表面210b围绕的顶表面210a。第一裸片体210包括靠近第一裸片体210 的周围表面210b布置于顶表面210a上的至少一个第一接合焊盘2101。第一接合焊盘 2101经由第一导线211连接到接合焊盘2001,因此第一裸片体210经由第一导线211 电连接基板200。

45.第一非导电缓冲构件230设置在第一裸片体210的边缘处,并包括覆盖第一裸片体 210的周围表面210b的第一部分2301以及覆盖第一裸片体210的顶表面210a的一部分的第二部分2302。第一非导电缓冲构件230可以设置在第一裸片体210的一个边缘处。在一些实施例中,第一部分2301覆盖第一裸片体210的一个周围表面210b并且沿所述一个周围表面210b的整个长度延伸,第二部分2302覆盖顶表面210a的靠近所述一个周围表面210b的一部分并且沿所述一个周围表面210b的整个长度延伸。在一些实施例中,第一部分2301覆盖第一裸片体210的一个周围表面210b并且沿所述一个周围表面 210b的部分长度延伸,第二部分2302覆盖顶表面210a的靠近所述一个周围表面210b 的一部分,并且沿所述一个周围表面210b的所述部分长度延伸。第一非导电缓冲构件 230还可以设置在第一裸片体210的两个或更多个边缘处。在一些实施例中,第一非导电缓冲构件230延伸越过第一裸片体210的一个或多个拐角。在一些实施例中,第一非导电缓冲构件230围绕第一裸片体210的顶表面210a,即,第一部分2301覆盖第一裸片体210的全部周围表面210b并且沿周围表面210b的整个长度延伸,第二部分2302 覆盖顶表面210a的靠近全部外表面210b的部分并且沿周围表面210b的整个长度延伸。

46.第一非导电缓冲构件230的第二部分2302可以布置在第一接合焊盘2101的外侧且靠近周围表面210b。第一非导电缓冲构件230的第二部分2302避开且暴露第一接合焊盘2101。第一非导电缓冲构件230的第二部分2302与第一接合焊盘2101之间具有一定间隙d。由于第一非导电缓冲构件230可以覆盖并保护第一裸片体210的邻近第一接合焊盘2101的边缘,因此连接到第一接合焊盘2101的第一布线211可以贴近第一裸片体 210设置,而不用担心电流泄漏问题。在一些实施例中,第一导线211可以接触第一非导电缓冲构件230。在一

些实施例中,第一导线211部分地嵌入第一非导电缓冲构件230 中。此外,由于第一导线211可以贴近第一裸片体210设置,因此当其他裸片堆叠于第一裸片体210上方或下方时,第一导线211不会影响其他裸片的导线的布置,并为其他裸片的导线的布置提供了充足的空间,因此可以避免导线之间的短路。半导体封装结构 20具有良好的电连接可靠性以及组装和测试良率,而无需担心焊线机到机器之间的差异。

47.第一非导电缓冲构件230的硬度可以比第一裸片体210的硬度低。第一非导电缓冲构件230可以形成为第一裸片体210的平滑曲线边缘。第一非导电缓冲构件230的第一部分2301和第二部分2302可以具有粗糙的表面。

48.第一非导电缓冲构件230可以由各种合适的非导电材料制成。在一些实施例中,第一非导电缓冲构件230的材料可以与裸片附着膜(a die attaching film)的材料相似。在一些实施例中,第一非导电缓冲构件230可以由环氧树脂制成。

49.半导体封装结构20可以应用于任何合适封装结构。在一些实施例中,半导体封装结构20可以应用于mcp结构。在一些实施例中,第一裸片体310是dram裸片。在一些实施例中,第一裸片体310是nand裸片。

50.图3示出了根据本公开另一实施例的半导体封装结构的剖视图。如图3所示,半导体封装结构30包括基板300、第一裸片体310、第二裸片体320、第一非导电缓冲构件 330和第二非导电缓冲构件340。基板300、第一裸片体310和第一非导电缓冲构件330 与图2中的基板200、第一裸片体210和第一非导电缓冲构件230相似,这里不再赘述。

51.第二裸片体320堆叠在第一裸片体310的顶表面310a上并且与第一裸片体310形成阶梯构造。虽然图3中示出了类似于梯形的阶梯构造,但是其不限于此,也可以是类似于平行四边形的阶梯构造或其他阶梯构造。第二裸片体320限定多个周围表面320b 以及由多个周围表面320b围绕的顶表面320a。第二裸片体320包括靠近第二裸片体320 的周围表面320b布置于顶表面320a上的至少一个第二接合焊盘3201。第二接合焊盘 3201相对于第一裸片体310上的第一接合焊盘3101垂直偏移。第二接合焊盘3201分别经由第二导线321和第三导线322连接到第一裸片体310的第一接合焊盘3101和基板 300的接合焊盘3001,以实现第二裸片体320与第一裸片体310和基板300的电连接。

52.第二非导电缓冲构件340包括覆盖第二裸片体320的周围表面320b的第一部分3401 以及覆盖第二裸片体320的顶表面320a的一部分的第二部分3402。第二非导电缓冲构件340与第一非导电缓冲构件330的结构相似,可以设置在第二裸片体320的一个或多个边缘处。在一些实施例中,第一部分3401覆盖第二裸片体320的一个周围表面320b 并且沿所述一个周围表面320b的整个长度延伸,第二部分3402覆盖顶表面320a的靠近所述一个周围表面320b的一部分并且沿所述一个周围表面320b的整个长度延伸。在一些实施例中,第一部分3401覆盖第二裸片体320的一个周围表面320b并且沿所述一个周围表面320b的部分长度延伸,第二部分3402覆盖顶表面320a的靠近所述一个周围表面320b的一部分并且沿所述一个周围表面320b的所述部分长度延伸。在一些实施例中,第二非导电缓冲构件340延伸越过第二裸片体320的一个或多个拐角。在一些实施例中,第二非导电缓冲构件340围绕第二裸片体320的顶表面320a。

53.第二非导电缓冲构件340的第二部分3402可以布置在第二接合焊盘3201的外侧且靠近周围表面320b。第二非导电缓冲构件340的第二部分3402避开且暴露第二接合焊盘

3201。第二非导电缓冲构件340的第二部分3402与第二接合焊盘3201之间具有一定间隙。由于第二非导电缓冲构件340可以覆盖并保护第二裸片体320的邻近第二接合焊盘3201的边缘,因此连接到第二接合焊盘3201的第二布线321可以贴近第二裸片体320 设置,而不用担心电流泄漏问题。在一些实施例中,第一导线321可以接触第二非导电缓冲构件340。在一些实施例中,第二导线321部分地嵌入第二非导电缓冲构件340中。

54.在半导体封装结构30中,第一导线311和第二导线321可以分别贴近第一裸片体 310和第二裸片体320设置,因此第一导线311和第二导线321不会影响第三导线322 的布置,并为第三导线322的布置提供了充足的空间。第三导线322与第一导线311和第二导线322之间分别具有第一间隙w3和第二间隙w4。对比图1和图3可知,图3中的半导体封装结构30具有相对较大的第一间隙w3和第二间隙w4,因此可以避免导线的短路风险。并且,由于第一非导电缓冲构件330和第二非导电缓冲构件340的存在,即使第一导线311和第二导线322接触第一裸片体310或第二裸片体320的边缘,也不会发生电流泄漏。因此,半导体封装结构30具有良好的电连接可靠性以及组装和测试良率。

55.第二非导电缓冲构件340的硬度可以比第二裸片体320的硬度低。第二非导电缓冲构件340可以形成为第二裸片体320的平滑曲线边缘。第二非导电缓冲构件340的第一部分3401和第二部分3402可以具有粗糙的表面。

56.第二非导电缓冲构件340可以由各种合适的非导电材料制成。在一些实施例中,第二非导电缓冲构件340的材料可以与裸片附着膜的材料相似。在一些实施例中,第二非导电缓冲构件340可以由环氧树脂制成。

57.半导体封装结构30可以应用于任何合适的封装结构。在一些实施例中,半导体封装结构30可以应用于mcp结构。在一些实施例中,第一裸片体310和第二裸片体320 均为dram裸片,在一些实施例中,第一裸片体310为dram裸片,第二裸片体320 为nand裸片。将dram裸片设置于堆叠结构中与基板较近之处能够有效减少信号传递路径,进而增加装置运算速度。

58.如前所述,现有技术中的mcp结构通常具有高裸片堆叠和间隔件。然而,当本公开的半导体封装结构20或30应用于mcp结构时,由于本公开的半导体封装结构中的裸片体因受非导电缓冲构件的保护可以并排设置,从而可以降低mcp结构中的裸片堆叠的高度,并且为裸片堆叠提供了多种合适的选择,例如不包括间隔件。下面将参照图 4和图5详细描述上述这两种不同的mcp结构之间的区别。

59.图4示出了现有技术中具有间隔件的半导体封装结构的剖视图。如图4所示,半导体封装结构40包括基板400、第一裸片体410、第二裸片体420、第三裸片体440、第四裸片体460、第五裸片体470、第一间隔件430、第二间隔件450和模塑材料490。第一裸片体410设置在基板400的第一表面400a上。第二裸片体420堆叠在第一裸片体 410上方并且第二裸片体420与第一裸片体410之间设置有第一间隔件430。第三裸片体440设置在基板400的第一表面400a上,并且邻近第一裸片体410。至少两个第二间隔件450围绕第三裸片体440设置,以帮助第三裸片体440支撑悬置于第三裸片体440 上方的第四裸片体460和第五裸片体470。第四裸片体460设置在第三裸片体440和第二间隔件450的上方。第五裸片体470堆叠在第四裸片体460上。模塑材料490设置在基板400的第一表面400a上,并且封装基板400、第一裸片体410、第二裸片体420、第三裸片体440、第四裸片体460、第五裸片体470、第一间隔件430和

第二间隔件45。半导体封装结构40进一步包括位于基板400的第二表面400b上的连接件480以及裸片体之间或裸片体与基板400之间的裸片附着层(图4中仅标出裸片附着层401作为示例)。

60.在图4示出的半导体封装结构40中,体积较大的第一裸片体410和第二裸片体420 因存在短路风险而无法并排设置,因此第一裸片体410、第二裸片体420和第一间隔件 430形成的堆叠结构具有较高的高度。并且由于第三裸片体440的体积较小,无法单独支撑其上方的第四裸片体460和第五裸片体470,因此需要至少两个第二间隔件450。图4中的半导体封装结构40需要设置多个间隔件,并且在垂直方向上具有较高的高度。

61.图5a示出了根据本公开一实施例的导体封装结构的剖视图。图5b示出了图5a中的导体封装结构的部分俯视图。如图5a和图5b所示,半导体封装结构50包括基板500、第一裸片体510、第二裸片体520、第三裸片体540、第四裸片体560、第五裸片体570、第一非导电缓冲构件511、第二非导电缓冲构件521、第三非导电缓冲构件561、第四非导电缓冲构件571和模塑材料490。第一裸片体510和第二裸片体520并排设置在基板 500的第一表面500a上。第四裸片体560堆叠在第一裸片体510和第二裸片体520的顶表面上,第五裸片体570堆叠在第四裸片体560的顶表面上,并且与第四裸片体560形成阶梯构造。第三裸片体540设置在基板500的第一表面500a上并且邻近第一裸片体 510。第一非导电缓冲构件511、第二非导电缓冲构件521、第三非导电缓冲构件561、第四非导电缓冲构件571分别设置在第一裸片体510、第二裸片体520、第四裸片体560 和第五裸片体570的边缘处。模塑材料590设置在基板500的第一表面500a上,并且封装第一裸片体510、第二裸片体520、第三裸片体540、第四裸片体560、第五裸片体 570、第一非导电缓冲构件511、第二非导电缓冲构件521、第三非导电缓冲构件561和第四非导电缓冲构件571。半导体封装结构50进一步包括位于基板500的第二表面500b 上的连接件580以及裸片体之间或裸片体与基板500之间的裸片附着层(图5a中仅标出裸片附着层501作为示例)。

62.如图5b所示,第一裸片体510包括靠近第一裸片体510的周围表面布置于顶表面上的多个第一接合焊盘5101(图5b中用线条表示多个第一接合焊盘5101的设置位置)。多个第一接合焊盘5101分为两列并且分布在第一裸片体510的相对边缘处。多个第一接合焊盘5101经由多条导线(未示出)连接到基板500上的多个接合焊盘5001(图5b 中用线条表示多个接合焊盘5001)。虽然图中示出了多个第一接合焊盘5101设置在第一裸片体510的相对边缘处,但是其不限于此,多个第一接合焊盘5101也可以设置在第一裸片体510的一个或三个边缘处。第一非导电缓冲构件511设置在第一裸片体510的靠近第一裸片体510的相对边缘处以及邻近第二裸片体520的边缘处。在一些实施例中,第一非导电缓冲构件511可以设置在第一裸片体510的四个边缘处。第二裸片体520和第二非导电缓冲构件521与第一裸片体510和第一非导电缓冲构件511相似,这里不再赘述。由于第一裸片体510和第二裸片体520相邻的周围表面分别被第一非导电缓冲构件511和第二非导电缓冲构件521覆盖,因此虽然第一裸片体510和第二裸片体520并排设置也无需担心发生短路问题。

63.并排设置第一裸片体510和第二裸片体520的布置可以使得裸片堆叠高度减半,因此有效地降低半导体封装结构50在垂直方向上的高度。在一些实施例中,半导体封装结构50在垂直方向上的高度可以为约0.8mm。另外,由于体积较大的第一裸片体510 和第二裸片体520可以并排设置,因此体积较小的第四裸片体560和第五裸片体570可以堆叠在第一裸

片体510和第二裸片体520上方,从而无需将第四裸片体560和第五裸片体570堆叠在体积更小的第三裸片体540上方,也无需使用支撑它们的间隔件。因此,半导体封装结构50可以不包括间隔件。半导体封装结构50可以具有简单的制备工艺和较低的工艺成本。

64.半导体封装结构50中的第一非导电缓冲构件511、第二非导电缓冲构件521、第三非导电缓冲构件561、第四非导电缓冲构件571可以具有与图2和图3中的非导电缓冲构件相同的作用(例如,避免电流泄漏和导线短路问题)。因此,半导体封装结构50具有良好的电连接可靠性以及组装和测试良率。

65.在一些实施例中,第一裸片体510和第二裸片体520可以为dram裸片。在一些是实施例中,第三裸片体540可以为控制器裸片,例如专用集成电路(asic)裸片。在一些实施例中,第四裸片体560和第五裸片体570可以为nand裸片。虽然图5a和图 5b仅示出了半导体封装结构50包括五个裸片体,但是其不限于此,半导体封装结构50 可以包括更多个裸片体,并且具有更多合适的布置。

66.图6a至图6f示出了制备根据本公开一些实施例的半导体封装结构中的裸片的方法,其中图6c是图6b中所示的步骤的剖视图。

67.如图6a所示,将多个裸片610设置在载体600的表面600a上。多个裸片610可以通过裸片附着膜(例如图6c和图6d中的裸片附着膜620)设置在基板600的表面600a 上。多个裸片610在载体600的表面600a上布置成二维阵列,并且多个裸片610中的相邻裸片彼此分隔开一定分隔。多个裸片610的二维阵列可以包括多个行和多个列,其中列分隔的宽度可以与行分隔的宽度相同或不同。

68.接着,如图6b所示,将非导电缓冲材料630填充在多个裸片610中的相邻裸片之间的分隔中,同时暴露多个裸片610的顶表面。在一些实施例中,非导电缓冲材料630 为非导电环氧树脂。如图6c所示,可以利用模板印刷工艺将非导电缓冲材料630沿水平方向涂覆到多个裸片610的多个列之间的列分隔中,并沿竖直方向涂覆到多个裸片610 的多个行之间的行分隔中,从而每个裸片610的四个边缘均覆盖有非导电缓冲材料630 并且暴露每个裸片610的顶表面。

69.然后,如图6d所示,通过短时间地加热或利用紫外(uv)光照射来部分地固化非导电缓冲材料630,并且通过冷却来防止非导电缓冲材料630完全固化。由于非导电缓冲材料630是部分固化的,因此在后续进行引线键合工艺时,接触非导电缓冲材料630 的导线可以部分地嵌入非导电缓冲材料630中并且被非导电缓冲材料630固定。

70.如图6e所示,分别沿列分隔和行分隔中的非导电缓冲材料630的中心线进行切割,以获得单个裸片。图6e中的线641表示切割线。

71.如图6f所示,最终得到四个周围表面以及靠近四个周围表面的顶表面的一部分均覆盖有非导电缓冲材料630的单个裸片610。

72.最终形成的单个裸片610可以通过裸片堆叠、引线键合和模塑等工艺形成最终的半导体封装结构。

73.图7示出了根据本公开一实施例的半导体结构的俯视图。如图7所示,一种半导体结构70包括多个裸片710和缓冲结构720。多个裸片710在载体700的表面700a上布置成二维阵列。多个裸片710中的相邻裸片彼此分隔开一定分隔。缓冲结构720填充在多个裸片720中的相邻裸片之间的分隔中,同时暴露多个裸片720的顶表面。缓冲结构 720的硬度比裸片

710的硬度低。在一些实施例中,缓冲结构720包括环氧树脂。多个裸片710的二维阵列包括多个行和多个列。在一些实施例中,列分隔的宽度可以不同于行分隔的宽度。在一些实施例中,列分隔的宽度与行分隔的宽度相同。多个裸片710的每个包括靠近其边缘区域布置的凸块焊盘(图中未示出),缓冲结构720与凸块焊盘以一间隙保持距离(例如图2中的“d”)。多个裸片710可以包括任何已知的良好裸片,例如,dram裸片或nand裸片等。

74.本公开提供了一种包括非导电缓冲构件的半导体封装结构,所述半导体封装结构可以避免导线短路和电流泄漏,并且半导体封装结构可以不包括间隔件并具有较低的裸片堆叠高度。

75.本公开提供了一种包括非导电缓冲结构的半导体结构,所述半导体结构可以避免导线短路和电流泄漏。所述半导体结构可以用于制造不包括间隔件的半导体封装结构,并且所述半导体结构可以为mcp结构提供更多合适的裸片堆叠布置。

76.本说明书中的描述经提供以使所述领域的技术人员能够进行或使用本实用新型。所属领域的技术人员将易于显而易见对本实用新型的各种修改,且本说明书中所定义的一般原理可应用于其它变化形式而不会脱离本实用新型的精神或范围。因此,本实用新型不限于本说明书所述的实例和设计,而是被赋予与本说明书所揭示的原理和新颖特征一致的最宽范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。