1.本公开涉及存储器技术领域,具体而言,涉及一种检测动态随机存储器(dram)字线驱动单元pg高阻的字线驱动电路故障检测方法、装置与电子设备。

背景技术:

2.字线驱动电路是存储器中重要的功能电路,用于控制字线的状态设置。由于集成电路制程精细而复杂,不可避免的会出现制程上的缺陷。特别地,字线驱动电路pg(periphery gate,周边上的栅极)部分由于光刻掩模、opc(optical proximity correction,光学邻近效应修正)异常等因素,会造成pg cd shrink/broken(pg的cd收缩与破坏)现象,导致pg高阻(字线驱动单元nmos栅极高阻)甚至断路,导致字线关闭功能出现故障,存储器功能出现故障。dram中具有大量的重复字线驱动单元,因此pg高阻的检测变得尤为重要。

3.需要说明的是,在上述背景技术部分公开的信息仅用于加强对本公开的背景的理解,因此可以包括不构成对本领域普通技术人员已知的现有技术的信息。

技术实现要素:

4.本公开的目的在于提供一种字线驱动电路故障检测方法、装置与电子设备,用于至少在一定程度上克服字线驱动电路的pg高阻问题无法高效准确检测的问题。

5.根据本公开实施例的第一方面,提供一种字线驱动电路故障检测方法,包括:对待测字线输入驱动信号,对所述待测字线连接的至少一个目标存储单元写入第一电平;对所述待测字线输入停止驱动信号,所述驱动信号和所述停止驱动信号之间的时间差大于等于第一预设值;读取所述目标存储单元;在所述目标存储单元的读取结果不等于所述第一电平时,判断所述待测字线的字线驱动电路存在故障。

6.在本公开的一种示例性实施例中,在对所述待测字线输入停止驱动信号之后,将位线均衡电压设置为第二电平,并对所述目标存储单元的读写控制电路输入位线均衡控制信号,所述第二电平与所述第一电平不同。

7.在本公开的一种示例性实施例中,所述对待测字线输入驱动信号,对所述待测字线连接的至少一个目标存储单元写入第一电平包括:同时对目标页的多个位线写入所述第一电平;顺次对所述目标页的多个待测字线输入所述驱动信号。

8.在本公开的一种示例性实施例中,所述对待测字线输入驱动信号,对所述待测字线连接的至少一个目标存储单元写入第一电平包括:对一条所述待测字线连接的预设数量个目标存储单元写入所述第一电平;顺次对多条待测字线重复以上过程。

9.在本公开的一种示例性实施例中,所述预设数量等于所述待测字线对应的存储阵列的一个突发长度,或者,所述预设数量等于所述待测字线对应的全部存储单元的数量。

10.在本公开的一种示例性实施例中,所述对待测字线输入驱动信号,对所述待测字线连接的至少一个目标存储单元写入第一电平包括:对多条待测字线对应的连接相同位线

的目标存储单元顺次写入所述第一电平。

11.在本公开的一种示例性实施例中,所述目标存储单元分布在多个第一目标行,所述多个第一目标行之间间隔设置有第二目标行。

12.在本公开的一种示例性实施例中,所述待测字线之间间隔设置有空闲字线。

13.在本公开的一种示例性实施例中,所述目标存储单元呈棋盘状排列,或者,所述目标存储单元呈对角线状排列。

14.在本公开的一种示例性实施例中,按照所述待测字线的序号从小到大的方式进行测试之后,再按照所述待测字线的序号从大到小进行测试。

15.在本公开的一种示例性实施例中,所述第一电平为高电平,所述第二电平为低电平。

16.在本公开的一种示例性实施例中,所述第一电平为低电平,所述第二电平为高电平。

17.在本公开的一种示例性实施例中,所述高电平等于电源电压或子字线选择信号,所述低电平等于零电平或字线关闭电压。

18.在本公开的一种示例性实施例中,所述读取所述目标存储单元包括:在按地址对全部目标存储单元完成写入操作后,按地址读取所述目标存储单元。

19.根据本公开实施例的第二方面,提供一种电子设备,包括:存储器;以及耦合到所述存储器的处理器,所述处理器被配置为基于存储在所述存储器中的指令,执行如上述任意一项所述的方法。

20.本公开实施例通过在增加对每条字线的操作使能时间后关闭对应字线,能够在对多条字线进行顺次写入操作时,增加每条字线在操作后被设置为关闭状态的时间,进而增加存在关闭功能故障(字线驱动电路存在故障)的字线连接的存储单元的漏电时间,最后通过检查各存储单元的状态准确地识别出字线驱动电路存在故障的字线,相比现有技术,具有更高的检测效率和检测准确率。

21.应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本公开。

附图说明

22.此处的附图被并入说明书中并构成本说明书的一部分,示出了符合本公开的实施例,并与说明书一起用于解释本公开的原理。显而易见地,下面描述中的附图仅仅是本公开的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

23.图1是本公开实施例中字线驱动电路存在pg高阻的故障示意图。

24.图2是本公开示例性实施例中字线驱动电路故障检测方法的流程图。

25.图3是目标存储单元的读写电路示意图。

26.图4是图3所示电路的写入过程示意图。

27.图5是本公开一个实施例中图3所示电路的写入过程示意图。

28.图6是本公开一个实施例中步骤s1的子流程图。

29.图7是本公开另一个实施例中步骤s1的子流程图。

30.图8a~图8e是本公开实施例中目标存储单元的分布示意图。

31.图9是本公开示例性实施例中一种电子设备的方框图。

具体实施方式

32.现在将参考附图更全面地描述示例实施方式。然而,示例实施方式能够以多种形式实施,且不应被理解为限于在此阐述的范例;相反,提供这些实施方式使得本公开将更加全面和完整,并将示例实施方式的构思全面地传达给本领域的技术人员。所描述的特征、结构或特性可以以任何合适的方式结合在一个或更多实施方式中。在下面的描述中,提供许多具体细节从而给出对本公开的实施方式的充分理解。然而,本领域技术人员将意识到,可以实践本公开的技术方案而省略所述特定细节中的一个或更多,或者可以采用其它的方法、组元、装置、步骤等。在其它情况下,不详细示出或描述公知技术方案以避免喧宾夺主而使得本公开的各方面变得模糊。

33.此外,附图仅为本公开的示意性图解,图中相同的附图标记表示相同或类似的部分,因而将省略对它们的重复描述。附图中所示的一些方框图是功能实体,不一定必须与物理或逻辑上独立的实体相对应。可以采用软件形式来实现这些功能实体,或在一个或多个硬件模块或集成电路中实现这些功能实体,或在不同网络和/或处理器装置和/或微控制器装置中实现这些功能实体。

34.下面结合附图对本公开示例实施方式进行详细说明。

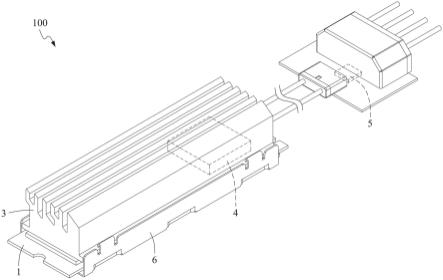

35.图1是本公开实施例中字线驱动电路存在pg高阻的故障示意图。

36.参考图1,在字线驱动电路100中,主字线信号mwlb的信号线通过由第一晶体管q1和第二晶体管q2构成的反相器连接对应的子字线wl,第一晶体管q1的源极连接子字线选择信号fxt,第二晶体管q2的源极连接字线关闭电压vkk。同时,子字线wl通过第三晶体管q3接地,第三晶体管q3的栅极连接辅助子字线选择信号fxb,子字线选择信号fxt与辅助子字线选择信号fxb的相位相反,均用于使能当前子字线wl对应的字线驱动电路。pg高阻是指第二晶体管q2和第三晶体管q3的栅极部分存在高阻。

37.在fxt信号为高电平、fxb信号为低电平时,第一晶体管q1和第二晶体管q2构成能够正常工作的反相器,对主字线信号mwlb进行反相,并传输到子字线wl上。在fxt信号为低电平、fxb信号为高电平时,第一晶体管q1和第二晶体管q2无法构成反相器,主字线信号mwlb无法传输到子字线wl上来,同时,第三晶体管q3开启,子字线wl连接字线关闭电压vkk,子字线wl处于稳定的关闭状态。

38.当第二晶体管q2的栅极存在高阻时,如果fxt信号为高电平,子字线wl处于正常工作状态,需要接收主字线信号mwlb的反相信号。如果主字线信号mwlb为高电平(逻辑“1”),第一晶体管q1应该关闭,第二晶体管q2应该开启,从而子字线wl上的电压应为字线关闭电压vkk,即逻辑“0”,但是此时第二晶体管q2的栅极存在高阻,第二晶体管q2无法及时导通,从而第一晶体管q1和第二晶体管q2均处于关闭状态,子字线wl处于浮空状态(floating)。此时fxb信号为低电平,第三晶体管q3关闭。

39.当第三晶体管q3的栅极存在高阻时,如果fxt信号为低电平,由第一晶体管q1和第二晶体管q2构成的反相器不工作,需要设置fxb信号为高电平,以开启第三晶体管q3,将子字线wl设置为字线关闭电压vkk,即逻辑“0”,以避免子字线wl出现浮空状态。但是,如果第

三晶体管q3的栅极存在高阻,则第三晶体管q3无法开启,子字线wl处于浮空状态(floating)。

40.由此可知,字线驱动电路100的pg高阻问题会导致子字线wl在被使能和/或被禁用状态下处于浮空状态(floating)。

41.为了解决pg高阻的检测问题,发明人进行了以下分析:

42.设字线驱动电路100存在pg高阻问题,即第二晶体管q2和/或第三晶体管q3的栅极部分存在高阻或断路。

43.当子字线wl被选择(子字线wl被设置为高电平,即fxt或vpp)时,通过mwlb输出低电平以控制第一晶体管q1导通、第二晶体管q2关闭,此时,由于第二晶体管q2和/或第三晶体管q3的栅极部分存在高阻或断路,第二晶体管q2、第三晶体管q3不导通或缓慢关闭,字线wl维持高电压fxt或者电位缓慢下降,或处于浮空状态。

44.当需要停止子字线wl的工作(子字线wl被设置为低电平,即字线关闭电压vkk)时,通过mwlb输出高电平以控制第一晶体管q1关闭、第二晶体管q2导通,此时,由于第二晶体管q2和/或第三晶体管q3的栅极部分存在高阻或断路,第二晶体管q2、第三晶体管q3无法导通或缓慢导通,导致字线wl无法或者缓慢到达电压vkk,或处于浮空状态。

45.基于上述分析,发明人提出本公开的字线驱动电路故障检测方法。

46.为了方便说明,本公开以下内容将子字线统称为字线。

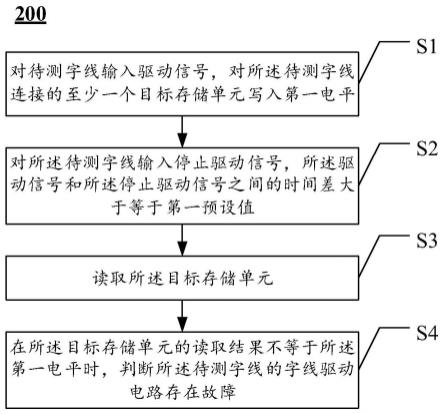

47.图2是本公开示例性实施例中字线驱动电路故障检测方法的流程图。

48.参考图2,字线驱动电路故障检测方法200可以包括:

49.步骤s1,对待测字线输入驱动信号,对所述待测字线连接的至少一个目标存储单元写入第一电平;

50.步骤s2,对所述待测字线输入停止驱动信号,所述驱动信号和所述停止驱动信号之间的时间差大于等于第一预设值;

51.步骤s3,读取所述目标存储单元;

52.步骤s4,在所述目标存储单元的读取结果不等于所述第一电平时,判断所述待测字线的字线驱动电路存在故障。

53.本公开实施例通过在增加对每条字线的操作使能时间后关闭对应字线,能够在对多条字线进行顺次写入操作时,增加每条字线在操作后被设置为关闭状态的时间,进而增加存在关闭功能故障(字线驱动电路存在故障)的字线连接的存储单元的漏电时间,最后通过检查各存储单元的状态准确地识别出字线驱动电路存在故障的字线,相比现有技术,具有更高的检测效率和检测准确率。

54.下面,对字线驱动电路故障检测方法100的各步骤进行详细说明。

55.在步骤s1,对待测字线输入驱动信号,对所述待测字线连接的至少一个目标存储单元写入第一电平。

56.图3是目标存储单元的读写电路示意图。

57.参考图3,目标存储单元31包括存储晶体管m1和电容c,存储晶体管m1例如可以为n型晶体管,存储晶体管m1的源极连接电容c,漏极连接位线bl,栅极连接待测字线wl。位线bl上顺次设置有列选择单元32、均衡单元33和感应放大器34。

58.列选择单元32包括第二开关元件m2,第二开关元件m2为n型晶体管,源极连接局部

信号线lio(local input/output),漏极连接位线bl,栅极连接列选择信号线ys(y select)。

59.均衡单元33包括第三开关元件m3、第四开关元件m4和第五开关元件m5,第三开关元件m3、第四开关元件m4和第五开关元件m5均为n型晶体管,第三开关元件m3、第四开关元件m4和第五开关元件m5的栅极均连接位线均衡控制信号veq(voltage of equalizer)。其中,第三开关元件m3的源极和第四开关元件m4的漏极均连接位线均衡电压vblp(voltage of bit line precharge),第三开关元件m3的漏极连接位线bl,第四开关元件m4的源极连接互补位线/bl。

60.感应放大器(sense amplifier,sa)34是一种差分放大器,两个输入端分别连接位线bl和互补位线/bl,用于将位线bl和互补位线/bl的电压差放大。感应放大器34包括第六开关元件m6、第七开关元件m7、第八开关元件m8、第九开关元件m9。其中,第六开关元件m6、第七开关元件m7均为n型晶体管,第八开关元件m8、第九开关元件m9均为p型晶体管。第六开关元件m6的一端通过第一节点n1连接位线bl,另一端连接低电位节点ncs,低电位节点ncs连接下拉电压vss,第六开关元件m6的控制端连接互补位线/bl。第七开关元件m7的一端通过第二节点n2连接互补位线/bl,另一端连接低电位节点ncs,第七开关元件m7的控制端连接位线bl。第八开关元件m8的一端通过第一节点n1连接位线bl,另一端连接高电位节点pcs,高电位节点pcs连接上拉电压vary,第八开关元件m8的控制端连接互补位线/bl。第九开关元件m9的一端通过第二节点n2连接互补位线/bl,另一端连接高电位节点pcs,第九开关元件m9的控制端连接位线bl。

61.图4是图3所示电路的写入过程示意图。

62.参考图4,在写入之前,位线均衡控制信号veq控制均衡单元33中的三个开关元件导通,位线bl和互补位线/bl均等于位线均衡电压vblp。字线驱动电路100控制待测字线wl为低电平。

63.激活信号act在第一时刻t1到达后,位线均衡控制信号veq关闭(veq off),允许位线bl和互补位线/bl之间存在电压差。字线驱动电路100在第一时刻t1对待测字线wl输入高电平vpp(wl on),使待测字线wl在第二时刻t2达到高电平vpp,以控制存储单元31中的存储晶体管m1开启。结合图1,字线驱动电路100通过设置控制信号mwlb为低电平以控制第一晶体管q1导通、第二晶体管q2关闭。无论此时字线驱动电路100中是否存在pg高阻现象,p型的第一晶体管q1均导通,待测字线wl均会被成功设置为高电平vpp。

64.在第一时刻t1和第二时刻t2之间,待测字线wl的电压大于存储晶体管m1的开启电压,存储晶体管m1导通。假设此时存储电容c中存储“0”,存储电容c的上极板电压等于零。由于位线bl的电压vblp大于零,位线bl通过导通的存储晶体管m1对存储电容c充电,存储电容c的电位上升,位线bl的电位下降。当位线bl的电位下降到与互补位线/bl之间存在的电压差大于感应放大器34的感应阈值电压时,感应放大器34在第三时刻t3开始翻转,在第四时刻t4将位线bl和互补位线/bl的电压分别拉到其下拉电压vss和上拉电压vary。

65.在第五时刻t5之前,均可以通过读写转换电路将局部信号线lio设置为待写入的第一电平,以在第五时刻t5,通过控制列选择信号线ys输出高电平脉冲,控制第二开关元件m2开启,以将位线bl设置为第一电平。假设第一电平为高电平(逻辑电平1),第二电平为低电平(逻辑电平0),则第五时刻之后,由于位线bl的电平发生变化,感应放大器34发生翻转,

位线bl被设置为感应放大器34的上拉电压vary,互补位线/bl被设置为感应放大器34的下拉电压vss。

66.此时待测字线wl为高电平,位线bl的电压通过导通的存储晶体管m1存入存储电容c,完成对目标存储单元31写入第一电压的过程。

67.当第一电平为低电平时,对应的写入过程可根据上述原理推出,于此不再赘述。

68.在步骤s2,对所述待测字线输入停止驱动信号,所述驱动信号和所述停止驱动信号之间的时间差大于等于第一预设值。

69.继续参考图3。在第六时刻t6,对待测字线wl输入停止驱动信号即控制待测字线wl为低电平(wl off),以控制存储晶体管m1关闭。在第七时刻t7,位线均衡控制信号veq被设置为高电平(eq on),位线均衡控制信号veq控制均衡单元33中的三个开关元件导通,位线bl和互补位线/bl均等于位线均衡电压vblp。

70.结合图1,在第六时刻t6,字线驱动电路100通过设置控制信号mwlb为高电平以控制第一晶体管q1关闭、第二晶体管q2导通。

71.当待测字线wl连接的字线驱动电路100不存在pg高阻问题时,第一晶体管q1能够在第七时刻t7之前关闭,第二晶体管q2能够在第七时刻t7之前导通,使待测字线wl在第七时刻t7之前达到低电平,控制存储晶体管m1关闭。

72.当待测字线wl连接的字线驱动电路100存在pg高阻问题时,第一晶体管q1能够在第七时刻t7之前关闭,但是第二晶体管q2不能够在第七时刻t7之前导通。由此,待测字线wl要在第八时刻t8才能达到低电平,此前均处于浮空状态(wl floating)。

73.在第六时刻t6和第八时刻t8之间(可以称为预充电阶段precharge),由于待测字线wl仍维持一个较高的电位,存储晶体管m1维持开启状态,存储电容c中的高电平为感应放大器34的上拉电压vary,大于位线均衡电压vblp,存储电容c对位线bl漏电,存储电容c中的电位缓慢下降。

74.在第七时刻t7之后,开始对下一条字线进行写入操作(下一条字线进入wl on状态),直至完成对整个阵列的字线的操作。也就是说,在第六时刻t6和第八时刻t8之间,存储电容c持续漏电时,正在进行对其他字线的操作。

75.因此,本公开实施例设置对字线输入驱动信号即控制字线为高电平(wl on)的第一时刻t1和对字线输入停止驱动信号即控制字线为低电平(wl off)的第六时刻t6之间的时间差(tras)大于第一预设值,以为字线驱动电路存在故障的字线连接的存储单元提供较长的漏电时间,使其充分漏电,有助于后续通过读取进行检测,这种策略可以成为长字线操作时间,即long tras。

76.在步骤s3,读取所述目标存储单元。

77.可以在按地址对全部目标存储单元完成写入操作后,按地址读取目标存储单元。即,在完成对阵列对应的全部字线顺次进行写入操作后,可以从头开始对全部字线进行读取操作。

78.其中,对图2中的待测字线wl进行读取的过程可以简述为:

79.响应激活信号act,对位线均衡控制信号veq输入高电平脉冲,以通过位线均衡控制信号veq控制均衡单元33中的三个开关元件导通,使位线bl和互补位线/bl上的电压均等于位线均衡电压vblp。位线均衡控制信号veq的高电平脉冲结束后,均衡单元33中的三个开

关元件关闭,允许位线bl和互补位线/bl出现电压差。接下来,控制待测字线wl为高电平(wl on),开启存储晶体管m1,位线bl(此时电压等于vblp)与存储电容c的上极板出现电压差。

80.如果存储电容c的上极板电压较低(低于vblp),则位线bl对存储电容c充电,位线bl上电位下降,当电位下降幅度超过感应放大器34的感应阈值电压时,感应放大器将位线bl下拉到感应放大器34的下拉电压vss,将互补位线/bl上拉到感应放大器34的上拉电压vary。接下来发送ys脉冲,将位线bl的电平读取到局部信号线lio上。

81.如果存储电容c的上极板电压较高(高于vblp),则存储电容c对位线bl充电,位线bl上电位上升,当电位上升幅度超过感应放大器34的感应阈值电压时,感应放大器将位线bl上拉到感应放大器34的上拉电压vary,将互补位线/bl下拉到感应放大器34的下拉电压vss。接下来发送ys脉冲,将位线bl的电平读取到局部信号线lio上。

82.读取结束后,控制待测字线wl关闭(wl off),对位线均衡控制信号veq输入高电平脉冲,以通过位线均衡控制信号veq控制均衡单元33中的三个开关元件导通,使位线bl和互补位线/bl上的电压均等于位线均衡电压vblp。

83.在步骤s4,在所述目标存储单元的读取结果不等于所述第一电平时,判断所述待测字线的字线驱动电路存在故障。

84.结合图4所示实施例,当对每条字线均设置长字线操作时间时,待测字线在结束一个阵列的字线操作被读取前的时长,达到或超过第六时间点t6到第八时间点t8之间的时长,待测字线连接的目标存储单元31的存储电容c具有充分的漏电时间,在第八时间点t8(即待测字线wl电压为零)之前,存储电容c都可能充分漏电。如此,就能够在读取阶段对在位线bl上制造充分的电压差,使该电压差超过感应放大器34的感应阈值电压,以使感应放大器34将位线bl设置为下拉电压vss,被读取到局部信号线lio上,识别为目标存储单元的读取结果等于第二电平(低电平)。

85.同理,如果字线驱动电路100不存在故障,待测字线wl在第七时间点t7之前达到低电平,则存储电容c不具有充分的漏电时间,存储电容c的上极板保持为第一电平,从而读取结果为第一电平。

86.因此,上述实施例可以通过读取结果是否为第一电平,来判断字线驱动电路100是否存在故障,该故障例如为pg高阻故障。

87.在一些实施例中,除了设置长字线操作时间,还可以在对待测字线输入停止驱动信号之后,将位线均衡电压设置为第二电平,并对目标存储单元的读写控制电路输入位线均衡控制信号。

88.通过将位线均衡电压vblp设置为第二电平,可以加快存储电容c的漏电速度,进而提高测试效率。

89.图5是本公开一个实施例中图3所示电路的写入过程示意图。

90.参考图5,在另一个实施例中,在第六时间点t6之后,除了对待测字线wl输入停止驱动信号(wl off),还可以将位线均衡电压vblp设置为第二电平,以在故障字线连接的存储晶体管尚未完全关闭时,对存储电容c写入第二电平。

91.在图5所示实施例中,设第一电平为高电平、第二电平为低电平,待测字线wl存在pg高阻故障,在第七时间点t7之后,位线bl被设置为vss。则在第七时间点t7到第八时间点t8之间,待测字线wl有一段时间维持在一个较高的电平,存储晶体管m1未完全关闭,存储电

容c的上极板通过未完全关闭的存储晶体管m1对位线bl充电,存储电容c的电位迅速下降,极有可能在待测字线wl上的电压尚未降低到存储晶体管m1的导通阈值电压时,存储电容c的上极板电压已经等于vss了。由此,即使在第八时间点t8之前对目标存储单元31进行读取,也能够读到第二电平。相比图3所示实施例,可以设置相对较短的字线操作时间(第一时间点t1和第六时间点t6之间的时间差),提高测试效率。

92.以上均以第一电平为高电平、第二电平为低电平为例,在另一个实施例中,第一电平可以为低电平、第二电平可以为高电平。在本公开的一些实施例中,高电平等于电源电压(例如vary),低电平等于零电平(例如vss);在另一些实施例中,可以配合dft使用,例如高电平等于子字线选择信号fxt,低电平等于字线关闭电压vkk,提高故障的侦测能力。

93.上述实施例是以对一个目标存储单元进行操作、测试目标存储单元连接的待测字线为例对本公开实施例的原理进行说明。在实际应用中,通常对存储阵列进行批量操作,以测试存储阵列中的多个或全部字线。

94.图6是本公开一个实施例中步骤s1的子流程图。

95.参考图6,在本公开的一个实施例中,步骤s1可以包括:

96.步骤s61,同时对目标页的多个位线写入所述第一电平;

97.步骤s62,顺次对所述目标页的多个待测字线输入所述驱动信号。

98.其中,目标页是指当前正在操作的页。每个页被操作时均可以被称为目标页。

99.图6所示实施例的写入方法,是一次对一页的存储单元实现写入,可以称为y-page写入方法。

100.图7是本公开另一个实施例中步骤s1的子流程图。

101.参考图7,在本公开的另一个实施例中,步骤s1可以包括:

102.步骤s71,对一条所述待测字线连接的预设数量个目标存储单元写入所述第一电平;

103.步骤s72,顺次对多条待测字线重复以上过程。

104.在一个实施例中,预设数量等于所述待测字线对应的存储阵列的一个突发长度(burst length,bl),此时称为x-fast写入方法。

105.在另一个实施例中,预设数量等于所述待测字线对应的全部存储单元的数量,此时称为y-fast写入方法。

106.除了上述写入方法,还可以对多条待测字线对应的连接相同位线的目标存储单元顺次写入第一电平,即x-march写入方法。

107.读取方法可以与写入方法对应,例如写入方法是x-fast写入方法时,读取方法是x-fast读取方法。读取方法也可以与写入方法不同,例如写入方法是x-fast写入方法时,读取方法是y-fast读取方法。

108.通过批量顺次写入多个存储单元、批量顺次读取多个存储单元,可以通过对存储阵列进行完整的、系统的测试,检测多条或全部字线是否存在故障,提高存储器产品的可靠性。

109.在上述测试方法中,多个目标存储单元可以连续,也可以不连续。

110.图8a~图8e是本公开实施例中目标存储单元的分布示意图。图8a~图8e以存储的第一电平是高电平(即逻辑电平“1”)为例标识目标存储单元81。

111.参考图8a,在一个实施例中,目标存储单元81为存储阵列中的全部存储单元。

112.参考图8b,在本公开的一种示例性实施例中,目标存储单元81可以分布在多个第一目标行810,多个第一目标行810之间间隔设置有第二目标行820。其中,“行”指位线bl的延伸方向。第一目标行810可以与第二目标行820间隔设置,连续的第一目标行810的数量可以与连续的第二目标行820的数量相等,也可以不等。

113.参考图8c,在本公开的一种示例性实施例中,待测字线之间间隔设置有空闲字线。

114.在图8d所示实施例中,目标存储单元81呈棋盘状排列。

115.在图8e所示实施例中,目标存储单元81呈对角线状排列。

116.在本公开的其他实施例中,目标存储单元81在存储阵列中的排列方式还可以有多种,本公开对此不作特殊限制。

117.通过设置不同的测试图谱(pattern),可以减小目标存储单元的位置设置对测试结果的影响,提高测试准确性。

118.此外,在本公开的一个实施例中,可以按照待测字线的序号从小到大的方式进行测试(写入然后读取)之后,再按照待测字线的序号从大到小进行测试,即采用forward(序号由小到大)和backward(序号由大到小)的施压(stress)方式对存储阵列进行两次测试,可以控制字线测试的公平性,以降低待测字线的序号对测试结果的影响,有效降低测试时的误宰率,提高测试准确性。

119.本公开实施例利用y-page写入方法,执行long tras写入方式,配合在预充电阶段(precharge)将位线均衡电压vblp设置为vss的测试模式,使因字线驱动单元pg高阻而处于字线浮空(wl floating)的存储单元进行充分漏电,叠加存储单元在预充电阶段(precharge)时回存数据“1”不足或者回存反向“0”数据,使得读取存储单元时,感应放大器感应“1”错误,使得具有字线驱动单元pg高阻缺陷的问题芯片会被有效的检测出来。

120.使用该检测方法应用于量产程式,可以提升字线驱动单元的缺陷检测能力,有助于提升产品可靠性和良率。

121.综上所述,通过应用多种写入、读取方法,对多种分布的目标存储单元进行测试,并改变测试顺序进行多次测试,可以通过本公开实施例提供的测试方法检测到存在故障的字线驱动电路,有效提高存储器产品的可靠性。

122.应当注意,尽管在上文详细描述中提及了用于动作执行的设备的若干模块或者单元,但是这种划分并非强制性的。实际上,根据本公开的实施方式,上文描述的两个或更多模块或者单元的特征和功能可以在一个模块或者单元中具体化。反之,上文描述的一个模块或者单元的特征和功能可以进一步划分为由多个模块或者单元来具体化。

123.在本公开的示例性实施例中,还提供了一种能够实现上述方法的电子设备。

124.所属技术领域的技术人员能够理解,本发明的各个方面可以实现为系统、方法或程序产品。因此,本发明的各个方面可以具体实现为以下形式,即:完全的硬件实施方式、完全的软件实施方式(包括固件、微代码等),或硬件和软件方面结合的实施方式,这里可以统称为“电路”、“模块”或“系统”。

125.下面参照图9来描述根据本发明的这种实施方式的电子设备900。图9显示的电子设备900仅仅是一个示例,不应对本发明实施例的功能和使用范围带来任何限制。

126.如图9所示,电子设备900以通用计算设备的形式表现。电子设备900的组件可以包

括但不限于:上述至少一个处理单元910、上述至少一个存储单元920、连接不同系统组件(包括存储单元920和处理单元910)的总线930。

127.其中,所述存储单元存储有程序代码,所述程序代码可以被所述处理单元910执行,使得所述处理单元910执行本说明书上述“示例性方法”部分中描述的根据本发明各种示例性实施方式的步骤。例如,所述处理单元910可以执行如本公开实施例所示的方法。

128.存储单元920可以包括易失性存储单元形式的可读介质,例如随机存取存储单元(ram)9201和/或高速缓存存储单元9202,还可以进一步包括只读存储单元(rom)9203。

129.存储单元920还可以包括具有一组(至少一个)程序模块9205的程序/实用工具9204,这样的程序模块9205包括但不限于:操作系统、一个或者多个应用程序、其它程序模块以及程序数据,这些示例中的每一个或某种组合中可能包括网络环境的实现。

130.总线930可以为表示几类总线结构中的一种或多种,包括存储单元总线或者存储单元控制器、外围总线、图形加速端口、处理单元或者使用多种总线结构中的任意总线结构的局域总线。

131.电子设备900也可以与一个或多个外部设备1000(例如键盘、指向设备、蓝牙设备等)通信,还可与一个或者多个使得用户能与该电子设备900交互的设备通信,和/或与使得该电子设备900能与一个或多个其它计算设备进行通信的任何设备(例如路由器、调制解调器等等)通信。这种通信可以通过输入/输出(i/o)接口950进行。并且,电子设备900还可以通过网络适配器960与一个或者多个网络(例如局域网(lan),广域网(wan)和/或公共网络,例如因特网)通信。如图所示,网络适配器960通过总线930与电子设备900的其它模块通信。应当明白,尽管图中未示出,可以结合电子设备900使用其它硬件和/或软件模块,包括但不限于:微代码、设备驱动器、冗余处理单元、外部磁盘驱动阵列、raid系统、磁带驱动器以及数据备份存储系统等。

132.通过以上的实施方式的描述,本领域的技术人员易于理解,这里描述的示例实施方式可以通过软件实现,也可以通过软件结合必要的硬件的方式来实现。因此,根据本公开实施方式的技术方案可以以软件产品的形式体现出来,该软件产品可以存储在一个非易失性存储介质(可以是cd-rom,u盘,移动硬盘等)中或网络上,包括若干指令以使得一台计算设备(可以是个人计算机、服务器、终端装置、或者网络设备等)执行根据本公开实施方式的方法。

133.在本公开的示例性实施例中,还提供了一种计算机可读存储介质,其上存储有能够实现本说明书上述方法的程序产品。在一些可能的实施方式中,本发明的各个方面还可以实现为一种程序产品的形式,其包括程序代码,当所述程序产品在终端设备上运行时,所述程序代码用于使所述终端设备执行本说明书上述“示例性方法”部分中描述的根据本发明各种示例性实施方式的步骤。

134.根据本发明的实施方式的用于实现上述方法的程序产品可以采用便携式紧凑盘只读存储器(cd-rom)并包括程序代码,并可以在终端设备,例如个人电脑上运行。然而,本发明的程序产品不限于此,在本文件中,可读存储介质可以是任何包含或存储程序的有形介质,该程序可以被指令执行系统、装置或者器件使用或者与其结合使用。

135.所述程序产品可以采用一个或多个可读介质的任意组合。可读介质可以是可读信号介质或者可读存储介质。可读存储介质例如可以为但不限于电、磁、光、电磁、红外线、或

半导体的系统、装置或器件,或者任意以上的组合。可读存储介质的更具体的例子(非穷举的列表)包括:具有一个或多个导线的电连接、便携式盘、硬盘、随机存取存储器(ram)、只读存储器(rom)、可擦式可编程只读存储器(eprom或闪存)、光纤、便携式紧凑盘只读存储器(cd-rom)、光存储器件、磁存储器件、或者上述的任意合适的组合。

136.计算机可读信号介质可以包括在基带中或者作为载波一部分传播的数据信号,其中承载了可读程序代码。这种传播的数据信号可以采用多种形式,包括但不限于电磁信号、光信号或上述的任意合适的组合。可读信号介质还可以是可读存储介质以外的任何可读介质,该可读介质可以发送、传播或者传输用于由指令执行系统、装置或者器件使用或者与其结合使用的程序。

137.可读介质上包含的程序代码可以用任何适当的介质传输,包括但不限于无线、有线、光缆、rf等等,或者上述的任意合适的组合。

138.可以以一种或多种程序设计语言的任意组合来编写用于执行本发明操作的程序代码,所述程序设计语言包括面向对象的程序设计语言—诸如java、c 等,还包括常规的过程式程序设计语言—诸如“c”语言或类似的程序设计语言。程序代码可以完全地在用户计算设备上执行、部分地在用户设备上执行、作为一个独立的软件包执行、部分在用户计算设备上部分在远程计算设备上执行、或者完全在远程计算设备或服务器上执行。在涉及远程计算设备的情形中,远程计算设备可以通过任意种类的网络,包括局域网(lan)或广域网(wan),连接到用户计算设备,或者,可以连接到外部计算设备(例如利用因特网服务提供商来通过因特网连接)。

139.此外,上述附图仅是根据本发明示例性实施例的方法所包括的处理的示意性说明,而不是限制目的。易于理解,上述附图所示的处理并不表明或限制这些处理的时间顺序。另外,也易于理解,这些处理可以是例如在多个模块中同步或异步执行的。

140.本领域技术人员在考虑说明书及实践这里公开的发明后,将容易想到本公开的其它实施方案。本技术旨在涵盖本公开的任何变型、用途或者适应性变化,这些变型、用途或者适应性变化遵循本公开的一般性原理并包括本公开未公开的本技术领域中的公知常识或惯用技术手段。说明书和实施例仅被视为示例性的,本公开的真正范围和构思由权利要求指出。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。