1.本发明涉及显示技术领域,尤其涉及一种阵列基板及其制备方法、显示面板。

背景技术:

2.面内转换(in-plane switching,ips)型阵列基板利用与基板面大致平行的电场来驱动液晶分子沿基板面内转动,由于ips型阵列基板将像素电极和公共电极设计为一次成膜的结构,为保证不同电极之间相互绝缘,电极与电极之间需要设置线距,但这个线距对透过率没有帮助,浪费了开口空间,导致透过率下降。

3.故,有必要改善这一缺陷。

技术实现要素:

4.本发明实施例提供一种阵列基板,用于解决现有技术的阵列基板的透过率低的技术问题。

5.本发明实施例提供一种阵列基板,包括衬底层、绝缘层、多个第一电极以及多个第二电极;所述绝缘层位于所述衬底层上,所述绝缘层远离所述衬底层的一侧设置有多个凹槽;多个所述第一电极位于多个所述凹槽内;多个所述第二电极位于多个所述凹槽外的所述绝缘层远离所述衬底层的一侧表面,多个所述第二电极与多个所述第一电极绝缘设置。

6.在本发明实施例提供的阵列基板中,多个所述第一电极和多个所述第二电极由同一道金属沉积工艺形成。

7.在本发明实施例提供的阵列基板中,所述第一电极包括一个第一主干电极和多个平行设置的第一分支电极,多个所述第一分支电极与所述第一主干电极电连接;所述第二电极包括一个第二主干电极和多个平行设置的第二分支电极,多个所述第二分支电极与所述第二主干电极电连接;其中,所述第一分支电极在所述衬底层上的正投影与相邻的所述第二分支电极在所述衬底层上的正投影之间的间距大于或等于0且小于或等于0.5微米。

8.在本发明实施例提供的阵列基板中,位于中间区域的所述第一分支电极在所述衬底层上的正投影与所述第二主干电极在所述衬底层上的正投影之间的间距大于位于边缘区域的所述第一分支电极在所述衬底层上的正投影与所述第二主干电极在所述衬底层上的正投影之间的间距;和/或位于中间区域的所述第二分支电极在所述衬底层上的正投影与所述第一主干电极在所述衬底层上的正投影之间的间距大于位于边缘区域的所述第二分支电极在所述衬底层上的正投影与所述第一主干电极在所述衬底层上的正投影之间的间距。

9.在本发明实施例提供的阵列基板中,在垂直于所述衬底层至所述绝缘层的方向上,位于边缘区域的所述第一分支电极的宽度大于位于中间区域的所述第一分支电极的宽度;和/或位于边缘区域的所述第二分支电极的宽度大于位于中间区域的所述第二分支电极的宽度。

10.在本发明实施例提供的阵列基板中,在所述衬底层至所述绝缘层的方向上,位于

中间区域的所述第一分支电极与相邻的所述第二分支电极之间的间距大于位于边缘区域的所述第一分支电极与相邻的所述第二分支电极之间的间距。

11.在本发明实施例提供的阵列基板中,在所述衬底层至所述绝缘层的方向上,所述第一电极与相邻的所述第二电极之间的间距为第一值,所述第一电极的膜层厚度为第二值,所述第一值与所述第二值的比值大于10。

12.在本发明实施例提供的阵列基板中,所述凹槽的侧壁与所述凹槽的底面之间形成的夹角大于0且小于或等于90度。

13.本发明实施例提供一种阵列基板的制备方法,包括:在衬底层上制备绝缘层;在所述绝缘层远离所述衬底层的一侧制备多个凹槽;在所述绝缘层上制备金属层,所述金属层包括相互绝缘的多个第一电极和多个第二电极,其中,多个所述第一电极位于多个所述凹槽内,多个所述第二电极位于多个所述凹槽外的所述绝缘层远离所述衬底层的一侧表面。

14.本发明实施例还提供一种显示面板,包括彩膜基板和上述的阵列基板,所述彩膜基板与所述阵列基板相对设置。

15.有益效果:本发明实施例提供的一种阵列基板,包括衬底层、绝缘层、多个第一电极以及多个第二电极;绝缘层位于衬底层上,绝缘层远离衬底层的一侧设置有多个凹槽;多个第一电极位于多个凹槽内;多个第二电极位于多个凹槽外的绝缘层远离衬底层的一侧表面,多个第二电极与多个第一电极绝缘设置;本发明通过在多个凹槽内形成多个第一电极,在多个凹槽外的绝缘层远离衬底层的一侧表面形成多个第二电极,位于凹槽内的第一电极与相邻的位于凹槽外的第二电极在垂直于阵列基板所在平面的方向上具有一定的间距,从而在垂直于阵列基板所在平面的方向上实现第一电极与第二电极分离,从而可以减小甚至取消第一电极在衬底层上的正投影与相邻的第二电极在衬底层上的正投影之间的线距,从而可以大大提高透过率。

附图说明

16.图1是现有技术的像素电极和公共电极的俯视图。

17.图2是沿图1中a-a’方向的阵列基板的剖面图。

18.图3是现有技术的另一像素电极和另一公共电极的俯视图。

19.图4是沿图3中b-b’方向的另一阵列基板的剖面图。

20.图5是本发明实施例提供的第一电极和第二电极的俯视图。

21.图6是本发明实施例提供的沿图5中c-c’方向的阵列基板的剖面图。

22.图7是本发明实施例提供的另一第一电极和另一第二电极的俯视图。

23.图8是本发明实施例提供的又一第一电极和又一第二电极的俯视图。

24.图9是本发明实施例提供的另一阵列基板的剖面图。

25.图10是本发明实施例提供的又一阵列基板的剖面图。

26.图11是本发明实施例提供的阵列基板的制备方法流程图。

具体实施方式

27.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述。在附图中,为了清晰及便于理解和描述,附图中绘示的组件的尺寸和厚度并未按

照比例。

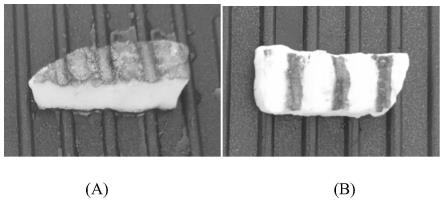

28.如图1和图2所示,分别为现有技术的像素电极和公共电极的俯视图以及沿图1中a-a’方向的阵列基板的剖面图,阵列基板包括衬底层11、位于衬底层11上的绝缘层12、位于绝缘层12上的像素电极13和公共电极14,从图1中可以很明显的看出,像素电极13和公共电极14之间存在线距a,这个线距a的区域没有设置电极,不能发出电场,因此这部分空间没有利用上,造成阵列基板的整体透过率下降,本发明实施例可以解决上述缺陷。

29.如图5和图6所示,分别为本发明实施例提供的第一电极和第二电极的俯视图以及沿图5中c-c’方向的阵列基板的剖面图,所述阵列基板包括衬底层11、绝缘层12、多个第一电极21以及多个第二电极22;所述绝缘层12位于所述衬底层11上,所述绝缘层12远离所述衬底层11的一侧设置有多个凹槽121;多个所述第一电极21位于多个所述凹槽121内;多个所述第二电极22位于多个所述凹槽121外的所述绝缘层12远离所述衬底层11的一侧表面,多个所述第二电极22与多个所述第一电极21绝缘设置。

30.可以理解的是,本发明实施例通过在绝缘层12上形成多个凹槽121,使得绝缘层12在垂直于阵列基板所在平面的方向(即垂直方向)上具有两种厚度,通过在多个凹槽121内形成多个第一电极21,在多个凹槽121外的绝缘层12远离衬底层11的一侧表面形成多个第二电极22,位于凹槽121内的第一电极21与相邻的位于凹槽121外的第二电极22在垂直方向上具有一定的间距,从而在垂直方向上实现第一电极21与第二电极22分离,从而可以减小甚至取消第一电极21在衬底层11上的正投影与相邻的第二电极22在衬底层11上的正投影之间(即水平方向)的线距,从而可以大大提高透过率。

31.需要说明的是,绝缘层12在垂直方向上具有两种厚度是通过半色调掩模(half tone mask,htm)工艺实现的。在一种实施例中,所述绝缘层12的材料为氮化硅。

32.需要说明的是,第一电极21和第二电极22分别为像素电极和公共电极中互不相同的一者,即第一电极21为像素电极时,第二电极22为公共电极;第一电极21为公共电极时,第二电极22为像素电极。

33.在一种实施例中,多个所述第一电极21和多个所述第二电极22由同一道金属沉积工艺形成。

34.可以理解的是,如图3和图4所示,分别为现有技术的另一像素电极和另一公共电极的俯视图以及沿图3中b-b’方向的另一阵列基板的剖面图,图3和图4的阵列基板通过将像素电极13和公共电极14异层设置,从而取消了图1和图2中的线距a,从而提升了透过率,但图3和图4中的像素电极13和公共电极14需要分开制备,因此,比图1和图2中的像素电极13和公共电极14多一道光罩制程,造成成本和复杂度高。本实施例通过将多个第一电极21和多个第二电极22采用同一道金属沉积工艺形成,具体的,当在绝缘层12上沉积金属层时,部分金属层落入多个凹槽121内形成多个第一电极21,另一部分金属层20落在多个凹槽121外的绝缘层12远离衬底层11的一侧表面形成多个第二电极22,因此,不用额外增加一道光罩制程,降低了制作难度,节约了生产成本。

35.继续参阅图5,在一种实施例中,所述第一电极21包括一个第一主干电极211和多个平行设置的第一分支电极212,多个所述第一分支电极212与所述第一主干电极211电连接;所述第二电极22包括一个第二主干电极221和多个平行设置的第二分支电极222,多个所述第二分支电极222与所述第二主干电极221电连接;其中,所述第一分支电极212在所述

衬底层11(如图6)上的正投影与相邻的所述第二分支电极222在所述衬底层11上的正投影之间的间距大于或等于0且小于或等于0.5微米。可以理解的是,本实施例通过将第一电极21和第二电极22设置为相互啮合,减小了第一电极21和第二电极22之间的距离,增大了第一电极21和第二电极22之间的电场强度。

36.请参阅图6,在一种实施例中,在所述衬底层11至所述绝缘层12的方向上,所述第一电极21与相邻的所述第二电极22之间的间距为第一值b,所述第一电极21的膜层厚度为第二值c,所述第一值b与所述第二值c的比值b/c大于10。可以理解的是,b/c越大,在所述衬底层11至所述绝缘层12的方向上,第一电极21与第二电极22相距越远,第一电极21和第二电极22之间越容易断开,因此,b/c越大越好。本实施例通过将b/c设置为大于10,可以在不增加光罩制程的前提下,使第一电极21和第二电极22之间断开。

37.在一种实施例中,所述第一值b大于或等于4000埃且小于或等于20000埃,所述第二值c大于或等于300埃且小于或等于1000埃。

38.接下来,请参阅图7,为本发明实施例提供的另一第一电极和另一第二电极的俯视图,在本实施例中,位于中间区域的所述第一分支电极212在所述衬底层11(如图6)上的正投影与所述第二主干电极221在所述衬底层11上的正投影之间的间距d大于位于边缘区域的所述第一分支电极212在所述衬底层11上的正投影与所述第二主干电极221在所述衬底层11上的正投影之间的间距e;和/或位于中间区域的所述第二分支电极222在所述衬底层11上的正投影与所述第一主干电极211在所述衬底层11上的正投影之间的间距f大于位于边缘区域的所述第二分支电极222在所述衬底层11上的正投影与所述第一主干电极211在所述衬底层11上的正投影之间的间距g。

39.可以理解的是,本实施例通过减小边缘区域的第一分支电极212在所述衬底层11上的正投影与第二主干电极221在所述衬底层11上的正投影之间的间距e,和/或边缘区域的第二分支电极222在所述衬底层11上的正投影与第一主干电极211在所述衬底层11上的正投影之间的间距g,从而增大边缘区域的电场强度,从而可以弥补子像素边缘的亮度不足,提高显示均一性。

40.需要说明的是,位于最边缘的第二分支电极222(即位于g远离f的一侧)在所述衬底层11上的正投影与第一主干电极211在所述衬底层11上的正投影之间的间距为0。

41.接下来,请参阅图8,为本发明实施例提供的又一第一电极和又一第二电极的俯视图,在本实施例中,在垂直于所述衬底层11(如图6)至所述绝缘层12(如图6)的方向上,位于边缘区域的所述第一分支电极212的宽度k大于位于中间区域的所述第一分支电极212的宽度m;和/或位于边缘区域的所述第二分支电极222的宽度h大于位于中间区域的所述第二分支电极222的宽度j。

42.可以理解的是,在垂直于所述衬底层11(如图6)至所述绝缘层12(如图6)的方向上,本实施例通过增大边缘区域的第一分支电极212的宽度k,和/或边缘区域的第二分支电极222的宽度h,从而增大边缘区域的电场强度,从而可以弥补子像素边缘的亮度不足,提高显示均一性。

43.接下来,请参阅图9,为本发明实施例提供的另一阵列基板的剖面图,在本实施例中,在所述衬底层11至所述绝缘层12的方向上,位于中间区域的所述第一分支电极212与相邻的所述第二分支电极222之间的间距n大于位于边缘区域的所述第一分支电极212与相邻

的所述第二分支电极222之间的间距p。

44.可以理解的是,在所述衬底层11至所述绝缘层12的方向上,本实施例通过减小边缘区域的第一分支电极212与相邻的第二分支电极222之间的间距p,从而增大边缘区域的电场强度,从而可以弥补子像素边缘的亮度不足,提高显示均一性。

45.需要说明的是,在所述衬底层11至所述绝缘层12的方向上,第一分支电极212与相邻的第二分支电极222之间的间距不同,是通过htm工艺将绝缘层12上的凹槽121的深度设置为不同而实现的。

46.接下来,请参阅图10,为本发明实施例提供的又一阵列基板的剖面图,在本实施例中,所述凹槽121的侧壁与所述凹槽121的底面之间形成的夹角r大于0且小于或等于90度。

47.可以理解的是,所述凹槽121是通过将绝缘层12采用htm工艺形成的,其中,所述凹槽121的侧壁与所述凹槽121的底面之间形成的夹角r越小越好,这样有利于实现在垂直于阵列基板所在平面的方向上,第一电极21与第二电极22断开。

48.接下来,请参阅图11,为本发明实施例提供的阵列基板的制备方法流程图,所述制备方法包括:

49.s1、在衬底层上制备绝缘层;

50.s2、在所述绝缘层远离所述衬底层的一侧制备多个凹槽;

51.s3、在所述绝缘层上制备金属层,所述金属层包括相互绝缘的多个第一电极和多个第二电极,其中,多个所述第一电极位于多个所述凹槽内,多个所述第二电极位于多个所述凹槽外的所述绝缘层远离所述衬底层的一侧表面。

52.可以理解的是,本实施例通过采用一道光罩制程在绝缘层上制备多个凹槽,当在绝缘层上沉积金属层时,部分金属层落入多个凹槽内形成多个第一电极,另一部分金属层落在多个凹槽外的绝缘层远离衬底层的一侧表面形成多个第二电极,位于凹槽内的第一电极与相邻的位于凹槽外的第二电极在垂直于阵列基板所在平面的方向分离,从而可以减小甚至取消第一电极在衬底层上的正投影与相邻的第二电极在衬底层上的正投影之间的线距,从而可以大大提高透过率,而且不用额外增加一道光罩制程,降低了制作难度,节约了生产成本。

53.本发明实施例还提供一种显示面板,包括彩膜基板和上述的阵列基板,所述彩膜基板与所述阵列基板相对设置,所述阵列基板的结构及制备方法请参阅图5至图11,此处不再赘述。

54.综上所述,本发明实施例提供的一种阵列基板,包括衬底层、绝缘层、多个第一电极以及多个第二电极;绝缘层位于衬底层上,绝缘层远离衬底层的一侧设置有多个凹槽;多个第一电极位于多个凹槽内;多个第二电极位于多个凹槽外的绝缘层远离衬底层的一侧表面,多个第二电极与多个第一电极绝缘设置;本发明通过在多个凹槽内形成多个第一电极,在多个凹槽外的绝缘层远离衬底层的一侧表面形成多个第二电极,位于凹槽内的第一电极与相邻的位于凹槽外的第二电极在垂直于阵列基板所在平面的方向上具有一定的间距,从而在垂直于阵列基板所在平面的方向上实现第一电极与第二电极分离,从而可以减小甚至取消第一电极在衬底层上的正投影与相邻的第二电极在衬底层上的正投影之间的线距,从而可以大大提高透过率,解决了现有技术的阵列基板的透过率低的技术问题。

55.以上对本发明实施例所提供的一种阵列基板及其制备方法、显示面板进行了详细

介绍。应理解,本文所述的示例性实施方式应仅被认为是描述性的,用于帮助理解本发明的方法及其核心思想,而并不用于限制本发明。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。