1.本发明实施例是关于一种存储器技术,且特别为关于一种存储器装置及其形成方法。

背景技术:

2.许多现代电子装置包含配用以存储数据的电子存储器。随着技术的飞速发展,工程师们努力使存储器装置更小更复杂,以改进及开发更有效率、更可靠、更有能力的电子装置。单独的存储器可在三维(3d)存储器中进行垂直堆叠,允许更大的位元密度,使电子装置更有效率。

技术实现要素:

3.在一些实施例中,一种存储器装置的形成方法包括:形成多个字元线堆叠于一半导体基底上,分别包括多个字元线与多个绝缘层交替堆叠;沿着字元线堆叠的两相对侧壁形成一数据存储层;沿着数据存储层的两相对侧壁形成一通道层;形成一内部绝缘层位于通道层的内侧壁之间,且包括一第一介电材料;进行一隔离阻断制程,其包括第一蚀刻制程穿过内部绝缘层及通道层,以形成一隔离开口;形成一隔离结构,其填充隔离开口,且包括一第二介电材料;进行一第二蚀刻制程,穿过位于隔离结构的两相对侧的内部绝缘层,以形成多个源极/漏极开口;以及形成多个源极/漏极接点于源极/漏极开口内。

4.在一些实施例中,一种存储器装置的形成方法,包括:形成与多个绝缘层交替堆叠的多个字元线于一在半导体基底上;蚀刻出多个沟槽于上述字元线内而定义出上述字元线的多个内侧壁;沿着上述字元线的内侧壁形成一铁电数据存储层;沿着铁电数据存储层的多个内侧壁形成一通道层;形成一内部绝缘层于通道层的多个内侧壁之间,且包括一第一材料;蚀刻通道层及内部绝缘层,以形成一开口,其中开口从铁电数据存储层的一内侧壁连续延伸至铁电数据存储层的一相对内侧壁;形成一隔离结构于开口内,其中隔离结构包括对于第一材料具有高蚀刻选择性的一第二材料及横向延伸超过内部绝缘层的相对的外侧壁的一第一对相对的侧壁;以及蚀刻内部绝缘层并形成一对源极/漏极接点于隔离结构的两相对侧。

5.在一些实施例中,一种存储器装置,包括:一半导体基底;多个字元线堆叠,分别包括交替堆叠于半导体基底上的多个字元线及多个绝缘层。字元线大致延伸于第一方向并平行于半导体基底的一上表面;一铁电数据存储层,沿着字元线堆叠的两相对内侧延伸于第一方向;一通道层,延伸于第一方向,沿着铁电数据存储层的两相对内侧壁设置;一对源极/漏极区,设置于通道层的两相对内侧之间,大致沿垂直于半导体基底的上表面延伸,且大致垂直于字元线。此对源极/漏极区通过一第一介电材料的一绝缘结构沿第一方向相互分开;以及一隔离结构,设置于通道层及此对源极/漏极区的端点处,且排置于铁电数据存储层的两相对侧壁之间,其中隔离结构包括一第二介电材料,其不同于第一介电材料。

附图说明

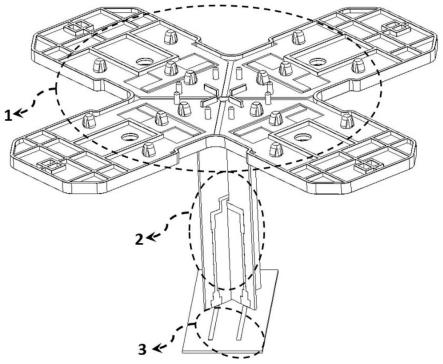

6.图1a-图1c绘示出一些实施例的包括不同材料的隔离结构及内部绝缘层的存储器装置剖面示意图及三维示意图。

7.图2绘示出一些实施例的三维(3d)存储器装置区块图。

8.图3-图14绘示出一些实施例的存储器装置的形成方法平面示意图及三维示意图,存储器装置包括在回缩内部绝缘层以形成源极/漏极区之前进行隔离阻断(isolation cut)以隔离记忆胞。

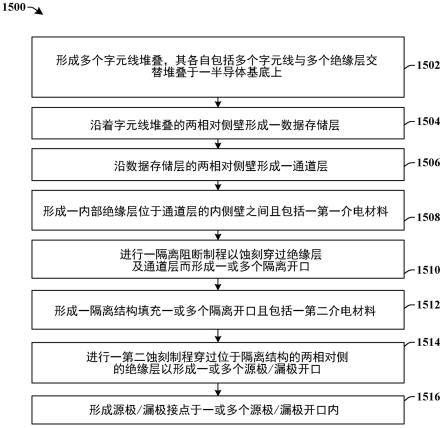

9.图15绘示出根据一些实施例的存储器装置的形成方法制造流程。

10.其中,附图标记说明如下:

11.1-1-1,1-1-1’,1-1-2,1-1-2’,2-1-1,2-1-1’,2-1-2,2-1-2’,3-1-1,3-1-1’,3-1-2,3-1-2’,3-2-1,3-2-1’,3-2-2,3-2-2’,3-3-1’,3-3-2’:记忆胞

12.100a,300a,400a,500a,600a,700a,800a,900a,1000a,1100a,1200a,1300a,1400a:剖面示意图

13.100b,100c,300b,400b,500b,600b,700b,800b,900b,1000b,1100b,1200b,1300b,1400b:三维(3d)示意图

14.102:隔离结构

15.104:绝缘层

16.106:数据存储层

17.108:通道层

18.110:介电层

19.112:内部绝缘层

20.114,402:填充层

21.116a:第一列记忆胞对

22.116b:第二列记忆胞对

23.118:半导体基底

24.120a:第一上层记忆胞对

25.120b:第二上层记忆胞对

26.120c:第三上层记忆胞对

27.120d:第四上层记忆胞对

28.120e:第五上层记忆胞对

29.122a:第一中层记忆胞对

30.122d:第四中层记忆胞对

31.124a:第一下层记忆胞对

32.124d:第四下层记忆胞对

33.200:区块图

34.202:源极线解码器

35.204:位元线解码器

36.206:字元线解码器

37.502a:第一沟槽

38.502b:第二沟槽

39.702:绝缘开口

40.802,1202:介电开口

41.902:隔离开口

42.1102:开口

43.1302:源极/漏极开口

44.1500:流程图

45.1502,1504,1506,1508,1510,1512,1514,1516:动作

46.bl-1,bl-1’,bl-2,bl-2’,bl-3’:漏极接点

47.ls1:第一表面

48.ls2:第二表面

49.ls3:第三表面

50.sl-1,sl-1’,sl-2,sl-2’,sl-3’:源极接点

51.st1:第一字元线堆叠

52.st2:第二字元线堆叠

53.st3:第三字元线堆叠

54.st4:第四字元线堆叠

55.wl1-1:第一下层字元线

56.wl1-1’:第四下层字元线

57.wl1-2:第二下层字元线

58.wl1-2’:第三下层字元线

59.wl2-1:第一中层字元线

60.wl2-2:第二中层字元线

61.wl2-2’:第三中层字元线

62.wl3-1:第一上层字元线

63.wl3-1’:第四上层字元线

64.wl3-2:第二上层字元线

65.wl3-2’:第三上层字元线

具体实施方式

66.以下的公开提供许多不同的实施例或范例,以实施本发明的不同特征部件。而以下的公开为叙述各个部件及其排列方式的特定范例,以求简化本公开。当然,这些仅为范例说明并非用以所定义本发明。举例来说,若为以下的公开叙述了将一第一特征部件形成于一第二特征部件之上或上方,即表示其包含了所形成的上述第一特征部件与上述第二特征部件为直接接触的实施例,亦包含了尚可将附加的特征部件形成于上述第一特征部件与上述第二特征部件之间,而使上述第一特征部件与上述第二特征部件可能未直接接触的实施例。另外,本公开于各个不同范例中会重复标号及/或文字。重复为为了达到简化及明确目的,而非自列指定所探讨的各个不同实施例及/或配置之间的关系。

67.再者,于空间上的相关用语,例如“下方”、“之下”、“下”、“上方”、“上”等等于此处

是用以容易表达出本说明书中所绘示的图式中元件或特征部件与另外的元件或特征部件的关系。这些空间上的相关用语除了涵盖图式所绘示的方位外,也涵盖装置于使用或操作中的不同方位。此装置可具有不同方位(旋转90度或其它方位)且此处所使用的空间上的相关符号同样有相应的解释。

68.三维(3d)存储器结构包括排列成行(row)及列(column)的记忆胞阵列。各个记忆胞包括一通道层、一对源极/漏极区设置于通道层一侧以及一字元线设置于通道层另一侧的。源极/漏极区通过内部绝缘层而彼此分开。在一些情况下,存储器的阵列的制作通过先形成多个字元线堆叠于一基底上、沿字元线堆叠的侧壁形成一通道材料以及形成绝缘材料于通道材料的内侧壁之间。然后,绝缘材料通过第一蚀刻制程形成多个源极/漏极开口及位于源极/漏极开口之间的内部绝缘层,并临时填入一虚置结构于形成的源极/漏极开口,以便于后续的制程。接着进行隔离阻断(包括第二蚀刻制程),以切割通道材料,形成不同记忆胞的隔离开口及隔离的通道层。然后使用不同于虚置结构的材料的一隔离结构填充隔离开口。隔离结构形成之后,选择性去除虚置结构,并以源极/漏极区取而代之。

69.上述的制程因虚置结构的形成及去除而变得复杂。另外,在去除虚置结构时,内部绝缘层及/或隔离结构可能损坏。这类损坏会导致效能问题,甚至是电性短路。或者,可能需要对虚置结构及隔离结构具有高蚀刻选择比的蚀刻剂(其非常昂贵)来避免对隔离结构。

70.有鉴于上述情况,本技术是关于一种在不使用虚置填充物及去除制程的情况下形成三维(3d)记忆胞的方法,以及相关的装置结构。在一些实施例中,形成了多个字元线堆叠,各自包括多个字元线与多个绝缘层交替堆叠。沿着多个元线堆叠的内侧壁形成一通道层(其沿第一方向延伸)。形成一绝缘层于通道层的内侧壁之间。进行一隔离阻断制程,其包括第一蚀刻制程,以蚀穿通道层,形成不同记忆胞的隔离开口及隔离通道层。随后以隔离结构填充隔离开口。然后,进行第二蚀刻制程穿过隔离结构两相对侧的绝缘层,形成源极/漏极开口,而源极/漏极接点填充于源极/漏极开口。相较于形成源极/漏极开口之后进行隔离阻断制程的方法,通过在形成源极/漏极开口之前进行隔离阻断制程及形成隔离结构,本方法免除了对于虚置结构的需要。因此,简化了制造制程。在一些实施例中,相对于绝缘层,隔离结构的材料以具有高蚀刻选择性的第二蚀刻制程进行蚀刻,使得蚀刻源极/漏极开口过程中免除了对于隔离结构的蚀刻损坏。这反而提高了三维(3d)存储器的制造效率。

71.图1a-图1c绘示出一些实施例的存储器装置的剖面示意图100a及三维示意图100b-100c,其中存储器装置包括具有不同材料的隔离结构及内部绝缘层。

72.如图1a的剖面示意图100a所示,存储器装置包括第一记忆胞3-2-1’,包括一第一字元线wl3-1’。一数据存储层106沿第一字元线wl3-1’的内侧壁设置。一通道层108沿数据存储层106的内侧壁设置,一介电层110沿通道层108的内侧壁设置,一内部绝缘层112沿介电层110的内侧壁设置。一对源极/漏极接点(例如,位元线bl-2’及源极线sl-2’)设置于内部绝缘层112的两相对侧,使得此对源极/漏极接点在第一方向上经由内部绝缘层112而横向分开。一隔离结构102沿着数据存储层106的内侧壁设置。

73.在一些实施例中,在第一记忆胞3-2-1’的操作期间,为了写入,一设定电压或一重置电压从第一字元线wl3-1’施加至通道层108及数据存储层106。设定电压将数据存储层106设定为一第一状态(例如,逻辑“1”),而重置电压将数据存储层106设置为一第二状态(例如,逻辑“0”)。数据存储层106用来存储第一状态或第二状态的数据的一位元。读取时,

一读取电压施加至第一字元线wl3-1’。读取电压可在第一状态的阈值电压与第二状态的阈值电压之间,使得读取电压会使通道层108在一种状态下导通,而在另一种状态则否。因此,数据的位元的状态可通过一对源极/漏极接点bl-2’、sl-2’之间的漏极电流来进行读取。

74.在一些实施例中,一对源极/漏极接点bl-2’、sl-2’可分别包括一第一表面ls1横向延伸于一第二方向(与第一方向实质上正交),并与隔离结构102接触。在一些实施例中,这对源极/漏极接点bl-2’、sl-2’可分别包括一第二表面ls2横向延伸于第二方向,并与内部绝缘层112接触。在一些实施例中,这对源极/漏极接点bl-2’、sl-2’可分别包括一第三表面ls3横向延伸于第二方向,并与介电层110接触。在进一步的实施例中,第三表面ls3在第一方向上横向位于第一表面ls1与第二表面ls2之间。在一些实施例中,通道层108的内侧壁与一对源极/漏极接点bl-2’、sl-2’接触。在一些实施例中,此对源极/漏极接点bl-2’、sl-2’与介电层110的内侧壁接触。

75.在一些实施例中,此对源极/漏极接点bl-2’、sl-2’包括与隔离结构102接触的一第一部及与内部绝缘层112接触的一第二部,并包括多个侧壁通过第三表面连接于第一部的多个侧壁。其中,第二部的多个侧壁横向位于第一部的多个侧壁之间。在一些实施例中,介电层110接触第一部的侧壁,而通道层108接触第二部的侧壁。在一些实施例中,隔离结构102的第一对的相对侧壁平行于且接触这对源极/漏极接点bl-2’、sl-2’。在一些实施例中,隔离结构102包括第二对的相对侧壁,且隔离结构102具有在第二对的相对的侧壁之间连续延伸的固定宽度。在一些实施例中,隔离结构102的第二对的相对侧壁横向分开此对源极/漏极接点bl-2’,sl-2’的第二部的侧壁。

76.存储器装置包括在结构及操作上相似于第一记忆胞3-2-1’的其他记忆胞。举例来说,存储器装置包括一第二记忆胞3-2-2’,其在结构及操作上均与第一记忆胞3-2-1’相似,存储器装置并包括一第二字元线wl3-2’。第一记忆胞3-2-1’及第二记忆胞3-2-2’定义出一第一记忆胞对。第一记忆胞对中的各个记忆胞共用一对源极/漏极接点bl-2’、sl-2’,并在第二方向上彼此横向分开。在一些实施例中,隔离结构102在第一方向上横向分开第一记忆胞对与一或多个记忆胞对,定义出记忆胞对的第一列。在一些实施例中,一或多个记忆胞对在结构上与第一记忆胞对相似。在一些实施例中,第一字元线wl3-1’及第二字元线wl3-2’可在第一方向上横向延伸,使得一或多个记忆胞对包括第一字元线wl3-1’及第二字元线wl3-2’。在一些实施例中,存储器装置还包括一第二列记忆胞对,结构上相似于第一列记忆胞对,存储器装置并包括第三字元线wl3-1及第四字元线wl3-2。在进一步的实施例中,第二列的记忆胞对通过填充层114在第二方向上横向分开第一列的记忆胞对。

77.隔离结构102可为不同于内部绝缘层112的材料。在一些实施例中,隔离结构102可为,例如,碳氧化硅、氮碳氧化硅、氧化铝、二氧化铪、氧化镧、一些其他合适的氧化物掺杂或金属氧化物材料(相对于内部绝缘层112可以高蚀刻选择比进行蚀刻)或一些其他合适的材料(相对于内部绝缘层112可以高蚀刻选择比进行蚀刻)或包括以上材料。在一些实施例中,高蚀刻选择比为大于1000∶1的比率。在蚀刻选择比低于1000∶1时,隔离结构102在蚀刻内部绝缘层112时可能受损。在一些实施例中,隔离结构102包括不同于内部绝缘层112的材料。

78.在一些实施例中,内部绝缘层112可为,例如,氧化物或一些其他合适的材料或包括以上材料。在一些实施例中,介电层110可为,例如,氧化铝、二氧化铪、氧化镧、氧化钛或一些其他合适的高介电材料或内部绝缘层112包括以上材料。在一些实施例中,通道层108

可为,例如,氧化铟镓锌、氧化锌、氧化锡或其他一些合适的氧化物半导体材料或通道层108包括以上材料。在一些实施例中,数据存储层106可为,例如,铁电材料(氧化铪、氧化铪或其他合适的铁电材料),磁隧道接面(mtj)或其他合适的数据存储结构或数据存储层106包括以上材料。在一些实施例中,第一字元线wl3-1’、第二字元线wl3-2’、第三字元线wl3-1及第四字元线wl3-2为导电的,且可为,例如,钨、氮化钛、铝铜、或一些其他合适的材料,或者上述字元线包括以上材料。在一些实施例中,一对源极/漏极接点bl-2’、sl-2’为导电的,且可为氮化钛、钨、钌或其他合适的材料,或者源极/漏极接点bl-2’、sl-2’包括以上材料。在一些实施例中,填充层114可为,例如,氮化物(例如,氮化硅、氧氮化硅)或一些其他合适的材料,或者填充层114包括以上材料。

79.由于隔离结构102包括相对于内部绝缘层112可以高蚀刻选择比进行蚀刻的材料,因此在形成一对源极/漏极接点期间消除了对于隔离结构102的蚀刻损伤。这反过来可提高三维(3d)存储器的制造效率。

80.如图1b的三维(3d)示意图100b所示,在一些实施例中,存储器装置包括位于半导体基底118上方的多个字元线堆叠st1、st2、st3、st4。各自的字元线堆叠st1、st2、st3、st4包括多个字元线与多个绝缘层104交替堆叠。举例来说,第一字元线堆叠st1包括与多个绝缘层104交替堆叠的多个字元线wl1-1、2-1、3-1。第二字元线堆叠st2包括与多个绝缘层104交替堆叠的多个字元线wl1-2、2-2、3-2。第三条字元线堆叠st3包括多个与多个绝缘层104交替堆叠的字元线wl 1-2’,2-2’,3-2’。第四字元线堆叠st4包括多个与多个绝缘层104交替堆叠的字元线wl 1-1’、2-1’、3-1’。在一些实施例中,第二字元线堆叠st2的字元线wl 1-2、2-2、3-2通过填充层114分别与第三字元线堆叠st3的字元线wl 1-2’、2-2’、3-2’通过填充层114分开。一数据存储层106沿着多个字元线堆叠st1、st2、st3、st4的两相对侧壁设置。一通道层108沿着数据存储层106的两相对侧壁设置、一介电层110沿着通道层108的两相对侧壁设置以及一内部绝缘层112设置于介电层110的两相对侧壁之间。多对源极/漏极接点bl-1’、sl-2’、bl-2’、sl-3’、sl-1、bl-1、sl-2、bl-2(例如,一位元线及一源极线)设置于内部绝缘层112的两相对侧,使得每对源极/漏极接点bl-1’、sl-2’、bl-2’、sl-3’、sl-1、bl-1、sl-2、bl-2在第一方向上通过内部绝缘层112彼此横向分开。隔离结构102设置于数据存储层106的两相对侧壁之间。

81.上述多对源极/漏极接点bl-1’、sl-2’、bl-2’、sl-3’、sl-1、bl-1、sl-2、bl-2包括一第一位元线bl-1’及第一源极线(未绘示)。第二位元线bl-2’及第二源极线sl-2’、第三位元元线(未绘示)及第三源极线sl-3’、第四位元线bl-1及第四源极线sl-1,以及第五位元线bl-2及第五源极线sl-2。

82.在一些实施例中,半导体基底118可为,例如,块材硅基底、块材锗基底、iii-v族基底或一些其他合适的半导体基底,或者半导体基底118包括上述材料。在一些实施例中,多个绝缘层104可为,例如,氧化物或一些其他合适的材料,或者绝缘层104包括上述材料。在一些实施例中,多个绝缘层104及内部绝缘层112由相同的材料组成。在一些实施例中,多个字元线为导电的,可为,例如,钨,氮化钛,铝铜,或一些其他合适的材料,或者字元线包括上述材料。在一些实施例中,多对源极/漏极接点bl-1’、sl-2’、bl-2’、sl-3’、sl-1、bl-1、sl-2、bl-2为导电的,可为氮化钛、钨、钌或其他一些合适的材料,或者上述源极/漏极接点包括上述材料。

83.如图1c的三维(3d)示意图100c所示,存储器装置包括多个记忆胞。在一些实施例中,记忆胞可在结构上及操作上相似于图1a中所绘示的记忆胞3-2-1’。多个记忆胞分成多个垂直堆叠的记忆胞层。在一些实施例中,二或更多的记忆胞对可相互垂直堆叠。多层记忆胞进一步分离成第一列记忆胞对116a及第二列记忆胞对116b,横向延伸于第一方向上。第一列记忆胞对116a的个别记忆胞标记为z-y-x’,第二列记忆胞对116b的个别记忆胞标记为z-y-x,其中z代表记忆胞的垂直位置(例如,1、2、3),其中y代表记忆胞在第一方向上的横向位置(例如,1、2、3),且其中x代表记忆胞的一对识别码(identifier)(例如,1、2)。

84.在多个垂直堆叠的上层内,第一列记忆胞对116a包括一第一上层记忆胞对120a(其包括记忆胞3-1-1’及3-1-2’)、一第二上层记忆胞对120b(其包括记忆胞3-2-1’及3-2-2’)以及一第三上层记忆胞对120c(其包括记忆胞3-3-1’及3-3-2’)。第二列记忆胞对116b包括一第四上层记忆胞对120d(其包括记忆胞3-1-1及3-1-2)以及一第五上层记忆胞对120e(其包括记忆胞3-2-1及3-2-2)。多个垂直堆叠层的一中间层实质上相似上层,使得中间层的个别记忆胞具有对应上层的记忆胞相同的y-x位置及2的z位置。在一些实施例中,中间层可包括,例如,记忆胞2-1-1’及2-1-2’(例如,第一中层记忆胞对122a)、2-1-1及2-1-2(第四中层记忆胞对122d)以及2-2-1。多个垂直堆叠层的一下层实质上相似上层,例如下层的个别记忆胞具有对应上层的记忆胞相同的y-x位置及1的z位置。在一些实施例中,下层可包括,例如,记忆胞1-1-1’及1-1-2’(例如,第一下层记忆胞对124a)、1-1-1及1-1-2(例如,第四下层记忆胞对124d)以及1-2-1。

85.图2绘示出一些实施例的三维(3d)存储器装置的一区块图200。存储器装置可如图1a-图1b中所述。在一些实施例中,存储器装置包括多个记忆胞,分成一第一列记忆胞对及一第二列记忆胞对。第一列记忆胞对中的个别记忆胞标记为z-y-x’,第二列记忆胞对中的个别记忆胞标记为z-y-x,其中z代表记忆胞的垂直位置(例如,1、2、3),其中y代表记忆胞的横向位置(例如,1、2、3),而x代表记忆胞的一对识别码(例如,1,2)。在一些实施例中,第一列记忆胞对包括18个记忆胞。在进一步的实施例中,具有三层垂直堆叠的记忆胞,使得对应膜层包括三个记忆胞对。在一些实施例中,第二列的记忆胞对包括12个记忆胞。在进一步的实施例中,具有三层记忆胞垂直堆叠,使得对应膜层包括两个记忆胞对。在一些实施例中,可能有超过两列的记忆胞对。在某些实施例中,可能有超过三层的记忆胞。

86.存储器装置还包括多个字元线电性耦接至多个记忆胞中对应的记忆胞。第一列记忆胞对的个别字元线标记为wlz-x’,第二列记忆胞对的个别字元线标记为wlz-x,其中z代表记忆胞的垂直位置(例如,1、2、3),而其中x代表记忆胞的对识别码(例如,1、2),使得在每一列记忆胞对中,具有共同z及x位置的各个记忆胞共用一共同的字元线。多对位元线及源极线(例如,多对源极/漏极接点)也电性耦接至多个记忆胞中对应的记忆胞。第一列记忆胞对中的个别位元线及源极线对分别标为bl-y’及sl-y’,而第二列记忆胞对中的个别位元线及源极线则分别标示为bl-y及sl-y,其中y代表记忆胞的横向位置(例如,1,2,3),使得在每一列的记忆胞对中,各自的位元线及源极线垂直地延伸通过记忆胞的每一层,并由对应的记忆胞对中的每一者所共用。

87.在一些实施例中,各个源极线(例如,sl-1’、sl-2’、sl-3’、sl-1、sl-2)连接至一源极线解码器(source line decoder,sld)202。在一些实施例中,各个位元线(例如,bl-1’、bl-2’、bl-3’、bl-1、bl-2)连接至一位元线解码器(bit line decoder,bld)204。在一些实

施例中,各个字元线(例如,wl1-1’、wl2-1’、wl3-1’、wl1-2’、wl2-2’、wl3-2’、wl1-1、wl2-1、wl3-1、wl1-2、wl2-2、wl3-2)连接至一字元线解码器(word line decoder,wld)206。

88.请参照图3-图14,一连串的平面示意图及三维(3d)示意图300a-1400b绘示出一些实施例的一种存储器装置的形成方法,存储器装置包括一隔离结构,相对于一内部绝缘层,隔离结构以高蚀刻选择性进行蚀刻。在一些实施例中,存储器装置可为第1a-1c图的存储器装置。尽管图3-图14述及一种方法,但可理解的是,图3-图14中所示的结构并未局限于上述的方法,而是可脱离于上述方法而独立存在的结构。

89.如图3的平面示意图300a及三维(3d)示意图300b所示,多个绝缘层104与多个填充层402交替形成于半导体基底118上。在一些实施例中,多个填充层402可为,例如,氮化物(例如,氮化硅,氮氧化硅),或一些其他合适的材料,或包括上述材料。在一些实施例中,多个绝缘层104及多个填充层402通过沉积制程(例如,化学气相沉积(chemical vapor deposition,cvd)制程、等离子体增强化学气相沉积(plasma enhanced cvd,cvd)制程、物理气相沉积(physical vapor deposition process)制程或相似的方式)形成。

90.如图4的平面示意图400a及三维(3d)示意图400b所示,一第一沟槽502a及一第二沟槽502b形成于多个绝缘层104及多个填充层402内,以定义多个绝缘层104的内侧壁及多个填充层402的内侧壁。第一沟槽502a及第二沟槽502b沿第一方向延伸,并由多个绝缘层104沿第二方向隔开,而第二方向可实质上正交于第一方向。然后,通过蚀刻(例如,湿式蚀刻制程)局部的多个填充层402,以定义出位于多个绝缘层104之间的多个空间。在一些实施例中,多个填充层402的余留部分可称作填充层114。

91.如图5的平面示意图500a及三维(3d)示意图500b所示,然后将第一导电材料沉积至多个空间内,且去除制程去除第一导电材料多余的量。第一导电材料的对应部分及多个绝缘层104定义出多个字元线堆叠st1、st2、st3、st4(其分别包括与多个绝缘层104交替堆叠的多个字元线)。多个字元线堆叠st1、st2、st3、st4中的一第一字元线堆叠st1包括一第一下层字元线wl1-1、一第一中层字元线wl2-1及一第一上层字元线wl3-1。多个字元线堆叠st1、st2、st3、st4中的一第二字元线堆叠st2包括一第二下层字元线wl1-2、一第二中层字元线wl2-2、一第二上层字元线wl3-2。多个字元线堆叠st1、st2、st3、st4中的一第三字元线堆叠st3包括一第三下层字元线wl1-2’、一第三中层字元线wl2-2’及一第三上层字元线wl3-2’。多个字元线堆叠st1、st2、st3、st4中的一第四字元线堆叠st4包括一第四下层字元线wl1-1’、一第四中层字元线wl2-1’及一第四上层字元线wl3-1’。在一些实施例中,第三下层字元线wl1-2’通过填充层114与第二下层字元线wl1-2分开。在进一步的实施例中,第三中层字元线wl2-2’也通过填充层114与第二中层字元线wl2-2分开,而第三上层字元线wl3-2’也通过填充层114与第二上层字元线wl3-2分开。在一些实施例中,填充层114将各自的字元线与多个绝缘层104分开。

92.第一沟槽502a及第二沟槽502b可通过第一蚀刻制程(例如干式蚀刻及/或湿式蚀刻)进行蚀刻。在各种实施例中,第一蚀刻制程包括干式蚀刻,其利用等离子体蚀刻剂、离子轰击蚀刻剂或相似物,及/或可利用湿式蚀刻剂(包括氢氟酸(hf)、氢氧化钾(koh)、碱性湿式蚀刻剂或相似物)。在各种实施例中,湿式蚀刻可利用湿式蚀刻剂,其包括由磷酸(h3po4)、氢氟酸(hf)、氢氧化钾(koh)、碱性湿式蚀刻剂或相似物。去除制程可为或包括,例如,湿式蚀刻。第一导电材料可通过沉积制程的方式(例如,原子层沉积(ald)制程、化学气相沉积

(cvd)制程、物理气相沉积(pvd)制程、溅镀制程、电镀制程(例如,电镀制程、无电镀制程)或相似方式)进行沉积。

93.如图6的平面示意图600a及三维(3d)示意图600b所示,形成一数据存储层106于多个绝缘层104上、于第一沟槽502a及第二沟槽502b内以及沿着多个绝缘层104的内侧壁及多个字元线的内侧壁。然后,一第一去除制程去除数据存储层106的横向部分。然后形成一通道层108于多个绝缘层104上、于第一沟槽502a及第二沟槽502b内以及沿着数据存储层106的内侧壁。然后,一第二去除制程去除数据存储层106的横向延伸部分。然后形成一介电层110于多个绝缘层104上、于第一沟槽502a及第二沟槽502b内以及沿着通道层108的内侧壁。然后,一第三去除制程去除通道层108的横向延伸部分。然后在介电层110的内侧壁之间形成一内部绝缘层112,以填充第一沟槽502a及第二沟槽502b。在一些实施例中,内部绝缘层112接着经受一第一平坦化制程,以去除多余的材料。

94.第一去除制程、第二去除制程及第三去除制程可为或包括,例如,湿式蚀刻制程及/或干式蚀刻制程。在各种实施例中,湿式蚀刻制程可使用湿式蚀刻剂,包括氢氟酸(hf)、氢氧化钾(koh)、碱性湿式蚀刻剂或相似的蚀刻剂。在一些实施例中,干式蚀刻制程可使用干式蚀刻剂,包括等离子体蚀刻剂、离子轰击蚀刻剂或相似的蚀刻剂。第一平坦化制程可为或包括,例如,化学机械平坦化(chemical-mechanical planarization,cmp)、磨削、蚀刻或一些其他合适的制程。数据存储层106、通道层108、介电层110及内部绝缘层112可通过,例如,沉积制程(例如,化学气相沉积(cvd)制程、等离子体增强化学气相沉积(cvd)制程、物理气相沉积制程或相似制程)形成。

95.如图7的平面示意图700a及三维(3d)示意图700b所示,于第一沟槽502a及第二沟槽502b内,于内部绝缘层112内蚀刻出一或多个绝缘开口702,留下露出的介电层110的第一部。在一些实施例中,一或多个绝缘开口702延伸穿过内部绝缘层112,并可从内部绝缘层112的上表面延伸至半导体基底118的上表面。可通过湿式蚀刻制程及/或干式蚀刻制程来蚀刻出一或多个绝缘开口702。在各种实施例中,湿式蚀刻制程可使用湿式蚀刻剂,包括氢氟酸(hf)、氢氧化钾(koh)、碱性湿式蚀刻剂或相似的蚀刻剂。在一些实施例中,干式蚀刻制程可使用干式蚀刻剂,包括等离子体蚀刻剂、离子轰击蚀刻剂或相似的蚀刻剂。

96.如图8的平面示意图800a及三维(3d)示意图800b所示,在第一沟槽502a及第二沟槽502b内,蚀刻去除介电层110的第一露出部,留下通道层108的第一露出部并定义出一或多个介电开口802。在一些实施例中,介电层110的露出部从内部绝缘层112的上表面蚀刻至半导体基底118的上表面。可通过湿式蚀刻制程及/或干式蚀刻制程来蚀刻介电层110。在各种实施例中,湿式蚀刻制程可使用湿式蚀刻剂,包括氢氟酸(hf)、氢氧化钾(koh)、碱性湿式蚀刻剂或相似的蚀刻剂。在一些实施例中,干式蚀刻制程可使用干式蚀刻剂,包括等离子体蚀刻剂、离子轰击蚀刻剂或相似的蚀刻剂。

97.如图9的平面示意图900a及三维(3d)示意图900b所示,于第一沟槽502a及第二沟槽502b内,蚀刻去除通道层108的第一露出部,留下数据存储层106的露出部并定义出隔离开口902。在一些实施例中,通道层108的第一露出部从内部绝缘层112的上表面蚀刻至内部绝缘层112的下表面。可通过湿式蚀刻制程及/或干式蚀刻制程来蚀刻通道层108。在各种实施例中,湿式蚀刻制程可使用湿式蚀刻剂,包括氢氟酸(hf)、氢氧化钾(koh)、碱性湿式蚀刻剂或相似的蚀刻剂。在一些实施例中,干式蚀刻制程可使用包括干式蚀刻剂,包括等离子体

蚀刻剂、离子轰击蚀刻剂或相似的蚀刻剂。

98.如图10的平面示意图1000a及三维(3d)示意图1000b所示,于各个隔离开口902内形成一隔离结构102。在一些实施例中,隔离结构102经受一第二平坦化制程,以去除多余的材料。在一些实施例中,隔离结构102延伸穿过内部绝缘层112,并可从内部绝缘层112的上表面延伸至半导体基底118的上表面。隔离结构102可通过沉积制程(例如,化学气相沉积(cvd)制程、等离子体增强化学气相沉积(cvd)制程、物理气相沉积制程或相似制程)形成。第二平坦化制程可为或包括,例如,化学机械平坦化(cmp)、磨削、蚀刻或一些其他合适的制程。

99.如图11的平面示意图1100a及三维(3d)示意图1100b所示,于第一沟槽502a及第二沟槽502b内,蚀刻隔离结构102的两相对侧的内部绝缘层112部分,以形成一对或多对开口1102,留下露出的介电层110的第二部。在一些实施例中,内部绝缘层112从内部绝缘层112的上表面蚀刻至内部绝缘层112的下表面。可通过湿式蚀刻制程及/或干式蚀刻制程来蚀刻内部绝缘层112。在各种实施例中,湿式蚀刻制程可使用湿式蚀刻剂,包括氢氟酸(hf)、氢氧化钾(koh)、碱性湿式蚀刻剂或相似的蚀刻剂。在一些实施例中,干式蚀刻制程可使用干式蚀刻剂,包括等离子体蚀刻剂、离子轰击蚀刻剂或相似的蚀刻剂。

100.如图12的平面示意图1200a及三维(3d)示意图1200b所示,于第一沟槽502a及第二沟槽502b内,蚀刻去除介电层110的第二露出部,留下通道层108的第二露出部并定义出一对或多对介电开口1202。在一些实施例中,介电层110的第二露出部从内部绝缘层112的上表面蚀刻至内部绝缘层112的下表面。可通过例如湿式蚀刻制程及/或干式蚀刻制程来蚀刻介电层110的露出部。在各种实施例中,湿式蚀刻制程可使用湿式蚀刻剂,包括氢氟酸(hf)、氢氧化钾(koh)、碱性湿式蚀刻剂或相似的蚀刻剂。在一些实施例中,干式蚀刻制程可使用干式蚀刻剂,包括等离子体蚀刻剂、离子轰击蚀刻剂或相似的蚀刻剂。

101.如图13的平面示意图1300a及三维(3d)示意图1300b所示,于第一沟槽502a及第二沟槽502b内,对隔离结构102的两相对侧的内部绝缘层112上进行回缩(pullback)蚀刻,留下露出的介电层110的第二部并定义出源极/漏极开口1302。相对于隔离结构102,内部绝缘层112以高蚀刻选择性进行蚀刻。这免除了在蚀刻源极/漏极开口1302过程中对对隔离结构102的蚀刻损害。这反而有效分离了第一及第二沟槽502a、502b内相邻的记忆胞对,提高了记忆胞装置的效率。在一些实施例中,相对于隔离结构102,内部绝缘层112可以至少1000:1的蚀刻选择比进行蚀刻。在一些实施例中,内部绝缘层112是从内部绝缘层112的上表面蚀刻至下表面。回缩蚀刻可为或包括,湿式蚀刻制程。在各种实施例中,湿式蚀刻制程可使用湿式蚀刻剂。包括氢氟酸(hf)、氢氧化钾(koh)、碱性湿式蚀刻剂、氟化物类的化学剂或气体或相似的蚀刻剂。

102.如图14的平面示意图1400a及三维(3d)示意图1400b所示,第二导电材料形成于源极/漏极开口1302内,定义出一对源极/漏极接点。个别的一对源极/漏极接点包括一源极线(例如,sl-1、sl-2、sl-2’、sl-3’)及一位元线(例如,bl-1、bl-2、bl-1’、bl-2’),垂直延伸穿过多层的记忆胞。在一些实施例中,第二导电材料经受一第三个平坦化制程,以去除多余的材料。在一些实施例中,在形成第二导电材料后,隔离结构102及填充层114将存储器结构分离成第一列的记忆胞对、记忆胞对的第二列、记忆胞的下层、记忆胞的中层、以及记忆胞的上层。第三平坦化制程可为或包括,化学机械平坦化(cmp)、磨削、蚀刻或一些其他合适的制

程。第二导电材料可通过沉积制程(例如,原子层沉积(ald)制程、化学气相沉积(cvd)制程、物理气相沉积(pvd)制程、溅镀制程、电镀制程(例如,电镀制程、无电镀制程)或相似方式)进行沉积。

103.请参照图15,流程图1500绘示出一些实施例的存储器装置的形成方法,存储器装置包括一隔离结构(相对于内部绝缘层,隔离结构以高蚀刻选择性进行蚀刻)。举例来说,上述方法可对应于第3-14图的方法。

104.尽管所公开的流程图1500所绘示所述为一连串的动作或情事,但可理解的是,上述动作或情事所绘示的顺序不应解释为具限制性。举例来说,除了此处所绘示及/或所述的动作或情事以外,一些动作可能以不同的顺序发生及/或与其他动作或情事同时发生。另外,并非所有绘示的动作都需要实施此处所述的一或多个型态或实施例。再者,此处所述的一或多个动作可在一或多个分别的动作及/或阶段中进行。

105.在动作1502中,形成多个字元线堆叠,其各自包括多个字元线与多个绝缘层交替堆叠于一半导体基底上。图3-图5绘示出对应于动作1502的一些实施例的平面示意图300a-500a及三维(3d)示意图300b-500b。

106.在动作1504中,沿着字元线堆叠的两相对侧壁形成一数据存储层。图6绘示出对应于动作1504的一些实施例的平面示意图600a及三维(3d)示意图600b。

107.在动作1506中,沿数据存储层的两相对侧壁形成一通道层。图6绘示出对应于动作1506的一些实施例的平面示意图600a及三维(3d)示意图600b。

108.在动作1508中,形成包括一第一介电材料的一内部绝缘层于通道层的内侧壁之间。图6绘示出对应于动作1508的一些实施例的平面示意图600a及三维(3d)示意图600b。

109.在动作1510中,进行一隔离阻断制程(其包括一第一蚀刻制程),以蚀刻穿过绝缘层及通道层而形成一隔离开口。图7-图9绘示出对应于动作1510的一些实施例的平面示意图700a-900a及三维(3d)示意图700b-900b。

110.在动作1512中,形成包括一第二介电材料的一隔离结构,填充隔离开口。图10绘示出对应于动作1512的一些实施例的平面示意图1000a及三维(3d)示意图1000b。

111.在动作1514中,进行一第二蚀刻制程穿过位于隔离结构的两相对侧的绝缘层,以形成源极/漏极开口。相对于隔离结构,内部绝缘层以具有高蚀刻选择性进行蚀刻,以免除在蚀刻源极/漏极开口过程中对于隔离结构的蚀刻损伤。这反而有效分离了两相邻的记忆胞对,提高了存储器装置的效率。图11-图13绘示出对应于动作1514的一些实施例的平面示意图1100a-1300a及三维(3d)示意图1100b-1300b。

112.在动作1516中,形成源极/漏极接点于源极/漏极开口内。图14绘示出对应于动作1516的一些实施例的平面示意图1400a及三维(3d)示意图1400b。

113.因此,在一些实施例中,本公开系有关于一种存储器装置的形成方法,包括:形成多个字元线堆叠于一半导体基底上,分别包括多个字元线与多个绝缘层交替堆叠;沿着字元线堆叠的两相对侧壁形成一数据存储层;沿着数据存储层的两相对侧壁形成一通道层;形成一内部绝缘层位于通道层的内侧壁之间,且包括一第一介电材料;进行一隔离阻断制程,其包括第一蚀刻制程穿过内部绝缘层及通道层,以形成一隔离开口;形成一隔离结构,其填充隔离开口,且包括一第二介电材料;进行一第二蚀刻制程,穿过位于隔离结构的两相对侧的内部绝缘层,以形成多个源极/漏极开口;以及形成多个源极/漏极接点于源极/漏极

开口内。

114.在一些实施例中,上述方法还包括:在形成内部绝缘层之前,沿着通道层的内侧壁形成一介电层。再者,在一些实施例中,第一蚀刻制程包括:蚀刻出一绝缘开口于内部绝缘层内,留下介电层的多个露出部;横向蚀刻介电层的多个露出部,留下通道层的多个露出部;以及横向蚀刻通道层的多个露出部,以定义出隔离开口。再者,在一些实施例中,第二蚀刻制程包括:蚀刻位于隔离结构的两相对侧的部分的内部绝缘层,以形成多个开口而留下介电层的多个第一露出部;横向蚀刻介电层的多个第一露出部,留下露出的部分的通道层;以及对位于隔离结构的两相对侧的内部绝缘层进行一回缩制程,留下介电层的多个第二露出部且定义出源极/漏极开口。在一些实施例中,第二介电材料不同于第一介电材料。在一些实施例中,源极/漏极接点的外侧壁与内部绝缘层的外侧壁分开。在一些实施例中,数据存储层一铁电材料。在一些实施例中,第二介电材料包括一金属氧化物或掺杂氧。在一些实施例中,相对于第二介电材料,第一介电材料以大于1000∶1的蚀刻选择比进行蚀刻。

115.在其他实施例中,本公开系有关于一种存储器装置的形成方法,包括:形成与多个绝缘层交替堆叠的多个字元线于一在半导体基底上;蚀刻出多个沟槽于上述字元线内而定义出上述字元线的多个内侧壁;沿着上述字元线的内侧壁形成一铁电数据存储层;沿着铁电数据存储层的多个内侧壁形成一通道层;形成一内部绝缘层于通道层的多个内侧壁之间,且包括一第一材料;蚀刻通道层及内部绝缘层,以形成一开口,其中开口从铁电数据存储层的一内侧壁连续延伸至铁电数据存储层的一相对内侧壁;形成一隔离结构于开口内,其中隔离结构包括对于第一材料具有高蚀刻选择性的一第二材料及横向延伸超过内部绝缘层的相对的外侧壁的一第一对相对的侧壁;以及蚀刻内部绝缘层并形成一对源极/漏极接点于隔离结构的两相对侧。

116.在一些实施例中,一对源极/漏极接点中各自包括:一第一部,接触隔离结构;以及一第二部,接触内部绝缘层,且包括多个侧壁,其通过一横向延伸表面连接第一部的多个侧壁,其中第二部的侧壁横向位于第一部的侧壁之间。在一些实施例中,上述方法还包括:在形成内部绝缘层之前,沿着通道层的内侧壁形成一介电层。再者,一些实施例中,上述方法还包括:蚀刻出一绝缘开口于内部绝缘层内,留下介电层的多个露出部;在蚀刻出绝缘开口后,横向蚀刻介电层的多个露出部,留下通道层的多个露出部;以及在蚀刻出绝缘开口后,横向蚀刻通道层的多个露出部,留下铁电数据存储层的多个露出部,并定义出开口。再者,在一些实施例中,隔离结构形成于铁电数据存储层的多个露出部之间,并与其接触。在一些实施例中,隔离结构的第一对相对的侧壁平行于一对源极/漏极接点,并与的接触。在一些实施例中,隔离结构包括一第二对相对的侧壁,其中在形成此对源极/漏极接点之后,隔离结构具有一等宽延续性延伸于第二对相对的侧壁之间。

117.在另一实施例中,本公开系关于一种存储器装置,包括:一半导体基底;多个字元线堆叠,分别包括交替堆叠于半导体基底上的多个字元线及多个绝缘层。字元线大致延伸于第一方向并平行于半导体基底的一上表面;一铁电数据存储层,沿着字元线堆叠的两相对内侧延伸于第一方向;一通道层,延伸于第一方向,沿着铁电数据存储层的两相对内侧壁设置;一对源极/漏极区,设置于通道层的两相对内侧之间,大致沿垂直于半导体基底的上表面延伸,且大致垂直于字元线。此对源极/漏极区通过一第一介电材料的一绝缘结构沿第一方向相互分开;以及一隔离结构,设置于通道层及此对源极/漏极区的端点处,且排置于

铁电数据存储层的两相对侧壁之间,其中隔离结构包括一第二介电材料,其不同于第一介电材料。

118.在一些实施例中,第二介电材料对第一介电材料具有高蚀刻选择性。在一些实施例中,存储器装置还包括:一介电层,沿通道层的内侧壁设置,并于沿着与第一方向正交的一第二方向延伸的一表面处接触此对源极/漏极区。

119.以上概略说明了本发明实施例的特征部件,使所属技术领域中具有通常知识者对于本公开的型态可更为容易理解。任何所属技术领域中具有通常知识者应了解到可轻易利用本公开作为其它制程或结构的变更或设计基础,以进行相同于此处所述实施例的目的及/或获得相同的优点。任何所属技术领域中具有通常知识者也可理解与上述等同的结构并未脱离本公开的精神及保护范围,且可于不脱离本公开的精神及范围,当可作更动、替代与润饰。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。