电荷泵电路

1.相关申请的交叉引用

2.本技术案要求2021年1月28日提交的美国临时申请案第63/142,498号的优先权权益。上文所提及的专利申请案的全部内容特此以引用的方式并入本文中且构成本说明书的一部分。

技术领域

3.本公开涉及电路;特定来说,本公开涉及电荷泵电路。

背景技术:

4.显示装置大体上包括显示面板和驱动电路。由于限制显示面板的材料,所以驱动电路的一些部分通常安置于驱动集成电路上而非显示面板上。举例来说,扫描信号产生器安置于驱动集成电路上以为显示面板上的像素提供扫描信号。

5.然而,为了将来自驱动集成电路的扫描信号提供到显示面板,需要低阻抗传输。此外,为了优化区域开销,扫描信号用于提供到所有像素。因此,传输线的低电阻和低寄生电容以及扫描信号的条件将一些限制引入到显示装置。

6.此外,电压调节器通常使用电荷泵电路。由于电荷泵电路的输出并非线性的,电荷泵电路并非适合于信号产生器。

技术实现要素:

7.本公开是针对电荷泵电路,以便实施像素中扫描信号产生器(in-pixel sweep signal generator)。

8.在本公开中,电荷泵电路包含第一晶体管、第一电容器、第二晶体管以及第二电容器。第一晶体管具有第一端和第二端。第一电容器具有第一端和第二端。第一电容器的第二端电连接到第一晶体管的第二端。第二晶体管具有第一端和第二端。第二晶体管的第一端电连接到第一晶体管的第二端。第二电容器具有第一端和第二端。第二电容器的第一端电连接到第二晶体管的第二端。

9.基于以上内容,根据本公开的电荷泵电路,通过将多个输入信号施加到电荷泵电路,获得多个输出信号。由于电荷泵电路的结构是简单的,所以其能够安置于衬底上且由此可实施像素中扫描信号产生器。

10.为了可更好地理解前述内容,如下参考附图详细地描述若干实施例。

附图说明

11.包含附图以提供对本公开的进一步理解,且附图并入本说明书中并构成本说明书的一部分。附图示出本公开的示范性实施例,且与描述一起用来解释本公开的原理。

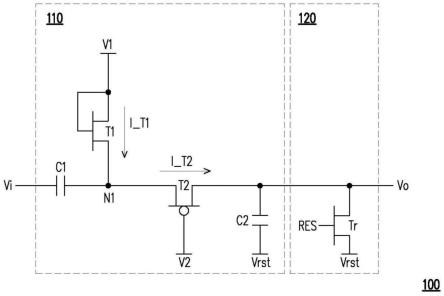

12.图1是根据本公开的第一实施例的电荷泵电路的示意图;

13.图2是根据本公开的第一实施例的电荷泵电路的示意性信号时序图;

14.图3是根据本公开的第二实施例的电荷泵电路的示意图;

15.图4是根据本公开的第二实施例的电荷泵电路的示意性信号时序图;

16.图5是根据本公开的第二实施例的修改的电荷泵电路的示意图;

17.图6是根据本公开的第三实施例的电荷泵电路的示意图;

18.图7是根据本公开的第三实施例的修改的电荷泵电路的示意图;

19.图8是根据本公开的第四实施例的电荷泵电路的示意图;

20.图9是根据本公开的第四实施例的电荷泵电路的示意性信号时序图;

21.图10是根据本公开的第四实施例的修改的电荷泵电路的示意图;

22.图11a是根据本公开的一个实施例的用于am-led显示面板的像素电路的示意性框图。

23.图11b是根据本公开的一个实施例的用于am-led显示面板的像素电路的示意性信号时序图;

24.图12a是根据本公开的一个实施例的用于光子计数检测器的像素电路的示意性框图;

25.图12b是根据本公开的一个实施例的用于光子计数检测器的像素电路的比较器的示意性输入信号;

26.图12c是根据本公开的一个实施例的用于光子计数检测器的像素电路的比较器的示意性输出信号;

27.图12d是根据本公开的一个实施例的用于光子计数检测器的像素电路的计数器的示意性输出信号;

28.图13是根据本公开的一个实施例的任意波形产生器的示意图。

29.附图标号说明

30.100、300、500、600、700、800、1000、1103:电荷泵电路;

31.110:升压电路;

32.120:复位电路;

33.1100、1200:像素电路;

34.1101:扫描晶体管;

35.1102:电容器;

36.1104:比较器;

37.1105:电流产生器;

38.1106:发光二极管;

39.1110:发射时间段;

40.1201:光检测器;

41.1202:脉冲整形器;

42.1203:第一比较器;

43.1204:第二比较器;

44.1205:第一计数器;

45.1206:第二计数器;

46.1207:第一扫描晶体管;

47.1208:第二晶体管;

48.1210、vi、vi3、vi5、vi6、vi7、vi8、vi10:输入信号;

49.1220:第一比较信号;

50.1230:第二比较信号;

51.1240:第一计数信号;

52.1250:第二计数信号;

53.1300:任意波形产生器;

54.c1、c31、c51、c61、c71、c81、c101:第一电容器;

55.c1d:第一下调电容器;

56.c1u:第一上调电容器;

57.c2、c32、c52、c62、c72、c82、c102、c132:第二电容器;

58.c33、c53、c63、c73、c83、c103:第三电容器;

59.comp3、comp5:补偿信号;

60.comp81、comp101:第一补偿信号;

61.comp82、comp102:第二补偿信号;

62.data(m):数据线;

63.d_pwm:脉冲宽度调制数据;

64.e_c:发射控制信号;

65.init3、init5、init6、init7:初始化信号;

66.i_c32、i_c62、i_c72、i_c82、i_c102:第二电容器电流;

67.i_pd:光检测器电流;

68.i_t1、i_t31、i_t51、i_t61、i_t71、i_t81、i_t101:第一晶体管电流;

69.i_t2、i_t32、i_t52、i_c62、i_t72、i_t82、i_t102:第二晶体管电流;

70.i_t33、i_t53、i_t83、i_t103:第三晶体管电流;

71.i_t34、i_t64、i_t74、i_t84、i_t104:第四晶体管电流;

72.i_t35、i_t65、i_t75、i_t85、i_t105:第五晶体管电流;

73.i_t36、i_t66、i_t86、i_t106:第六晶体管电流;

74.i_t88_1、i_108_1:第八晶体管步骤一电流;

75.i_t88_3、i_t108_3:第八晶体管步骤三电流;

76.i_t88_4:第八晶体管步骤四电流;

77.i_t89、i_t109:第九晶体管电流;

78.l:光;

79.n1、n31、n51、n61、n71、n81、n101:第一节点;

80.n32、n52、n62、n72、n82、n102:第二节点;

81.n33、n53、n63、n73、n83、n103:第三节点;

82.q:额外电荷;

83.q':不足电荷;

84.res、res3、res5、res6、res7、res8、res10、res13:复位信号;

85.ref1:第一参考信号;

86.ref2:第二参考信号;

87.scan(n):扫描线;

88.scan1(n):第一扫描线;

89.sense(m):感测线;

90.sw:扫描信号;

91.t1、t31、t51、t61、t71、t81、t101:第一晶体管;

92.t2、t32、t52、t62、t72、t82、t102:第二晶体管;

93.t33、t53、t63、t73、t83、t103:第三晶体管;

94.t34、t54、t64、t74、t84、t104:第四晶体管;

95.t35、t55、t65、t75、t85、t105:第五晶体管;

96.t36、t56、t66、t76、t86、t106:第六晶体管;

97.t87、t107:第七晶体管;

98.t88、t108:第八晶体管;

99.t89、t109:第九晶体管;

100.tr、t13r:复位晶体管;

101.t_d1:第一下调晶体管;

102.t_d2:第二下调晶体管;

103.t_u1:第一上调晶体管;

104.t_u2:第二上调晶体管;

105.t_1、t_2、t_3、t_31、t_32、t_33、t_34、t_t35、t_36、t_37、t_38、t_39、t_4、t_5、t_6、t_7:时间;

106.v1:第一电压;

107.v2:第二电压;

108.vdd、vh:第一参考电压;

109.vid:输入下调信号;

110.vin:输入电压;

111.viu:输入上调信号;

112.vl、vss:第二参考电压;

113.vo、vo3、vo5、vo6、vo7、vo8、vo10、vo13:输出信号;

114.vrst、vrst3、vrst5、vrst6、vrst7、vrst8、vrst10、vrst13:复位电压;

115.vstep、vstep3、vstep5、vstep6、vstep7、vstep8、vstep10:跨步电压;

116.vth1、vth31、vth51、vth61、vth71、vth81、vth101:第一阈值电压;

117.vth2、vth32、vth52、vth62、vth72、vth82、vth102:第二阈值电压;

118.vth63、vth73、vth83、vth103:第三阈值电压;

119.vth64、vth74:第四阈值电压。

具体实施方式

120.现将详细参照本公开的示范性实施例,附图中示出所述示范性实施例的实例。只要可能,在附图和描述中使用相同参考标号来指代相同或相似组件。

121.在本公开的整个本说明书和所附权利要求中,特定术语用以指代特定组件。本领域的技术人员应理解,电子装置制造商可通过不同名称来指相同组件。本文并不意图区分具有相同功能但不同名称的那些组件。在以下描述和权利请求中,如“包括”和“包含”的词语是开放式术语,且应解释为“包含但不限于

…”

。

122.贯穿本技术的整个说明书(包含所附权利要求)所使用的术语“耦合(或连接)”可指任何直接或间接连接构件。举例来说,如果文本描述第一装置耦合(或连接)到第二装置,那么应解释为第一装置可直接连接到第二装置,或第一装置可通过其它装置或某些连接构件间接连接以连接到第二装置。贯穿本技术的整个说明书(包含所附权利要求)所提及的术语“第一”、“第二”以及类似术语仅用于命名离散元件或用于区分不同实施例或范围。因此,术语不应视为限制元件数量的上限或下限且不应用于限制元件的布置顺序。另外,在可能的情况下,在附图和实施例中使用相同参考标号的元件/组件/步骤表示相同或类似部分。在不同实施例中可使用相同参考标号或使用相同术语来相互参考元件/组件/步骤的相关描述。

123.本公开的发光装置可例如适于液晶、发光二极管、量子点(quantum dot;qd)、荧光、磷光体、其它合适的材料或前述材料的组合,但本公开不限于此。发光二极管可包含例如有机发光二极管(organic light emitting diode;oled)、亚毫米发光二极管(微led)、微型发光二极管(微型led)或量子点发光二极管(quantum dot light emitting diode;qled或qdled)或其它合适的材料。材料可任意地布置和组合,但本公开不限于此。本公开的发光装置可包含支持发光装置的外围系统,如驱动系统、控制系统、光源系统、机箱系统和类似物。

124.应注意,在以下实施例中,可在不脱离本公开的精神的情况下替换、重组以及混合若干不同实施例的技术特征以完成其它实施例。只要每一实施例的特征并不违反本公开的精神或彼此冲突,其可任意地一起混合和使用。

125.图1是根据本公开的第一实施例的电荷泵电路的示意图。参考图1,电荷泵电路100可包含升压(pump up)电路110和复位电路120。升压电路110可包含第一晶体管t1、第二晶体管t2、第一电容器c1以及第二电容器c2。具体来说,第一晶体管t1可具有第一端和第二端。在一个实施例中,第一晶体管t1的第一端可以是源极端子,且第一晶体管t1的第二端可以是漏极端子,但本公开不限于此。在另一实施例中,第一晶体管t1的第一端可以是漏极端子,且第一晶体管t1的第二端可以是源极端子。在实施例中,第一电容器c1可具有第一端和第二端。第一电容器c1的第二端可在第一节点n1处电连接到第一晶体管t1的第二端。第二晶体管t2可具有第一端和第二端。在实施例中,第二晶体管t2的第一端可在第一节点n1处电连接到第一晶体管t1的第二端。第二电容器c2可具有第一端和第二端。第二电容器c2的第一端可电连接到第二晶体管t2的第二端。

126.此外,复位电路120可包含复位晶体管tr。复位晶体管可具有第一端和第二端。复位晶体管tr的第一端可电连接到第二电容器c2的第一端。复位晶体管tr的第二端可接收复位电压。复位晶体管tr可进一步具有控制端。复位晶体管tr的控制端可接收复位信号res。

127.在实施例中,复位电路120可安置于电荷泵电路100中。复位电路120和升压电路110可集成在电子装置中(例如,显示装置的像素中)。在实施例中,电子装置可包含发光装置或显示装置,但本公开不限于此。在一个实施例中,显示装置可包含有源矩阵发光二极管

(active matrix light emitting diode;am-led)显示面板,但本公开不限于此。

128.此外,在一个实施例中,复位电路120可安置于电荷泵电路100外部。在实施例中,复位电路120可安置于显示装置的像素的驱动集成电路上以将复位信号res提供到升压电路110。也就是说,电荷泵电路100可不包含复位电路120,但本公开不限于此。

129.图2是根据本公开的第一实施例的电荷泵电路的示意性信号时序图。参考图1和图2,第一电容器c1的第一端可接收输入信号vi,且第二电容器c2的第一端可提供输出信号vo。在实施例中,晶体管t1的第一端接收第一电压v1,且第二晶体管t2的控制端接收第二电压v2。第一电压v1可低于第二电压v2,但本公开不限于此。第二电容器c2的第二端接收复位电压vrst。第一晶体管t1可具有第一阈值电压vth1,且第二晶体管t2可具有第二阈值电压vth2。第一晶体管t1的第一端电连接到第一晶体管的控制端。也就是说,第一晶体管t1可充当二极管。在实施例中,第一晶体管t1可以是n型晶体管,且第二晶体管t2可以是p型晶体管,但本公开不限于此。在一个实施例中,第一晶体管t1可以是p型晶体管,且第二晶体管t2可以是n型晶体管。

130.在实施例中,为方便理解,例如,第一电压v1可以是7伏。第二电压v2可以是9伏。第一阈值电压vth1和第二阈值电压vth2的绝对值可以是1伏,但本公开不限于此。在时间t_1处,复位信号res可从低电压电平切换到高电压电平。在高电压电平施加到复位晶体管tr的控制端之后,复位晶体管tr接通,且第二电容器c2的第一端复位到复位电压vrst。也就是说,输出信号vo复位到复位电压vrst。在时间t_2之前,复位信号res可从高电压电平切换到低电压电平。此外,第一节点n1的电压可通过从第一电压v1减去第一阈值电压vth1获得,因此第一节点n1的电压可表示为v1-|vth1|。

131.在时间t_2处,输入信号vi可从低电压电平切换到高电压电平,且低电压电平与高电压电平之间的电压差可以是输入电压vin。在实施例中,假定输入电压vin是5伏,但本公开不限于此。由于第一电容器c1的第一端与第二端之间的电压差可维持恒定值,所以第一节点n1的电压可从v1-|vth1|变为v1-|vth1| vin。然而,由于第一节点n1电连接到第二晶体管t2的第一端,所以第一节点n1的电压值可受第二晶体管t2约束。也就是说,在时间t_2处,第一节点n1的电压值可以是v2 |vth2|(图2中的n1的实线)而非v1-|vth1| vin(图2中的n1的虚线),且第二晶体管t2可接通。因此,额外电荷q可基于电压差而从第一电容器c1放电且可由以下等式(1)计算。

132.q=c1

×

{(v1-|vth1|) vin-(v2 |vth2|)}

…………

(1)

133.在实施例中,额外电荷q可通过第二晶体管电流i_t2从第一电容器c1传递到第二电容器c2,且由此可对第二电容器c2充电。也就是说,输出信号vo的值可增加跨步电压vstep的值,且跨步电压vstep的值可由以下等式(2)计算。

[0134][0135]

在实施例中,第一电容器c1与第二电容器c2的比率可以是1/100。也就是说,跨步电压vstep的值可以是10毫伏。因此,输出信号vo的值可从复位电压vrst增加到vrst vstep。

[0136]

在时间t_3处,输入信号vi可从高电压电平切换到低电压电平,且低电压电平与高电压电平之间的电压差也可以是输入电压vin。由于第一电容器c1的第一端与第二端之间

的电压差可维持恒定值,所以第一节点n1的电压可从v2 |vth2|变为v2 |vth2|-vin。然而,由于第一节点n1电连接到第一晶体管t1的第二端,所以第一节点n1的电压值可受第一晶体管t1约束。也就是说,在时间t_3处,第一节点n1的电压值可以是v1-|vth1|(图2中的n1的实线)而非v2 |vth2|-vin(图2中的n1的虚线),且第一晶体管t1可接通。因此,不足电荷q'可基于电压差而通过第一晶体管电流i_t1充电到第一电容器c1中,且可由以下等式(3)计算。

[0137]q′

=c1

×

{(v2 |vth2|)-vin-(v1 |vth1|)}=-q

…………

(3)

[0138]

在时间t_4处,输入信号vi可从低电压电平切换到高电压电平,且低电压电平与高电压电平之间的电压差可以是输入电压vin。参考时间t_2,额外电荷q可从第一电容器c1放电。此外,额外电荷q可通过第二晶体管电流i_t2从第一电容器c1传递到第二电容器c2,且由此可对第二电容器c2充电。也就是说,输出信号vo的值可增加跨步电压vstep的值。因此,输出信号vo的值可从vrst vstep增加到vrst (2

×

vstep)。

[0139]

在时间t_5处,输入信号vi可从高电压电平切换到低电压电平,且低电压电平与高电压电平之间的电压差也可以是输入电压vin。参考时间t_3,不足电荷q'可通过第一晶体管电流i_t1充电到第一电容器c1中。

[0140]

在时间t_6处,输入信号vi可从低电压电平切换到高电压电平,且低电压电平与高电压电平之间的电压差可以是输入电压vin。参考时间t_2和时间t_4,额外电荷q可从第一电容器c1放电。此外,额外电荷q可通过第二晶体管电流i_t2从第一电容器c1传递到第二电容器c2,且由此可对第二电容器c2充电。也就是说,输出信号vo的值可增加跨步电压vstep的值。因此,输出信号vo的值可从vrst (2

×

vstep)增加到vrst (3

×

vstep)。

[0141]

在时间t_7处,输入信号vi可从高电压电平切换到低电压电平,且低电压电平与高电压电平之间的电压差也可以是输入电压vin。参考时间t_3和时间t_5,不足电荷q'可通过第一晶体管电流i_t1充电到第一电容器c1中。

[0142]

应注意,在时间t_2、时间t_4以及时间t_6处,输出信号vo可分别增加跨步电压vstep的值。也就是说,通过重复切换高电压电平与低电压电平之间的输入信号vi,输出信号vo的值可增加到多个不同值。此外,所述多个不同值可与切换输入信号vi的重复次数成正比。也就是说,各种波形可能够由电荷泵电路100输出,且输出是大体上线性的。因此,电荷泵电路100可用作信号产生器。在一个实施例中,电荷泵电路100可用作显示装置的像素的扫描信号产生器以实施像素中扫描信号产生器。此外,由于电荷泵电路100的结构是简单的,所以电荷泵电路100可安置于衬底上且由此可实施像素中扫描信号产生器。在一个实施例中,衬底可包括玻璃或聚酰亚胺或其它合适的材料,但本公开不限于此。

[0143]

在实施例中,第二晶体管t2是p型晶体管,但本公开不限于此。在实施例中,第二晶体管t2可提供第二电容器c2的充电电流(第二晶体管电流i_t2),且由此电荷泵电路100可以是升压电路。在另一实施例中,第二晶体管t2可以是n型晶体管,且由此可提供第二电容器c2的放电电流。因此,电荷泵电路100可变为降压(pump down)电路。

[0144]

图3是根据本公开的第二实施例的电荷泵电路的示意图。参考图1和图3,电荷泵电路300可具有与电荷泵电路100类似的结构。电荷泵电路300可包含第一晶体管t31、第二晶体管t32、第一电容器c31以及第二电容器c32。这些元件可称为电荷泵电路100且本文中不逐一地冗余地描述细节。

[0145]

在实施例中,电荷泵电路300可还包含第三晶体管t33、第四晶体管t34、第五晶体

管t35、第六晶体管t36以及第三电容器c33。在实施例中,第三晶体管t33可具有第一端和第二端。第三晶体管t33可电连接于第二晶体管t32的第二端与第二电容器c32的第一端之间。第三电容器c33可具有第一端和第二端。第三电容器c33的第一端可电连接到第二晶体管t32的控制端。第四晶体管t34可具有第一端和第二端。第四晶体管t34可电连接于第二晶体管t32的第二端与第三电容器c33的第一端之间。第五晶体管t35可具有第一端和第二端。第五晶体管t35可电连接于第四晶体管t34的第二端与第三电容器c33的第二端之间。第六晶体管t36可具有第一端和第二端。第六晶体管t36可电连接于第三晶体管t33的第二端与第二电容器c32的第二端之间。在实施例中,第一电容器c31的第二端可指示为第一节点n31,第三电容器c33的第一端可指示为第二节点n32,且第二电容器c32的第一端可指示为第三节点n33。在实施例中,第一晶体管t31可具有第一阈值电压vth31,第二晶体管t32可具有第二阈值电压vth32,但本公开不限于此。

[0146]

在实施例中,第一晶体管t31的第一端接收第一参考电压vh。第二电容器c32的第二端接收第二参考电压vl。第三电容器c33的第二端接收复位电压vrst3。在实施例中,第五晶体管t35的控制端可接收复位信号res3。第六晶体管t36的控制端可接收初始化信号init3。在实施例中,第三晶体管t33的控制端和第四晶体管t34的控制端接收补偿信号comp3。在实施例中,第一电容器c31的第一端可接收输入信号vi3。第二电容器c32的第一端可提供输出信号vo3。

[0147]

图4是根据本公开的第二实施例的电荷泵电路的示意性信号时序图。参考图3和图4,附图中的带圆圈数字可分别指示电荷泵电路300的操作的不同步骤。具有附图中的带圆圈数字的箭头可分别指示电荷泵电路300的操作的某一步骤期间的电流。朝向第一电容器c31的箭头可指示对第一电容器c31充电,且远离第一电容器c31的箭头可指示使第一电容器c31放电。

[0148]

在从时间t_31到时间t_32的时间段(步骤1)期间,复位信号res3可从低电压电平切换到高电压电平,且补偿信号comp3和初始化信号init3可保持在低电压电平下。在高电压电平施加到第五晶体管t35的控制端之后,第五晶体管t35接通。因此,第三电容器c33的第一端通过第五晶体管电流i_t35复位到复位电压vrst3。也就是说,第二节点n32复位到复位电压vrst3。由于复位电压vrst3在低电压电平下,所以第二晶体管t32可接通。此外,第一晶体管t31由于第一参考电压vh的高电压电平而接通,且第三晶体管t33由于补偿信号comp3的低电压电平而接通。因此,第一节点n31和第三节点n33均通过第二电容器电流i_c32复位到vh-|vth31|。在时间t_32之前,复位信号res可从高电压电平切换到低电压电平。

[0149]

在从时间t_32到时间t_33的时间段(步骤2)期间,补偿信号comp3可从低电压电平切换到高电压电平。在高电压电平施加到第三晶体管t33和第四晶体管t34的控制端之后,第三晶体管t33从接通切换到断开,且第四晶体管t34从断开切换到接通。第二节点n32随后通过第四晶体管电流i_t34补偿到vh-|vth31|-|vth32|。在时间t_33之前,补偿信号comp3可从高电压电平切换到低电压电平。

[0150]

在从时间t_33到时间t_34的时间段(步骤3)期间,初始化信号init3可从低电压电平切换到高电压电平。在高电压电平施加到第六晶体管t36的控制端之后,第六晶体管t36从断开切换到接通。节点n33通过第六晶体管电流i_t36复位到第二参考电压vl。在时间t_34之前,初始化信号init3可从高电压电平切换到低电压电平。

[0151]

在从时间t_t34到时间t_t35的时间段(步骤4)期间,输入信号vi3可从低电压电平切换到高电压电平,且低电压电平与高电压电平之间的电压差可以是输入电压vin。由于第一电容器c1的第一端与第二端之间的电压差可维持恒定值,所以第一节点n31的电压可从vh-|vth31|变为vh-|vth31| vin。然而,由于第一节点n31电连接到第二晶体管t32的第一端,所以第一节点n31的电压值可受第二晶体管t32约束。也就是说,在时间t_34处,第一节点n31的电压值可保持在vh-|vth31|(图4中的n31的实线)而非vh-|vth31| vin(图4中的n31的虚线)下。第二晶体管t32和第三晶体管t33可接通。因此,额外电荷q可基于电压差而从第一电容器c31放电且可由以下等式(4)计算。

[0152]

q=c31

×

{(vh-|vth31| vin)-(vh-|vth31|)}=c31

×

vin

…

(4)

[0153]

在实施例中,额外电荷q可通过第二晶体管电流i_t32和第三晶体管电流i_t33从第一电容器c31传递到第二电容器c32且由此可对第二电容器c32充电。也就是说,输出信号vo3的值可增加跨步电压vstep3的值,且跨步电压vstep3的值可由以下等式(5)计算。

[0154][0155]

因此,输出信号vo3的值可从第二参考电压vl增加到vl vstep3。

[0156]

在从时间t_35到时间t_36的时间段(步骤5)期间,输入信号vi3可从高电压电平切换到低电压电平,且低电压电平与高电压电平之间的电压差也可以是输入电压vin。由于第一电容器c1的第一端与第二端之间的电压差可维持恒定值,所以第一节点n31的电压可从vh-|vth31|变为vh-|vth31|-vin。然而,由于第一节点n31电连接到第一晶体管t31的第二端,所以第一节点n31的电压值可受第一晶体管t31约束。也就是说,在时间t_34处,第一节点n31的电压值可保持在vh-|vth31|(图4中的n31的实线)而非vh-|vth31|-vin(图4中的n31的虚线)下,且第一晶体管t31可接通。因此,不足电荷q'可基于电压差而通过第一晶体管电流i_t31充电到第一电容器c31中,且可由以下等式(6)计算。

[0157]q′

=c31

×

{(vh-|vth31|-vin)-(vh-|vth31|)}=c31

×

(-vin)=-q

…………

(6)

[0158]

在从时间t_36到时间t_37的时间段期间,充电操作可作为步骤4再次重复。额外电荷q可从第一电容器c31放电。此外,额外电荷q可通过第二晶体管电流i_t32和第三晶体管电流i_t33从第一电容器c31传递到第二电容器c32且由此可对第二电容器c32充电。因此,输出信号vo3的值可从vl vstep3增加到vl (2

×

vstep3)。在从时间t_37到时间t_38的时间段期间,充电操作可作为步骤5再次重复。不足电荷q'可通过第一晶体管电流i_t31充电到第一电容器c31中。

[0159]

在从时间t_38到时间t_39的时间段期间,充电操作可作为步骤4再次重复。额外电荷q可从第一电容器c31放电。此外,额外电荷q可通过第二晶体管电流i_t32和第三晶体管电流i_t33从第一电容器c31传递到第二电容器c32且由此可对第二电容器c32充电。因此,输出信号vo3的值可从vl (2

×

vstep3)增加到vl (3

×

vstep3)。在时间t_39之后,充电操作可作为步骤5再次重复。不足电荷q'可通过第一晶体管电流i_t31充电到第一电容器c31中。

[0160]

应注意,输出信号vo3的值可在时间t_34、时间t_36以及时间t_38处分别增加跨步电压vstep3的值。也就是说,通过重复步骤4和步骤5,输出信号vo3的值可增加到多个不同值。此外,所述多个不同值与步骤4和步骤5的重复次数成正比。也就是说,各种波形可能够由电荷泵电路300输出,且输出是大体上线性的。因此,电荷泵电路300可用作信号产生器。

在一个实施例中,电荷泵电路300可用作显示装置的像素的扫描信号产生器以实施像素中扫描信号产生器。此外,由于电荷泵电路300的结构是简单的,所以电荷泵电路300可安置于衬底上,且由此可实施像素中扫描信号产生器。

[0161]

在实施例中,第二晶体管t32是p型晶体管,但本公开不限于此。在实施例中,第二晶体管t32可提供第二电容器c32的充电电流(第二晶体管电流i_t32)且由此电荷泵电路300可以是升压电路。在另一实施例中,第二晶体管t32可以是n型晶体管,且由此可提供第二电容器c32的放电电流。因此,电荷泵电路300可变为降压电路。

[0162]

图5是根据本公开的第二实施例的修改的电荷泵电路的示意图。参看图5,图3与图5之间的主要差异在于电荷泵电路300的第二晶体管t32是p型晶体管且电荷泵500的第二晶体管t52是n型晶体管。在实施例中,电荷泵电路500可包含第一晶体管t51、第二晶体管t52、第一电容器c51以及第二电容器c52。这些元件可称为电荷泵电路100且本文中不逐一地冗余地描述细节。

[0163]

在实施例中,电荷泵电路500可还包含第三晶体管t53、第四晶体管t54、第五晶体管t55、第六晶体管t56以及第三电容器c53。在实施例中,第三晶体管t53可具有第一端和第二端。第三晶体管t53可电连接于第二晶体管t52的第二端与第二电容器c52的第一端之间。第三电容器c53可具有第一端和第二端。第三电容器c53的第一端可电连接到第二晶体管t52的控制端。第四晶体管t54可具有第一端和第二端。第四晶体管t54可电连接于第二晶体管t52的第二端与第三电容器c53的第一端之间。第五晶体管t55可具有第一端和第二端。第五晶体管t55可电连接于第四晶体管t54的第二端与第三电容器c53的第二端之间。第六晶体管t56可具有第一端和第二端。第六晶体管t56可电连接于第三晶体管t53的第二端与第二电容器c52的第二端之间。

[0164]

在实施例中,第一电容器c51的第二端可指示为第一节点n51,第三电容器c53的第一端可指示为第二节点n52,且第二电容器c52的第一端可指示为第三节点n53。在实施例中,第一晶体管t51可具有第一阈值电压vth51,第二晶体管t52可具有第二阈值电压vth52,但本公开不限于此。在实施例中,第一晶体管t51的第一端接收第二参考电压vl。第二电容器c52的第二端接收第一参考电压vh。第三电容器c53的第二端接收复位电压vrst5。

[0165]

在实施例中,第五晶体管t55的控制端可接收复位信号res5。第六晶体管t56的控制端可接收初始化信号init5。在实施例中,第三晶体管t53的控制端和第四晶体管t54的控制端可接收补偿信号comp5。在实施例中,第一电容器c51的第一端可接收输入信号vi5。第二电容器c52的第一端可提供输出信号vo5。

[0166]

在实施例中,附图中的带圆圈数字可分别指示电荷泵电路500的操作的不同步骤。具有附图中的带圆圈数字的箭头可分别指示电荷泵电路500的操作的某一步骤期间的电流。朝向第一电容器c51的箭头可指示对第一电容器c51充电,且远离第一电容器c51的箭头可指示使第一电容器c51放电。

[0167]

在实施例中,步骤1到步骤3可指第二实施例的步骤1到步骤3,同时本文中不逐一地冗余地描述细节。应注意,复位信号res5、补偿信号comp5以及初始化信号init5可在步骤1、步骤2以及步骤3期间分别从高电压电平切换到低电压电平。因此,在步骤1期间,第一节点n51和第三节点n53可复位到vl |vth51|,且第二节点n52可复位到复位电压vrst5。在步骤2期间,第二节点n52可补偿到vl |vth51| |vth52|。在步骤3期间,第三节点n53可初始化

到第一参考电压vh。

[0168]

在步骤4的时间段期间,输入信号vi5可从高电压电平切换到低电压电平,且低电压电平与高电压电平之间的电压差可以是输入电压vin。由于第一电容器c51的第一端与第二端之间的电压差可维持恒定值,所以第一节点n51的电压可从vl |vth51|变为vl |vth51|-vin。然而,由于第一节点n51电连接到第二晶体管t52的第一端,所以第一节点n51的电压值可受第二晶体管t52约束。也就是说,在步骤4期间,第一节点n51的电压值可保持在vl |vth51|而非vl |vth51|-vin下。第二晶体管t52和第三晶体管t53可接通。因此,不足电荷q'可基于电压差而充电到第一电容器c51中。不足电荷q'的值可等于c51

×

(-vin)。

[0169]

在实施例中,不足电荷q'可通过第二晶体管电流i_t52和第三晶体管电流i_t53从第二电容器c52传递到第一电容器c51且由此可使第二电容器c52放电。也就是说,输出信号vo5的值可减小跨步电压vstep5的值,且跨步电压vstep5的值可等于(c51/c52)

×

vin。因此,输出信号vo5的值可从第一参考电压vh减小到vh-vstep5。

[0170]

在步骤5的时间段期间,输入信号vi5可从低电压电平切换到高电压电平,且低电压电平与高电压电平之间的电压差也可以是输入电压vin。由于第一电容器c51的第一端与第二端之间的电压差可维持恒定值,所以第一节点n51的电压可从vl |vth51|变为vl |vth51| vin。然而,由于第一节点n51电连接到第一晶体管t51的第二端,所以第一节点n51的电压值可受第一晶体管t51约束。也就是说,在步骤5的时间段期间,第一节点n51的电压值可保持在vl |vth51|而非vl |vth51| vin下,且第一晶体管t51可接通。因此,额外电荷q可基于电压差而通过第一晶体管电流i_t51从第一电容器c51放电且可等于(-q')。

[0171]

应注意,输出信号vo5的值可在步骤4期间减小跨步电压vstep5的值。也就是说,通过重复步骤4和步骤5,输出信号vo5的值可减小到多个不同值。此外,所述多个不同值与步骤4和步骤5的重复次数成正比。也就是说,各种波形可能够由电荷泵电路500输出,且输出是线性的。因此,电荷泵电路500可用作信号产生器。在一个实施例中,电荷泵电路500可用作显示装置的像素的扫描信号产生器以实施像素中扫描信号产生器。此外,由于电荷泵电路500的结构是简单的,所以电荷泵电路500可安置于衬底上且由此可实施像素中扫描信号产生器。

[0172]

图6是根据本公开的第三实施例的电荷泵电路的示意图。参考图1和图6,电荷泵电路600可具有与电荷泵电路100类似的结构。电荷泵电路600可包含第一晶体管t61、第二晶体管t62、第一电容器c61以及第二电容器c62。这些元件可称为电荷泵电路100且本文中不逐一地冗余地描述细节。

[0173]

在实施例中,电荷泵电路600可还包含第三晶体管t63、第四晶体管t64、第五晶体管t65、第六晶体管t66以及第三电容器c63。在实施例中,第三晶体管t63可具有第一端和第二端。第四晶体管t64可具有第一端和第二端。第四晶体管t64的第二端可电连接到第三晶体管t63的第一端。第五晶体管t65可具有第一端和第二端。第五晶体管t65的第一端可电连接到第四晶体管t64的第一端。第六晶体管t66可具有第一端和第二端。第六晶体管t65的第一端可电连接到第二电容器c62的第一端。第六晶体管t66的第二端可电连接到第二电容器c62的第二端。第三电容器c63可具有第一端和第二端。第三电容器c63的第一端可电连接到第五晶体管c65的第一端。第三电容器c63的第二端可电连接到第五晶体管c65的第二端。

[0174]

在实施例中,第一电容器c61的第二端可指示为第一节点n61,第三电容器c63的第

一端可指示为第二节点n62,且第二电容器c62的第一端可指示为第三节点n63。在实施例中,第一晶体管t61可具有第一阈值电压vth61,第二晶体管t62可具有第二阈值电压vth62,第三晶体管t63可具有第三阈值电压vth63,且第四晶体管t64可具有第四阈值电压vth64。在实施例中,第一阈值电压vth61可等于第三阈值电压vth63,且第二阈值电压vth62可等于第四阈值电压vth64,但本公开不限于此。在实施例中,第一晶体管t61的第一端和第三晶体管t63的第二端接收第一参考电压vh。第二电容器c62的第二端接收第二参考电压vl。第三电容器c63的第二端接收复位电压vrst6。

[0175]

在实施例中,第五晶体管t65的控制端可接收复位信号res6。第六晶体管t66的控制端可接收初始化信号init6。在实施例中,第三晶体管t63的第二端可电连接到第三晶体管t63的控制端。第四晶体管t64的第一端可电连接到第四晶体管t64的控制端。在实施例中,第一电容器c61的第一端可接收输入信号vi6。第二电容器c62的第一端可提供输出信号vo6。

[0176]

在实施例中,附图中的带圆圈数字可分别指示电荷泵电路600的操作的不同步骤。具有附图中的带圆圈数字的箭头可分别指示电荷泵电路600的操作的某一步骤期间的电流。朝向第一电容器c61的箭头可指示对第一电容器c61充电,且远离第一电容器c61的箭头可指示使第一电容器c61放电。在实施例中,步骤1和步骤3可指第二实施例的步骤1和步骤3,同时本文中不逐一地冗余地描述细节。应注意,由于第一晶体管t61到第四晶体管t64的阈值电压的指定条件而不需要实施例中的步骤2。也就是说,第三晶体管t63和第四晶体管t64被指定以提供用于补偿的第四晶体管电流i_t64。此外,复位信号res6和初始化信号init6可在步骤1和步骤3的时间段期间分别从低电压电平切换到高电压电平。因此,在步骤1的时间段期间,第一节点n61和第三节点n63可通过第二电容器电流i_c62复位到vh-|vth61|,且第二节点n62可通过第五晶体管电流i_t65复位到复位电压vrst6。在步骤3的时间段期间,第三节点n63可通过第六晶体管电流i_t66初始化到第二参考电压vl,且第二节点n62可初始化到vh-|vth61|-|vth62|。

[0177]

在步骤4的时间段期间,输入信号vi6可从低电压电平切换到高电压电平,且低电压电平与高电压电平之间的电压差可以是输入电压vin。由于第一电容器c61的第一端与第二端之间的电压差可维持恒定值,所以第一节点n61的电压可从vh-|vth61|变为v1-|vth61| vin。然而,由于第一节点n61电连接到第二晶体管t62的第一端,所以第一节点n61的电压值可受第二晶体管t62约束。也就是说,在步骤4的时间段期间,第一节点n61的电压值可保持在vh-|vth61|而非vh-|vth61| vin下。第二晶体管t62可接通。因此,额外电荷q可基于电压差而从第一电容器c61放电且可等于c61

×

vin。

[0178]

在实施例中,额外电荷q可通过第二晶体管电流i_t62从第一电容器c61传递到第二电容器c62,且由此可对第二电容器c62充电。也就是说,输出信号vo6的值可增加跨步电压vstep6的值,且跨步电压vstep6的值可等于(c61/c62)

×

vin。因此,输出信号vo6的值可从第二参考电压vl增加到vl vstep6。

[0179]

在步骤5的时间段期间,输入信号vi6可从高电压电平切换到低电压电平,且低电压电平与高电压电平之间的电压差也可以是输入电压vin。由于第一电容器c61的第一端与第二端之间的电压差可维持恒定值,所以第一节点n61的电压可从vh-|vth61|变为vh-|vth61|-vin。然而,由于第一节点n61电连接到第一晶体管t61的第二端,所以第一节点n61

的电压值可受第一晶体管t61约束。也就是说,在步骤5的时间段期间,第一节点n61的电压值可保持在vh-|vth61|而非vh-|vth61|-vin下,且第一晶体管t61可接通。因此,不足电荷q'可基于电压差而通过第一晶体管电流i_t61充电到第一电容器c61中且可等于(-q)。

[0180]

应注意,输出信号vo6的值可在步骤4期间增加跨步电压vstep6的值。也就是说,通过重复步骤4和步骤5,输出信号vo4的值可增加到多个不同值。此外,所述多个不同值与步骤4和步骤5的重复次数成正比。也就是说,各种波形可能够由电荷泵电路600输出,且输出是线性的。因此,电荷泵电路600可用作信号产生器。在一个实施例中,电荷泵电路600可用作显示装置的像素的扫描信号产生器以实施像素中扫描信号产生器。此外,由于电荷泵电路600的结构是简单的,所以电荷泵电路600可安置于衬底上且由此可实施像素中扫描信号产生器。

[0181]

在实施例中,第二晶体管t62是p型晶体管,但本公开不限于此。在实施例中,第二晶体管t62可提供第二电容器c62的充电电流(第二晶体管电流i_t62),且由此电荷泵电路600可以是升压电路。在另一实施例中,第二晶体管t62可以是n型晶体管,且由此可提供第二电容器c62的放电电流。因此,电荷泵电路600可变为降压电路。

[0182]

图7是根据本公开的第三实施例的修改的电荷泵电路的示意图。参看图7,图6与图7之间的主要差异在于电荷泵电路600的第二晶体管t62是p型晶体管且电荷泵700的第二晶体管t72是n型晶体管。在实施例中,电荷泵电路700可包含第一晶体管t71、第二晶体管t72、第一电容器c71以及第二电容器c72。这些元件可称为电荷泵电路100且本文中不逐一地冗余地描述细节。

[0183]

在实施例中,电荷泵电路700可还包含第三晶体管t73、第四晶体管t74、第五晶体管t75、第六晶体管t76以及第三电容器c73。在实施例中,第三晶体管t73可具有第一端和第二端。第三晶体管t73的第一端可电连接到第四晶体管t74的第二端。第三电容器c73可具有第一端和第二端。第三电容器c73的第一端可电连接到第二晶体管t72的控制端。第四晶体管t74可具有第一端和第二端。第四晶体管t74可电连接于第二晶体管t72的控制端与第三晶体管t73的第一端之间。第五晶体管t75可具有第一端和第二端。第五晶体管t75可电连接于第四晶体管t74的第一端与第三电容器c73的第二端之间。第六晶体管t76可具有第一端和第二端。第六晶体管t76可电连接于第二电容器c72的第一端与第二电容器c72的第二端之间。

[0184]

在实施例中,第一电容器c71的第二端可指示为第一节点n71,第三电容器c73的第一端可指示为第二节点n72,且第二电容器c72的第一端可指示为第三节点n73。在实施例中,第一晶体管t71可具有第一阈值电压vth71,第二晶体管t72可具有第二阈值电压vth72,第三晶体管t73可具有第三阈值电压vth73,且第四晶体管t74可具有第四阈值电压vth74。在实施例中,第一阈值电压vth71可等于第三阈值电压vth73,且第二阈值电压vth72可等于第四阈值电压vth74,但本公开不限于此。

[0185]

在实施例中,第一晶体管t71的第一端、第三晶体管t73的控制端以及第三晶体管t73的第二端接收第二参考电压vl。第二电容器c72的第二端接收第一参考电压vh。第三电容器c73的第二端接收复位电压vrst7。在实施例中,第五晶体管t75的控制端可接收复位信号res7。第六晶体管t76的控制端可接收初始化信号init7。在实施例中,第一电容器c71的第一端可接收输入信号vi7。第二电容器c72的第一端可提供输出信号vo7。

[0186]

在实施例中,具有附图中的带圆圈数字的箭头可分别指示电荷泵电路700的操作的某一步骤期间的电流。朝向第一电容器c71的箭头可指示对第一电容器c71充电,且远离第一电容器c71的箭头可指示使第一电容器c71放电。在实施例中,步骤1到步骤3可指第二实施例的步骤1到步骤3的时间段,同时本文中不逐一地冗余地描述细节。应注意,由于第一晶体管t71到第四晶体管t74的阈值电压的指定条件而不需要实施例中的步骤2。也就是说,第三晶体管t73和第四晶体管t74被指定以提供用于补偿的第四晶体管电流i_t74。此外,复位信号res7和初始化信号init7可在步骤1和步骤3的时间段期间分别从高电压电平切换到低电压电平。因此,在步骤1的时间段期间,第一节点n71和第三节点n73可通过第二电容器电流i_c72复位到vl |vth71|,且第二节点n72可通过第五晶体管电流i_t75复位到复位电压vrst7。在步骤3的时间段期间,第二节点n72可初始化到vl |vth1| |vth2|。

[0187]

在步骤4的时间段期间,输入信号vi7可从高电压电平切换到低电压电平,且低电压电平与高电压电平之间的电压差可以是输入电压vin。由于第一电容器c71的第一端与第二端之间的电压差可维持恒定值,所以第一节点n71的电压可从vl |vth71|变为vl |vth71|-vin。然而,由于第一节点n71电连接到第二晶体管t72的第一端,所以第一节点n71的电压值可受第二晶体管t72约束。也就是说,在步骤4期间,第一节点n71的电压值可保持在vl |vth71|而非vl |vth71|-vin下。第二晶体管t72可接通。因此,不足电荷q'可基于电压差而充电到第一电容器c71中。不足电荷q'的值可等于c71

×

(-vin)。

[0188]

在实施例中,不足电荷q'可通过第二晶体管电流i_t72从第二电容器c72传递到第一电容器c71且由此可使第二电容器c72放电。也就是说,输出信号vo7的值可减小跨步电压vstep7的值,且跨步电压vstep7的值可等于(c71/c72)

×

vin。因此,输出信号vo7的值可从第一参考电压vh减小到vh-vstep7。

[0189]

在步骤5的时间段期间,输入信号vi7可从低电压电平切换到高电压电平,且低电压电平与高电压电平之间的电压差也可以是输入电压vin。由于第一电容器c71的第一端与第二端之间的电压差可维持恒定值,所以第一节点n71的电压可从vl |vth71|变为vl |vth71| vin。然而,由于第一节点n71电连接到第一晶体管t71的第二端,所以第一节点n71的电压值可受第一晶体管t71约束。也就是说,在步骤5期间,第一节点n71的电压值可保持在vl |vth71|而非vl |vth71| vin下,且第一晶体管t71可接通。因此,额外电荷q可基于电压差而通过第一晶体管电流i_t71从第一电容器c71放电且可等于(-q')。

[0190]

应注意,输出信号vo7的值可在步骤4的时间段期间减小跨步电压vstep7的值。也就是说,通过重复步骤4和步骤5,输出信号vo7的值可减小到多个不同值。此外,所述多个不同值与步骤4和步骤5的重复次数成正比。也就是说,各种波形可能够由电荷泵电路700输出,且输出是线性的。因此,电荷泵电路700可用作信号产生器。在一个实施例中,电荷泵电路700可用作显示装置的像素的扫描信号产生器以实施像素中扫描信号产生器。此外,由于电荷泵电路700的结构是简单的,所以电荷泵电路700可安置于衬底上且由此可实施像素中扫描信号产生器。

[0191]

图8是根据本公开的第四实施例的电荷泵电路的示意图。参考图1和图8,电荷泵电路800可具有与电荷泵电路100类似的结构。电荷泵电路800可包含第一晶体管t81、第二晶体管t82、第一电容器c81以及第二电容器c82。这些元件可称为电荷泵电路100且本文中不逐一地冗余地描述细节。

[0192]

在实施例中,电荷泵电路800可还包含第三晶体管t83、第四晶体管t84、第五晶体管t85、第六晶体管t86、第七晶体管t87、第八晶体管t88、第九晶体管t89以及第三电容器c83。在实施例中,第三晶体管t83可具有第一端和第二端。第三晶体管t83可电连接于第二晶体管t82的第二端与第二电容器c82的第一端之间。第三电容器c83可具有第一端和第二端。第三电容器c83的第一端可电连接到第二晶体管t82的控制端。第四晶体管t84可具有第一端和第二端。第四晶体管t84可电连接于第二晶体管t82的第二端与第三电容器c83的第一端之间。第五晶体管t85可具有第一端和第二端。第五晶体管t85可电连接于第四晶体管t84的第二端与第三电容器c83的第二端之间。第六晶体管t86可具有第一端和第二端。第六晶体管t86的第一端可电连接到第二电容器c82的第一端。第七晶体管t87可具有第一端和第二端。第七晶体管t87的第二端可电连接到第六晶体管t86的第二端。第八晶体管t88可具有第一端和第二端。第八晶体管t88的第一端可电连接到第七晶体管t87的第二端。第九晶体管t89可具有第一端和第二端。第九晶体管t89的第一端可电连接到第八晶体管t88的第二端。

[0193]

在实施例中,第一电容器c81的第二端可指示为第一节点n81,第三电容器c83的第一端可指示为第二节点n82,且第二电容器c82的第一端可指示为第三节点n83。在实施例中,第一晶体管t81可具有第一阈值电压vth81,第二晶体管t82可具有第二阈值电压vth82,且第八晶体管t88可具有第三阈值电压vth83。在实施例中,第一晶体管t81的第一端和第七晶体管t87的第一端接收第一参考电压vh。第二电容器c82的第二端和第九晶体管t89的第二端接收第二参考电压vl。第三电容器c83的第二端接收复位电压vrst8。

[0194]

在实施例中,第五晶体管t85的控制端可接收复位信号res8。在实施例中,第三晶体管t83的控制端和第四晶体管t84的控制端可接收第一补偿信号comp81。第六晶体管t86的控制端、第七晶体管t87的控制端以及第九晶体管t89的控制端可接收第二补偿信号comp82。在实施例中,第一电容器c81的第一端可接收输入信号vi8。第八晶体管t88的第二端可提供输出信号vo8。

[0195]

图9是根据本公开的第四实施例的电荷泵电路的示意性信号时序图。参考图8和图9,附图中的带圆圈数字可分别指示电荷泵电路800的操作的不同步骤。具有附图中的带圆圈数字的箭头可分别指示电荷泵电路800的操作的某一步骤期间的电流。朝向第一电容器c81的箭头可指示对第一电容器c81充电,且远离第一电容器c81的箭头可指示使第一电容器c81放电。在实施例中,步骤1和步骤2可指第二实施例的步骤1和步骤2,同时本文中不逐一地冗余地描述细节。在实施例中,复位信号res8、第一补偿信号comp81、第二补偿信号comp82可在步骤1、步骤2以及步骤3的时间段期间分别从低电压电平切换到高电压电平。因此,在步骤1的时间段期间,第一节点n81和第三节点n83可通过第二电容器电流i_c82复位到vh-|vth81|,第二节点n82可通过第五晶体管电流i_t85复位到复位电压vrst8,且输出信号vo8可通过第八晶体管步骤一电流i_t88_1复位到vh-|vth81|-|vth83|。在步骤2的时间段期间,第二节点n82可通过第四晶体管电流i_t84补偿到vh-|vth81|-|vth82|。在步骤3的时间段期间,第三节点n83可通过第六晶体管电流i_t86补偿到vl |vth83|,且输出信号vo8可通过第八晶体管步骤三电流i_t88_3和第九晶体管电流i_t89补偿到第二参考电压vl。

[0196]

在步骤4的时间段期间,输入信号vi8可从低电压电平切换到高电压电平,且低电压电平与高电压电平之间的电压差可以是输入电压vin。由于第一电容器c81的第一端与第

二端之间的电压差可维持恒定值,所以第一节点n81的电压可从vh-|vth81|变为vh-|vth81| vin。然而,由于第一节点n81电连接到第二晶体管t82的第一端,所以第一节点n81的电压值可受第二晶体管t82约束。也就是说,在步骤4的时间段期间,第一节点n81的电压值可保持在vh-|vth81|(图9中的n81的实线)而非vh-|vth81| vin(图9中的n81的虚线)下。第二晶体管t82和第三晶体管t83可接通。因此,额外电荷q可基于电压差而从第一电容器c81放电且可等于c81

×

vin。

[0197]

在实施例中,额外电荷q可通过第二晶体管电流i_t82和第三晶体管电流i_t83从第一电容器c81传递到第二电容器c82且由此可对第二电容器c82充电。此外,输出信号vo8的电压值可通过从第三节点n83的电压值减去第三阈值电压vth83获得。也就是说,输出信号vo8的值可增加跨步电压vstep8的值,且跨步电压vstep8的值可等于(c81/c82)

×

vin。因此,输出信号vo8的值可通过第八晶体管步骤四电流i_t88_4从第二参考电压vl增加到vl vstep8。

[0198]

在步骤5的时间段期间,输入信号vi8可从高电压电平切换到低电压电平,且低电压电平与高电压电平之间的电压差也可以是输入电压vin。由于第一电容器c81的第一端与第二端之间的电压差可维持恒定值,所以第一节点n81的电压可从vh-|vth81|变为vh-|vth81|-vin。然而,由于第一节点n81电连接到第一晶体管t81的第二端,所以第一节点n81的电压值可受第一晶体管t81约束。也就是说,在步骤5的时间段期间,第一节点n81的电压值可保持在vh-|vth81|而非vh-|vth81|-vin下,且第一晶体管t81可接通。因此,不足电荷q'可基于电压差而通过第一晶体管电流i_t81充电到第一电容器c81中且可等于(-q)。

[0199]

应注意,输出信号vo8的值可在步骤4期间增加跨步电压vstep8的值。也就是说,通过重复步骤4和步骤5,输出信号vo8的值可增加到多个不同值。此外,所述多个不同值与步骤4和步骤5的重复次数成正比。也就是说,各种波形可能够由电荷泵电路800输出,且输出是线性的。因此,电荷泵电路800可用作信号产生器。在一个实施例中,电荷泵电路800可用作显示装置的像素的扫描信号产生器以实施像素中扫描信号产生器。此外,由于电荷泵电路800的结构是简单的,所以电荷泵电路800可安置于衬底上且由此可实施像素中扫描信号产生器。

[0200]

在实施例中,第二晶体管t82是p型晶体管,但本公开不限于此。在实施例中,第二晶体管t82可提供第二电容器c82的充电电流(第二晶体管电流i_t82),且由此电荷泵电路800可以是升压电路。在另一实施例中,第二晶体管t82可以是n型晶体管,且由此可提供第二电容器c82的放电电流。因此,电荷泵电路800可变为降压电路。

[0201]

在实施例中,图3与图8之间的差异在于输出信号vo3可通过第二电容器c32的第一端提供,但输出信号vo8可通过第八晶体管t88的第二端提供。也就是说,输出信号vo8可取决于第八晶体管t88而非电容器。

[0202]

图10是根据本公开的第四实施例的修改的电荷泵电路的示意图。参考图8,图8与图10之间的主要差异在于电荷泵电路800的第二晶体管t82是p型晶体管且电荷泵1000的第二晶体管t102是n型晶体管。在实施例中,电荷泵电路1000可包含第一晶体管t101、第二晶体管t102、第一电容器c101以及第二电容器c102。这些元件可称为电荷泵电路100且本文中不逐一地冗余地描述细节。

[0203]

在实施例中,电荷泵电路1000可还包含第三晶体管t103、第四晶体管t104、第五晶

体管t105、第六晶体管t106、第七晶体管t107、第八晶体管t108、第九晶体管t109以及第三电容器c103。在实施例中,第三晶体管t103可具有第一端和第二端。第三晶体管t103可电连接于第二晶体管t102的第二端与第二电容器c102的第一端之间。第三电容器c103可具有第一端和第二端。第三电容器c103的第一端可电连接到第二晶体管t102的控制端。第四晶体管t104可具有第一端和第二端。第四晶体管t104可电连接于第二晶体管t102的控制端与第三晶体管t103的第一端之间。第五晶体管t105可具有第一端和第二端。第五晶体管t105可电连接于第四晶体管t104的第二端与第三电容器c103的第二端之间。第六晶体管t106可具有第一端和第二端。第六晶体管t106的第一端可电连接到第二电容器c102的第一端。第七晶体管t107可具有第一端和第二端。第七晶体管t107的第二端可电连接到第六晶体管t106的第二端。第八晶体管t108可具有第一端和第二端。第八晶体管t108的第一端可电连接到第七晶体管t107的第二端。第九晶体管t109可具有第一端和第二端。第九晶体管t109的第一端可电连接到第八晶体管t108的第二端。

[0204]

在实施例中,第一电容器c101的第二端可指示为第一节点n101,第三电容器c103的第一端可指示为第二节点n102,且第二电容器c102的第一端可指示为第三节点n103。在实施例中,第一晶体管t101可具有第一阈值电压vth101,第二晶体管t102可具有第二阈值电压vth102,且第八晶体管t108可具有第三阈值电压vth103。在实施例中,第一晶体管t101的第一端和第七晶体管t107的第一端接收第二参考电压vl。第二电容器c102的第二端和第九晶体管t109的第二端接收第一参考电压vh。第三电容器c103的第二端接收复位电压vrst10。

[0205]

在实施例中,第五晶体管t105的控制端可接收复位信号res10。在实施例中,第三晶体管t103的控制端和第四晶体管t104的控制端可接收第一补偿信号comp101。第六晶体管t106的控制端、第七晶体管t107的控制端以及第九晶体管t109的控制端可接收第二补偿信号comp102。在实施例中,第一电容器c101的第一端可接收输入信号vi10。第八晶体管t108的第一端可提供输出信号vo10。

[0206]

在实施例中,附图中的带圆圈数字可分别指示电荷泵电路1000的操作的不同步骤。具有附图中的带圆圈数字的箭头可分别指示电荷泵电路1000的操作的某一步骤期间的电流。朝向第一电容器c101的箭头可指示对第一电容器c101充电,且远离第一电容器c101的箭头可指示使第一电容器c101放电。

[0207]

在实施例中,步骤1和步骤2可指第二实施例的步骤1和步骤2,同时本文中不逐一地冗余地描述细节。在实施例中,复位信号res10、第一补偿信号comp101、第二补偿信号comp102可在步骤1、步骤2以及步骤3的时间段期间分别从高电压电平切换到低电压电平。因此,在步骤1的时间段期间,第一节点n101和第三节点n103可通过第二电容器电流i_c102复位到vl |vth101|,第二节点n102可通过第五晶体管电流i_t105复位到复位电压vrst10,且输出信号vo10可通过第八晶体管步骤一电流i_108_1复位到vl |vth01| |vth103|。在步骤2的时间段期间,第二节点n102可通过第四晶体管电流i_t104补偿到vl |vth101| |vth102|。在步骤3的时间段期间,第三节点n103可通过第六晶体管电流i_t106补偿到vh-|vth103|,且输出信号可通过第八晶体管步骤三电流i_t108_3和第九晶体管电流i_t109补偿到第一参考电压vh。

[0208]

在步骤4的时间段期间,输入信号vi10可从高电压电平切换到低电压电平,且低电

压电平与高电压电平之间的电压差可以是输入电压vin。由于第一电容器c101的第一端与第二端之间的电压差可维持恒定值,所以第一节点n101的电压可从vl |vth101|变为v1 |vth101|-vin。然而,由于第一节点n101电连接到第二晶体管t102的第一端,所以第一节点n101的电压值可受第二晶体管t102约束。也就是说,在步骤4期间,第一节点n101的电压值可保持在vl |vth101|而非vl |vth101|-vin下。第二晶体管t102和第三晶体管t103可接通。因此,不足电荷q可基于电压差而充电到第一电容器c101中且可等于c101

×

(-vin)。

[0209]

在实施例中,不足电荷q可通过第二晶体管电流i_t102和第三晶体管电流i_t103从第二电容器c102传递到第一电容器c101且由此可使第二电容器c102放电。此外,输出信号vo10的电压值可通过将第三阈值电压vth103相加到第三节点n103的电压值获得。也就是说,输出信号vo10的值可减小跨步电压vstep10的值,且跨步电压vstep10的值可等于(c101/c102)

×

vin。因此,输出信号vo10的值可从第二参考电压vl减小到vl-vstep10。

[0210]

在步骤5的时间段期间,输入信号vi10可从低电压电平切换到高电压电平,且低电压电平与高电压电平之间的电压差也可以是输入电压vin。由于第一电容器c101的第一端与第二端之间的电压差可维持恒定值,所以第一节点n101的电压可从vl |vth101|变为vl |vth101| vin。然而,由于第一节点n101电连接到第一晶体管t101的第二端,所以第一节点n101的电压值可受第一晶体管t101约束。也就是说,在步骤5的时间段期间,第一节点n101的电压值可保持在vl |vth101|而非vl |vth101| vin下且第一晶体管t101可接通。因此,额外电荷q'可基于电压差而通过第一晶体管电流i_t101从第一电容器c101放电且可等于(-q)。

[0211]

应注意,输出信号vo10的值可在步骤4的时间段期间减小跨步电压vstep10的值。也就是说,通过重复步骤4和步骤5,输出信号vo10的值可减小到多个不同值。此外,所述多个不同值与步骤4和步骤5的重复次数成正比。也就是说,各种波形可能够由电荷泵电路1000输出,且输出是线性的。因此,电荷泵电路1000可用作信号产生器。在一个实施例中,电荷泵电路1000可用作显示装置的像素的扫描信号产生器以实施像素中扫描信号产生器。此外,由于电荷泵电路1000的结构是简单的,所以电荷泵电路1000可安置于衬底上且由此可实施像素中扫描信号产生器。

[0212]

图11a是根据本公开的一个实施例的用于am-led显示面板的像素电路的示意性框图。参考图11a,像素电路1100可包含电荷泵电路1103、比较器1104、电流产生器1105、发光二极管1106、电容器1102以及扫描晶体管1101。在实施例中,电流产生器1105可接收第一参考电压vdd。电容器1102可具有第一端和第二端。扫描晶体管1101可具有第一端和第二端。电容器1102的第一端可电连接到扫描晶体管1101的第二端。电容器1102的第二端可接收第二参考电压vss。扫描晶体管1101的第一端可电连接到多个数据线的数据线data(m)。扫描晶体管1101的控制端可电连接到多条扫描线的扫描线scan(n)。比较器1104可具有正极端和负极端。扫描晶体管1101的第二端可电连接到比较器1104的正极端以提供脉冲宽度调制数据d_pwm。电荷泵电路1103可电连接到比较器1104的负极端以提供扫描信号sw。比较器1104的输出端可电连接到电流产生器1105以提供发射控制信号e_c。发光二极管1106可接收第二参考电压vss且电连接到电流产生器1105。

[0213]

图11b是根据本公开的一个实施例的用于am-led显示面板的像素电路的示意性信号时序图。参考图11a和图11b,比较器1104可配置成根据脉冲宽度调制数据d_pwm和扫描信

号sw来输出发射控制信号e_c。在实施例中,在发射时间段1110之前,比较器1104可配置成输出低电压电平,同时不存在扫描信号sw的输入。在发射时间段1110期间,比较器1104可配置成输出高电压电平,同时脉冲宽度调制数据d_pwm的值大于扫描信号sw的值。在发射时间段1110之后,比较器1104可配置成输出低电压电平,同时脉冲宽度调制数据d_pwm的值小于扫描信号sw的值。在实施例中,扫描信号sw可以是随时间增强的线性信号,且线性信号可具有特定斜率。在实施例中,电荷泵电路1103可由图1、图3、图5到图8以及图10的以上实施例的电荷泵电路100、电荷泵电路300、电荷泵电路500、电荷泵电路600、电荷泵电路700、电荷泵电路800、电荷泵电路1000中的一个实施。因此,所述特定斜率可由电荷泵电路1103的跨步电压确定。由于电荷泵电路1103的结构是简单的,所以电荷泵电路1103可安置于am-led显示面板的衬底上且由此可实施像素中扫描信号产生器。

[0214]

图12a是根据本公开的一个实施例的用于光子计数检测器的像素电路的示意性框图。参考图12a,用于光子计数检测器的像素电路可包含光检测器1201、脉冲整形器1202、第一比较器1203、第二比较器1204、第一计数器1205、第二计数器1206、第一扫描晶体管1207以及第二晶体管1208。在实施例中,光检测器1201可配置成检测光l且根据光l来产生光检测器电流i_pd。在实施例中,光l可以是用于计算机断层扫描的x射线,但本公开不限于此。

[0215]

在实施例中,脉冲整形器1202可配置成根据光检测器电流i_pd来产生输入信号1210。第一比较器1203可具有正极端和负极端。第二比较器1204可具有正极端和负极端。第一比较器1203的正极端和第二比较器1204的正极端可接收输入信号1210。第一比较器1203的负极端可接收第一参考信号ref1。第二比较器1204的负极端可接收第二参考信号ref2。第一比较器1203可配置成根据输入信号和第一参考信号ref1来输出第一比较信号1220。第二比较器1204可配置成根据输入信号和第二参考信号ref2来输出第二比较信号1230。

[0216]

在实施例中,第一计数器1205可配置成根据第一比较信号来输出第一计数信号1240。第二计数器1206可配置成根据第二比较信号来输出第二计数信号1250。第一扫描晶体管1207可具有第一端和第二端。第二扫描晶体管1208可具有第一端和第二端。第一扫描晶体管1207的控制端可电连接到多条扫描线的第一扫描线scan1(n)。第二扫描晶体管1208的控制端可电连接到多条扫描线的第二扫描线scan2(n)。第一扫描晶体管1207的第二端和第二扫描晶体管1208的第二端可电连接到多个感测线的感测线sense(m)。

[0217]

图12b是根据本公开的一个实施例的用于光子计数检测器的像素电路的比较器的示意性输入信号。图12c是根据本公开的一个实施例的用于光子计数检测器的像素电路的比较器的示意性输出信号。图12d是根据本公开的一个实施例的用于光子计数检测器的像素电路的计数器的示意性输出信号。参考图12a到图12d,脉冲整形器1202可配置成根据光检测器电流i_pd来产生输入信号1210。输入信号1210可通过第一比较器1203与第一参考信号ref1相比较以获得第一比较信号1220。输入信号1210可通过第二比较器1204与第二参考信号ref2相比较以获得第二比较信号1230。

[0218]

在实施例中,第一比较器1203和第二比较器1204可分别输出高电压电平,同时输入信号1210大于第一参考信号ref1或第二参考信号ref2的值。第一比较器1203和第二比较器1204可分别输出低电压电平,同时输入信号1210小于第一参考信号ref1或第二参考信号ref2的值。

[0219]

在实施例中,输入信号1210的峰值仅存在大于第一参考信号ref1的值的一个值。

因此,第一比较信号1220可包含一个方形波。在实施例中,输入信号1210的峰值存在大于第二参考信号ref2的值的三个值。因此,第二比较信号1230可包含三个方形波。也就是说,第一比较信号1220的方形波的数目和第二比较信号1230的方形波的数目分别根据输入信号1210、第一参考信号ref1以及第二参考信号ref2来确定。

[0220]

在实施例中,第一计数器1205和第二计数器1206可分别由图1、图3、图5到图8以及图10的以上实施例的电荷泵电路100、电荷泵电路300、电荷泵电路500、电荷泵电路600、电荷泵电路700、电荷泵电路800以及电荷泵电路1000中的一个实施。第一计数器1205可配置成根据第一比较信号1220的方形波的数目来输出第一计数信号1240。第二计数器1206可配置成根据第二比较信号1230的方形波的数目来输出第二计数信号1250。因此,像素电路1200可检测光l的相片的数目,且可实施像素中光计数检测器。

[0221]

图13是根据本公开的一个实施例的任意波形产生器的示意图。参考图13,任意波形产生器1300可包含第一上调晶体管(up transistor)t_u1、第二上调晶体管t_u2、第一下调晶体管(down transistor)t_d1、第二下调晶体管t_d2、复位晶体管t13r、第一上调电容器(up capacitor)c1u、第一下调电容器(down capacitor)c1d以及第二电容器c132。在实施例中,第一上调晶体管t_u1可具有第一端和第二端。第二上调晶体管t_u2可具有第一端和第二端。

[0222]

第一下调晶体管t_d1可具有第一端和第二端。第二下调晶体管t_d2可具有第一端和第二端。复位晶体管t13r可具有第一端和第二端。第一上调电容器c1u可具有第一端和第二端。第一下调电容器c1d可具有第一端和第二端。第二电容器c132可具有第一端和第二端。

[0223]

在实施例中,第一上调电容器c1u的第一端可接收输入上调信号(input up signal)viu。第一上调电容器c1u的第二端可电连接到第一上调晶体管t_u1的第二端。第一上调晶体管t_u1的第一端和控制端可接收第一参考电压vh。第二上调晶体管t_u2的第一端可电连接到第一上调晶体管t_u1的第二端。第二上调晶体管t_u2的控制端可接收第一参考电压vh。第二上调晶体管t_u2的第二端可电连接到第二电容器c132的第一端。

[0224]

在实施例中,第一下调电容器c1d的第一端可接收输入下调信号(input down signal)vid。第一下调电容器c1d的第二端可电连接到第一下调晶体管t_d1的第一端。第一下调晶体管t_d1的第二端和控制端可接收第二参考电压vl。第二下调晶体管t_d2的第一端可电连接到第一下调晶体管t_d1的第一端。第二上调晶体管t_d2的控制端可接收第二参考电压vl。第二下调晶体管t_d2的第二端可电连接到第二电容器c132的第一端。第二电容器c132的第一端可提供输出信号vo13。在实施例中,复位晶体管t13r的第一端可接收复位电压vrst13。复位晶体管t13r的控制端可接收复位信号res13。复位晶体管t13r的第二端可提供输出信号vo13。

[0225]

参考图1和图13,第一上调晶体管t_u1、第二上调晶体管t_u2、复位晶体管t13r、第一上调电容器c1u以及第二电容器c132可形成升压电路作为图1的电荷泵电路100。第一下调晶体管t_d1、第二下调晶体管t_d2、复位晶体管t13r、第一下调电容器c1d以及第二电容器c132可形成降压电路。也就是说,输出信号vo13可根据输入上调信号viu和输入下调信号vid而包含多个升压信号和多个降压信号。通过改变输入上调信号viu和输入下调信号vid的组合,可获得各种输出信号vo13。因此,任意波形产生器1300可输出任意波形。

[0226]

总之,根据本公开的电荷泵电路,通过电荷泵电路的以上电路设计,电荷泵可根据输入信号来输出多个波形且电荷泵的输出是线性的。此外,由于电荷泵电路的结构是简单的,所以电荷泵电路可安置于am-led显示面板的衬底上,且由此可实施像素中扫描信号产生器。

[0227]

本领域的技术人员将显而易见,在不脱离本公开的范围或精神的情况下,可对所公开的实施例进行各种修改和变化。鉴于前述内容,希望本公开涵盖属于所附权利要求和其等效物的范围内的本公开的修改和变化。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。