1.本文涉及但不限于显示技术领域,尤其涉及一种移位寄存器、栅极驱动电路及显示装置。

背景技术:

2.阵列基板行驱动(gate driver on array,简称goa)技术将薄膜晶体管(thin film transistor,简称tft)栅极开关电路集成在显示面板的阵列基板上以形成对显示面板的驱动,从而可以省去集成电路(integrated circuit,简称ic)的绑定(bonding)区域以及扇出(fan-out)区域的布线空间,从而实现窄边框。

3.氧化物薄膜晶体管由于材料透明以及制作工艺相对简单、工艺温度低受到越来越多的关注。针对氧化物薄膜晶体管,需要设计新的goa电路以适应氧化物薄膜晶体管载流子迁移率较低的特点。

技术实现要素:

4.第一方面,本公开提供了一种移位寄存器,包括:输入模块、第一输出模块、第二输出模块、第一控制模块、第二控制模块、第三控制模块、第四控制模块和储能模块;

5.输入模块,与输入信号端、第一时钟信号端和第二节点连接,配置为在第一时钟信号端的第一时钟信号的控制下将输入信号端的输入信号提供给第二节点;

6.第一输出模块,与第一电源信号端、第二节点和输出信号端连接,配置为在第二节点的电压控制下将第一电源信号端的第一电源信号提供给输出信号端;

7.第二输出模块,与第二电源信号端、第一节点和输出信号端连接,配置为在第一节点的电压控制下将第二电源信号端的第二电源信号提供给输出信号端;

8.第一控制模块,与第二电源信号端、第二节点和第一节点连接,配置为在第二节点的电压控制下将第二电源信号端的第二电源信号提供给第一节点;

9.第二控制模块,与第一时钟信号端、第三节点和第一节点连接,配置为在第三节点的电压控制下将第一时钟信号端的第一时钟信号提供给第一节点;

10.第三控制模块,与输入信号端、第二电源信号端、第二时钟信号端和第三节点连接,配置为在输入信号端的输入信号控制下将第二电源信号端的第二电源信号提供给第三节点,在第二时钟信号端的第二时钟信号的控制下将第二电源信号端的第二电源信号提供给第三节点;

11.第四控制模块,与第一电源信号端、第一时钟信号端、第二电源信号端、第二时钟信号端和第四节点连接,配置为在第一时钟信号端的第一时钟信号控制下将第一电源信号端的第一电源信号提供给第四节点,在第二时钟信号端的第二时钟信号的控制下将第二电源信号端的第二电源信号提供给第四节点;

12.储能模块,包括第一电容,所述第一电容的两端分别与第三节点和第四节点连接。

13.第二方面,本公开提供了一种栅极驱动电路,包括n个级联的移位寄存器sr(i);第

k个移位寄存器sr(k)的输出信号端与第k 1个移位寄存器sr(k 1)的输入信号端连接;1≤k≤n-1,n》1;n个移位寄存器中至少一个移位寄存器sr(i)采用上述移位寄存器;1≤i≤n。

14.第三方面,本公开提供了一种显示装置,包括上述栅极驱动电路。

15.本公开实施例提供了一种移位寄存器、栅极驱动电路及显示装置,移位寄存器包括输入模块、第一输出模块、第二输出模块、第一控制模块、第二控制模块、第三控制模块、第四控制模块和储能模块;输入模块将输入信号端的输入信号提供给第二节点,第一输出模块在第二节点的电压控制下将第一电源信号端的第一电源信号提供给输出信号端,第二输出模块在第一节点的电压控制下将第二电源信号端的第二电源信号提供给输出信号端,第一控制模块和第二控制模块控制第一节点的电压,第三控制模块控制第三节点的电压,第四控制模块控制第四节点的电压,通过四个控制模块和储能模块的配合能够使得节点电位及时跳变,从而输出波形满足要求的脉冲信号。

附图说明

16.附图用来提供对本公开技术方案的理解,并且构成说明书的一部分,与本公开的实施例一起用于解释本公开的技术方案,并不构成对本公开技术方案的限制。

17.图1为本公开实施例提供的一种移位寄存器的结构示意图;

18.图2为本公开实施例提供的一种移位寄存器的等效电路示意图;

19.图3为本公开实施例提供的另一种移位寄存器的等效电路示意图(包括第二电容和第三电容);

20.图4为本公开实施例提供的另一种移位寄存器的等效电路示意图(包括第十晶体管);

21.图5为本公开实施例提供的一种移位寄存器的信号时序图;

22.图6为本公开实施例提供的一种栅极驱动电路的级联结构示意图。

具体实施方式

23.为使本公开的目的、技术方案和优点更加清楚明白,下文中将结合附图对本公开的实施例进行详细说明。注意,实施方式可以以多个不同形式来实施。所属技术领域的普通技术人员可以很容易地理解一个事实,就是方式和内容可以在不脱离本公开的宗旨及其范围的条件下被变换为各种各样的形式。因此,本公开不应该被解释为仅限定在下面的实施方式所记载的内容中。在不冲突的情况下,本公开中的实施例及实施例中的特征可以相互任意组合。

24.在附图中,有时为了明确起见,夸大表示了各构成要素的大小、层的厚度或区域。因此,本公开的一个方式并不一定限定于该尺寸,附图中各部件的形状和大小不反映真实比例。此外,附图示意性地示出了理想的例子,本公开的一个方式不局限于附图所示的形状或数值等。

25.本说明书中的“第一”、“第二”、“第三”等序数词是为了避免构成要素的混同而设置,而不是为了在数量方面上进行限定的。

26.在本说明书中,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解。例如,可以是固定连接,或可拆卸连接,或一体地连接;可以是机械连接,或电连接;

可以是直接相连,或通过中间件间接相连,或两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本公开中的具体含义。

27.在本说明书中,晶体管是指至少包括栅极、漏极以及源极这三个端子的元件。晶体管的源极、漏极是对称的,在使用极性相反的晶体管的情况或电路工作中的电流方向变化的情况等下,“源极”及“漏极”的功能有时互相调换。在本公开实施例中,将源极和漏极中的一个称为第一极,将源极和漏极中的另一个称为第二极,栅极称为控制极。

28.在本说明书中,“电连接”包括构成要素通过具有某种电作用的元件连接在一起的情况。“具有某种电作用的元件”只要可以进行连接的构成要素间的电信号的授受,就对其没有特别的限制。“具有某种电作用的元件”的例子不仅包括电极和布线,而且还包括晶体管等开关元件、电阻器、电感器、电容器、其它具有各种功能的元件等。

29.在以下示例中以驱动晶体管为n型薄膜晶体管的情况进行描述,其他晶体管根据电路设计与驱动晶体管具有相同或不同的类型。类似地,在其他实施例中,驱动晶体管也可以被示为p型薄膜晶体管。本领域技术人员能够理解的是,通过将其他晶体管的类型相应地改变并将各驱动信号和电平信号进行反相(和/或进行其他附加的适应性修改),同样能够实现本公开的技术方案。

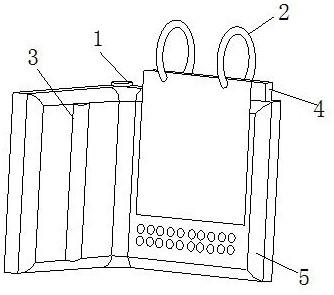

30.本公开实施例提供了一种移位寄存器,如图1所示,本公开实施例提供的一种移位寄存器,包括:输入模块10、第一输出模块20、第二输出模块30、第一控制模块40、第二控制模块50、第三控制模块60、第四控制模块70和储能模块80;

31.输入模块,与输入信号端in、第一时钟信号端ck1和第二节点n2连接,配置为在第一时钟信号端的第一时钟信号的控制下将输入信号端的输入信号提供给第二节点;

32.第一输出模块,与第一电源信号端vgh、第二节点n2和输出信号端out连接,配置为在第二节点的电压控制下将第一电源信号端的第一电源信号提供给输出信号端;

33.第二输出模块,与第二电源信号端vgl、第一节点n1和输出信号端out连接,配置为在第一节点的电压控制下将第二电源信号端的第二电源信号提供给输出信号端;

34.第一控制模块,与第二电源信号端vgl、第二节点n2和第一节点n1连接,配置为在第二节点的电压控制下将第二电源信号端的第二电源信号提供给第一节点;

35.第二控制模块,与第一时钟信号端ck1、第三节点n3和第一节点n1连接,配置为在第三节点的电压控制下将第一时钟信号端的第一时钟信号提供给第一节点;

36.第三控制模块,与输入信号端in、第二电源信号端vgl、第二时钟信号端ck2和第三节点n3连接,配置为在输入信号端的输入信号控制下将第二电源信号端的第二电源信号提供给第三节点,在第二时钟信号端的第二时钟信号的控制下将第二电源信号端的第二电源信号提供给第三节点;

37.第四控制模块,与第一电源信号端vgh、第一时钟信号端ck1、第二电源信号端vgl、第二时钟信号端ck2和第四节点n4连接,配置为在第一时钟信号端的第一时钟信号控制下将第一电源信号端的第一电源信号提供给第四节点,在第二时钟信号端的第二时钟信号的控制下将第二电源信号端的第二电源信号提供给第四节点;

38.储能模块,包括第一电容c1,所述第一电容的两端分别与第三节点和第四节点连接。

39.上述实施例提供的移位寄存器包括输入模块、第一输出模块、第二输出模块、第一

控制模块、第二控制模块、第三控制模块、第四控制模块和储能模块;输入模块将输入信号端的输入信号提供给第二节点,第一输出模块在第二节点的电压控制下将第一电源信号端的第一电源信号提供给输出信号端,第二输出模块在第一节点的电压控制下将第二电源信号端的第二电源信号提供给输出信号端,第一控制模块和第二控制模块控制第一节点的电压,第三控制模块控制第三节点的电压,第四控制模块控制第四节点的电压,通过四个控制模块和储能模块的配合能够使得节点电位及时跳变,缩短输出的脉冲信号的上升沿和下降沿的时间,使得输出波形满足要求。

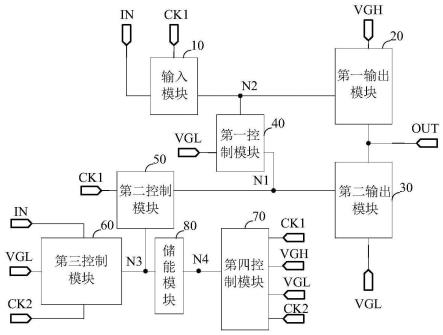

40.图2提供了一种移位寄存器的等效电路图。

41.如图2所示,在一些示例性的实施方式中,所述输入模块包括第一晶体管t1,所述第一晶体管的控制极连接第一时钟信号端,所述第一晶体管的第一极连接输入信号端,所述第一晶体管的第二极连接第二节点。

42.如图2所示,在一些示例性的实施方式中,所述第一输出模块包括第二晶体管t2,所述第二晶体管的控制极连接第二节点,所述第二晶体管的第一极连接第一电源信号端,所述第二晶体管的第二极连接输出信号端。

43.如图2所示,在一些示例性的实施方式中,所述第二输出模块包括第三晶体管t3,所述第三晶体管的控制极连接第一节点,所述第三晶体管的第一极连接第二电源信号端,所述第三晶体管的第二极连接输出信号端。

44.如图2所示,在一些示例性的实施方式中,所述第一控制模块包括第四晶体管t4,所述第四晶体管的控制极连接第二节点,所述第四晶体管的第一极连接第二电源信号端,所述第四晶体管的第二极连接第一节点。

45.如图2所示,在一些示例性的实施方式中,所述第二控制模块包括第五晶体管t5,所述第五晶体管的控制极连接第三节点,所述第五晶体管的第一极连接第一时钟信号端,所述第五晶体管的第二极连接第一节点。

46.如图2所示,在一些示例性的实施方式中,所述第三控制模块包括第六晶体管和第七晶体管,所述第六晶体管的控制极连接输入信号端,所述第六晶体管的第一极连接第二电源信号端,所述第六晶体管的第二极连接第三节点,所述第七晶体管的控制极连接第二时钟信号端,所述第七晶体管的第一极连接第二电源信号端,所述第七晶体管的第二极连接第三节点。

47.如图2所示,在一些示例性的实施方式中,所述第四控制模块包括第八晶体管和第九晶体管,所述第八晶体管的控制极连接第一时钟信号端,所述第八晶体管的第一极连接第一电源信号端,所述第八晶体管的第二极连接第四节点,所述第九晶体管的控制极连接第二时钟信号端,所述第九晶体管的第一极连接第二电源信号端,所述第九晶体管的第二极连接第四节点。

48.图3提供了另一种移位寄存器的等效电路图。

49.如图3所示,在一些示例性的实施方式中,所述第一输出模块还包括第二电容c2,所述第二电容的一端与第二晶体管的控制极连接,所述第二电容的另一端与第二晶体管的第二极连接。第二电容跨接在第二晶体管的控制极和第二极之间,能够稳定第二晶体管的控制极的电位。

50.如图3所示,在一些示例性的实施方式中,所述第二输出模块还包括第三电容c3,

所述第三电容的一端与第三晶体管的控制极连接,所述第三电容的另一端与第三晶体管的第一极连接。第三电容跨接在第三晶体管的控制极和第一极之间,能够稳定第三晶体管的控制极的电位。

51.图4提供了另一种移位寄存器的等效电路图。

52.如图4所示,在一些示例性的实施方式中,所述第一输出模块还包括第十晶体管t10,所述第十晶体管的控制极连接第一电源信号端,所述第十晶体管的第一极连接第二节点,所述第十晶体管的第二极连接第二晶体管的控制极。在第二节点和第二晶体管的控制极之间设置第十晶体管,能够稳定第二晶体管的控制极的电位。

53.在一些示例性的实施方式中,所述移位寄存器中所有的晶体管为n型晶体管。

54.在一些示例性的实施方式中,当所述移位寄存器中所有的晶体管为n型晶体管时,所述移位寄存器的一个工作周期包括以下多个时段:第一时段、第二时段、第三时段、第四时段和多次交替出现的第五时段和第六时段;

55.第一电源信号和第二电源信号为直流信号,第一电源信号为高电平信号,第二电源信号为低电平信号,输入信号为脉冲信号,第一时钟信号和第二时钟信号为周期性脉冲信号;输入信号在第一时段和第二时段为高电平信号,在其他时段为低电平信号;第一时钟信号在第一时段、第三时段和第五时段为低电平信号,在第二时段、第四时段和第六时段为高电平信号;第二时钟信号在第一时段、第三时段和第五时段为高电平信号,在第二时段、第四时段和第六时段为低电平信号。

56.在一些示例性的实施方式中,所述移位寄存器中所有的晶体管为氧化物薄膜晶体管。氧化物薄膜晶体管的载流子迁移率较低,通过四个控制模块和储能模块的配合能够使得节点电位及时跳变,缩短输出的脉冲信号的上升沿和下降沿的时间,使得输出波形满足要求。

57.下面结合信号时序图对移位寄存器的工作过程进行说明。

58.图5提供了移位寄存器的信号时序图。移位寄存器采用图2至图4中任意一种结构,所有的晶体管都是n型晶体管,第一电源信号端提供第一电源信号,第二电源信号端提供第二电源信号,第一时钟信号端提供第一时钟信号,第二时钟信号端提供第二时钟信号,输入信号端提供输入信号,输出信号端提供输出信号。第一电源信号和第二电源信号为直流信号,输入信号为脉冲信号,第一时钟信号和第二时钟信号为周期性脉冲信号,第一时钟信号和第二时钟信号相位相反。

59.对于n型晶体管,当晶体管栅极(控制极)的电压高于开启电压时,晶体管导通,当晶体管栅极的电压低于开启电压时,晶体管处于截止状态。高电平信号为高于晶体管开启电压的信号,低电平信号为低于晶体管开启电压的信号。第一电源信号为高电平信号,第二电源信号为低电平信号。

60.移位寄存器的一个工作周期可以包括多个时段:第一时段(t1)、第二时段(t2)、第三时段(t3)、第四时段(t4)和多次交替出现的第五时段(t5)与第六时段(t6)。

61.(一)第一时段(t1时段)

62.输入信号为高电平信号,第一时钟信号为低电平信号,第二时钟信号为高电平信号。

63.第一时钟信号为低电平信号,第一晶体管截止,第二节点保持上一个时段(t5)的

电位,上一个时段的电位为低电平。第二节点的电位为低电平,第二晶体管截止。

64.输入信号为高电平信号,第六晶体管导通,第二电源信号提供给第三节点。第二时钟信号为高电平信号,第七晶体管导通,第二电源信号提供给第三节点。第二电源信号为低电平信号,所以第三节点的电位为低电平。

65.第一时钟信号为低电平信号,第八晶体管截止。第二时钟信号为高电平信号,第九晶体管导通,第二电源信号提供给第四节点。第二电源信号为低电平信号,所以第四节点的电位为低电平。

66.第二节点为低电平,第四晶体管截止。第三节点为低电平,第五晶体管截止。第一节点n1保持上一个时段(t5)的电位,上一个时段的电位为高电平。

67.第一节点的电位为高电平,第三晶体管导通,第二电源信号提供给输出信号端。第二电源信号为低电平信号,所以输出信号端输出的输出信号为低电平信号。当第三电容跨接在第三晶体管的控制极和第一极之间时,第一节点给第三电容充电。

68.(二)第二时段(t2时段)

69.输入信号为高电平信号,第一时钟信号为高电平信号,第二时钟信号为低电平信号。

70.第一时钟信号为高电平信号,第一晶体管导通,输入信号提供给第二节点。输入信号为高电平信号,第二节点的电位从低电平跳变为高电平,第二晶体管从截止变为导通,第一电源信号提供给输出信号端。第一电源信号为高电平信号,所以输出信号端输出的输出信号从低电平跳变为高电平。

71.输入信号为高电平信号,第六晶体管导通,第二电源信号提供给第三节点。第二时钟信号为低电平信号,第七晶体管截止。第二电源信号为低电平信号,所以第三节点的电位继续保持低电平。

72.第一时钟信号为高电平信号,第八晶体管导通,第一电源信号提供给第四节点。第二时钟信号为低电平信号,第九晶体管截止。第一电源信号为高电平信号,所以第四节点的电位为高电平。第四节点的电位为高电平,第三节点的电位为低电平,第四节点给第一电容充电。

73.第二节点为高电平,第四晶体管导通,第二电源信号提供给第一节点。第三节点为低电平,第五晶体管截止。由于第二电源信号为低电平信号,所以第一节点的电位从高电平跳变为低电平,第三晶体管从导通变为截止。第三节点的电位保持低电平能够使得第五晶体管可靠地保持截止状态,使得第一节点的电位跳变仅受第二节点的影响,第二节点电位的跳变使得第三晶体管截止和第二晶体管导通同步,缩短了输出信号的电压上升时间。

74.(三)第三时段(t3时段)

75.输入信号为低电平信号,第一时钟信号为低电平信号,第二时钟信号为高电平信号。

76.第一时钟信号为低电平信号,第一晶体管截止。第二节点保持上一个时段(t2)的电位,上一个时段的电位为高电平。第二节点的电位为高电平,第二晶体管继续保持导通,输出信号端输出的输出信号继续维持高电平。当第二电容跨接在第二晶体管的控制极和第二极之间时,第二电容能够保持第二节点的高电平。

77.输入信号为低电平信号,第六晶体管截止。第二时钟信号为高电平信号,第七晶体

管导通,第二电源信号提供给第三节点。第二电源信号为低电平信号,所以第三节点的电位继续保持低电平。

78.第一时钟信号为低电平信号,第八晶体管截止。第二时钟信号为高电平信号,第九晶体管导通,第二电源信号提供给第四节点。第二电源信号为低电平信号,所以第四节点的电位为低电平。

79.第二节点的电位继续保持高电平,第四晶体管继续保持导通。第三节点的电位继续保持低电平,第五晶体管继续保持截止。第一节点的电位继续保持低电平,第三晶体管继续保持截止。

80.(四)第四时段(t4时段)

81.输入信号为低电平信号,第一时钟信号为高电平信号,第二时钟信号为低电平信号。

82.第一时钟信号为高电平信号,第一晶体管导通,输入信号提供给第二节点。输入信号为低电平信号,第二节点的电位从高电平跳变为低电平,第二晶体管从导通变为截止。

83.输入信号为低电平信号,第六晶体管截止。第二时钟信号为低电平信号,第七晶体管截止。

84.第一时钟信号为高电平信号,第八晶体管导通,第一电源信号提供给第四节点。第二时钟信号为低电平信号,第九晶体管截止。第一电源信号为高电平信号,所以第四节点的电位从低电平变为高电平。第四节点的电位从低电平跳变为高电平,在第一电容的作用下,第三节点的电位跟随第四节点的电位发生跳变,从低电平跳变为高电平。

85.第二节点为低电平,第四晶体管截止。第三节点为高电平,第五晶体管导通,第一时钟信号提供给第一节点。由于第一时钟信号为高电平信号,所以第一节点的电位从低电平跳变为高电平,第三晶体管从截止变为导通,第二电源信号提供给输出信号端。第二电源信号为低电平信号,所以输出信号端输出的输出信号从高电平跳变为低电平。当第三电容跨接在第三晶体管的控制极和第一极之间时,第一节点给第三电容充电。

86.第四时段之后,第五时段和第六时段多次交替出现直至本工作周期结束。

87.(五)第五时段(t5时段)

88.输入信号为低电平信号,第一时钟信号为低电平信号,第二时钟信号为高电平信号。

89.第一时钟信号为低电平信号,第一晶体管截止。第二节点保持上一个时段(t4)的电位,上一个时段的电位为低电平。第二节点的电位为低电平,第二晶体管继续保持截止。

90.输入信号为低电平信号,第六晶体管截止。第二时钟信号为高电平信号,第七晶体管导通,第二电源信号提供给第三节点。第二电源信号为低电平信号,所以第三节点的电位从高电平跳变为低电平。

91.第一时钟信号为低电平信号,第八晶体管截止。第二时钟信号为高电平信号,第九晶体管导通,第二电源信号提供给第四节点。第二电源信号为低电平信号,所以第四节点的电位为低电平。

92.第二节点的电位继续保持低电平,第四晶体管继续保持截止。第三节点的电位从高电平跳变为低电平,第五晶体管从导通变为截止。第一节点的电位保持上一个时段(t4)的电位,上一个时段的电位为高电平。第一节点的电位为高电平,第二晶体管继续保持导

通,输出信号端的输出信号保持低电平。

93.(六)第六时段(t6时段)

94.输入信号为低电平信号,第一时钟信号为高电平信号,第二时钟信号为低电平信号。

95.第一时钟信号为高电平信号,第一晶体管导通,输入信号提供给第二节点。输入信号为低电平信号,第二节点的电位保持低电平,第二晶体管继续保持截止。

96.输入信号为低电平信号,第六晶体管截止。第二时钟信号为低电平信号,第七晶体管截止。

97.第一时钟信号为高电平信号,第八晶体管导通,第一电源信号提供给第四节点。第二时钟信号为低电平信号,第九晶体管截止。第一电源信号为高电平信号,所以第四节点的电位从低电平跳变为高电平。第四节点的电位从低电平跳变为高电平,在第一电容的作用下,第三节点的电位跟随第四节点的电位发生跳变,从低电平跳变为高电平。

98.第三节点为高电平,第五晶体管导通,第一时钟信号提供给第一节点。由于第一时钟信号为高电平信号,所以第一节点的电位继续保持高电平,第三晶体管继续保持导通,输出信号端的输出信号继续保持低电平。

99.如图6所示,本公开实施例还提供了一种栅极驱动电路,包括n个级联的移位寄存器sr(i);第k个移位寄存器sr(k)的输出信号端与第k 1个移位寄存器sr(k 1)的输入信号端连接;1≤k≤n-1,n》1;n个移位寄存器中至少一个移位寄存器sr(i)采用上述实施例中的移位寄存器;1≤i≤n。

100.上述栅极驱动电路可以和显示面板的像素驱动电路连接,用于向像素驱动电路提供各种控制信号,比如:行扫描信号、复位信号等。

101.所述显示面板包括:有机发光二极管(organic light-emitting diode,简称:oled)显示面板。

102.本公开实施例还提供了一种显示装置,包括上述栅极驱动电路。

103.所述显示装置可以为:手机、平板电脑、电视机、显示器、笔记本电脑、数码相框、导航仪等任何具有显示功能的产品或部件。对于该显示装置的其它必不可少的组成部分均为本领域的普通技术人员应该理解具有的,在此不做赘述,也不应作为对本发明的限制。

104.虽然本技术所揭露的实施方式如上,但所述的内容仅为便于理解本技术而采用的实施方式,并非用以限定本发明。任何本发明所属领域内的技术人员,在不脱离本发明所揭露的精神和范围的前提下,可以在实施的形式及细节上进行任何的修改与变化,但本发明的专利保护范围,仍须以所附的权利要求书所界定的范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。