基于存储单元环的时间数字转换器

背景技术:

1.在一些电子系统中,数字电路经布置以控制及/或测量各种电子电路(例如模拟电路)的电量。在一些此类电子电路中,测量电子信号的时序信息且将其转换为数值。测量可用于控制及/或监测被测量的电子信号的产生时序。此类测量及转换的稳定性、分辨率及速度受用于转换中的各种组件的大小、速度及功耗限制。

技术实现要素:

2.在所描述的实例中,一种存储单元环包含圆耦合存储单元。每一存储单元包含:相应电容器,其用于响应于选择相应存储单元的相应持续时间而产生相应积分电压;相应阈值转换器,其用于产生用于指示所述相应积分电压是否已穿越阈值的相应阈值信号;及相应选择电路系统,其经配置以响应于由相应相邻存储单元产生的选择信号而产生相应选择信号。所述环经耦合到用于响应于所述所产生的相应积分电压及相应选择信号而产生转换值的模拟量化器。所述环经耦合到用于响应于至少一些所述相应阈值信号的值变化而产生循环计数值的循环计数器。所述转换值及所述循环计数值可包括时间测量。

附图说明

3.图1是展示基于双向存储单元环的时间数字转换器(tdc)的实例的系统图,其包含用于分别产生所得转换的较低有效位及较高有效位的模/数转换器及循环计数器。

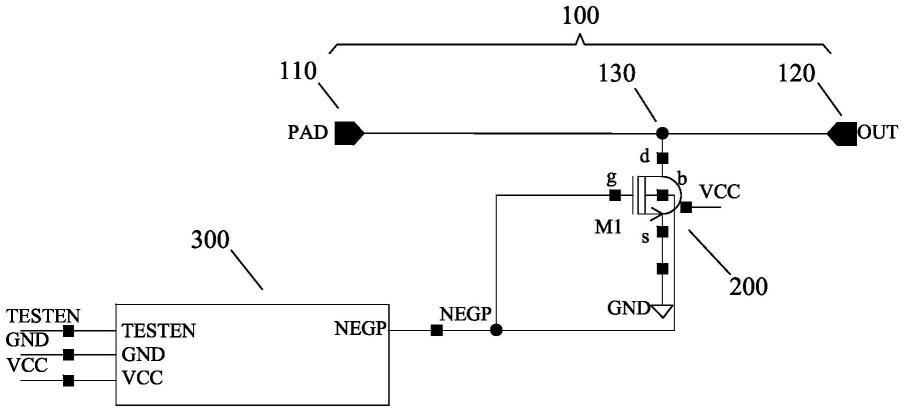

4.图2是展示时间数字转换器(tdc)的实例双向存储单元的系统图。

5.图3是实例六存储单元环的实例双向操作的波形图。

6.图4是展示耦合到相位频率检测器(pfd)的实例基于双向存储单元环的时间数字转换器(tdc)的系统图。

7.图5a及图5b是包含响应于循环计数器的操作而产生的实例值的列的实例图。

8.图6是实例基于双向存储单元环的时间数字转换器(tdc)的实例模拟取样电路的示意图。

9.图7是包含图4的实例系统的实例模拟的波形的波形图。

10.图8是包含图7在较小比例下的实例模拟的波形的波形图。

11.图9是包含图4的实例系统的实例双取样模拟的波形的波形图。

12.图10是包含图9在较小比例下的实例模拟的波形的波形图。

13.图11是用于图4的实例系统的时间数字转换的实例方法的流程图。

具体实施方式

14.在图式中,相同参考元件符号指代相同元件,且各种特征不一定按比例绘制。

15.各种电子电路包含用于将时域信号转换为阈值信号(例如,其可包含至少一个数值、代码、数目或值)的模/数转换器。此类电路可用于各种终端用户应用(例如秒表、信号调节及反馈控制)中。本文中描述的技术可应用于几乎任何此终端用户应用。一个此应用包含

至少一个数字锁相环(pll)电路,其中pll的振荡频率与参考信号的频率比较,至少一个反馈信号响应于参考信号的量而产生,且pll的振荡响应于反馈信号而控制。pll的振荡可经控制以便与参考信号的频率匹配(例如,锁定到参考信号的频率上)。

16.数字pll包含时间数字转换器(tdc)。tdc可经配置以转换参考时钟与反馈时钟之间的时间或相位差(例如,响应于反馈信号的先前值而产生)。时间或相位差经转换为对应数字代码。数字代码经计算处理以产生反馈信号。反馈信号由产生反馈时钟的振荡器输入。振荡器经配置以响应于反馈信号而调谐振荡器的频率(例如,使得反馈时钟是由反馈信号控制的反馈控制时钟,且使得反馈时钟被锁定到参考时钟上)。

17.tdc适于接收输出参考时钟与反馈控制时钟之间的相位关系(例如相位偏移)的指示。参考时钟与反馈控制时钟之间的相位关系的指示包含开始时间的指示及停止时间的指示。响应于相位关系的指示,tdc适于将模拟域中表示的两个事件(例如参考时钟的上升或下降沿及反馈控制时钟的上升或下降沿)之间的时间差转换为数字域中的离散值。例如,时间可经测量为无限小模拟域内的近似值且由tdc转换为数字代码。特定种类的tdc的性能可使特定种类的tdc适于或不适于特定终端用户应用。

18.tdc的性能(例如准确度、速度或分辨率)经受操作上受由tdc包含的技术及架构限制。在第一实例中,tdc的分辨率(例如时间分辨率)受限于用于切换对应于输入相位误差(例如存在于参考时钟与反馈时钟之间的相位误差)的计数器的时钟(例如高速时钟)的时段。在其中tdc包含模/数转换器(adc)的第二实例中,分辨率(例如电压分辨率)受限于adc的分辨率,adc适于将输入相位误差电压转换(例如,取样)为数字代码(例如,输入相位误差可由pfd电荷泵转换为对应电压)。

19.如本文中描述,实例tdc包含8级双向存储单元环(bdscr)。bdscr可在第一方向(例如顺时针,cw)或第二方向(例如逆时针,ccw)上振荡(例如,传播振荡)。bdscr适于响应于输入相位误差而在cw或ccw方向上振荡,使得在对应于输入相位误差的持续时间内维持bdscr振荡的方向。bdscr振荡包含“环沿”(下文关于图5a及图5b描述),其指示在bdscr内的循环中数字传播的振荡信号的前沿。

20.在bdscr振荡期间(例如,当bdscr在cw或ccw方向上振荡时),使用循环计数器计数环沿的数目。可停止bdscr振荡,使得可对所存储的bdscr振荡量(例如内部电压)进行取样。例如,可停止振荡以周期性取样,其中可响应于取样时段而确定tdc的时间分辨率。

21.响应于断言信号停止bdscr振荡,bd-scr的两个输出(来自两个相邻scr)保持模拟电压,且其它六个输出保持数字电压值(其中可响应于相应电源轨“vdd”或“vss”而产生用于表示二进制值的每一离散电压)。两个模拟电压中的一者被取样且转发到adc以将模拟电压转换为对应数字代码。对应数字代码指示从第一存储单元到相邻存储单元的部分(例如,小于全部)传播时间(例如单元间部分传播时间)的值。adc输出值及循环计数器值(例如,每一取样时段产生)分别提供tdc的输出位的较不精细分辨率部分及较精细分辨率部分(例如,adc的转换值的时间分辨率比循环计数值的时间分辨率更精确)。循环计数器、bdscr及adc在每一取样时段重新初始化(例如,响应于在连续取样时段内接收相位误差输入)。

22.图1是展示实例基于双向存储单元环的时间数字转换器(tdc)的系统图,其包含用于分别产生所得转换的较低有效位及较高有效位的模/数转换器及循环计数器。一般来说,tdc 100是包含环110、模拟量化器140及循环计数器130的实例tdc。环图120是环110的概念

流程图。

23.tdc 100包含用于接收将确定其时间测量的信号的至少一个输入。在实例中,两个输入适于接收上行信号(up)信号及下行(down)信号。up信号及down信号可从相位频率检测器(pfd)接收,例如下文描述的pfd 450。下文关于图4描述tdc及pfd的操作。

24.tdc 100包含用于输出时间测量的数字值的输出总线。在实例中,循环计数器130的数字输出可作为较高有效位级联到由模拟量化器140输出的较低有效位,使得可产生包含比由模拟量化器140包含的adc(例如下文描述的adc 444)固有的分辨率更高的分辨率的经组合转换结果。在实例中,数字值(例如数字字或数字输出)的较低有效位不比数字值的最高有效位更有效,且数字值的较高有效位比数字值的最低有效位更有效。

25.组合循环计数器130数字输出与adc数字输出以形成较高分辨率数字输出(如本文中描述)可降低adc的复杂性,否则需要复杂adc来获得adc的数字输出的相同分辨率。此外,adc的降低复杂性促成由adc执行的转换的更小布局及更高速度。

26.环110是经配置为环形振荡器的实例双向存储单元环。环110经耦合到时序输出(例如图4的pfd 450)且包含耦合于循环中的存储单元。循环可包含八个存储单元,例如存储单元111、存储单元112、存储单元113、存储单元114、存储单元115、存储单元116、存储单元117及存储单元118。存储单元在循环中相互耦合,使得每一存储单元在顺时针方向上具有逻辑相邻存储单元且在逆时针方向上具有逻辑相邻存储单元。每一此存储单元包含经耦合以接收up信号及down信号(例如,从例如下文描述的pfd 450的时序输出耦合)的时序输入,使得环110(例如)可选择性经配置以在顺时针或逆时针方向上振荡。环110经配置为环形振荡器,其经配置以响应于开始时间的指示而开始振荡且经配置以响应于停止时间的指示而停止振荡。

27.每一存储单元包含用于接收左信号(l)、右信号(r)、s(-2)信号及s( 2)信号的输入。左信号(l)经耦合到第一cw相邻存储单元的dx输出,右信号(r)经耦合到第一ccw相邻存储单元的dx输出,s(-2)信号经耦合到与第一cw相邻存储单元cw相邻的第二cw相邻存储单元的s输出,且s( 2)信号经耦合到与第一ccw相邻存储单元ccw相邻的第二ccw相邻存储单元的s输出。在实例中,存储单元的线性布置的第一及最后存储单元可为存储单元环中的一对相邻存储单元(例如,其中第一单元的d《1》输出经耦合到最后单元的r输入)。每一存储单元的s输出按位级联以便形成选择总线s(例如s《8:1》)。(在各种实例中,相邻存储单元是逻辑相邻存储单元,其中环沿可从第一存储单元传播到第二存储单元而不首先传播通过任何其它存储单元,不管环沿的振荡方向如何。)

28.每一存储单元经配置以响应于l信号及r信号而(在存储单元输出处)产生单元选择(s)信号且响应于up信号及down信号而产生模拟输出(ax)信号及数字输出(dx)信号。可在环中使用更少存储单元(例如总共六个存储单元,与八个存储单元相比),但在环中使用更少存储单元往往会增加设计复杂性,因为例如使用基数七或更小算术来计数环沿已传播通过的存储单元的数目。下文关于图2描述实例存储单元。

29.环图120是用于展示环110的顺时针(cw)及逆时针(ccw)振荡(例如振荡的传播)的环110的概念流程图。在实例中,环110经配置以选择性在第一时段期间在第一方向上振荡及在第一时段之后的第二时段期间在第二方向上振荡。在cw旋转中,环沿从节点a1(与存储单元111及节点d1相关联)传播,接着到节点a8(与存储单元118及节点d8相关联),接着到节

点a7(与存储单元117及节点d7相关联),接着到节点a6(与存储单元116及节点d6相关联),接着到节点a5(与存储单元115及节点d5相关联),接着到节点a4(与存储单元114及节点d4相关联),接着到节点a3(与存储单元113及节点d3相关联),接着到节点a2(与存储单元112及节点d2相关联),接着到节点a1,接着到节点a8,等等,直到接收取样指示。在ccw方向上,环沿从节点a1传播,接着到节点a2,接着到节点a3,接着到节点a4,接着到节点a5,接着到节点a6,接着到节点a7,接着到节点a8,接着到节点a1,等等,直到接收取样指示。下文关于图3及图5a及图5b描述环沿传播。

30.每一存储单元的模拟(ax)信号输出共同经分组以形成模拟总线a《8:1》,每一存储单元的数字(dx)信号输出共同经分组以形成数字总线d《8:1》,且每一存储单元的选择(sx)信号输出共同经分组以形成状态总线s《8:1》。模拟总线a《8:1》经耦合到模拟量化器140的选择输入(例如,其包含八个端子)。下文关于图4及图6描述模拟量化器140的操作。数字总线d《8:1》经耦合到循环计数器130的输入(例如,其包含八个端子)。下文关于图4描述循环计数器130的操作。状态总线s《8:1》经耦合到模拟量化器的选择输入(例如,其包含八个端子)。下文关于图4描述模拟量化器140的操作。

31.循环计数器130经配置以具有“m 3”位输出总线tdc-out《m 3:1》(例如8位宽),且模拟量化器140经配置以具有n位(例如8位)输出总线tdc-out《n:1》。输出总线tdc-out《n:1》作为较低有效位附加到循环计数器130输出位(例如输出总线tdc-out《m 3 n:n 1》)以形成输出总线tdc-out《m 3 n:1》。

32.图2是展示时间数字转换器(tdc)的实例双向存储单元的系统图。一般来说,电路200是包含存储单元201的实例电路。存储单元201是例如存储单元111的存储单元。存储单元201包含耦合到模拟总线a《8:1》的模拟输出ax(c_analog《x》)、耦合到数字总线d《8:1》的数字输出dx(d_digital《x》)及耦合到状态总线s《8:1》的选择输出(sx)。在实例中,每一存储单元201包含相应电容器(例如电容器225)及相应开关(例如高侧开关223),其中相应电容器(例如电容器225)经配置以响应于其中闭合耦合到相应电容器(例如电容器225)的相应开关(例如高侧开关223)的持续时间而积分以在相应模拟输出处积分相应积分电压。

33.模拟量化器140经配置以对由选定存储单元(例如存储单元201)的电荷泵电容器c

cp

存储的积分电压(例如,响应于泵送电荷而产生)进行取样。模拟量化器140包含可选择性耦合到c_analog《8:1》的模拟电压中的任一者的adc。所存储的电荷指示已选择存储单元的持续时间。所存储的电荷(当被选择用于取样时)响应于取样及保持电路(如下文关于图6描述)而产生保持电压,来自取样及保持电路的保持电压转换为总线tcd_out《n:1》上的数字值输出。响应于状态总线s《8:1》的相邻位的逻辑状态而选择经选择用于模/数转换的存储单元(例如,其中耦合于循环中的第一及最后存储单元被视为相邻的)。

34.循环计数器130经配置以响应于数字总线d《8:1》的位的转变而产生用于在总线tdc-out《m 3 n:n 1》上输出的数字值。一般来说,由循环计数器130输出的数字值随着存储单元环振荡而指示环沿的位置,且指示环沿已横越穿过的存储单元的数目。在实例中,d《8:1》的数字值的较低有效部分随着存储单元振荡而指示环沿的位置(例如,在循环内),且d《8:1》的数字值的较高有效部分可用于指示循环的次数(例如环沿已横越整个存储单元环的次数)。循环计数器130的输出及模拟量化器140的输出经级联以形成输出总线tdc-out《m 3 n:1》,使得时间数字转换可被确定为具有比循环计数器130的输出的分辨率更大(例如,更

精确)的电压分辨率。存储单元的低延时可提高包含存储单元201的存储单元环的振荡速率,使得例如可进行1皮秒分辨率的测量(如下文关于图7、图8、图9、图10描述)。

35.存储单元201包含控制器210、电荷泵220、放电/预充电电路230及阈值转换器240。

36.控制器210是包含分别经耦合以接收左信号(l)、右信号(r)、down信号及up信号的输入的选择电路。控制器210经配置以响应于左相邻单元被选择(例如,通过l信号为数字高)且响应于右相邻单元未被选择(例如,通过r信号为数字低)而(在第一输出处)断言s信号(其指示存储单元201已被选择)。在实例中,控制器210经配置以响应于相应相邻存储单元的相应选择信号输出的值而在选择输出处产生相应选择信号来选择其包含的存储单元(例如存储单元201,其包含控制器210)。控制器210经配置以在相应选择信号输出s处输出相应选择信号(例如sx)。针对环(例如110)中的每一存储单元(例如201),相应选择电路(例如控制器210)经配置以在每一相应选择电路的选择输出(例如sx)处产生相应选择信号。

37.控制器210经配置以响应于所接收的down信号及s信号而(在控制器210的第二输出处)断言局部down信号。第二输出经耦合到电荷泵220的低侧开关224的控制端子。电荷泵220经配置以响应于局部down信号及由电流源222传导的电流i

cp

而可控地(例如,以受控速率)汲取存储于电荷泵电容器c

cp

(耦合到高侧开关223与低侧开关224之间的节点)中的电荷。电压是在电荷泵电容器c

cp

的高侧(例如电荷泵220输出节点c_analog《x》)处产生的积分电压。积分电压指示对应于局部down信号的断言的持续时间的时段(例如其中已选择存储单元201的时段)。

38.控制器210经配置以响应于所接收的up信号及s信号而(在控制器210的第三输出处)断言局部up信号。第三输出经耦合到电荷泵220的高侧开关223的控制端子。电荷泵220经配置以响应于局部up信号及由电流源221传导的电流i

cp

而在电荷泵电容器c

cp

中可控地存储电荷。电压analog《x》是在电荷泵电容器c

cp

的高侧处产生的模拟电压,其指示对应于局部up信号的断言的持续时间的时段(例如其中已选择存储单元201的时段)。

39.放电/预充电电路230经耦合到电荷泵220输出节点c_analog《x》。放电/预充电电路230包含开关234,其具有耦合到s(-2)信号的控制端子,使得开关234经配置以响应于s(-2)信号(例如,响应于耦合到第二最左cw相邻存储单元的存储单元被选择)而使电荷泵电容器c

cp

放电。放电/预充电电路230包含开关233,其具有耦合到s( 2)信号的控制端子,使得开关233经配置以响应于s( 2)信号(例如,响应于耦合到第二最右ccw相邻存储单元的存储单元被选择)而对电荷泵电容器c

cp

预充电。开关233及234的强度(例如电流容量)比电荷泵220的高侧开关223及低侧开关224的电流容量更强(例如,使得电荷泵220输出节点c_analog《x》可在包含存储单元201的存储单元环的每一振荡期间完全充电或放电)。

40.阈值转换器240包含耦合到电荷泵220输出节点c_analog《x》的输入及耦合到输出c_digital《x》的输出。阈值转换器240经配置以将在电荷泵220输出节点c_analog《x》处产生的模拟电压转换为数字值(例如位)且在输出c_digital《x》处断言结果。例如,阈值转换器240经配置以输出阈值信号。阈值信号在电荷泵220输出节点c_analog《x》处产生的电压超过第一阈值时输出为逻辑1(高),及在电荷泵220输出节点c_analog《x》处产生的电压低于第二阈值时输出为逻辑0(低)。第一阈值大于或等于第二阈值的电压。针对环(例如110)中的每一存储单元(例如201),相应阈值转换器(例如240)经配置以在相应数字输出处产生用于指示相应积分电压是否已穿越阈值的相应阈值信号。

41.在存储单元201的另一实例中,信号up或down的输入中的一者经耦合到接地,使得包含存储单元环的存储单元环在单个方向上振荡。响应于up信号的输入经耦合到接地(且down信号被断言),包含存储单元201的存储单元环经配置以在ccw方向上振荡(使得电荷泵220输出节点c_analog《x》响应于s( 2)信号而预充电,及使得电荷泵220输出节点c_analog《x》响应于down信号而放电)。响应于down信号的输入经耦合到接地(且up信号被断言),包含存储单元201的存储单元环经配置以在cw方向上振荡(使得电荷泵220输出节点c_analog《x》响应于s(-2)信号而放电,及使得电荷泵220输出节点c_analog《x》响应于down信号而充电)。

42.在实例中,每一存储单元包含相应选择电路(例如图1的111及/或图2的210),其具有耦合到相应相邻存储单元(例如118)的输出(输出dx)的第一输入(例如输入l)及耦合到时序输出的第二输入(例如输入up),其中每一存储单元包含相应电容器(例如225)及相应开关(例如223),相应开关包含耦合到相应选择电路(例如210)的选择输出(例如输出up)的控制端子且包含耦合到相应电容器(例如225)的电流端子,且其中每一存储单元(例如111)包含具有耦合到相应电容器(例如225)的输入的相应阈值转换器(例如240)。

43.图3是实例tdc的实例六存储单元环的实例双向操作的波形图。波形300是包含up、down、a1、a2、a3、a4、a5及a6信号的实例波形。波形300可由类似于包含八个存储单元的环110般配置的实例六存储单元环产生。

44.一般来说,up及down信号可由相位频率检测器(例如下文描述的pfd 450)产生。pfd经配置以响应于反馈时钟的相位滞后于参考时钟的相位而断言up信号及响应于反馈时钟的相位领先于参考时钟的相位而断言down信号。反馈时钟及参考时钟被独立产生,其可导致反馈时钟的相位相对于参考时钟的相位向前及向后时间漂移。在时段301期间,反馈时钟的相位滞后于参考时钟(例如,使得断言up信号)。在时段302期间,反馈时钟及参考时钟的相位大体上相等(例如,大体上相等使得不断言down信号及up信号两者)。在时段303期间,反馈时钟的相位领先于参考时钟(例如,使得断言down信号)。作为实例,在时段304期间断言up及down信号两者(例如,响应于用于指示将进行tdc时序取样的周期性时序信号)。高分辨率(例如精细)时序信息可从在时段302期间存储为信号量343及353的模拟值产生,且可从在时段304期间存储为信号量326及336的模拟值产生。

45.在时段301的开始,down信号为低(未断言)且up信号转变为高(断言),使得up信号从低电压状态转变为高电压状态。响应于up信号的断言,实例六存储单元环经配置以在ccw方向上振荡,其中第一存储单元的a4信号开始从低值转变为高值。响应于a4信号穿越第一阈值,d4信号被切换为高。响应于d4信号被切换为高,信号s5被切换为高,其响应性将第一存储单元(例如,其包含a1信号输出)的s(-2)输入驱动到逻辑高电平。响应于在第一存储单元的s(-2)输入处接收的信号,第一存储单元的a1信号放电到低电压状态。其它存储单元经配置以类似且连续地(例如,在ccw方向上)依序充电及放电,使得一系列上升环沿可在围绕存储单元环的ccw循环中传播(例如,其中信号a4的上升触发信号a5的上升,信号a5的上升触发信号a6的上升,信号a6的上升触发信号a1的上升,信号a1的上升触发信号a2的上升,信号a2的上升触发信号a3的上升,信号a3的上升触发信号a4的上升,等等)。

46.响应于第一存储单元的l信号输入被驱动为高(例如,通过第六存储单元在耦合到l信号输入的输出上断言d6信号,或通过响应于up信号的上升沿而产生的初始化脉冲),a1

信号随转变311上升。a1信号响应于第一存储单元的电荷泵220响应于up信号激活而上升。随着a1信号上升,转换器(例如阈值转换器240)的输入的电压上升到高于阈值,使得d1输出(其耦合到第二存储单元的l信号输入用于产生a2)被切换为高(例如,被驱动为高)。响应于d1输出被驱动为高,第二存储单元的电荷泵(用于驱动信号a2)经激活使得(响应于第二存储单元的经激活电荷泵)信号a2上升以具有转变321。

47.转变321比转变311延后时段tst(例如电荷泵电容器c

cp

(例如电容器225)的电压上升的积分到取样阈值时间)。可响应于每一存储单元的时段tst而确定实例六存储单元环的振荡速率。实例六存储单元环的每一存储单元具有类似设计(且使用相同处理及相同衬底形成),使得六个存储单元的每一组件的操作参数(例如延时及驱动强度)类似于相应组件。例如,第一存储单元的电荷泵220可经配置以具有相同于相同存储单元环中的其它电荷泵中的电荷泵220的结构设计。

48.转变331响应于转变321而触发(例如,响应于在第二存储单元的输出处断言信号s而触发,第二存储单元的输出经耦合到第三存储单元的信号l输入)。以类似于通过转变321触发转变331的方式,信号a4随后响应于转变331而在转变341处转变为高。

49.类似地,信号a5随后响应于信号a4的转变341而在转变351处转变为高。响应于信号a5的转变351,第五存储单元的控制器在第五存储单元的输出上断言s信号,第五存储单元的输出经耦合到第一存储单元的s(-2)输入。响应于第一存储单元的s(-2)输入被驱动为高,第一存储单元的放电开关(例如开关234)经闭合使得a1信号放电到低电压状态。

50.以类似于初始化信号a5的转变351的方式,信号a6随后响应于信号a5的转变351而随转变361转变为高。响应于转变361,信号a1随转变312上升。

51.因此,在从转变311的开始延续到转变312的开始的时段内,一序列环沿已完成整个循环(围绕存储单元环)。上升环沿系列持续传播,直到时段301结束(且直到时段302开始),此时up信号被驱动为低。up信号的反转隔离及维持在up信号的反转瞬间保持的由每一存储单元的每一电荷泵电容器c

cp

存储的电荷。

52.在所展示的特定实例中,在时段302期间,信号a4包含信号量343且信号a5包含信号量353。信号量343指示已选择第五存储单元的时间(例如,在此期间已主要选择第五存储单元)。下文参考图6描述信号量343的adc转换的实例操作。

53.在时段303开始时,断言down信号且up信号保持低,使得六存储单元环经配置以在cw方向上振荡。响应于down信号的断言,第六存储单元的a6信号最初充电到高电压状态。响应于第二存储单元的s( 2)输入及/或响应于down信号的上升沿而产生的初始化脉冲,第六存储单元的a6信号充电到高电压状态。其它存储单元类似且连续地(例如,在cw方向上)依序充电(例如,使得下降沿的环沿可在围绕存储单元环的循环中传播)。

54.响应于第六存储单元的r信号输入被驱动为低(例如,通过第一存储单元在耦合到r信号输入的输出上断言低d1信号,或通过响应于down信号的上升沿而产生的初始化脉冲),a6信号随转变364下降。a6信号响应于第一存储单元的电荷泵220响应于down信号激活而下降。随着a6信号下降,转换器(例如阈值转换器240)的输入的电压下降到低于阈值,使得输出d6(其经耦合到第五存储单元的r信号输入用于产生a5)被切换为低(例如,被驱动为低)。响应于d6输出被驱动为低,第五存储单元的电荷泵(用于驱动信号a5)经激活使得(响应于第五存储单元的经激活电荷泵)信号a5下降以具有转变354。

55.转变354比转变364延后时段tst。实例六存储单元环在cw及ccw上的振荡速率大体上相等(例如,在彼此的10%内大体上相等)。实例六存储单元环的每一存储单元具有类似设计(且使用相同处理及相同衬底形成),使得六个存储单元的每一组件的操作参数(例如延时及驱动强度)类似于相应组件。例如,电流源221及电流源222经配置以产生大体上相等(例如,在彼此的10%内大体上相等)电流i

cp

。

56.信号a4的转变344响应于转变354而触发(例如,响应于在第五存储单元的输出处断言信号s而触发,第五存储单元的输出经耦合到第四存储单元的信号r输入),使得信号a4下降。以类似于通过转变354触发转变344的方式,信号a3随后响应于转变344而在转变334处转变为低。

57.类似地,信号a2随后响应于信号a3的转变334而转变为低。响应于信号a3的转变334,第二存储单元的控制器在第二存储单元的输出上断言s信号,第二存储单元的输出经耦合到第六存储单元的s( 2)输入。响应于第二存储单元的s( 2)输入被驱动为高,第一存储单元的预充电开关(例如开关233)经闭合使得a1信号被预充电到高电压状态。

58.以类似于信号a2的转变的方式,信号a1随后响应于信号a2的向下转变而随转变314转变为低。转变314的开始比转变324的开始延后时段tst 306。响应于转变314,信号a6随转变365下降。

59.因此,一序列下降环沿已完成整个循环(围绕存储单元环),其中整个循环开始于转变364的开始且结束于转变365的开始。环沿持续传播,直到时段303结束(及时段304开始),此时up信号被驱动为高。up信号及down信号的断言隔离及维持(例如,为了取样目的)在up信号的反转瞬间保持的由每一存储单元的每一电荷泵电容器c

cp

存储的电荷。

60.在所展示的特定实例中,在时段304期间,信号a2包含信号量326且信号a3包含信号量336。信号量336指示已选择第三存储单元的时间(例如,在此期间已主要选择第三存储单元)。信号量326由模拟量化器140转换为数字值,其指示精细分辨率时间测量(例如,相对于由循环计数器130产生的值)。

61.图4是展示耦合到相位频率检测器(pfd)的实例基于双向存储单元环的时间数字转换器(tdc)的系统图。系统400是经配置以测量参考时钟与反馈时钟之间的相位差的实例系统,其中可响应于相位测量(例如时间测量)而调整反馈时钟的相位/频率。例如,系统400的tdc是包含环110、模拟量化器440(例如模拟量化器140)及循环计数器430(例如循环计数器130)的实例tdc。tdc可经配置以测量参考时钟信号与响应于相位差测量而产生(例如,通过数字控制振荡器)的反馈时钟信号之间的相位差(例如,在时间上)。一般来说,tdc经配置以(例如,在环110的时序输入处)从pfd(例如pfd 450)接收时间差(例如相位差)的指示,使得tdc可响应于从pfd 450接收的指示而测量时间差。

62.在实例中,pfd 450是包含参考时钟(ref clk)输入、反馈时钟(fb clk)输入、pfd复位信号输出及包含up信号输出及down信号输出的检测器输出的检测器。检测器输出经耦合到环110的时序输入,时序输入包含up信号输入及down信号输出。pfd 450经配置以比较参考时钟的输入相位与反馈时钟的相位。pfd 450经配置以响应于反馈时钟的相位滞后于参考时钟的相位而断言up信号及响应于反馈时钟的相位领先于参考时钟的相位而断言down信号。响应于up及down信号的断言,环110经配置以产生用于指示相位比较的第一测量的至少一个模拟信号,且经配置以产生用于指示相位比较的第二测量的至少一个二进制信

号(例如,其中第二测量具有小于第一测量的电压分辨率的电压分辨率)。在至少一个实例中,pfd 450包含适于产生开始时间的指示及停止时间的指示的时序输出(例如up信号输出及down信号输出)。

63.pfd复位信号可响应于(例如)用于指示将进行tdc时序取样的周期性时序信号而断言。tdc的速度越高,测量时序样本的频率越高(例如,使得可提高反馈时钟对参考时钟的频率保真度)。同时断言up及down信号(例如,使得up信号波形的一部分为高,同时down信号的一部分为高)可响应于pfd复位信号及/或周期性时序信号。周期性时序信号可响应于pfd 450的时钟输入(例如参考时钟)而产生。

64.pfd复位输出经耦合到延迟链及脉冲产生器452的输入。延迟链及脉冲产生器452包含其中产生启用adc(en_adc)信号(例如,通过延迟链及脉冲产生器452产生)的输出。sample_adc波形730(下文关于图7描述)是信号en_adc的实例波形。在至少一个实例中,en_adc信号是响应于周期性时序信号而产生的脉冲,其中脉冲的第一沿相对于周期性时序信号的值或值变化而延迟,且其中脉冲的第二沿相对于脉冲的第一沿而延迟。

65.延迟链及脉冲产生器452的en_adc信号输出经耦合到模拟量化器440的选择器442的en_adc信号输入及延迟链454的en_adc信号输入。在实例中,模拟量化器440经配置以响应于相应积分电压中的选定一者而在转换输出处产生转换值,其中相应积分电压中的选定一者响应于相应选择信号中的至少一者而选择,且其中转换值指示从开始时间延续到停止时间的持续时间的时间测量的第一部分。

66.选择器442是下文关于图6描述的实例选择器。选择器442经配置以对响应于选定存储单元的电容器的电荷积分而产生的电压进行取样(例如,如同用取样及保持模拟电路的取样)。选择器442包含耦合到存储单元的相应数字输出(例如选择总线s《8:1》)的选择输入。特定存储单元可响应于选择总线的位值(例如相邻位值对)而选择。

67.选择器442的取样及保持输出经耦合到adc 444的adc_in信号输入。adc 444可包含电阻阶梯及比较器网络,使得adc 444经配置以(在转换输出处)输出用于指示响应于选择器442而产生的模拟电压的数字值(例如,作为n位值)(例如,其中可产生adc 444的输出值且无需时控adc 444)。

68.模拟量化器440进一步包含二进制补码产生器446、循环方向检测器447及多路复用器448。二进制补码产生器446包含耦合到adc 444的输出的输入且包含其中二进制补码产生器446经配置以响应于由adc 444输出的值而产生二进制补码值的输出。在实例中,模拟量化器440经配置以响应于环形振荡的第一方向或第二方向的选择而输出二进制补数。

69.循环方向检测器447包含耦合到pfd 450的up输出的第一输入(例如d输入)及耦合到pfd 450的down输出的第二输入(例如上升沿触发的时钟输入)。循环方向检测器447经配置以响应于up及down信号而产生循环方向信号。在实例中,循环方向信号响应于up信号的低值而为低(逻辑0),且循环方向信号响应于down信号的低到高转变而为高(逻辑1)。

70.多路复用器448包含耦合到adc 444的输出的第一输入且包含耦合到二进制补码产生器446的输出的第二输入。多路复用器448经配置以在多路复用器的输出处产生经方向调整的adc输出(direction-adj.adc_out)信号。当循环方向信号为低时,经方向调整的adc输出信号包含(响应于循环方向信号)adc_out值,及当循环方向信号为高时,经方向调整的adc输出信号包含所产生的二进制补码值(例如adc_out信号的所产生二进制补码值)。

71.延迟链454经配置以(例如,响应于信号en_adc)在延迟链454的write_clk信号输出处产生write_clock(write_clk)信号。write_clk波形740(下文关于图7描述)是信号write_clk的实例波形。在至少一个实例中,write_clk信号是响应于信号en_adc而产生的脉冲,其中脉冲的第一沿相对于信号en_adc的值或值变化而延迟,且其中脉冲的第二沿相对于脉冲的第一沿而延迟。延迟链454的write_clk信号输出经耦合到d型触发器(d-f/f或“锁存器”)462及464的相应write_clk信号输入(例如时钟输入)。延迟链454的write_clk信号输出进一步耦合到延迟链456的write_clk信号输入。

72.锁存器464包含耦合到adc 444的输出的n位adc结果输入。锁存器464经配置以响应于write_clk信号而锁存n位adc结果。锁存器464包含其中断言经锁存n位adc结果的n位tdc-out《n:1》输出。tdc-out《m 3 n:1》总线的tdc-out《n:1》部分包含被测量的时段的较低有效位(例如,如通过模/数转换来确定)。

73.锁存器462包含耦合到“m 3”位循环计数器输出的“m 3”位长循环计数器430结果输入。“m 3”位输出值是用于指示已完成振荡循环的整数次数(由较高有效“m”位指示,其中“m”是用于指示可计数的最大循环数的位数)及用于指示未完成振荡循环的分数(例如,小于1分数)(由较低有效“ 3”位指示,其中“ 3”是环110中的存储单元数的二进制指数)的定点数。锁存器462经配置以响应于write_clk信号而锁存“m 3”位循环计数器结果。锁存器462包含其中断言经锁存“m 3”位长循环计数器结果的“m 3”位tdc-out《m 3 n:n 1》输出。tdc-out《m 3 n:1》总线的tdc-out《n:1》部分包含被测量的时段的较低有效位(例如,如通过模/数转换来确定)。

74.延迟链456经配置以(例如,响应于信号write_clk)在延迟链456的clr_counter信号输出处产生清除计数器(clr_counter)信号。clr_counter波形750(下文关于图7描述)是信号clr_counter的实例波形。在至少一个实例中,clr_counter信号是响应于信号write_clk而产生的脉冲,其中脉冲的第一沿相对于信号write_clk的值或值变化而延迟,且其中脉冲的第二沿相对于脉冲的第一沿而延迟。延迟链454的clr_counter信号输出经耦合到切换型触发器(t-f/f或“锁存器”)431及m位计数器435的相应clr_counter信号输入。

75.循环计数器430包含锁存器431、m位计数器435、ex-nor门432、全加器433、全加器434及多路复用器436。锁存器431的输入是耦合到环110中的每一存储单元的相应数字输出的数字输入。在实例操作中,锁存器431及m位计数器435响应于clr_counter信号而初始化(例如,清除),clr_counter信号响应于先前时间测量完成而断言(例如,其响应于分别由循环计数器130及模拟量化器140产生的数字及模拟量的组合而产生)。下文参考图5a及5b描述循环计数器430的实例操作。

76.在实例中,模拟量化器(例如440)具有模拟输入(c_analog《8:1》)及数字输入(s《8:1》),其中每一模拟输入经耦合到相应电容器中的相应一者(例如,存储单元111到118的每一电容器225个别耦合到模拟量化器),且其中每一数字输入经耦合到相应选择电路的选择输出中的相应一者(例如,存储单元111到118中的每一者的输出sx个别耦合到模拟量化器)。模拟量化器(例如440)的输出是包括用于指示从开始时间延续到停止时间的持续时间的测量的较低有效位的转换值。

77.在实例中,循环计数器(例如430)具有输入(c_digital《8:1》),其中每一输入经耦合到相应阈值转换器的输出中的相应一者(例如,锁存器431的触发器系列的每一相应输入

个别耦合到存储单元111到118中的每一者的阈值转换器240的输出)。在实例中,循环计数器(例如430)经配置以响应于至少一些相应阈值信号的值变化而产生循环计数值,其中循环计数值指示从开始时间延续到停止时间的持续时间的时间测量的第二部分。在实例中,循环计数值包括用于指示从开始时间延续到停止时间的持续时间的测量的较高有效位。在实例中,循环计数值包括在开始时间与停止时间之间计数的环的已完成循环振荡的次数。

78.图5a及图5b是包含响应于图4的循环计数器的操作而产生的实例值的列的实例图。图500是包含一系列列的实例图,其中相应列的开头处的行包含初始起始值(例如,响应于clr_counter信号而初始化)。每一列中的连续行展示行中的某些值可如何随时间改变。

79.一般来说,每一行指示同时存在的值(例如,针对延续通过列510、列520、列530、列540、列550、列560及列570的每一行)。一列中的八行的第一群组501展示存储单元环(例如环110)中的振荡的第一循环,其中每一行包含响应于环沿从第一存储单元横越到相邻存储单元而产生的值。一列中的八行的第二群组502展示存储单元环中的振荡的第二循环,且一列中的八行的第三群组503展示存储单元环中的振荡的第三循环。下文参考图4、图5a及图5b描述循环计数器430的实例操作。

80.锁存器431包含耦合到数字总线d《8:1》的数字总线输入,数字总线d《8:1》在环110的c_digital《8:1》输出处产生。锁存器431还包含一组正逻辑输出q(例如,使得每一q输出从八个存储单元的相应输出耦合)及一组负逻辑输出qn(例如,使得每一qn输出从八个存储单元的相应输出耦合)。锁存器431的输出q各自耦合到ex-nor门432的八位输入的相应输入及全加器433的八位输入的相应输入。锁存器431的输出qn经耦合到全加器434的八位输入。

81.锁存器431经配置以响应于锁存器431的数字总线输入处的相应位的变化的正电压转变而切换每一输出(例如q或qn)的输出状态。例如,列510(图5a)中展示锁存器431的数字总线输入的值,且列520中展示锁存器431对数字总线输入的值的响应。在实例中,列520展示锁存器431对列510的值的响应,列510包含展示存储单元循环内的振荡的逆时针方向的值。

82.ex-nor门432包含耦合到m位计数器435的输入的输出。ex-nor门432经配置以(在ex-nor门432的输出处)产生存储单元循环中的振荡环沿的已完成循环的指示(例如,见列530)。例如,ex-nor门432可响应于环110的c_digital《8:1》输出及/或ex-nor门432的q输出而断言已完成循环的指示。如列520及列530中展示,ex-nor门432经配置以响应于锁存器431输出的所有位是第一逻辑状态(例如逻辑1)而产生初始指示(例如逻辑1)。在实例中,ex-nor门432可响应于相应阈值信号c_digital《8:1》输出中的每一者具有相同值(例如,其中每一相应阈值信号同时具有相同于其它相应阈值信号的值)而断言已完成循环的指示。例如,实际上可通过将m位计数器435的每一计数位预设为逻辑1(例如,使得第一指示将m位计数器435从预设值切换到输出值0(零),其指示未发生完整循环)来忽略初始指示。在实例中,循环计数值(例如,见图9的loop counter 980)包括环的已完成循环振荡的次数,且已完成循环振荡的次数响应于其中每一相应阈值信号同时具有相同于其它相应阈值信号的值的逻辑状态而递增。

83.ex-nor门432经配置以响应于锁存器431输出的所有位是不同于第一逻辑状态的第二逻辑状态(例如逻辑0)而产生第一完整循环的第一指示(例如逻辑1)。ex-nor门432经配置以响应于锁存器431输出的所有位是第一逻辑状态(例如逻辑1)而产生第二完整循环

的第三指示(例如逻辑1)。

84.例如,确定由ex-nor(例如等效逻辑函数,其中所有输入位具有相同逻辑状态)确定的循环完成促进提高实例存储单元环的振荡速度,因为存储单元的存储状态每一循环仅切换一次(例如,使得在存储单元环的振荡的单个循环期间,存储单元无需横越两个逻辑状态)。在所展示的实例中,第一循环响应于逻辑0到1转变的环而完成,且第二循环响应于逻辑1到0转变的环而完成。

85.除产生已完成循环振荡的次数的指示之外,循环计数器430还经配置以确定部分循环已横越通过的单元的数目(例如在循环振荡停止时在完成整个循环之后由环沿横越的单元的数目)。在实例中,循环计数器(例如循环计数器430)包括第一部分循环指示符产生器(例如全加器433)、第二部分循环指示符产生器(例如全加器434)及多路复用器(例如多路复用器436),多路复用器具有耦合到第一部分循环指示符产生器(例如全加器433)的输出的第一输入且具有耦合到第二部分循环指示符产生器(例如全加器434)的输出的第二输入,其中多路复用器(例如多路复用器436)经布置以响应于已完成循环振荡的次数的较低有效位(例如m位计数器435的输出的最低有效位)的逻辑状态而选择第一部分循环指示符产生器及第二部分循环指示符产生器中的一者。

86.在实例中,传播环沿可包含上升沿转变(例如,从0到1)且可包含下降沿转变(例如,从0到0)。第一部分循环指示符产生器(例如全加器433,其中列540中展示全加器433输出值)经配置以在输出处指示(例如,计数)上升转变环沿已传播通过的存储单元的数目。当传播环沿包含下降沿转变(例如,从0到1)时,第二部分循环指示符产生器(例如全加器434,其中列550中展示全加器434输出值)经配置以指示(例如,计数)下降转变环沿已传播通过的存储单元的数目。在各种实例中,部分循环指示符产生器可为温度计型进程指示器。

87.因为(例如)全加器434指示(例如,作为3位值)上升转变环沿已传播(例如,已在完整循环或复位条件之后传播)通过的存储单元数的数目且因为(例如)全加器434指示(例如,作为3位值)下降转变环沿已传播(例如,已在完整循环或复位条件之后传播)通过的存储单元的数目,所以多路复用器436(例如mux)经布置以在整个循环完成时交替选择部分循环指示符。全加器433的输出(例如3位输出)经耦合到多路复用器436的s(0)输入(例如第一输入),全加器434的输出(例如3位输出)经耦合到s(1)输入(例如第二输入),且m位计数器435的较低有效位(例如最低有效位)(例如,其指示已完成循环振荡的奇数或偶数次数是否已由m位计数器435计数)经耦合到多路复用器436的选择输入。

88.在实例中,多路复用器436经布置以响应于已完成循环振荡的次数的位的逻辑状态(例如,其中位指示已完成循环振荡的奇数或偶数次数)而选择第一部分循环指示符产生器(例如全加器433)及第二部分循环指示符产生器(例如全加器434)中的一者。在实例中,在停止时间(例如,在环停止振荡时)传播的振荡循环的小于1分数期间切换其相应阈值信号的存储单元的数个存储环(例如,环110)数目(例如存储单元111到118的任何链)通过在第一完整振荡循环期间包含上升转变及通过在第一完整振荡循环之后的连续第二振荡循环期间包含下降转变来切换其相应阈值信号。在实例中,循环计数值包括在停止时间传播的振荡循环的小于1分数,其中小于1分数响应于在停止时间传播的振荡循环的小于1分数期间切换其相应阈值信号的存储单元(例如存储单元111到118的任何链)的数目而确定。

89.多路复用器436经配置以响应于已完成循环振荡的次数的指示而在多路复用器

436输出处(例如,在mux输出《3:1》处)产生部分循环指示。m位计数器435输出《m 3:4》(例如“m 3”位长循环计数器430结果的八个最高有效位)经展示为列560的“粗计数”值,且多路复用器436输出(例如“m 3”位长循环计数器430结果的最低有效位)经展示为列570的“细计数”值。列560的“粗计数”是已完成循环振荡次数的指示,且列570的“细计数”是环沿已传播通过的存储单元环的存储单元的数目的指示。

90.图6是实例基于双向存储单元环的时间数字转换器(tdc)的实例模拟取样电路的示意图。取样电路600是通常包含选择器610逻辑电路系统、开关611、612、613、614、615、616、617、618及620及电容器c1及c2的实例取样电路。例如,开关可为低电阻模拟传输门。开关可经布置为具有八个输入及一个输出的模拟多路复用器。

91.选择器610是包含输入s《8:1》的逻辑电路,输入s《8:1》例如在环110的存储单元的相应数字输出处耦合(例如,按位耦合)到状态总线s《8:1》。选择器610逻辑电路系统经配置以产生用于对存储单元的存储电荷进行取样的选择信号,其中响应于由数字总线d《8:1》传送的信号对(例如s《x》及s《y》,其中“x”及“y”是逻辑相邻存储单元的数目)而产生开关的选择信号。在实例中,“y”等于“x 1”。

92.例如,开关611包含耦合到c_analog《1》输出的输入、耦合到选择器610逻辑电路系统的相应输出的控制输入及耦合到电容器c1的高侧节点的输出。开关611经配置以在s《1》及s《2》两者为高时闭合。开关611的闭合将电荷转移到电容器c1,在开关611断开之后,所转移的电荷存储于电容器c1中。

93.在实例中,开关612包含耦合到c_analog《2》输出的输入、耦合到选择器610逻辑电路系统的相应输出的控制输入及耦合到电容器c1的高侧节点的输出。开关612经配置以在s《2》及s《3》两者为高时闭合。开关612的闭合将电荷转移到电容器c1,在开关612断开之后,所转移的电荷存储于电容器c1中。

94.在实例中,开关613包含耦合到c_analog《3》输出的输入、耦合到选择器610逻辑电路系统的相应输出的控制输入及耦合到电容器c1的高侧节点的输出。开关613经配置以在s《3》及s《4》两者为高时闭合。开关613的闭合将电荷转移到电容器c1,在开关613断开之后,所转移的电荷存储于电容器c1中。

95.在实例中,开关614包含耦合到c_analog《4》输出的输入、耦合到选择器610逻辑电路系统的相应输出的控制输入及耦合到电容器c1的高侧节点的输出。开关614经配置以在s《4》及s《5》两者为高时闭合。开关614的闭合将电荷转移到电容器c1,在开关614断开之后,所转移的电荷存储于电容器c1中。

96.在实例中,开关615包含耦合到c_analog《5》输出的输入、耦合到选择器610逻辑电路系统的相应输出的控制输入及耦合到电容器c1的高侧节点的输出。开关615经配置以在s《5》及s《6》两者为高时闭合。开关615的闭合将电荷转移到电容器c1,在开关615断开之后,所转移的电荷存储于电容器c1中。

97.在实例中,开关616包含耦合到c_analog《6》输出的输入、耦合到选择器610逻辑电路系统的相应输出的控制输入及耦合到电容器c1的高侧节点的输出。开关616经配置以在s《6》及s《7》两者为高时闭合。开关616的闭合将电荷转移到电容器c1,在开关616断开之后,所转移的电荷存储于电容器c1中。

98.在实例中,开关617包含耦合到c_analog《7》输出的输入、耦合到选择器610逻辑电

路系统的相应输出的控制输入及耦合到电容器c1的高侧节点的输出。开关617经配置以在s《7》及s《8》两者为高时闭合。开关617的闭合将电荷转移到电容器c1,在开关617断开之后,所转移的电荷存储于电容器c1中。

99.在实例中,开关618包含耦合到c_analog《8》输出的输入、耦合到选择器610逻辑电路系统的相应输出的控制输入及耦合到电容器c1的高侧节点的输出。开关618经配置以在s《8》及s《1》两者为高时闭合。开关618的闭合将电荷转移到电容器c1,在开关618断开之后,所转移的电荷存储于电容器c1中。

100.开关620具有耦合到电容器c1的高侧节点的输入及耦合到电容器c2的高侧节点及adc(例如adc 444)的模拟输入(adc_in)的输出。开关620经配置以响应于en_adc(下文关于图7描述)而将所存储的电荷从电容器c1转移到电容器c2(例如,用于由adc 444取样)。如上文描述,adc 444经配置以产生数字值(例如tdc-out《n:1》),其指示单元间部分传播时间。

101.本文中描述的存储单元环的实例时序分辨率可响应于时段tst(例如时段tst 305)而确定。假设高侧电源轨vdd=1伏,电荷泵电容器c

cp

=2微微法拉,电荷泵电流i

cp

为4毫安,且时段tst具有以下关系:

[0102][0103]

时段tst为2.5

×

10-10

秒。假设adc输出为8个位,adc步进(adc_steps)的数目为256。tdc的分辨率(tdc_resolution)可响应于时段tst及adc_steps的数目而确定:

[0104][0105]

使得tdc分辨率为9.766

×

10-13

秒(其可舍入到1皮秒)。

[0106]

图7是包含图4的实例系统的实例模拟的波形的波形图。图700包含使用上文描述的参数及经选择用于制造电路的目标65纳米工艺(包含用于本文中描述的存储单元环的技术)的参数的实例模拟的波形。图700的实例波形包含信号up 710、down 720、sample_adc 730、write_clk 740、clr_counter 750、c《1》761、c《2》762、c《3》763、c《4》764、c《5》765、c《6》766、c《7》767、c《8》768、adc_out 770及loop counter 780。

[0107]

在实例模拟中,参考时钟(例如,见图4)经选择以比反馈时钟领先选定相位延迟(例如spd),如由信号up 710的断言与信号down 720的断言的时间差指示。信号up由pfd(例如pfd 450)响应于参考时钟的相位而断言(例如,作为低到高转变),且信号down 720由pfd响应于down信号相对于信号up 710的相位的相位差而断言(例如,作为低到高转变)。

[0108]

复位脉冲(例如由图4的pfd 450产生的信号pfd_reset)由pfd产生,其在模拟中指示为信号up 710与down 720的逻辑and函数。sample_adc 730(例如由延迟链及脉冲产生器452产生的en_adc信号)响应于复位脉冲(例如pfd_reset)而产生,信号write_clk 740响应于信号sample_adc 730而产生,且信号clr_counter 750响应于信号write_clk 740而产生。

[0109]

存储单元转变的次数“st_n”(例如环沿从第一存储单元到下一相邻存储单元的传播)可确定为st_n=round(spd/tst),其中(例如)转变次数可确定为选定相位延迟的量除以存储单元电容器充电时间的round函数。转变次数由循环计数器捕获(例如,其中已完成循环的次数输出为m位计数器435的“粗”输出,且其中部分完成循环的转变次数由多路复用

器436输出)。在图7及图8的模拟中,loop counter 780包含经组合“粗及细”数字循环测量。

[0110]

图8是包含图7在较小比例下的实例模拟的波形的波形图。在图800中,c《5》的电压(例如模拟电压)响应于在约1.838微秒开始的sample_adc 730脉冲而取样。为了对c《5》的电压进行取样,模拟取样及保持电路经配置以选择(例如,响应于存储单元环s《8:1》输出)由第五存储单元产生的中间模拟电压。c《5》的转换值(例如取样值)及循环计数器的输出响应于在约1.84微秒断言write_clk 740而取样。由adc产生的转换值是tdc-out《m 3 n:1》总线的tdc-out《n:1》部分,且循环计数器的输出是tdc-out《m 3 n:1》总线的tdc-out《m 3 n:n 1》部分。转换值指示(例如存储单元环的振荡时间的)开始时间与停止时间之间的持续时间的时间测量(例如时间测量值)的第一部分,且循环计数值指示开始时间与停止时间之间的持续时间的时间测量的第二部分。

[0111]

adc的输出及adc的输出的二进制补码基于相位误差的方向来多路复用。例如,多路复用器448经配置以响应于循环方向信号而产生选定输出。

[0112]

因为adc经配置以在存储单元环振荡停止后不久产生样本且因为存储单元环在每一write_clk 740脉冲之后复位,所以归因于泄漏效应的每一存储单元的电容器上的电压降不会显著影响最小操作输入频率。因此,参考时钟的频率可高达100兆赫。相比之下,最大操作频率通常受经选择用于adc的架构的速度限制。

[0113]

图9是包含图4的实例系统的实例双取样模拟的波形的波形图。图900包含使用上文描述的参数及经选择用于制造电路的目标工艺(包含用于本文中描述的存储单元环的技术)的参数的实例模拟的波形。图900的实例波形包含信号up 910、down 920、sample_adc 930、write_clk 940、clr_counter 950、c《1》961、c《2》962、c《3》963、c《4》964、c《5》965、c《6》966、c《7》967、c《8》968、adc_out 970、loop counter 980及tdc_out 990。

[0114]

在实例模拟中,参考时钟(例如,见图4)经选择以比反馈时钟领先选定相位差(例如,如由信号up 910的断言与信号down 920的断言的时间差指示)。信号up由pfd(例如pfd 450)响应于参考时钟的相位而断言(例如,作为低到高转变),且信号down 920由pfd响应于down信号相对于信号up 910的相位的相位差而断言(例如,作为低到高转变)。

[0115]

复位脉冲(例如由图4的pfd 450产生的信号pfd_reset)由pfd产生,其在模拟中指示为信号up 910与down 920的逻辑and函数。sample_adc 930(例如由延迟链及脉冲产生器452产生的en_adc信号)响应于复位脉冲(例如pfd_reset)而产生,信号write_clk 940响应于信号sample_adc 930而产生,且信号clr_counter 950响应于信号write_clk 940而产生。在图9及图10的模拟中,loop counter 980包含经组合“粗”及“细”数字循环测量。

[0116]

图10是包含图9在较小比例下的实例模拟的波形的波形图。在图1000中,c《5》的电压(例如模拟电压)的第一样本响应于在约1.838微秒开始的sample_adc 930脉冲而取样。c《5》的转换值由adc_out 970展示,adc_out 970具有用于第一样本的值39(例如二进制00100111),且loop counter 990的值为00001001。c《5》的转换值(例如取样值)及循环计数器的输出响应于在约1.84微秒断言write_clk 940而取样。因为循环计数器值包含较高有效位“00001001”且因为转换值包含较低有效位“00100111”,所以用于第一样本的tcd_out 990的值为“0000100100100111”。

[0117]

c《5》的电压(例如模拟电压)的第二样本响应于在约1.93微秒开始的sample_adc 930脉冲而取样。c《5》的转换值由adc_out 970展示,adc_out 970具有用于第一样本的值38

(例如二进制00100110),且loop counter 990的值为00001001。c《5》的转换值(例如取样值)及循环计数器的输出响应于在约1.94微秒断言write_clk 940而取样。因为循环计数器值包含较高有效位“00001001”且因为转换值包含较低有效位“00100110”,所以用于第一样本的tcd_out 990的值为“0000100100100110”。

[0118]

图11是图4的实例系统的时间数字转换的实例方法的流程图。实例方法1100可包含下文描述的各种技术。在各种实施方案中,所描述的操作无需以所描述的顺序执行。在实例方法1100中,方法可启动于1102。

[0119]

在1102,方法可包含由存储单元环接收开始时间的指示及停止时间的指示。

[0120]

在1104,方法可包含由存储单元环的圆耦合存储单元响应于开始时间的指示及响应于停止时间的指示而振荡。

[0121]

在1106,方法可包含由圆耦合存储单元中的第一存储单元的电容器响应于其中选择第一存储单元的持续时间而在模拟输出处积分积分电压。

[0122]

在1108,方法可包含由阈值转换器在数字输出处产生用于指示积分电压是否已穿越阈值的阈值信号。

[0123]

在1110,方法可包含由选择电路响应于用于选择逻辑相邻于第一存储单元的第二存储单元的第二选择信号而在第一选择输出处产生用于选择第一存储单元的第一选择信号,选择电路具有耦合到第二存储单元的选择输出的选择输入。

[0124]

在1112,方法可包含由具有耦合到模拟输出的输入的模拟量化器接收积分电压。可选地,可响应于第一选择信号而选择接收积分电压。

[0125]

在1114,方法可包含由模拟量化器响应于积分电压而在转换输出处产生转换值。

[0126]

在1116,方法可包含由具有耦合到数字输出的数字输入的循环计数器响应于阈值信号的值变化而产生循环计数值。

[0127]

在1118,方法可选地包含响应于转换值及循环计数值而产生时间测量值,其中转换值指示时间测量值的较精细分辨率部分,且其中循环计数值指示时间测量值的较不精细分辨率部分。

[0128]

在权利要求书的范围内,所描述的实施例可修改,且其它实施例是可行的。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。